RS08

微控制器

飞思卡尔半导体

MC9RS08KA2

数据手册 : 技术数据

MC9RS08KA1

数据手册:技术数据

MC9RS08KA2

MC9RS08KA1

数据手册

MC9RS08KA2ZHS

第 1 版

2006 年 4 月

rMC9RS08KA2 特性 es

8- 位 RS08 中央处理器 (CPU)

• 简化的 S08 指令集,增加了高性能指令

• LDA、 STA 和 CLR 指令 支持短型寻址模

式:$0000 至 $001F 能被单字节指令访问

• DD、 SUB、 INC 和 DEC 指令 支持小型寻

址模式;地址 $0000-$000F 能被具有精简

指令周期的单字节指令访问

• PC 寄存器指令 : SHA 和 SLA

• 等待中断指示

• 通过 D[X] 和 X 寄存器变址寻址

• 通过分页区访问整个存储器

存储器

• 片内 Flash EEPROM

• MC9RS08KA2: 2048 字节

• MC9RS08KA1:1024 字节

•63 字节 RAM

省电模式

• 等待和停止模式

• 在省电模式下,通过实时中断 (RTI)、KBI、ACMP

唤醒

• 在线调试允许设置单断点

封装选择

•6管脚 DFN 封装

• 2 个输入 / 输出脚

• 1 个输入脚

• 1 个输出脚

•8管脚 PDIP 封装

• 4 个输入 / 输出脚

• 1 个输入脚

• 1 个输出脚

•8管脚 SOIC 封装

• 4 个输入 / 输出脚

• 1 个输入脚

• 1 个输出脚

时钟源

• ICS — 可调整的 20 MHz 内部时钟源

• 最大到 10MHz 内部总线工作频率

• 0.2% 可调精度 , 在全温度和电压范围 2%

精度

系统保护

• 计算机正常工作(COP) 复位可以不依赖总线时钟正

常工作

• 低电压检测产生复位或唤醒停止状态

外设

• MTIM — 8 位模定时器

• ACMP — 模拟比较器

• 轨对轨电压工作

• 可选择内部固定的待隙参考电压做比较

• 能在停止模式下工作

• KBI — 键盘中断口

• 6 管脚封装有 3 个 KBI

• 8 管脚封装有 5 个 KBI

开发支持

• 后台调试系统

MC9RS08KA2 数据手册

MC9RS08KA2ZHS

第 1 版

2006 年 4 月

MC9RS08KA2 系列 数据手册

包括 :MC9RS08KA2

MC9RS08KA1

MC9RS08KA2 系列

第 1 版

2006 年 4 月

修订历史

为了提供最新日期的信息,网上文档的版本是最新的。已经印刷的册子也许是早期的版本。为了

获得最新版的信息,可以查阅:

http://freescale.com

下面修订本历史表总结在这个文档中的变化。

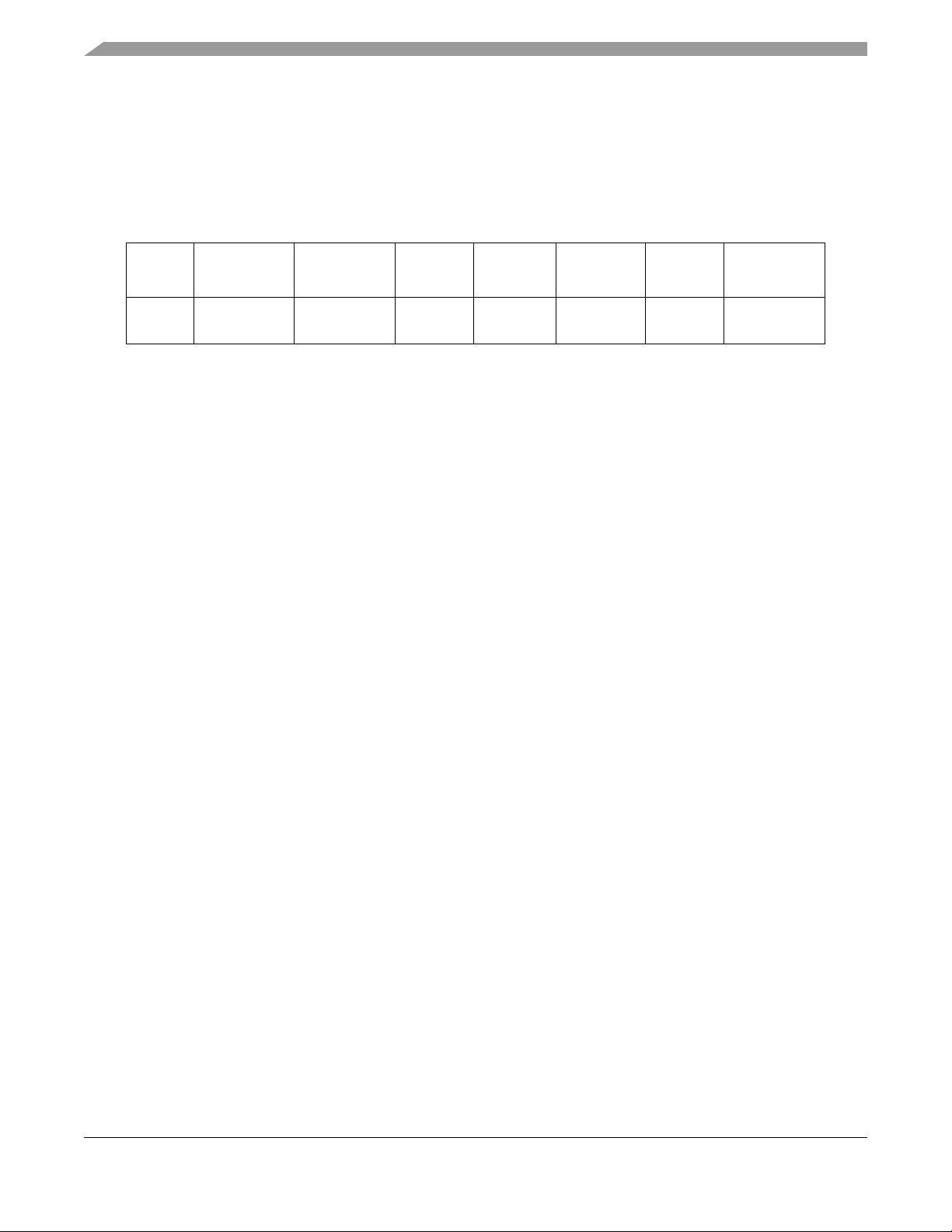

Table 1

修订编号 修订日期 变化描述

1.0 4/2006

第一版

此文档包含新产品开发的信息。飞思卡尔保留改变或停止此产品而不布告的权力。

这个产品结合了获得 SST 许可的 SuperFlash® 技术。

飞思卡尔和飞思卡尔标识是飞思卡尔半导体有限公司的商标。

© 飞思卡尔半导体有限公司, 2006。保留所有权力。

MC9RS08KA2 系列 数据手册 , 第 1 版

# 飞思卡尔半导体公司

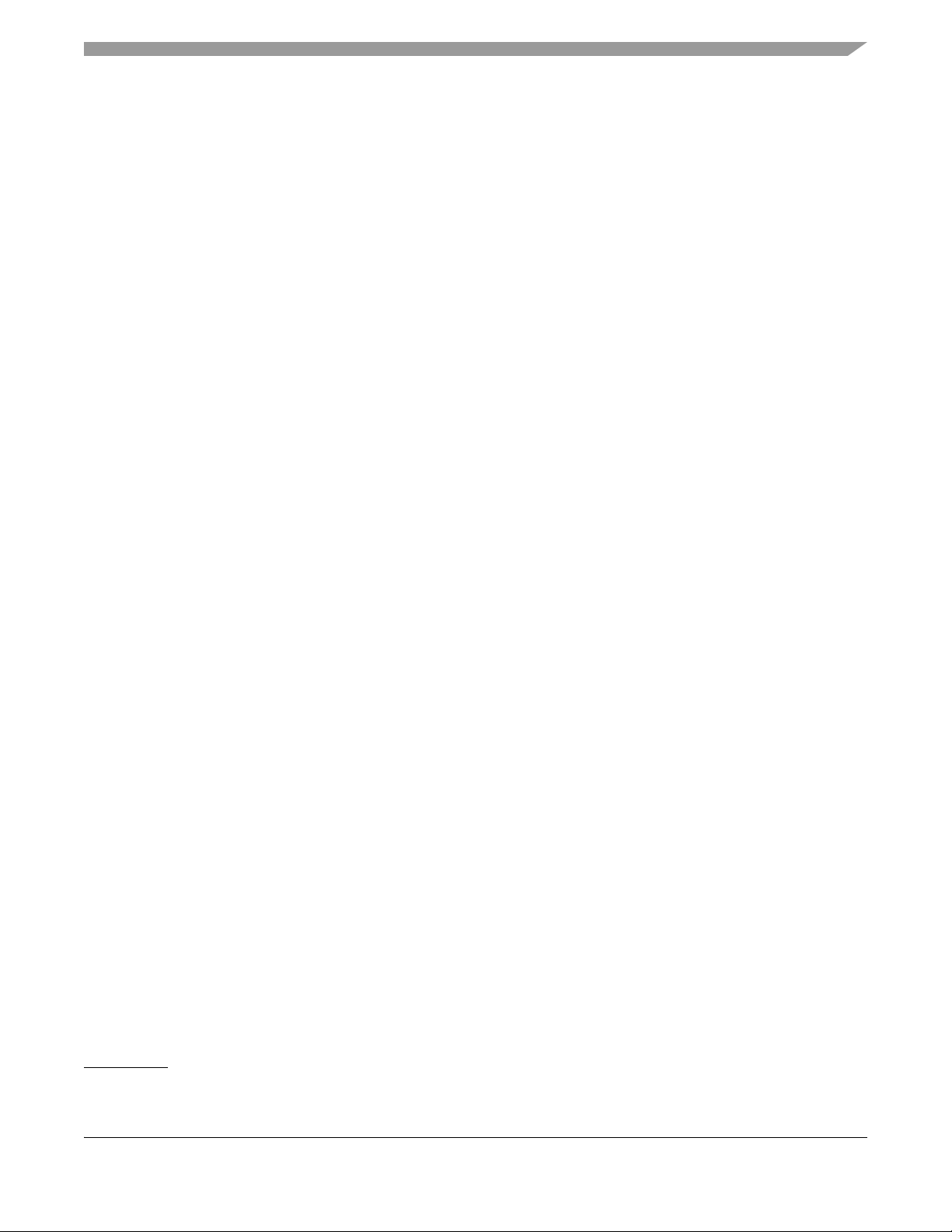

章节号 标题 页

第 1 章 MC9RS08KA2 系列 概述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

第 2 章 管脚和连接. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

第 3 章 工作模式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

第 4 章 存储器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

第 5 章 复位,中断,和通用系统控制 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

第 6 章 并行输入 / 输出控制 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

第 7 章 键盘中断 (RS08KBIV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

第 8 章 中央处理器单元 (RS08CPUV1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

第 9 章 内部时钟源 (RS08ICSV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

第 10 章 模拟比较器 (RS08ACMPV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

第 11 章 模定时器 (RS08MTIMV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

第 12 章 开发支持 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

附录 A 电气特性 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

附录 B 订货信息和机械图 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 7

MC9RS08KA2 系列 数据手册 , 第 1 版

8 飞思卡尔半导体

Running H/F 2

第 1 章

MC9RS08KA2 系列 概述

1.1 概述 .................................................................................................................................15

1.2 MCU 方框图 .....................................................................................................................15

1.3 系统时钟描述 ...................................................................................................................16

第 2 章

管脚和连接

2.1 介绍 .................................................................................................................................17

2.2 管脚分配 ..........................................................................................................................17

2.3 推荐的系统连接 ...............................................................................................................18

2.4 管脚详述 ..........................................................................................................................18

2.4.1 电源 .....................................................................................................................18

2.4.2 PTA2/KBIP2/TCLK/RESET/Vpp .........................................................................19

2.4.3 PTA3/ACMPO/BKGD/MS ...................................................................................19

2.4.4 通用 I/O 和外围端口 ............................................................................................19

第 3 章

工作模式

3.1 介绍 .................................................................................................................................21

3.2 特点 .................................................................................................................................21

3.3 运行模式 ..........................................................................................................................21

3.4 主动后台模式 ...................................................................................................................21

3.5 等待模式 ..........................................................................................................................22

3.6 停止模式 ..........................................................................................................................22

3.6.1 停止模式下主动 BDM 使能 ..................................................................................23

3.6.2 停止模式下低电压检测使能 .................................................................................24

第 4 章

存储器

4.1 存储器映象 .......................................................................................................................25

4.2 无效存储器 .......................................................................................................................26

4.3 变址 / 间接寻址 ................................................................................................................27

4.4 RAM 和寄存器地址和位分配 ............................................................................................27

4.5 RAM .................................................................................................................................29

4.6 Flash ................................................................................................................................29

4.6.1 特点 .....................................................................................................................29

4.6.2 Flash 编程步骤 ....................................................................................................30

4.6.3 Flash 块擦除操作 ................................................................................................30

4.6.4 安全性 .................................................................................................................31

4.7 Flash 寄存器和控制位 ......................................................................................................31

4.7.1 Flash 选项寄存器 (FOPT 和 NVOPT) .................................................................31

4.7.2 Flash 控制寄存器 (FLCR) ...................................................................................32

4.8 页选择寄存器 (PAGESEL) ...............................................................................................32

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体公司 #

Running H/F 4

第 5 章

复位,中断,和通用系统控制

5.1 介绍 .................................................................................................................................35

5.2 特点 .................................................................................................................................35

5.3 MCU 复位 ........................................................................................................................35

5.4 计算机正常工作 (COP) 看门狗 .........................................................................................36

5.5 中断 .................................................................................................................................36

5.6 低电压检测 (LVD) 系统 ....................................................................................................36

5.6.1 上电复位 (POR) 工作 ..........................................................................................37

5.6.2 LVD 复位工作 ......................................................................................................37

5.6.3 LVD 中断工作 ......................................................................................................37

5.7 实时中断 (RTI) .................................................................................................................37

5.8 复位,中断,及系统控制寄存器和控制位 ........................................................................37

5.8.1 系统复位状态寄存器 (SRS) .................................................................................37

5.8.2 系统选项寄存器 (SOPT) .....................................................................................39

5.8.3 系统设备识别寄存器 (SDIDH, SDIDL) ................................................................40

5.8.4 系统实时中断状态和控制寄存器 (SRTISC) .........................................................41

5.8.5 系统电源管理状态和控制 1 寄存器 (SPMSC1) ...................................................42

5.8.6 系统中断等待寄存器 (SIP1) ................................................................................42

第 6 章

并行输入 / 输出控制

6.1 在低功耗模式下管脚状态 .................................................................................................46

6.2 并口 I/O 寄存器 ................................................................................................................46

6.2.1 端口 A 寄存器 .....................................................................................................46

6.3 管脚控制寄存器 ...............................................................................................................47

第 7 章

键盘中断 (RS08KBIV1)

7.1 介绍 .................................................................................................................................49

7.1.1 特点 .....................................................................................................................49

7.1.2 工作模式 .............................................................................................................50

7.1.3 方框图 .................................................................................................................50

7.2 外部信号描述 ...................................................................................................................50

7.3 寄存器定义 .......................................................................................................................50

7.3.1 KBI 状态和控制寄存器 (KBISC) ..........................................................................51

7.3.2 KBI 管脚允许寄存器 (KBIPE) ..............................................................................52

7.3.3 KBI 边沿选择寄存器 (KBIES) ..............................................................................52

7.4 功能描述 ..........................................................................................................................52

7.4.1 仅边沿触发 ..........................................................................................................53

7.4.2 边沿和电平触发 ...................................................................................................53

7.4.3 KBI 上拉 / 下拉设备 .............................................................................................53

7.4.4 KBI 初始化 ..........................................................................................................53

MC9RS08KA2 系列 数据手册 , 第 1 版

# 飞思卡尔半导体公司

Running H/F 2

第 8 章

中央处理器单元 (RS08CPUV1)

8.1 介绍 .................................................................................................................................55

8.2 程序设计器模型和 CPU 寄存器 ........................................................................................55

8.2.1 程序计数器 (PC) .................................................................................................56

8.2.2 影子程序计数器 (SPC) ........................................................................................56

8.2.3 条件代码寄存器 (CCR) .......................................................................................57

8.2.4 变址数据寄存器 (D[X]) ........................................................................................58

8.2.5 变址寄存器 (X) ....................................................................................................58

8.2.6 页选择寄存器 (PAGESEL) ..................................................................................58

8.3 寻址方式 ..........................................................................................................................58

8.3.1 隐含寻址方式 (INH) .............................................................................................58

8.3.2 相对寻址方式 (REL) ............................................................................................58

8.3.3 立即数寻址方式 (IMM) ........................................................................................59

8.3.4 小型寻址方式 (TNY) ............................................................................................59

8.3.5 短型寻址方式 (SRT) ............................................................................................59

8.3.6 直接寻址方式 (DIR) .............................................................................................59

8.3.7 扩展寻址方式 (EXT) ............................................................................................59

8.3.8 变址寻址方式 (IX, 被伪指令执行 ) .......................................................................59

8.4 特殊操作 ..........................................................................................................................60

8.4.1 复位顺序 .............................................................................................................60

8.4.2 中断 .....................................................................................................................60

8.4.3 等待和停止模式 ...................................................................................................60

8.4.4 工作后台模式 ......................................................................................................60

8.5 指令表摘要 .......................................................................................................................61

第 9 章

内部时钟源 (RS08ICSV1)

9.1 介绍 .................................................................................................................................69

9.2 介绍 .................................................................................................................................70

9.2.1 特性 .....................................................................................................................70

9.2.2 工作模式 .............................................................................................................70

9.2.3 方框图 .................................................................................................................70

9.3 外部信号描述 ...................................................................................................................71

9.4 寄存器定义 .......................................................................................................................71

9.4.1 ICS 控制寄存器 1 (ICSC1) ..................................................................................71

9.4.2 ICS 控制寄存器 2 (ICSC2) ..................................................................................72

9.4.3 ICS 调整寄存器 (ICSTRM) ..................................................................................73

9.4.4 ICS 状态和控制 (ICSSC) ....................................................................................73

9.5 功能描述 ..........................................................................................................................73

9.5.1 工作模式 .............................................................................................................73

9.5.2 模式切换 .............................................................................................................75

9.5.3 总线频率分频器 ...................................................................................................75

9.5.4 低功耗位使用 ......................................................................................................75

9.5.5 内部参考时钟 ......................................................................................................75

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体公司 #

Running H/F 4

9.5.6 固定频率时钟 ......................................................................................................75

第 10 章

模拟比较器 (RS08ACMPV1)

10.1 介绍 .................................................................................................................................77

10.1.1 特点 .....................................................................................................................78

10.1.2 工作模式 .............................................................................................................78

10.1.3 方框图 .................................................................................................................78

10.2 外部信号描述 ...................................................................................................................79

10.3 寄存器定义 .......................................................................................................................79

10.3.1 ACMP 状态和控制寄存器 (ACMPSC) .................................................................79

10.4 功能描述 ..........................................................................................................................80

第 11 章

模定时器 (RS08MTIMV1)

11.1 介绍 .................................................................................................................................83

11.1.1 特点 .....................................................................................................................84

11.1.2 工作模式 .............................................................................................................84

11.1.3 方框图 .................................................................................................................84

11.2 外部信号描述 ...................................................................................................................85

11.3 寄存器定义 .......................................................................................................................85

11.3.1 MTIM 状态和控制寄存器 (MTIMSC) ...................................................................86

11.3.2 MTIM 时钟配置寄存器 (MTIMCLK) .....................................................................86

11.3.3 MTIM 计数寄存器 (MTIMCNT) ............................................................................87

11.3.4 MTIM 模寄存器 (MTIMMOD) ..............................................................................88

11.4 功能描述 ..........................................................................................................................88

11.4.1 MTIM 工作例子 ...................................................................................................89

第 12 章

开发支持

12.1 介绍 .................................................................................................................................91

12.2 特点 .................................................................................................................................91

12.3 RS08 后台调试控制器 (BDC) ...........................................................................................92

12.3.1 BKGD 管脚描述 ..................................................................................................92

12.3.2 通讯详述 .............................................................................................................93

12.3.3 同步和串行通讯定时溢出 ....................................................................................95

12.4 BDC 寄存器和控制位 .......................................................................................................95

12.4.1 BDC 状态和控制寄存器 (BDCSCR) ....................................................................96

12.4.2 BDC 断点匹配寄存器 ..........................................................................................97

12.5 RS08 BDC命令 ...............................................................................................................97

附录 A

电气特性

A.1 介绍 ................................................................................................................................101

A.2 最大绝对额定值 ..............................................................................................................101

MC9RS08KA2 系列 数据手册 , 第 1 版

# 飞思卡尔半导体公司

Running H/F 2

A.3 热特性.............................................................................................................................102

A.4 静电 (ESD) 保护特性 ......................................................................................................103

A.5 DC 特性 ..........................................................................................................................103

A.6 电源电流特性 ..................................................................................................................107

A.7 模拟比较器 (ACMP) 电气特性.........................................................................................109

A.8 内部时钟源特性 ..............................................................................................................109

A.9 AC 特性 ..........................................................................................................................109

A.9.1 控制时间 ............................................................................................................110

A.10 Flash 特性.......................................................................................................................110

附录 B

订货信息和机械图

B.1 订货信息 .........................................................................................................................113

B.2 机械图.............................................................................................................................113

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体公司 #

Running H/F 4

MC9RS08KA2 系列 数据手册 , 第 1 版

# 飞思卡尔半导体公司

第 1 章

RS08 CORE

USER FLASH

— 2,048 BYTES

USER RAM

— 63 BYTES

注意 :

(1) 当作为输入时,由软件设置管脚内部上拉 / 下拉。

(2) 当作为复位功能,内部上拉自动使能。 (RSTPE=1).

(3) 在 6 脚封装中这些管脚不存在。

POWER AND

PTA

V

SS

V

DD

INTERNAL CLOCK

SOURCE

BDC

RS08 SYSTEM CONTROL

RTI

CPU

COP

WAKEUP LVD

RESET AND STOP WAKEUP

MODES OF OPERATION

POWER MANAGEMENT

5-BIT KEYBOARD

INTERRUPT MODULE

PTA0/KBIP0/ACMP+

(1)

PTA1/KBIP1/ACMP-

(1)

PTA2/KBIP2/TCLK/RESET/VPP

(1),( 2)

PTA3/ACMPO/BKGD/MS

ANALOG COMPARATOR

MODULE

MODULO TIMER

MODULE

PTA4/KBIP4

(1),(3)

PTA5/KBIP5

(1), (3)

INTERNAL REGULATOR

(

KBI

)

5

TCLK

ACMP-

ACMP+

ACMPO

(

ICS

)

(

ACMP

)

(

MTIM

)

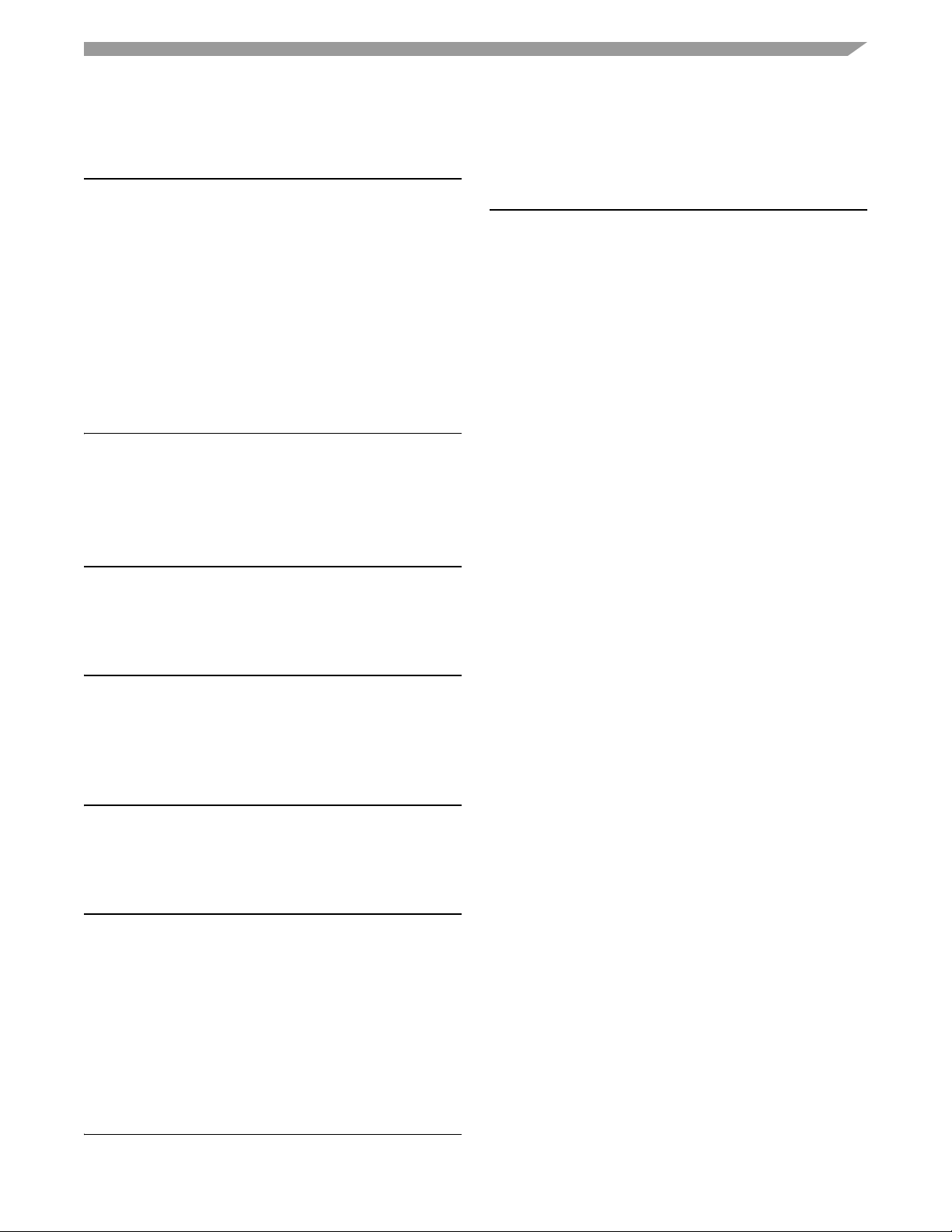

MC9RS08KA2 系列 概述

1.1 概述

MC9RS08KA2 系列 微控制器 (MCU) 是一款极低成本、低管脚数的芯片,可用在家电、玩具和小设备

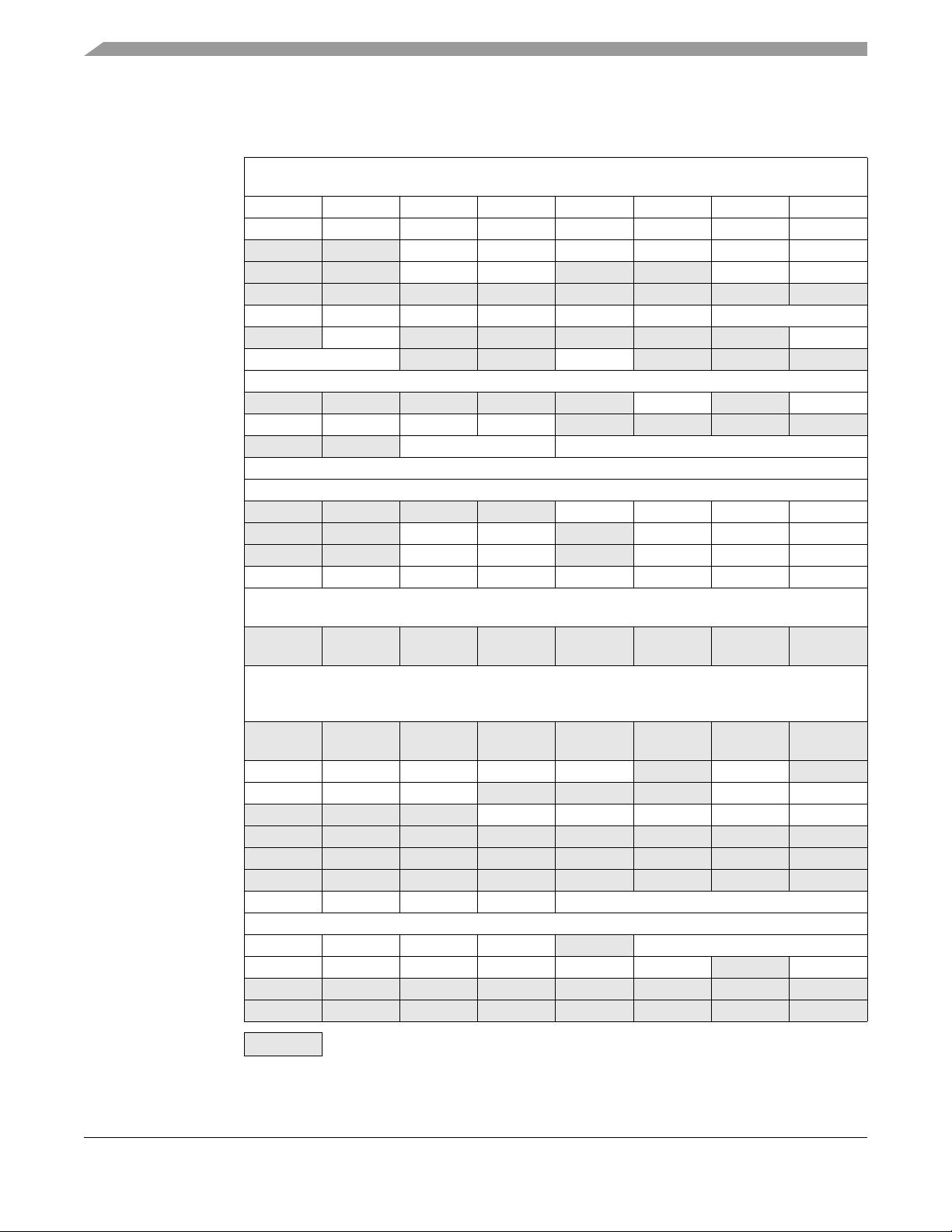

等。这款芯片是由标准的片内模块构成,包括一个非常小的、高效的 RS08 CPU 内核, 63 字节大小的 RAM,

2K 字节大小的 FLASH,一个 8 位模定时器,键盘中断和模拟比较器。这款芯片有 6 管脚和 8 管脚两种封装。

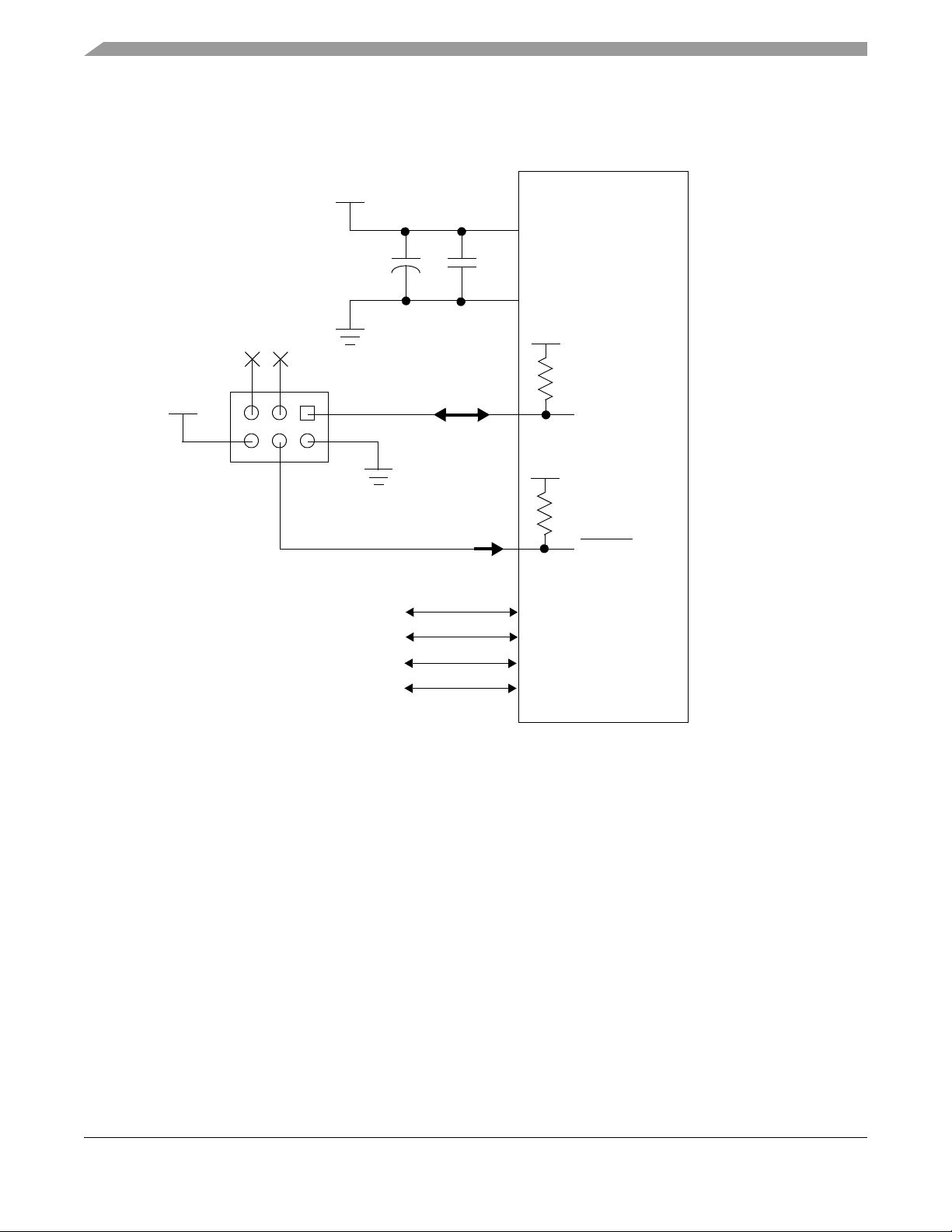

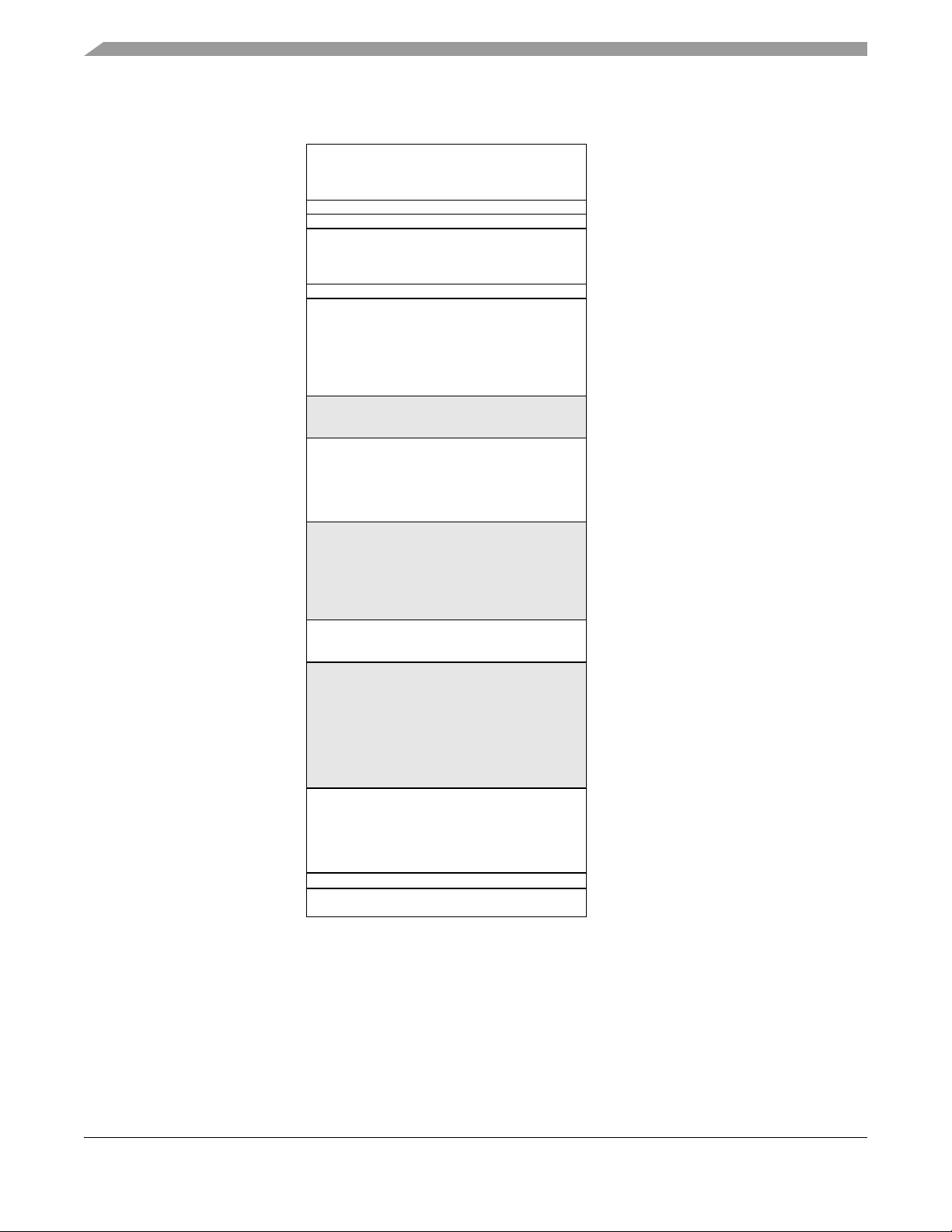

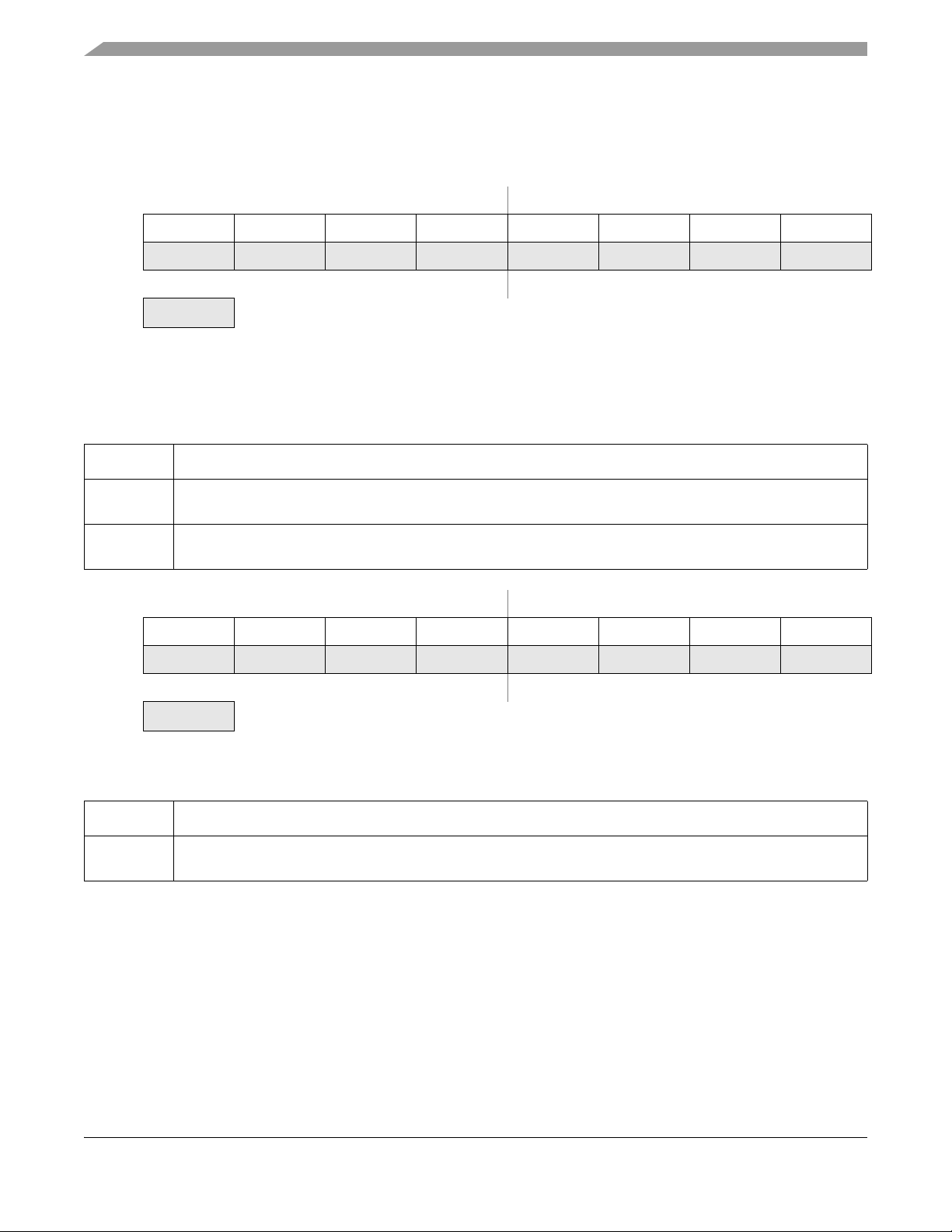

1.2 MCU 方框图

图 1-1 列出了 MC9RS08KA2 系列 MCU 结构。

图 1-1. MC9RS08KA2 系列 方框图

表 1-1 列出了片内模块的功能版本

飞思卡尔半导体 15

MC9RS08KA2 系列 数据手册 , 第 1 版

第 1 章 MC9RS08KA2 系列 概述

MTIM

BDC

FLASH

ICS

BDCBDC

CPU

SYSTEM CONTROL LOGIC

RTI

RTICLKS

1-kHz

÷2

ICSOUT

ICSFFCLK

ICSIRCLK

FIXED CLOCK (XCLK)

BUS CLOCK

TCLK

COP

÷32

模拟比较器 (ACMP) 1

键盘中断 (KBI) 1

模定时器 (MTIM) 1

内部时钟源 (ICS) 1

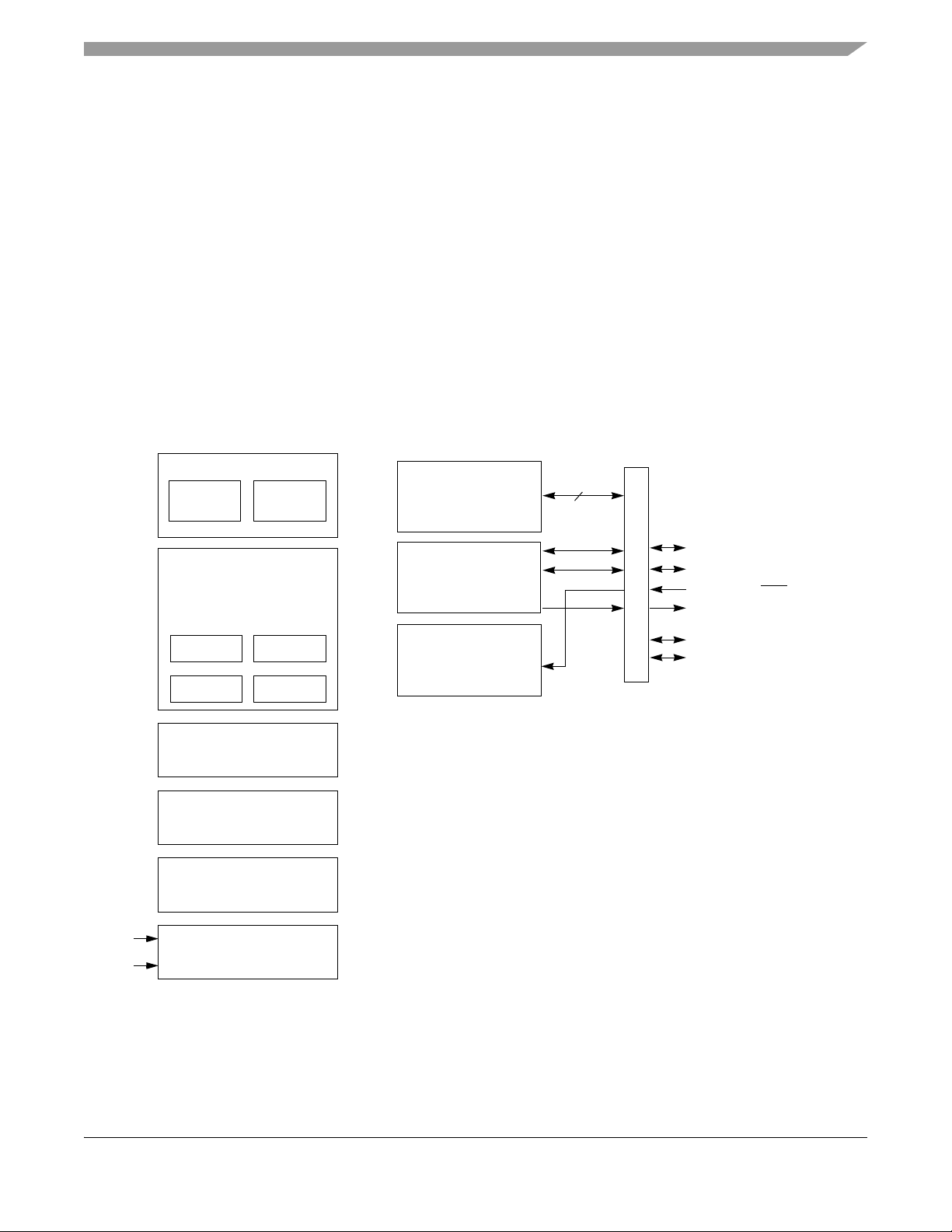

1.3 系统时钟描述

表 1-1. 框图版本

模块 版本

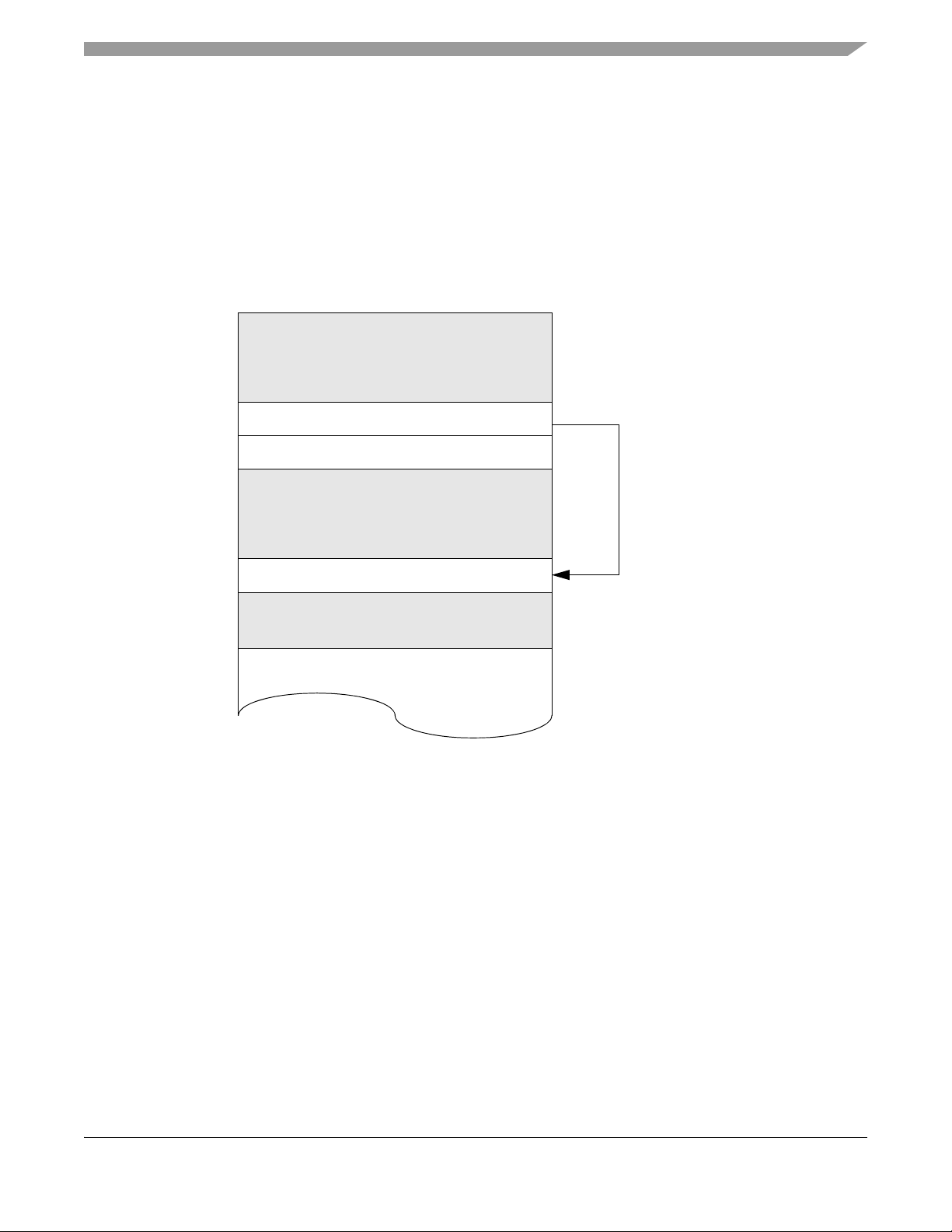

图 1-2. 系统时钟分配图

图 1-2 列出了此 MCU 简单的时钟连接方框图。总线时钟频率是 ICS 输出频率的一半,用于所有的模块。

MC9RS08KA2 系列 数据手册 , 第 1 版

16 飞思卡尔半导体

第 2 章

PTA2/KBIP2/TCLK/RESET/V

PP

PTA3/ACMPO/BKGD/MS

V

DD

V

SS

PTA0/KBIP0/ACMP+

1

2

3

6

5

4

PTA1/KBIP1/ACMP-

1

PTA2/KBIP2/TCLK/RESET/V

PP

PTA3/ACMPO/BKGD/MS

V

DD

V

SS

PTA4/KBIP4

PTA1/KBIP1/ACMP-

PTA0/KBIP0/ACMP+

PTA5/KBIP5

2

3

4

8

7

6

5

PTA2/KBIP2/TCLK/RESET/V

PP

PTA3/ACMPO/BKGD/MS

V

DD

V

SS

PTA4/KBIP4

PTA1/KBIP1/ACMP–

PTA0/KBIP0/ACMP+

PTA5/KBIP5

1

2

3

4

8

7

6

5

管脚和连接

2.1 介绍

本章描述了所有连接到封装管脚的信号。它包括管脚接线图、信号特性表和一个详细的信号讨论。

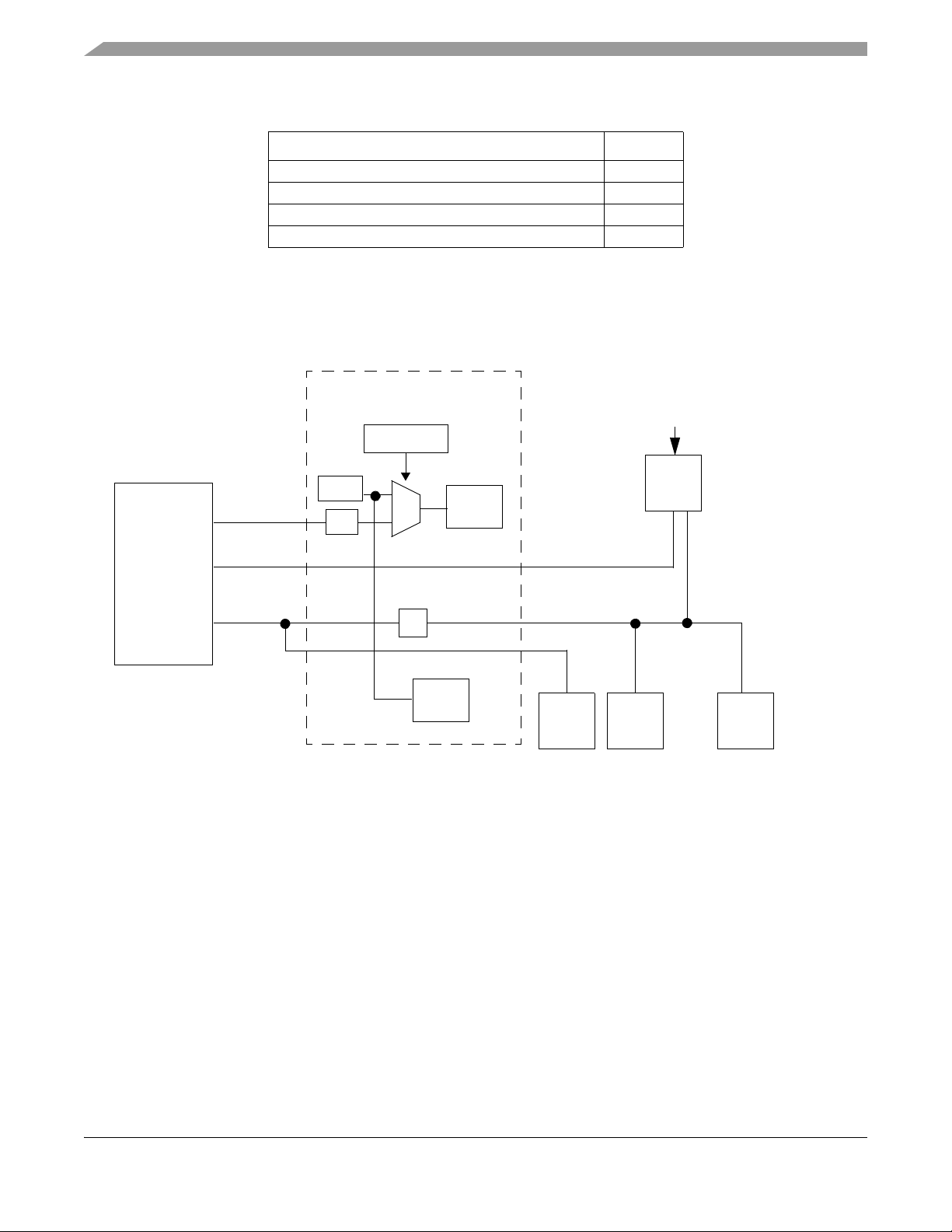

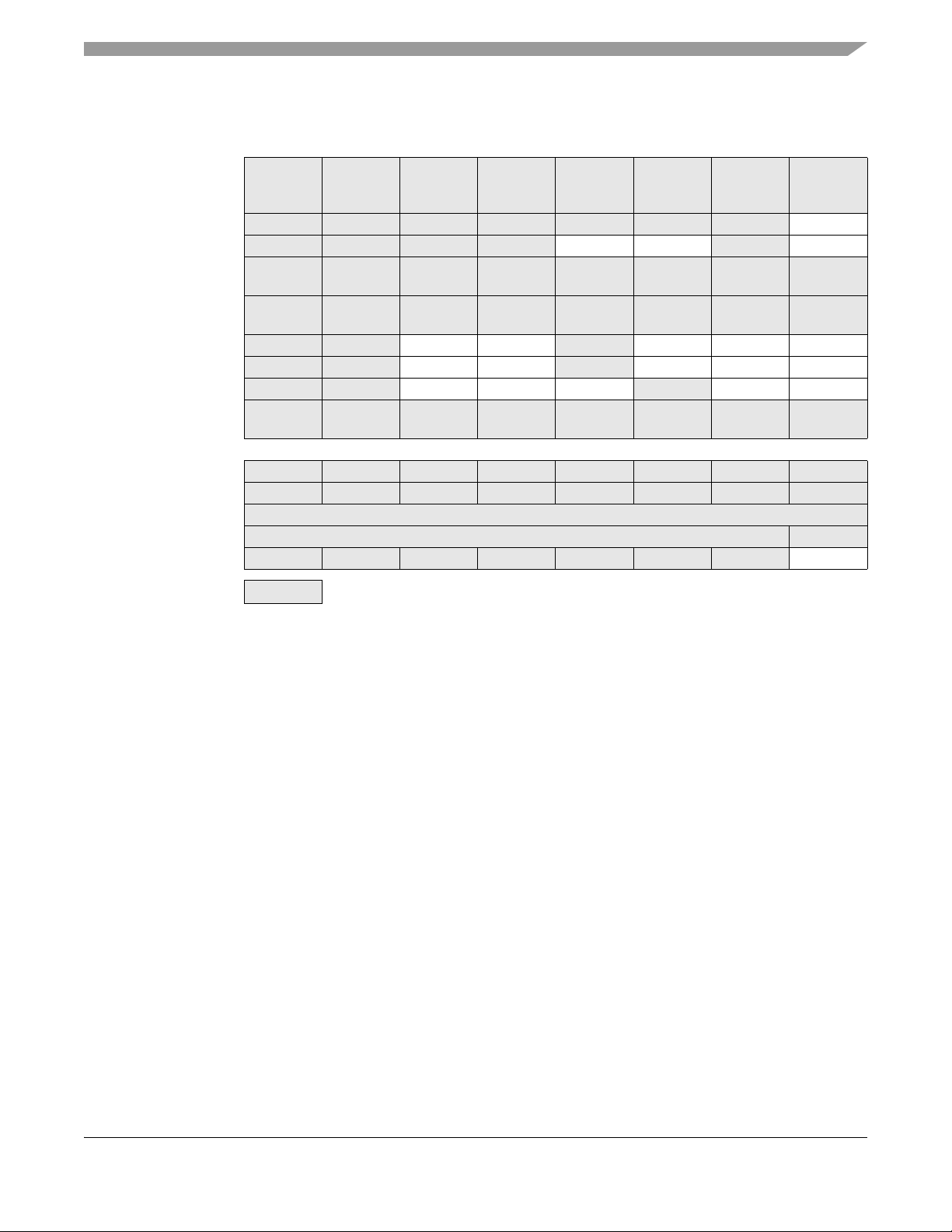

2.2 管脚分配

图 2-1 和图 2-3 列出了所有的 MC9RS08KA2 系列封装的管脚分配情况。

图 2-1. MC9RS08KA2 系列 in 6-Pin DFN

飞思卡尔半导体 17

图 2-2. MC9RS08KA2 系列 in 8-Pin PDIP

图 2-3. MC9RS08KA2 系列 in 8-Pin Narrow Body SOIC

MC9RS08KA2 系列 数据手册 , 第 1 版

第 2 章 管脚和连接

C

BUK

10 μF

C

BY

0.1 μF

V

DD

V

DD

V

DD

V

SS

BKGD/MS

RESET

/V

PP

PTA0/KBIP0/ACMP+

PTA1/KBIP1/ACMP-

MC9RS08KA2

BACKGROUND

HEADER

PTA4/KBIP4 (Note 1)

PTA5/KBIP5 (Note 1)

注意

1

6 引脚封装无此引脚。

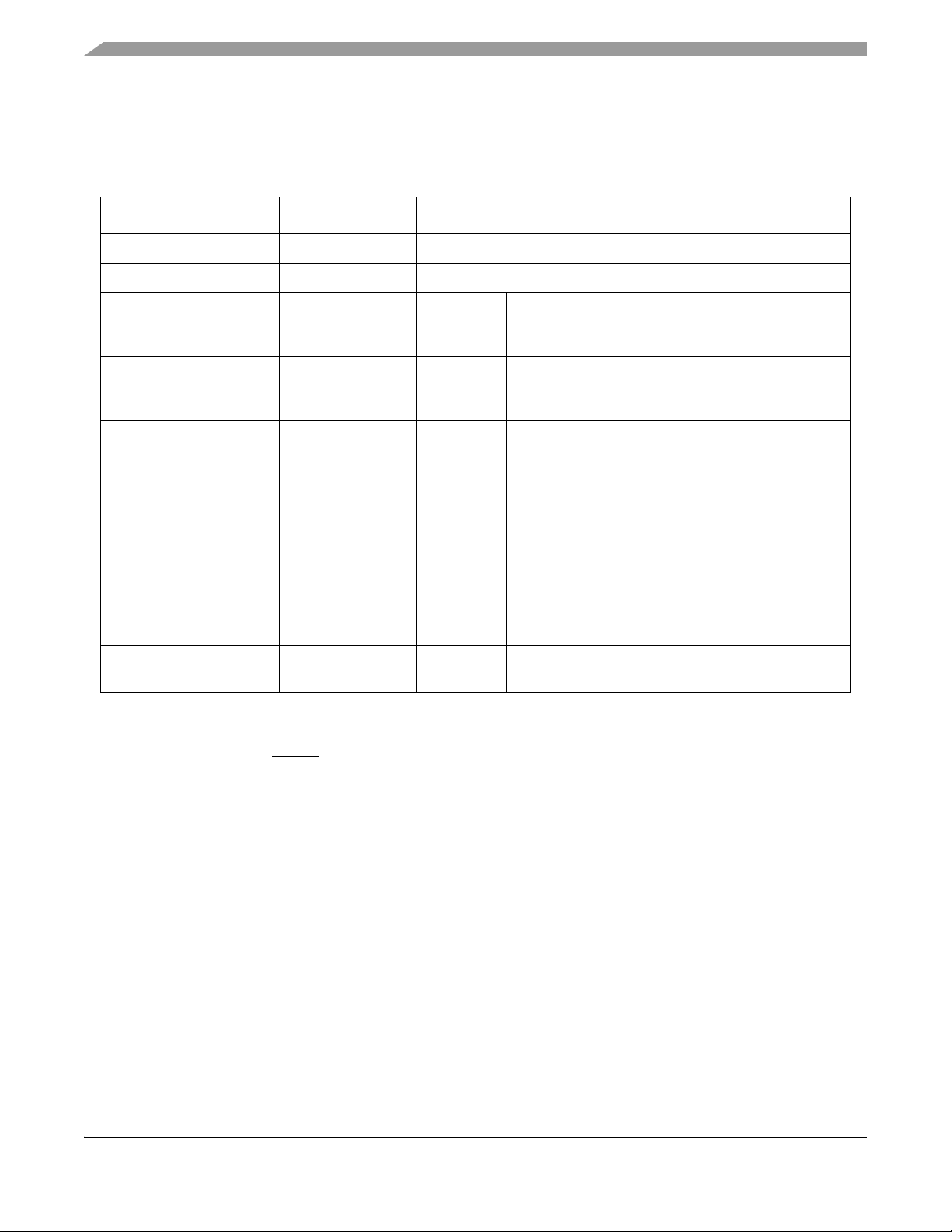

2.3 推荐的系统连接

图 2-4 列出了后台调试和 FLASH 编程的参考连接。

2.4 管脚详述

2.4.1 电源

电压调节器提供一个可调的更低电压源给 CPU 和 MCU 的其它内部电路。

系统提供大充电电荷;以及一个旁路电容,如一个 0.1 μF 陶瓷电容,放在离 MCU 电源管脚最近的地方,用于

抑止高频噪音。

18 飞思卡尔半导体

本节提供了系统连接的详细描述。

V

和 VSS 是 MCU 基本的电源管脚。这个电压源给所有的 I/O 电路和内部参考电压调节器提供电源。内部

DD

图 2-4. 系统连接方框图参考

典型地,应用系统有两个独立的电容连接在电源管脚:一个大的电解电容,如一个 10 μF 旦电容,给整个

MC9RS08KA2 系列 数据手册 , 第 1 版

第 2 章 管脚和连接

2.4.2 PTA2/KBIP2/TCLK/RESET/Vpp

上电复位 (POR) 进入用户模式后, PTA2/KBIP2/TCLK/RESET/VPP 管脚默认为输入管脚, PT A2。将

SOPT 寄存器的 RSTPE 置位,此管脚作为复位输入脚。配置为复位脚后,此管脚一直为复位脚,直到下次上

电复位。当此管脚被拉低,复位脚被一个外部源复位 MCU。当被设置为复位脚 (RSTPE = 1),内部上拉功能

自动使能。

当执行 FLASH 编程或擦除时,此管脚需要一个外部 V

特性 ”) 。不管此管脚为何功能, V

为了避免 FLASH 过重负荷,外部 V

接线总是连接到内部 FLASH模块。当没有作为 FLASH 编程或擦除时,

PP

电压必须被切断,并且高于 V

PP

电压 ( 典型值 12 V, 参见 Section A.10, 褾 LASH

PP

的电压必须避免

DD

。

注意

此管脚没有包含一个钳压二极管连接到 VDD ,当没有执行 FLASH 编程或擦除时

这个管脚的电压不能高于 V

DD

。

2.4.3 PTA3/ACMPO/BKGD/MS

作为只输出的 PTA3 管脚的功能可以设置为后台调试或模拟比较输出。在复位期间,这个管脚功能模式可

选择。复位后,这个管脚功能立即作为后台调试模式并且被用于后台调试通讯。在后台调试功能期间,这管脚

有一个内部上拉设备使能。作为一个只输出端口, SOPT 寄存器中的 BKGDPE 位必须被清零。

假如没有任何东西连接到这个管脚, MCU 在复位的上升沿期间进入到正常工作模式。假如有一个调试系

统连接到 6 管脚的标准后台调试头,在上电复位期间将 BKGD/MS 一直拉低,强迫 MCU 进入后台调试模式。

BKGD 管脚主要用于后台调试控制器 (BDC)通讯,此通讯使用目标 MCU 的 BDC 时钟的 16 个时钟周

期的通讯协议。目标 MCU 的 BDC 时钟等于总线时钟。因此,大电容连接到 BKGD/MS 管脚将会干扰后台串

行通讯。

尽管 BKGD管脚是个假的开漏极管脚,后台调试通讯协议提供了暂时的、积极驱动的高速脉冲确保快速

上升时间。来自电线的小电容和内部上拉设备在 BKGD 管脚的上升和下降沿几乎不起作用。

2.4.4 通用 I/O 和外围端口

剩下的管脚都具有通用 I/O和芯片外设功能,如定时器和模拟比较器。上电复位后,所有这些管脚立即被

设置为高阻态通用输入且内部上拉 / 下拉设备禁止。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 19

第 2 章 管脚和连接

注意

为了避免外部漏电流进入悬浮的输入管脚,应用例程中的复位初始化程序应该使能

芯片的上拉 / 下拉设备或将管脚设置为输出。

表 2-1. 管脚共享参数

—

1

通用输入 / 输出 (GPIO)

KBIP0

ACMP+

键盘中断 ( 只停止 / 等待唤醒 )

模拟比较输入

通用输入 / 输出 (GPIO)

KBIP1

ACMP-

4

PTA2

KBIP2

TCLK

RESET

V

PP

4

PTA3

ACMPO

BKGD

MS

键盘中断 ( 只停止 / 等待唤醒)

模拟比较输入

通用输入

键盘中断 ( 只停止 / 等待唤醒 )

模定时器时钟源

复位

V

PP

通用输出

模拟比较器输出

后台调试数据

模式选择

通用输入 / 输出 (GPIO)

KBIP4

键盘中断 ( 只停止 / 等待唤醒)

通用输入 / 输出 (GPIO)

KBIP5

键盘中断 ( 只停止 / 等待唤醒 )

管脚名称 方向

V

DD

V

SS

——

——

上拉 / 下拉

PTA0 I/O SWC PTA0

PTA1 I/O SWC PTA1

PTA2 I SWC

PTA3 I/O

5

PTA4

5

PTA5

1

SWC 是软件控制上拉 / 下拉电阻器,这个寄存器与各自端口有关。

2

任选功能首先从最低优先级被列出。例如,在 PTA0 管脚 GPIO 是最低优先级功能。 ACMP+ 是最高优先级功能。

3

当配置为 PTA3 功能是只输出。

4

当 PTA2 或 PTA3 配置为 RESET 或 BKGD/MS,各自的,上拉使能。当接上 V

5

在 6 管脚封装中这个管脚没有。使能上拉或下拉设备可以确保防止外部漏电流进入输入管脚。

3

I/O SWC PTA4

I/O SWC PTA5

可选的功能

电源

,上拉 / 下拉自动禁止。

PP

2

地

MC9RS08KA2 系列 数据手册 , 第 1 版

20 飞思卡尔半导体

第 3 章

工作模式

3.1 介绍

本章介绍了 MC9RS08KA2 系列 的工作模式 , 也详细介绍了进入每种模式、退出每种模式和每种模式的功

能。

3.2 特点

• 主动后台模式

• 等待模式 :

• CPU 关闭降低功耗

• 系统时钟继续运行

• 全电压调节被保持

• 停止模式 :

• 系统时钟被停止;电压调节器备用

• 所有内部电路保持供电用于快速恢复

3.3 运行模式

这是 MC9RS08KA2 系列正常工作模式。在复位的上升沿,当 BKGD/MS 管脚是高电平时选择这种模式。

在这种模式,CPU 执行启始地址为 $3FFD 的内部存储器开始执行代码。操作数位于 $3FFE–$3FFF 的一条

JMP 指令 ( 操作码 $BC) 必须被编程为正确的复位操作进入用户应用层。这个操作数定义在用户程序开始的地

点 , 取代 HC08/S08 系列中用于取出程序的向量。为确保 JMP 指令重新定位程序指针到正确的用户程序的起

始地址,需要用户程序负责完成。

3.4 主动后台模式

主动后台模式功能通过在 RS08 核中的后台调试控制器 (BDC) 管理。在软件调试期间 BDC 提供 分析

MCU 工作的方法。

主动后台模式通过四种方法中的任何一种可进入:

• 在上电复位 (POR)期间 BKGD/MS 管脚被拉低或发出了一条后台调试强迫复位 (BDC_RESET) 命

令

• 当 BKGD 管脚收到后台调试命令

• 当 BGND 指令被执行

• 当遇到一个 BDC 断点

进入知道后台模式后, CPU 保持悬浮状态等待串行后台命令,而不会从用户应用程序执行指令。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 21

第 3 章 工作模式

后台命令有 2 种类型:

• 无指令命令,被定义为在用户程序运行时能被发出的命令, MCU 在运行状态时能够通过 BKGD 管脚

发出。当 MCU 在主动后台模式时无指令命令也可以执行。无指令命令包括:

• 存储器存取命令

• 存储器存取与状态命令

• BACKGROUND 命令

• 主动后台命令,仅当 MCU 在主动后台模式时能被执行,包括:

• 读或写 CPU 寄存器

• 在某个时间跟踪一条用户程序指令

• 离开主动后台模式返回到用户应用程序 (GO)

主动后台模式用于 MCU 在进入运行模式之前第一时间将用户应用代码编程到 Flash 程序存储器中。当

MC9RS08KA2 系列 从飞思卡尔半导体工厂运出, Flash 程序存储器通常被擦除,因此在运行模式没有程序可

以运行,除非 Flash 程序存储器被编程。在预先编程后,主动后台模式也可以擦除和重新编程 Flash 存储器。

关于主动后台模式附加的信息,请参考此数据手册开发的支持章节。

3.5 等待模式

通过执行 WAIT 指令进入等待模式。在执行 WAIT 指令后,没有时钟提供给 CPU,进入低功耗状态。程

序计数器 (PC) 停止在 WAIT 被执行的位置。 当一个中断需求产生:

1. MCU 退出等待模式恢复工作。

2. PC 被加 1 并且取出下条指令执行。

由于没有向量被取出,用户程序需要查明唤醒 MCU 的相关中断源。

当 MCU 在等待模式,不是所有的后台调试命令都能够被使用,仅 BACKGROUND 命令和 存储器存取和

状态命令可用。存储器状态存取命令不允许存储器存取,但当 MCU 在停止或等待模式时可以报告一个错误的

标志。 BACKGROUND 命令可以从等待模式下唤醒 MCU 进入主动后台模式。

表 3-1 总结了 MCU 在等待模式下的状态。

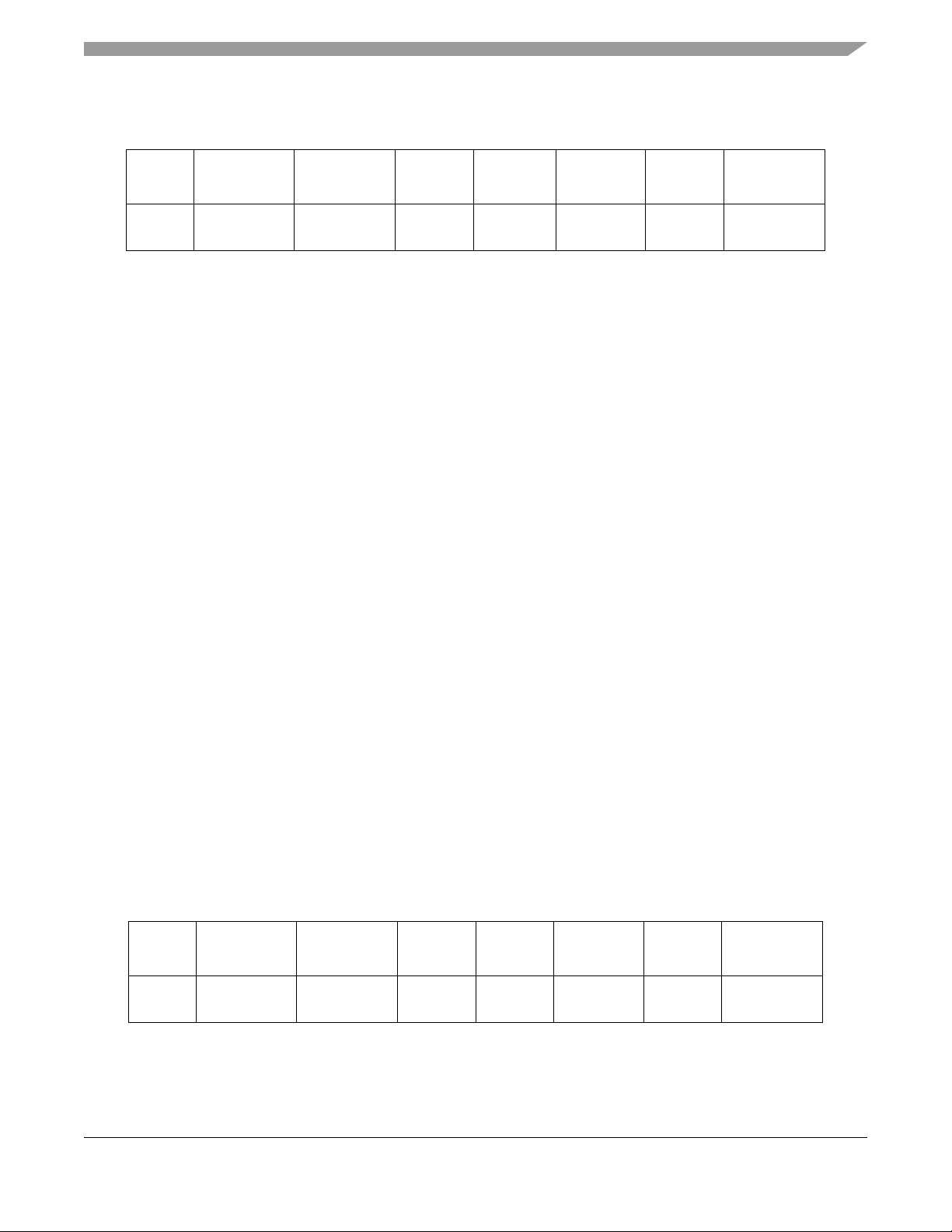

表 3-1. 等待模式状态

Mode CPU

Wait Standby Optionally on On Optionally

Digital

Peripherals

ICS ACMP Regulator I/O Pins RTI

On States held Optionally on

on

3.6 停止模式

当系统选型寄存器的 STOPE 位被置位,执行 STOP 指令进入停止模式。在停止模式,所有 CPU 和模块

的内部时钟被停止。假如 STOPE位没有被置位,当 CPU 执行 STOP 指令时, MCU 不会进入停止模式,并

且产生一个非法指令强迫复位。

MC9RS08KA2 系列 数据手册 , 第 1 版

22 飞思卡尔半导体

表 3-2 总结了 MCU 在停止模式下的状态。

第 3 章 工作模式

表 3-2. 停止模式状态

Mode CPU

Stop Standby Standby Optionally onOptionally onStandby States held Optionally on

1

在停止模式,内部时钟源需要 IREFSTEN = 1 并且 LVDE 和 LVDSE 必须被置位才能允许工作。

2

假如需要待隙参考,进入停止模式前, SPMSC1 中的 LVDE 和 LVDSE 位必须被置位。

3

假如在 ICS 模块中的 32 kHz 可调时钟被选择用于作为 RTI 的时钟源,进入停止模式前,在 SPMSC1 中的 LVDE

和 LVDSE 位必须被置位。

Digital

Peripherals

ICS

1

ACMP

2

Regulator I/O Pins RTI

3

进入停止模式后 MCU 内的所有时钟停止。当 IREFSTEN 位被清除内部时钟源默认关闭,电压调整器进

入旁路状态。所有内部寄存器和逻辑单元的状态保持不变,如 RAM 内容。 I/O 管脚状态被钳住。

任何异步中断或实时中断,都可以退出 STOP模式。异步中断包括键盘中断,低电压检测中断或模拟比

较中断。

假如是通过复位管脚退出停止模式, MCU 将复位且程序从 $3FFD 地址开始运行。假如是通过异步中断

或实时中断退出停止模式,停止指令地址的下条指令被执行。用户程序需要查明唤醒 CPU 的相关中断源。

一个用于实时中断 (RTI)的独立的时钟源 (

≈1kHz)允许从停止模式唤醒 CPU 而不需要外部器件。当

RTIS = 000, 实时中断功能和 1 kHz 时钟源被禁止。当 1 kHz 时钟源被禁止时功耗更低,但在这种情况下,实

时中断不能将 MCU 从停止模式下唤醒。

在内部时钟源模块内可调的 32-kHz 时钟源可以用于实时中断,允许不需要外部器件就可以从停止模式唤

醒 MCU。 IREFSTEN 位置位, 32-kHz 参考时钟使能。为了在停止模式下内部时钟源能运行,进入停止模式

前, SPMSC1 寄存器中的 LVDE 和 LVDSE 位必须都置位。

3.6.1 停止模式下主动 BDM 使能

假如 BDCSCR 寄存器中的 ENBDM 位被置位,从运行模式进入后台调试模式是允许的。本数据手册的开

发支持章有这个寄存器的描述。当 MCU 进入停止模式,后台调试逻辑的系统时钟保持活动的,因此后台调试

通讯依然可能。另外,电压调整器不会进入低功耗旁路状态;它维持全部的内部调节。

在停止模式下大部分后台调试命令不能用。存储器状态存取命令不允许存储器存取。但当 MCU 在停止或

等待模式时可以报告一个错误的标志。 假如 ENBDM 位被置位, BACKGROUND 命令可以从停止模式下唤醒

MCU 进入主动后台模式。进入后台调试模式后,所有的后台命令可用。

表 3-3 总结了当进入后台模式使能时在停止模式下 MCU 的状态

表 3-3. BDM 使能停止模式状态

Mode CPU

Stop Standby Standby On Optionally

Digital

Peripherals

MC9RS08KA2 系列 数据手册 , 第 1 版

ICS ACMP Regulator I/O Pins RTI

On States held Optionally on

on

飞思卡尔半导体 23

第 3 章 工作模式

3.6.2 停止模式下低电压检测使能

当电源下降低于 LVD 电压时, LVD 系统能够产生中断或复位。假如在停止模式下 LVD 使能 ( 在

SPMSC1 寄存器中的 LVDE 和 LVDSE 位被置位 ), CPU 执行 STOP 指令时,电压调整器保持活动状态。

表 3-4 总结了当允许 LVD 产生复位时停止模式下 MCU 的状态。

表 3-4. LVD 使能停止模式状态

Mode CPU

Stop Standby Standby Optionally onOptionally

Digital

Peripherals

ICS ACMP Regulator I/O Pins RTI

on

On States held Optionally on

MC9RS08KA2 系列 数据手册 , 第 1 版

24 飞思卡尔半导体

第 4 章

存储器

4.1 存储器映象

MCU 的存储器图被划分成以下块:

• 快速存取 RAM 用于小型指令和短型指令 ($0000–$000E

• 间接数据存储 D[X] ($000E)

• 用于 D[X] 的变址寄存器 X ($000F)

• 经常使用的外设寄存器 ($0010–$001E)

• 页寄存器 ($001F)

• RAM ($0020–$004F)

• 分页窗口 ($00C0–$00FF)

• 其它外设寄存器 ($0200–$023F)

• 非易式性存储器 ($3800–$3FFF)

1

)

1. 当变址寄存器 X 内容是 $0E 时, $000E 的物理 RAM 能通过 D[X] 寄存器访问。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 25

D[X]

REGISTER X

FAST ACCESS RAM

14 BYTES

FREQUENTLY USED REGISTERS

HIGH PAGE REGISTERS

$000E

$000F

$0000

$000D

$0010

$001E

$0200

$023F

RAM

48 BYTES

$0020

$004F

PAGING WINDOW

$00C0

$00FF

FLASH

$3800

$3FFB

2044 BYTES

UNIMPLEMENTED

UNIMPLEMENTED

NVOPT

$3FFC

$3FFD

$3FFF

FLASH

PAGESEL

$001F

UNIMPLEMENTED

PAGE REGISTER

$00

$08 (reset value)

$E0

CONTENT

第 4 章 存储器

图 4-1. MC9RS08KA2 存储器映象

4.2 无效存储器

在一个无效存储器地址试图存取数据或指令将会导致复位。

26 飞思卡尔半导体

MC9RS08KA2 系列 数据手册 , 第 1 版

第 4 章 存储器

D[X]

Register X

Content of this location can be accessed via D[X]

$000E

$000F

$00FF

Address indicated in

$0100

寄存器 X 能表示位于

$0000–$00FF

Register X

$0000

间的任何位置

4.3 变址 / 间接寻址

寄存器 D[X]和寄存器 X 一起实现间接数据存取。寄存器 D[X] 被映射地址 $000E. 寄存器 X 位于地址

$000F. 当寄存器 D[X] 被存取时这个 8 位寄存器 X 包含了被使用的地址。 复位后寄存器 X 被清零。通过编程寄

存器 X,位于第一页 ($0000–$00FF) 内的任何位置都能够通过 D[X] 被读 / 写。图 4-2 显示了 D[X] 和寄存器 X

的相对关系。例如,当寄存器 X 被写给定值, HC08/S08 语句 lda ,x 相当于 RS08 的语句 lda D[X] 。

$000E 物理位置在 RAM 区,当寄存器 X 的值是 $0E 时,通过 D[X] 访问这个地址获得 $000 E RAM 的内

容。 $000F 物理位置是寄存器 X 自身。通过 D[X] 读取这个地址获得寄存器 X 的内容;写这个地址修改寄存器

X。

4.4 RAM 和寄存器地址和位分配

码被编码为一个单字节。

式指令,操作数与操作码被编码为一个单字节。

飞思卡尔半导体 27

图 4-2. 间接寻址寄存器

使用小型、短型、直接寻址方式指令能访问直接存取 RAM 空间。对于小型寻址方式指令,操作数与操作

为了完成更快载入、存储和清除工作,频繁使用的寄存器可以使用短型寻址方式指令。对于短型寻址方

MC9RS08KA2 系列 数据手册 , 第 1 版

第 4 章 存储器

表 4-1. 寄存器总结

地址 寄存器名称

$0000–

$000D

$000E D[X]

1

位 7654321位 0

Fast Access RAM

Bit 7654321Bit 0

$000F X Bit 7654321Bit 0

$0010 PTAD

0 0 PTAD5 PTAD4 PTAD3 PTAD2 PTAD1 PTAD0

$0011 PTADD 0 0 PTADD5 PTADD4 0 0 PTADD1 PTADD0

$0012 Unimplemented

— — — — — — — —

$0013 ACMPSC ACME ACBGS ACF ACIE ACO ACOPE ACMOD

$0014 ICSC1

$0015 ICSC2 BDIV

0CLKS0 0 0 0 0IREFSTEN

0 0LP0 0 0

$0016 ICSTRM TRIM

$0017 ICSSC

$0018 MTIMSC TOF TOIE TRST TSTP

$0019 MTIMCLK

0 0 0 0 0CLKST0FTRIM

0 0 0 0

0 0CLKS PS

$001A MTIMCNT COUNT

$001B MTIMMOD MOD

$001C KBISC

0 0 0 0 KBF KBACK KBIE KBIMOD

$001D KBIPE — — KBIPE5 KBIPE4 — KBIPE2 KBIPE1 KBIPE0

$001E KBIES

— — KBEDG5 KBEDG4 — KBEDG2 KBEDG1 KBEDG0

$001F PAGESEL AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6

$0020–

$004F

$0050–

$00BF

Unimplemented

— — — — — — — —

RAM

$00C0

–

Paging Window

$00FF

$0100–

$01FF

$0200 SRS POR PIN COP ILOP ILAD

$0201 SOPT COPE COPT STOPE

$0202 SIP1

$0203 Unimplemented

$0204 Reserved

$0205 Unimplemented

Unimplemented

— — — — — — — —

0LVD0

0 0 0 BKGDPE RSTPE

— — — KBI ACMP MTIM RTI LVD

— — — — — — — —

— — — — — — — —

— — — — — — — —

$0206 SDIDH REV3 REV2 REV1 REV0 ID

$0207 SDIDL ID

$0208 SR TISC RTIF RTIACK RTICLKS RTIE

$0209 SPMSC1 LVDF LVDACK LVDIE LVDRE LVDSE LVDE

$020A Reserved

$020B Reserved

— — — — — — — —

— — — — — — — —

0RTIS

0BGBE

= Unimplemented or Reserved

MC9RS08KA2 系列 数据手册 , 第 1 版

28 飞思卡尔半导体

表 4-1. 寄存器总结 (continued)

第 4 章 存储器

地址 寄存器名称

$020C

–

$020F

$0210 FOPT 0 0 0 0 0 0 0 SECD

$0211 FLCR

$0212–

$0213

$0214–

$021F

$0220 PTAPE 0 0 PTAPE5 PTAPE4 0 PTAPE2 PTAPE1 PTAPE0

$0221 PTAPUD

$0222 PTASE 0 0 PTASE5 PTASE4 PTASE3 0 PTASE1 PTASE0

$0223–

$023F

$3FF8 Reserved — — — — — — — —

$3FF9 Reserved

$3FFA2Reserved Reserved for Room Temperature ICS Trim

$3FFB

$3FFC NVOPT

1

2

Unimplemented

Reserved

Unimplemented

Unimplemented

2

Reserved Reserved FTRIM

当变址寄存器 X 内容是 $0E,在 $000E 的物理 RAM 能通过 D[X] 寄存器访问。

假如使用的 MCU 未调整, $3FFA 和 $3FFB 可以被应用程序载入。

位 7654321位 0

— — — — — — — —

0 0 0 0 HVEN MASS 0PGM

— — — — — — — —

—

—

0 0 PTAPUD5 PTAPUD4 0 PTAPUD2 PTAPUD1 PTAPUD0

— — — — — — — —

— — — — — — — —

0 0 0 0 0 0 0 SECD

—

—

= Unimplemented or Reserved

—

—

—

—

—

—

—

—

—

—

—

—

4.5 RAM

此芯片包含两个区域的静态 RAM。从 $0000 到 $000D 的区域可以通过更高效的小型寻址方式指令和短

型寻址方式指令直接访问。当寄存器 X 值是 $0E 时,可以通过 D[X] 寄存器访问位于 $000E 的 RAM 值。或当

PAGESEL 寄存器值是 $00 时通过位于 $00CE 的分页窗口访问。第二个 RAM 区域从 $0020 到 $0040,它能

通过直接寻址方式指令访问。

当 MCU 在低功耗等待和停止模式时 RAM 保持数据。当给 RAM 供电的电压没有下降到低于维持 RAM 所

需的最小值时,任何复位都不会影响 RAM 数据 。

4.6 Flash

Flash 存储器主要用于存储程序。 在编译成功后,在线编程允许应用程序下载到 Flash 存储器中。通过单

线后台调试接口编程到整个空间是可以的。由于此芯片没有包括在线电压泵,在编程和擦除工作时需要外部

V

PP 。

4.6.1 特点

Flash 存储器特点包括:

• 在典型电压和温度下超过 1000 次编程 / 擦除。

• Flash 安全特性

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 29

第 4 章 存储器

4.6.2 Flash 编程步骤

基于行编程 Flash 存储器。一行由 64 个连续字节组成,起始地址为 $3X00, $3X40, $3X80, 或 $3XC0。

使用下列步骤编程一行 Flash存储器:

1. 加外部电压 V

PP

。

2. PGM 位置位。这用于配置编程的存储器和允许锁住编程的地址和数据。

3. 写任何数据到任何 Flash 位置,经过高页存取窗口,内部的行地址范围被编程 ( 数据写操作之前,

PAGESEL 寄存器必须配置正确去映射高页存取窗口到相关的 Flash 行 )。

4. 延时 t

nvs

。

5. HVEN 位置位。

6. 延时 t

pgs

。

7. 写数据到被编程的 Flash 空间。

8. 延时 t

prog

。

9. 重复步骤 7 和 8 直到行内所有字节编程完毕。

10. PGM 位清零。

11. 延时 t

nvh

。

12. HVEN 位清零。

13. 延时 t

14. 去除外部电压 V

后,存储器又能在读方式下访问。

rcv

。

PP

这个编程顺序重复到整个存储器,直到所有的数据被烧写。

注意

Flash 存储器不能被 Flash 空间内的代码执行编程或擦除。为了编程或擦除

Flash,必须来自 RAM 或 BDC 的命令才能执行。在擦除或编程过程中,用户代码

不能进入等待或停止模式。

这些操作必须在以上规定的步骤执行;其它一些不相干的操作可能在这些步骤之间

出现。

4.6.3 Flash 块擦除操作

用下面步骤块擦除整个 Flash 存储器:

。

PP

。

PP

。

MC9RS08KA2 系列 数据手册 , 第 1 版

1. 加外部电压 V

2. 在 Flash 控制寄存器 MASS 位置位;

3. 写任何数据到任何 Flash 位置,通过高页存取窗口 $00C0–$00FF.。 (数据写操作之前, PAGESEL 寄

存器必须配置正确去映射高页存取窗口任何 Flash位置 )。

4. 延时 t

nvs

。

5. HVEN 位置位。

6. 延时 t

me

。

7. MASS 位清零。

8. 延时 t

nvh1

9. HVEN 位清零。

10. 延时 t

, 后,存储器又能在读模式下访问。

rcv

11. 去除外部电压 V

30 飞思卡尔半导体

第 4 章 存储器

注意

Flash 存储器不能被 Flash 空间内的代码执行编程或擦除。为了编程或擦除

Flash,必须来自 RAM 或 BDC 的命令才能执行。在擦除或编程过程中,用户代码

不能进入等待或停止模式。

这些操作必须在以上规定的步骤执行;其它一些不相干的操作可能在这些步骤之间

出现。

4.6.4 安全性

MC9RS08KA2 系列 拥有的电路帮助防止未授权访问 Flash 存储器的内容。当有安全机制保证时, Flash

可以认为是一个安全的资源。 RAM、直接页寄存器和后台调试控制器被认为是不安全的资源。试图通过后台

调试接口,或无论 BKGDPE 是否被置位,访问一个安全的存储是行不通的 ( 读出全是 0)。

基于 FOPT寄存器的非易式性寄存器位 (SECD) 的状态决定是否安全。在复位期间,非易式性寄存器

NVOPT 被拷贝到高页寄存器 FOPT 寄存器。通过对 NVOPT 编程用户获得安全机制保护,与 Flash 存储器被

编程的相同的时间完成。注意被擦除状态 (SECD = 1) 使 MCU 不安全。当 NVOPT的 SECD 位被清零

(SECD = 0), 单片机下次通过上电复位,内部复位,或外部复位方式被复位,可以确保安全。为了使安全机制

失效,块擦除必须通过 BDM 命令执行并且跟随在任何复位后。

独立的后台调试控制器依然可以访问寄存器和 RAM。通过写 Flash 控制寄存器实现 Flash 块擦除是可以

的,通过 BDM 命令参考 4.6.3 节 Flash 块擦除操作。

由下面步骤通过后台调试接口总是能使安全机制失效:

1. 通过后台 BDM 命令或 RAM 装载程序块擦除 Flash 。

2. 执行复位单片机将用失效的安全保护引导。

注意

当单片机引导进入正常工作模式, MS 管脚在复位期间为高, SECD 位清零

(SECD = 0), Flash 安全机制起用。 BKGDPE 位复位后为 0,并且所有的 BDM 通

讯关闭,后台调试禁止。

4.7 Flash 寄存器和控制位

Flash 模块有一个非易式性寄存器,NVOPT ($3FFC), 复位时在 Flash 存储器被拷贝到相关的控制寄存器

FOPT ($0210)。

4.7.1 Flash 选项寄存器 (FOPT 和 NVOPT)

复位时非易式性单元 NVOPT 的内容在 Flash 内被拷贝到 FOPT。 位 7 至 1 不能使用并且读出总是为 0。

这个寄存器在任何时间都能被读出,但是写无意义或无效。为了改变这个寄存器的值,通常擦除和再编程

Flash 中的 NVOPT 寄存器后导致一次新的 MCU 复位。

76543210

R 0000000SECD

W

Reset 复位期间此寄存器从非易失性 NVOPT 载入 .

= Unimplemented or Reserved

图 4-3. Flash 选项寄存器 (FOPT)

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 31

第 4 章 存储器

表 4-2. FOPT 域描述

域描述

0

SECD

安全状态代码 — 此位决定 MCU 的安全状态 . MCU 被保护, Flash存储器内容不能被来自任何不安全源包括后台

调试接口访问。参考 4.6.4 节 安全性 ”.

0 安全使能

1 安全失效

4.7.2 Flash 控制寄存器 (FLCR)

76543210

R 0000

W

Reset00000000

= Unimplemented or Reserved

HVEN MASS

图 4-4. Flash 控制寄存器 (FLCR)

表 4-3. FLCR 域描述

域描述

3

HVEN

高电压使能 — 此读 / 写位允许高电压加载到 Flash 阵列用于编程和擦除操作。只有当 PGM = 1 或 MASS = 1 和

正常编程或擦除顺序被跟随, HVEN 可以被置位。

0 高电压禁止加载到阵列

1 高电压允许加载到阵列

0

PGM

1

2

MASS

0

PGM

1

当 Flash 安全机制有效时,写 PGM 位是无效的。结果,Flash 编程不允许。

块擦除位 — 这个读 / 写位配置存储器块擦除工作。

0 块擦除没有被选择。

1 选择块擦除。

编程控制位 — 这个读 / 写位配置存储器编程工作。PGM 与 MASS 位互锁因此这两个位不能同时等于 1 或置 1 。

1

0 不选择编程。

1 选择编程。

4.8 页选择寄存器 (PAGESEL)

这是一个在直接页地址可以分页访问 64 个字节的窗口 ($00C0–$00FF)。 编程页选择寄存器可以通过直接

页访问确定存储器映射中的 64 个字节块。例如,当 PAGESEL 寄存器值位 $08 时,高页寄存器

($0200–$023F) 能够由直接寻址方式指令通过页窗口 ($00C0–$00FF) 访问。

76543210

R

AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6

W

Reset 00001000

图 4-5. 页选择寄存器 (PAGESEL)

MC9RS08KA2 系列 数据手册 , 第 1 版

32 飞思卡尔半导体

表 4-4. PAGESEL 区描述

Field Description

第 4 章 存储器

7:0

AD[13:6]

页选择器 — 这些位定义地址行位 6 到位 13,它们决定通过直接页窗口被访问的存储器块的 64 字节的块界线,

见 图 4-6 和表 4-5。

选择的存储器块地址

图 4-6. 存储器块界线选择器

表 4-5 列出了通过页窗口 ($00C0–$00FF) 访问的存储器块。

表 4-5. 页窗口对应于 $00C0–$00FF

Page Memory Address

$00 $0000–$003F

$01 $0040–$007F

$02 $0080–$00BF

$03 $00C0–$00FF

$04 $0100–$013F

.

.

.

14- 位存储器地址

000000

AD[13:6]

.

.

.

$FE $3F80–$3FBF

$FF $3FC0–$3FFF

注意

物理地址 $0000-$000E 是 RAM。 物理地址 $000F 是寄存器 X。 D[X] 寄存器仅被

映射到地址 $000E 。当 X 寄存器值是 $0E 或 $CE, PAGESEL 是 $00 时,位于

$000E 的物理 RAM 能够通过 D[X] 寄存器访问。

当 PAGESEL 寄存器是 $00,页窗口被映射到第一页 ($00-$3F)。分页地址

$00C0–$00CE 被映射到物理地址 $0000-$000E,也就是, RAM。 分页地址

$00CF 被映射到寄存器 X。因此,访问地址 $CE 的内容返回实际 RAM $000E 的

内容。访问地址 $000E 返回 D[X] 寄存器内容。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 33

第 4 章 存储器

MC9RS08KA2 系列 数据手册 , 第 1 版

34 飞思卡尔半导体

第 5 章

复位,中断,和通用系统控制

5.1 介绍

本章讨论在 MC9RS08KA2 系列中的基本复位和中断机制和不同的复位与中断源。 MC9RS08KA2 系列一

些外设模块的中断源在本数据手册的其它章会更详细讨论。本章集合了关于所有中断和复位源的基本信息,放

在一起便于参考。一些复位和唤醒源,包括计算机正常工作 (COP) 看门狗和实时中断 (RTI), 在外设系统中没

有专门的篇章部分,但也是系统控制逻辑部分。

5.2 特点

复位和中断特点包括:

• 多复位源便于灵活系统配置和可靠工作

• 系统复位状态寄存器 (SRS) 可以显示出最后一次产生复位的复位源

• 系统中断等待寄存器 (SIP1) 可以显示出等待系统中断的状态

• 模拟比较器中断使能

• 键盘中断使能

• 低电压检测中断使能

• 模定时器中断使能

• 实时中断中断使能;在停止模式基于独立的 1 KHz 时钟源中断使能;

5.3 MCU 复位

复位的 MCU 通过一个已知初始化条件设置提供一个途径开始执行。复位期间,大多数控制和状态寄存器

被迫得到初始值并且程序计数器从 $3FFD 地址开始。为了正确的复位操作,操作数位于 $3FFE–$3FFF 的一

条 JMP 指令 ( 操作码 $BC) 必须被编程跳转到用户应用软件。此操作数定义的地址为用户程序的开始地址。

片上外设模块禁止且 I/O 管脚被初始配置为通用的高阻态输入,上拉 / 下拉功能禁止。

MC9RS08KA2 系列 有七个复位源:

• 外部管脚复位 (PIN) — SOPTE 寄存器的 RSTPE 位被置 1

• 上电复位 (POR)

• 低电压检测 (LVD)

• 计算机正常工作 (COP) 定时器

• 非法操作码检测 (ILOP)

• 非法地址检测 (ILAD)

• 通过 BDC 命令 BDC_RESET 强迫后台调试复位

每一个复位源,除去后台调试强迫复位外,在系统复位状态寄存器 (SRS) 中都有一个相关的位。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 35

第 5 章 复位,中断,和通用系统控制

5.4 计算机正常工作 (COP) 看门狗

假如应用软件没有预期执行, COP 看门狗将会强迫系统复位。为了防止看门狗复位,应用软件必须定期

周期性喂狗。假如系统程序跑飞,不能在 COP 定时器溢出前将 COP 计数值清零,系统复位将被产生,强迫

系统回到一个已知的起始点。

任何复位后, SOPT 中的 COPE 位被置位,允许 COP 看门狗工作 ( 见 5.8.2 节 系统选项寄存器 (SOPT)

及附加信息 )。假如 COP 看门狗在应用软件中不想被使用,将 COPE 清零即可。 SRS 地址单元写入任何值都

将 COP 计算器清零。这些写操作不会影响只读 SRS 寄存器的数据。相反地,写这个地址的行为将被译解为

发送一个清零信号到 COP 计数器。

SOPT 寄存器的 COPT 位控制长时间和短时间定时溢出。表 5-1 概括了 COPT 位的控制功能。COP看门

狗工作时钟源为 1 kHz ,默认为长时间定时溢出 (2

栏中

COPT COP 溢出计数

02

12

1

栏中列出的值基于 t

差,参见 Section A.9.1, “ 控制时间 ,” 中的 t

8

cycles)。

表 5-1. COP 配置选项

5

cycles (32 ms)

8

cycles (256 ms)

≈ 1ms。对于这个值的公

RTI

1

。

RTI

即使应用软件使用 COPE 和 COPT 复位的默认值,用户在复位初始化期间也应该写这个只能写一次的

SOPT 寄存器用于锁住设置。这样,假如应用软件跑飞也不会出现意外改变这个寄存器的情况。初次写 SOPT

寄存器将 COP 计数器清零。

在后台调试模式, COP 计数器不计数。

当 MCU 进入停止模式,COP 计数器在进入停止模式前被重新初始化为零。一旦退出停止模式 COP 计数

器重新从零开始计数。

5.5 中断

MC9RS08KA2 系列 没有像 HC08 和 HCS08does 那样拥有一个 具有向量表查询机制的中断控制器。然

而,模块中断源,如 LVD, KBI, 和 ACMP,依然可以将 CPU 从等待或停止模式唤醒。用户应用程序的职责是查

找相关的模块明确唤醒源。

每个模块唤醒源与相关的中断设置位有关系。假如这个位被禁止,此中断源被关闭,这个源不能将 CPU

从等待或停止模式唤醒。然而,相关的中断标志位依然会被置位,指出一个外部唤醒事件发生。

系统中断等待寄存器 (SIP1) 显示了系统等待中断的状态。 当 SIP1 的只读位被置 1,表明有一个等待中断

需要处理指明的模块。写这个寄存器位是无效的。当来自被指明的模块的所有相关中断标准位被清零,这个等

待中断标志位自动清零。

5.6 低电压检测 (LVD) 系统

为了保护存储器内容和控制 MCU 系统在电源电压变化状态, MC9RS08KA2 系列 拥有一个系统防止低电

压。这个系统由一个上电复位和一个具有预先定义下跌电压的 LVD 电路组成。 当 SPMSC1 寄存器的 LVDE 置

位, LVD 允许工作。进入停止模式后 LVD 禁止工作,除非 SPMSC1 的 LVDSE 位置 1。假如 LVDSE 和都被

置 1,在停止模式 LVD 工作功耗将更大些。

MC9RS08KA2 系列 数据手册 , 第 1 版

36 飞思卡尔半导体

第 5 章 复位,中断,和通用系统控制

5.6.1 上电复位 (POR) 工作

当电源刚开始给 MCU 供电时,或当电源电压下降低于 V

于电源电压上升, LVD 电路将保持 MCU 在复位状态,直到电源电压已经上升超过 V

POR,在 SRS 寄存器的 POR 位和 LVD 位都被置 1。

电压时 ,POR 电路将产生一个复位条件。由

POR

电压。随着一个

LVD

5.6.2 LVD 复位工作

通过 LVDRE 位置 1,依据一个低电压条件, LVD 可以被配置位产生复位。一个 LVD 复位产生后, LVD

系统将保持 MCU 在复位状态,直到电源电压上升高于 VLVD。随着 LVD 复位或 POR 后 SRS 寄存器的 LVD

位被置 1。

5.6.3 LVD 中断工作

当一个低电压条件被检测,LVD 电路利用 SPMSC1 寄存器被配置为中断工作 (LVDE 置 1、 LVDIE 置 1、

LVDRE 清零 ), SPMSC1 寄存器的 LVDF 位将被置 1 并且一个 LVD 中断请求将产生。

5.7 实时中断 (RTI)

实时中断功能用于产生定期中断。RTI 时钟可以是 1-kHz 内部参考时钟或 ICS 模块的被调整的 32-kHz 内

部参考时钟。32-kHz内部参考时钟被 32 分频产生一个被调整的 1-kHz 时钟用于应用程序需要更精确的实时中

断。 SRTISC 的 RTICLKS 位用于选择 RTI 时钟源。 当 MCU 在运行、等待或停止模式时,用于 RTI 的 1-kHz

和 32-kHz 时钟源都能使用。

SRTISC 寄存器包含一个只读状态标志位,一个只写应答位,和一个用于选择七种唤醒周期中的一种或

RTI 禁止的 3- 位控制值 (RTIS)。 RTI 由一个逻辑中断允许, RTIE,,用于允许屏蔽实时中断。 RTIS 位清零禁

止 RTI,并且不会中断产生。关于这个寄存器的详细介绍见 5.8.4 节 系统实时中断状态和控制寄存器

(SRTISC),” 。

5.8 复位,中断,及系统控制寄存器和控制位

对于所有寄存器绝对地址分配,参考第 4 章 存储器 直接页寄存器概要。此章节仅涉及到寄存器和控制位

的名称。有一个飞思卡尔提供的同等的或页眉文件用于将这些名称转换成合适的绝对地址。

SOPT 寄存器的一些控制位与工作模式有关。虽然这些位在这里提供了简单描述,在第 3 章 工作模式章

节有更详细相关功能阐释。

5.8.1 系统复位状态寄存器 (SRS)

此高页寄存器包含只读状态标志位指出大多数最近复位源。当一个调试工具通过 BDC_RESET命令强迫

复位时,在 SRS 的所有状态位将被清零。写任何值到这个寄存器地址使 COP 看门狗定时器清零且不会影响

这个寄存器的内容。这些位的复位状态取决于 MCU 产生复位的原因。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 37

第 5 章 复位,中断,和通用系统控制

76543210

R POR PIN COP ILOP ILAD 0 LVD 0

W 写任何值到 SRS 地址清零 COP 看门狗定时器

POR: 10000010

LVR: 00000010

Any other

0 Note 1 Note 1 Note 1 Note 1 0 0 0

reset:

1. 任何这些复位源在复位入口时间时是活动的都将导致相关位被置位;相关源的位在复位入口时间不是活动的将被清零。

图 5-1. 系统复位状态 (SRS)

表 5-2. SRS 域描述

域描述

7

POR

上电复位 — 通过上电检测逻辑导致复位。因为内部电源电压在那个时候正在上升,低电压复位 (LVR) 状态位也

被置位用于表明在内部电源低于 LV R 门限产生复位。

0POR没有产生复位

1POR 产生复位

6

PIN

外部复位管脚 — 一个在外部复位管脚上的有效低电平导致复位。

0 外部复位管脚没有导致复位

1 外部复位管脚导致复位

5

COP

计算机正常工作 (COP) 看门狗 — 通过 COP 看门狗定时器定时溢出导致复位。 COPE = 0 时此复位源被锁住。

0 没有 COP 定时溢出导致复位

1COP 定时溢出导致复位

4

ILOP

非法操作码 — 试图执行一个无效或非法操作码 导致复位。假如 SOPT 寄存器 STOPE = 0 停止模式被禁止,

STOP 指令被认为是非法的。假如 BDCSC 寄存器中 ENBDM = 0 主动后台模式禁止, BGND 指令被认为是非法

的。

0 没有非法操作码导致复位

1 非法操作码导致复位

3

ILAD

非法地址 — 试图访问无效存储器地址的数据或指令导致复位

0 没有非法地址导致复位

1 非法地址导致复位

1

LVD

低电压检测 — 假如 LVDRE 位置 1 且电源下跌低于 LVD 跌落电压,将导致 LVD 复位。

0 没有 LVD 跌落或 POR. 导致复位

1LVD 跌落或 POR. 导致复位

MC9RS08KA2 系列 数据手册 , 第 1 版

38 飞思卡尔半导体

第 5 章 复位,中断,和通用系统控制

5.8.2 系统选项寄存器 (SOPT)

此高页寄存器是一个只写一次的寄存器,因此只有复位后的第一次写是有效的。它能在任何时候被读出。

任何后来企图写 SOPT (有意或无意 ) 被忽略用于防止这些敏感设置被意外改变。 SOPT 必须在用户复位初始

化程序被写设置期望的控制,即使这些期望设置与复位默认设置相同。

76543210

R

COPE COPT STOPE

W

Reset: 1 1 0 0 0 0 1 (Note 1) u

POR:1100001 (Note1)0

= Unimplemented or Reserved u = Unaffected

图 5-2. 系统选项寄存器 1 (SOPT)

1. 当芯片复位进入正常模式 ( 复位期间 MS 为高 ),假 如 Flash 安全机制禁止 (SECD = 1)BKGDPE 被置位;假如 Flash 安全机制

使能 (SECD = 1)BKGDPE 被清零;当芯片复位进入主动 BDM 模式 ( 复位期间 MS 为低 ), BKGDPE i 总是被置 1 因此 BDM

通讯被允许。

表 5-3. SOPT 寄存器域描述

Field Description

000

BKGDPE RSTPE

7

COPE

COP 看门狗使能 — 此仅能写一次的位选择 COP 看门狗是否使用。

0COP 看门狗定时器禁止

1COP 看门狗定时器使能 (定时溢出强迫复位 )

6

COPT

COP 看门狗定时溢出 — 此仅能写一次的位选择 COP 定时溢出的周期

0 选择短定时溢出周期

1 选择长定时溢出周期

5

STOPE

停止模式使能 — 此仅能写一次的位用于使能停止模式。假如停止模式禁止且用户程序试图执行一条 STOP 指

令,导致一个非法操作码复位

0 停止模式禁止

1 停止模式使能

1

BKGDPE

后台调试模式管脚使能 — 此仅能写一次的位当置位时使能 PTA3/ACMPO/BKGD/MS 管脚功能作为

1,2

pinBKGD/MS.。当清零,管脚功能作为两种输出可选功能中的一种。任何 MCU 复位后这管脚默认作为

BKGD/MS 功能。

0 PTA3/ACMPO/BKGD/MS 管脚功能作为 PTA3或 ACMPO.

1 PTA3/ACMPO/BKGD/MS 管脚功能作为 BKGD/MS。

0

RSTPE

1

当芯片复位进入正常模式 ( 复位期间 MS 为高 ),假 如 Flash 安全机制禁止 (SECD = 1)BKGDPE 被置位;假如 Flash 安全机制

管脚使能 — 当置位时,此仅能写一次的位使能 PTA2/KBIP2/TCLK/RESET/VPP 管脚功能作为 RESET。

RESET

当清零,管脚功能作为两种输人可选功能中的一种。跟随一个 MCU POR,此管脚是只输入功能。当 RSTPE 被

置位,在 RESET

0 PTA2/KBIP2/TCLK/RESET

1 PTA2/KBIP2/TCLK/RESET

的内部上拉设备使能。

/VPP 管脚功能作为 PTA2/KBIP2/TCLK/VPP.。

/VPP 管脚功能作为 RESET/V

PP

。

使能 (SECD = 1)BKGDPE 被清零;当芯片复位进入主动 BDM 模式 ( 复位期间 MS 为低 ), BKGDPE i 总是被置 1 因此 BDM

通讯被允许。

2

BKGDPE 仅能从 1 到 0 写一次 。被用户软件从 0 到 1 写是不允许的。通过一个 POR 或对于在注释 1 中正常条件复位,

BKGDPE 能被改变成 1。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 39

第 5 章 复位,中断,和通用系统控制

5.8.3 系统设备识别寄存器 (SDIDH, SDIDL)

此高页只读寄存器包含了主机开发系统可以识别 RS08 衍生和修订的码。这允许开发软件认识位于目标

MCU 的专用存储器块,寄存器和控制位。

修订码

76543210

R REV3 REV2 REV1 REV0 ID11 ID10 ID9 ID8

W

Reset: 0 (Note 1) 0 (Note 1) 0 (Note 1) 0 (Note 1) 1 0 0 0

= Unimplemented or Reserved

1. 被硬编码到这些位的修订码反映了当前芯片版本级别。

图 5-3. 系统设备鉴定寄存器 — 高 (SDIDH)

表 5-4. SDIDH 寄存器域描述

域描述

7:4

修订码 — 地址 SDIDH 的高顺序 4 位被硬编码反映了当前芯片版本级别 (0-F)。

REV[3:0]

3:0

ID[11:8]

76543210

部分识别码 — 在 RS08 系列每个派生出的都有一个独一无二的识别码。 MC9RS08KA2 被硬编程值 $0800。也可

见在 图 5-4 中的 ID 位。

R ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

W

Reset: 00000000

= Unimplemented or Reserved

图 5-4. 系统设备识别寄存器 — 低 (SDIDL)

表 5-5. SDIDL Register Field Descriptions

Field Description

7:0

ID[7:0]

部分识别码 — 在 RS08 系列每个派生出的都有一个独一无二的识别码。 MC9RS08KA2 被硬编程值 $0800。也

可见在 图 5-3 中的 ID 位。

MC9RS08KA2 系列 数据手册 , 第 1 版

40 飞思卡尔半导体

第 5 章 复位,中断,和通用系统控制

5.8.4 系统实时中断状态和控制寄存器 (SRTISC)

此高页寄存器包含了 RTIde 状态和控制位。

76543210

R RTIF 0

RTICLKS RTIE

W RTIACK

Reset: 00000000

= Unimplemented or Reserved

图 5-5. 系统 RTI 状态和控制寄存器 (SRTISC)

表 5-6. SRTISC 寄存器域描述

域描述

0

RTIS

7

RTIF

6

RTIACK

5

RTICLKS

4

RTIE

2:0

RTIS

时钟中断标志位 — 这个只读状态位显示了周期唤醒定时器已经定时溢出。

0 周期唤醒定时器没有定时溢出。

1 周期唤醒定时器定时溢出。

实时中断应答 — 这个只写位用于应答实时中断请求 ( 写 1 清除 RTIF)。写 0 无意义或影响。读总是返回 0。

实时中断时钟选择 — 这读 / 写位选择实时中断的时钟源。

0 实时中断请求时钟源是内部 1-kHz 振动器。

1 实时中断请求时钟源是内部可调的 32-kHz 振荡器 (ICS 模块 ) 和在 RT 逻辑被 32 分频产生一个可调的 1-kHz

时钟源用于 RTI 计数器。

实时中断使能 — 此读写位使能实时中断。

0 实时中断禁止

1 实时中断允许

实时中断延时选择 — 这些读 / 写位选择 RTI 周期。见表 5-7.

表 5-7. 实时中断周期

RTIS RTI 定时溢出

000 Disable RTI

001 8 ms

010 32 ms

011 64 ms

1

100 128 ms

101 256 ms

110 512 ms

111 1.024 s

1

定时溢出值基于 1 ms 周期的 RTI 时钟源。内部 1-kHz 源公差参考 t

(Table A-8) 和来自 ICS 的内部 32-kHz (Table A-7).

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 41

RTI

第 5 章 复位,中断,和通用系统控制

注意

为了停止模式下完全关闭内部 1 kHz 振荡器, RTIS 位必须被选择为 %000 和

RTICLKS 位置 1。

5.8.5 系统电源管理状态和控制 1 寄存器 (SPMSC1)

此高页寄存器包含状态和控制位支持低电压检测功能,并且允许带隙参考电压用于 ACMP 和 LVD 模块。

76543210

R LV DF 0

W LV DA CK

Reset: 00011100

= Unimplemented or Reserved

1

复位后此位仅能写一次。额外的写被忽略。

LVDIE LVDRE

(1)

LV DS E LV DE

(1)

图 5-6. 系统电源管理状态和控制 1 寄存器 (SPMSC1) 寄存器

表 5-8. SPMSC1 寄存器域描述

Field Description

0

BGBE

7

LVDF

6

L VDACK

5

LVDIE

4

LVDRE

3

LVDSE

2

LVDE

0

BGBE

低电压检测标志位 — 倘若 LVDE = 1,此只读状态位指出一个低电压检测事件。

低电压检测应答 — T 只写位用于应答低电压检测错误 ( 写 1 清除 LVDF).。读总是返回 0。

低电压检测中断使能 — 此位使能用于 LVDF 硬件中断请求

0 硬件中断禁止 ( 用于登记 ).

1 当 LVDF = 1 请求一个硬件中断

低电压检测复位使能 — 此只写位使能低电压检测事件产生一个硬件复位 (倘若 LVDE = 1).

0LVDF 不产生中断复位

1 当 LVDF = 1 强迫 MCU 复位

低电压检测停止使能 — 倘若 LVDE = 1,这读 / 写位确定当 MCU 在停止模式时低电压检测功能是否工作。

0 停止模式期间低电压检测禁止。

1 停止模式期间低电压检测使能。

低电压检测使能 — 此只写位使能低电压检测逻辑和限制这个寄存器中的其它位的操作。

0LVD 逻辑禁止

1LVD 逻辑使能

待隙缓存使能 — 通过在内部通道中之一的 ACMP 模块,这位使能一个内部缓存用于待隙电压参考。

0 待隙缓存禁止

1 待隙缓存使能

5.8.6 系统中断等待寄存器 (SIP1)

此高页寄存器包含模块等待中断状态。

MC9RS08KA2 系列 数据手册 , 第 1 版

42 飞思卡尔半导体

第 5 章 复位,中断,和通用系统控制

76543210

R 0 0 0 KBI ACMP MTIM RTI LVD

W

Reset: 00000000

= Unimplemented or Reserved

图 5-7. 系统中断等待寄存器 (SIP1)

表 5-9. SIP1 寄存器域描述

域描绘

4

KBI

3

ACMP

2

MTIM

1

RTI

0

LVD

键盘中断等待 — 此只读位显示有一个来自 KBI 模块的等待中断。清除 KBISC 寄存器中的 KBF 位将此位清零。

读也将此位清零。

0 没有等待 KBI 中断;例如, KBF 标志位和 / 或 KBIE 位被清零。

1 有等待 KBI 中断;例如, KBF 标志位和 / 或 KBIE 位被置位。

模拟比较器中断等待 — 此只读位显示有一个来自 ACMP 模块的等待中断。清除 ACMPSC 寄存器中的 ACF 位将

此位清零。读也将此位清零。

0 没有等待 ACMP 中断;例如, ACF 标志位和 / 或 ACIE 位被清零。

1 有等待 ACMP 中断;例如, ACF 标志位和 / 或 ACIE 位被置位。

模定时器中断等待 — 此只读位显示有一个来自 MTIM 模块的等待中断。清除 MTIMSC 寄存器中的 TOF 位将此

位清零。读也将此位清零。

0 没有等待 MTIM 中断;例如, TOF 标志位和 / 或 TOIE 位被清零。

1 有等待 MTIM 中断;例如, TOF 标志位和 / 或 TOIE 位被置位。

实时中断等待 — 此只读位显示有一个来自 RTI 模块的等待中断。清除 SRTISC寄存器中的 RTIF 位将此位清零。

读也将此位清零。

0 没有等待 RTI 中断;例如, RTIF

标志位和 / 或 RTIE 位被清零。

1 没有等待 RTI 中断;例如, RTIF 标志位和 / 或 RTIE 位被置位。

低电压检测中断等待 — 此只读位显示有一个来自低电压模块的等待中断。清除 SPMSC1 寄存器中的 LVDF 位将

此位清零。读也将此位清零。

0 没有等待 LVD 中断;例如, LVDF 标志位和 / 或 LVDE 位被清零。

1 没有等待 LVD 中断;例如, LVDF 标志位和 / 或 LVDE 位被置位。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 43

第 5 章 复位,中断,和通用系统控制

MC9RS08KA2 系列 数据手册 , 第 1 版

44 飞思卡尔半导体

第 6 章

QD

QD

1

0

Port Read

PTADDn

PTADn

Output Enable

Output Data

Input Data

Synchronizer

Data

BUSCLK

并行输入 / 输出控制

本章节讲述了软件控制相关的并行输入 / 输出和管脚控制。 MC9RS08KA2 有一个并行 I/O 端口 , 此端口

在 6 脚封装包括两个 I/O 管脚或在 8 脚封装包括 4 个 I/O 管脚,一个只输出脚,和一个只输入脚。更多关于管

脚分配和外部硬件考虑见第 2 章 管脚和连接 。

表 2-1 显示所有 I/O 管脚与片内外设功能复用。外设模块有比 I/O 更大的优先权,因此当外设允许,则与

此复用的管脚的 I/O 功能禁止。复位后,复用外设功能被禁止因此这些管脚被 I/O 功能控制。所有这些 I/O 被

配置为输入 (PTADDn = 0) ,相关的上拉 / 下拉设备禁止,只输出管脚除外,它默认为 BKGD/MS 功能。

并行 I/O读写通过端口数据寄存器完成。方向,输入或输出,被端口数据方向寄存器控制。图 6-1 显示了

作为一个独立管脚并行 I/O 端口功能的方框图。

图 6-1. 并行 I/O 方框图

数据方向控制位 (PTADDn) 决定相关管脚的输出缓冲区是否允许,也控制端口数据寄存器读来源。 相关管

脚的输入缓冲区总是允许,除非这个管脚作为模拟功能或是一个只输出管脚。

当一个管脚的复用数字功能允许,输出缓冲区被这些复用功能控制。然而,数据方向寄存器位将继续控

制端口数据寄存器的方向。

当一个管脚的复用模拟功能允许,输入和输出缓冲区都禁止。从任何端口数据位读出值为 0,这个位是一

个输入 (PTADDn = 0) 且输入缓冲区禁止。通常,一个具有可选择数字功能和模拟功能的管脚,模拟功能具有

更高的优先级。因此当数字和模拟功能同时允许时,模拟功能控制此管脚。

飞思卡尔半导体 45

MC9RS08KA2 系列 数据手册 , 第 1 版

第 6 章 并行输入 / 输出控制

在改变端口管脚方向成输出前,写端口数据寄存器是个好的编程习惯。这保证此管脚不会被此端口数据

寄存器的老数据驱动。

与并行 I/O 端口相关的是位于高页寄存器空间的独立工作的并行 I/O 寄存器。这些寄存器用于控制管脚上

拉 / 下拉和斜率。更详细信息见 6.3 节 管脚控制寄存器 ” 。

6.1 在低功耗模式下管脚状态

在等待和停在模式,所有管脚状态被保持,这是因为内部逻辑维持供电。恢复后,所有管脚功能与进入

停在模式前一样。

6.2 并口 I/O 寄存器

本节提供了与并行 I/O端口有关的寄存器的信息。并行 I/O 寄存器位于存储器的地址小于 $001F,因此短

型和直接寻址方式指令可以使用。

所有并行 I/O绝对地址分配,参考第 4 章 存储器中的表格。本节仅通过名字涉及到寄存器和控制位。飞

思卡尔半导体提供等同的或页眉文件将这些名字转换成合适的绝对地址。

6.2.1 端口 A 寄存器

本节描述了端口 A 并行 I/O 功能,通过数据和数据方向寄存器控制。

76543210

R 00

PTAD5 PTAD4 PTAD3

W

Reset: 00000000

PTAD2

PTAD1 PTAD0

图 6-2. 端口 A 数据寄存器 (PTAD)

表 6-1. PTAD 寄存器区域描述

Field

5:0

PTAD[5:0]

76543210

R 00

W

Reset: 00000000

端口 A 数据寄存器位 — 当端口 A 管脚是输入,读管脚返回逻辑电平。当端口 A 被配置为输出,读返回被写入这

个寄存器最新的值。写入值被锁住这个寄存器所有的位。由于端口 A 管脚被配置为输出,逻辑电平驱动相关的

管脚。

复位后 PTAD 都为 0,但这些 0 电平不用于驱动相关管脚,这是因为复位也配置所有端口管脚为高阻态输入,且

上拉 / 下拉禁止。

PTADD5 PTADD4

描述

00

PTADD1 PTADD0

图 6-3. 端口 A 数据方向寄存器 (PTADD)

MC9RS08KA2 系列 数据手册 , 第 1 版

46 飞思卡尔半导体

表 6-2. PTADD 寄存器描述

第 6 章 并行输入 / 输出控制

Field

5:4,1:0

PTADD[5:4,1:0]

端口 A 数据方向位 — 这些读 / 些位控制端口 A 的方向并从 PTAD 读出。

0 输入 ( 输出驱动器禁止 ) 且读返回此管脚值

1 端口 A 位输出驱动允许且 PTAD 读返回 PTADn 的内容。

描述

6.3 管脚控制寄存器

此节提供了用于管脚功能的并行 I/O 端口相关的寄存器信息。

关于管脚控制寄存器绝对地址分配,参考第 4 章 存储器 。本节仅通过名字涉及到寄存器和控制位。飞思

卡尔半导体提供等同的或页眉文件将这些名字转换成合适的绝对地址。

在本节与端口 A 相关管脚被提供的寄存器控制。这些寄存器控制管脚上拉 / 下拉和端口斜率,不依赖于

并行 I/O 寄存器。

6.3.0.1 内部上拉装置允许

一个内部上拉装置可以通过设置上拉装置允许寄存器 (PTAPEn) 的相关位允许允许每个端口管脚内部上

拉。假如此管脚被并行 I/O 控制逻辑配置为输出或即使相关上拉装置允许寄存器置位但有复用外设输出功能,

上拉装置禁止。假如管脚被配置为一个模拟功能上拉装置也禁止。

76543210

R

W

00

PTAPE5 PTAPE4

0

PTAPE2 PTAPE1 PTAPE0

Reset: 00000000

图 6-4. 端口 A 寄存器内部上拉装置允许 (PTAPE)

表 6-3. PTAPE 寄存器域描述

Field Description

5:4,2:0

PTAPE[5:4,2:0]

内部拉设备使能用于端口 A 位 — 这些控制位中的每一位决定内部拉设备是否使能相关 PTA 管脚。当端口 A

管脚被配置位输出,这些位无效且内部上拉设备禁止。

0 内部上拉设备禁止用于端口 A 位 n。

1 内部上拉设备允许用于端口 A 位 n。

6.3.0.2 上拉 / 下拉控制

依据相关 PTAPE 位,上拉 / 下拉控制用于选择上拉或下拉装置使能。

76543210

R

W

Reset: 00000000

00

PTAPUD5 PTAPUD4

0

PTAPUD2 PTAPUD1 PTAPUD0

图 6-5. 上拉 / 下拉设备控制用于端口 A (PTAPUD)

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 47

第 6 章 并行输入 / 输出控制

域描述

表 6-4. PTAPUD 寄存器域描述

5:4,2:0

PTAPUD[5:4,2:0]

上拉 / 下拉设备控制用于端口 A 位 — 这些控制位的每一位决定内部上拉或下拉设备是否选择用于相关的

PTA 管脚。此实际的上拉 / 下拉设备仅被使能的相关 PT APE 位使能。

0 内部上拉设备被选择用于端口 A 位 n。

1 内部下拉设备被选择用于端口 A 位 n。

6.3.0.3 输出斜率控制允许

斜率控制可以被斜率控制寄存器 (PTASEn) 相关位允许用于每个端口管脚。当被允许使用时,斜率控制限

制输出电平变化的斜率,可以减小 EMC 发射。当管脚被配置为输入时斜率控制无效。

76543210

R

W

Reset: 00111011

00

PTASE5 PTASE4 PTASE3

0

PTASE1 PTASE0

图 6-6. S 斜率使能用于端口 A 寄存器 (PTASE)

表 6-5. PTASE 寄存器域描述

域描述

5:3;1:0

PTASE[5:3;1:0]

输出斜率使能用于端口 A 位 — 这些控制位中的每一位都决定输出斜率控制是否使能相关的 PTA 管脚。当端口

A 管脚被配置位输入,这些位无效。

0 输出斜率控制禁止用于端口 A 位 n。

1 输出斜率控制允许用于端口 A 位 n。

MC9RS08KA2 系列 数据手册 , 第 1 版

48 飞思卡尔半导体

第 7 章

RS08 CORE

USER FLASH — 2,048 BYTES

USER RAM — 63 BYTES

注意 :

(1) 当作为输入时,由软件设置管脚内部上拉 / 下拉。

(2) 当作为复位功能,内部上拉自动使能。 (RSTPE = 1).

(3) 在 6 脚封装中这些管脚不存在。

POWER AND

PTA

V

SS

V

DD

INTERNAL CLOCK

SOURCE

BDC

RS08 SYSTEM CONTROL

RTI

CPU

COP

WAKEUP LVD

RESET AND STOP WAKEUP

MODES OF OPERATION

POWER MANAGEMENT

5-BIT KEYBOARD

INTERRUPT MODULE

PTA0/KBIP0/ACMP+

(1)

PTA1/KBIP1/ACMP-

(1)

PTA2/KBIP2/TCLK/RESET/VPP

(1),( 2)

PTA3/ACMPO/BKGD/MS

ANALOG COMPARATOR

MODULE

MODULO TIMER

MODULE

PTA4/KBIP4

(1),(3)

PTA5/KBIP5

(1), (3)

INTERNAL REGULATOR

(KBI)

5

TCLK

ACMP-

ACMP+

ACMPO

(ICS)

(ACMP)

(MTIM)

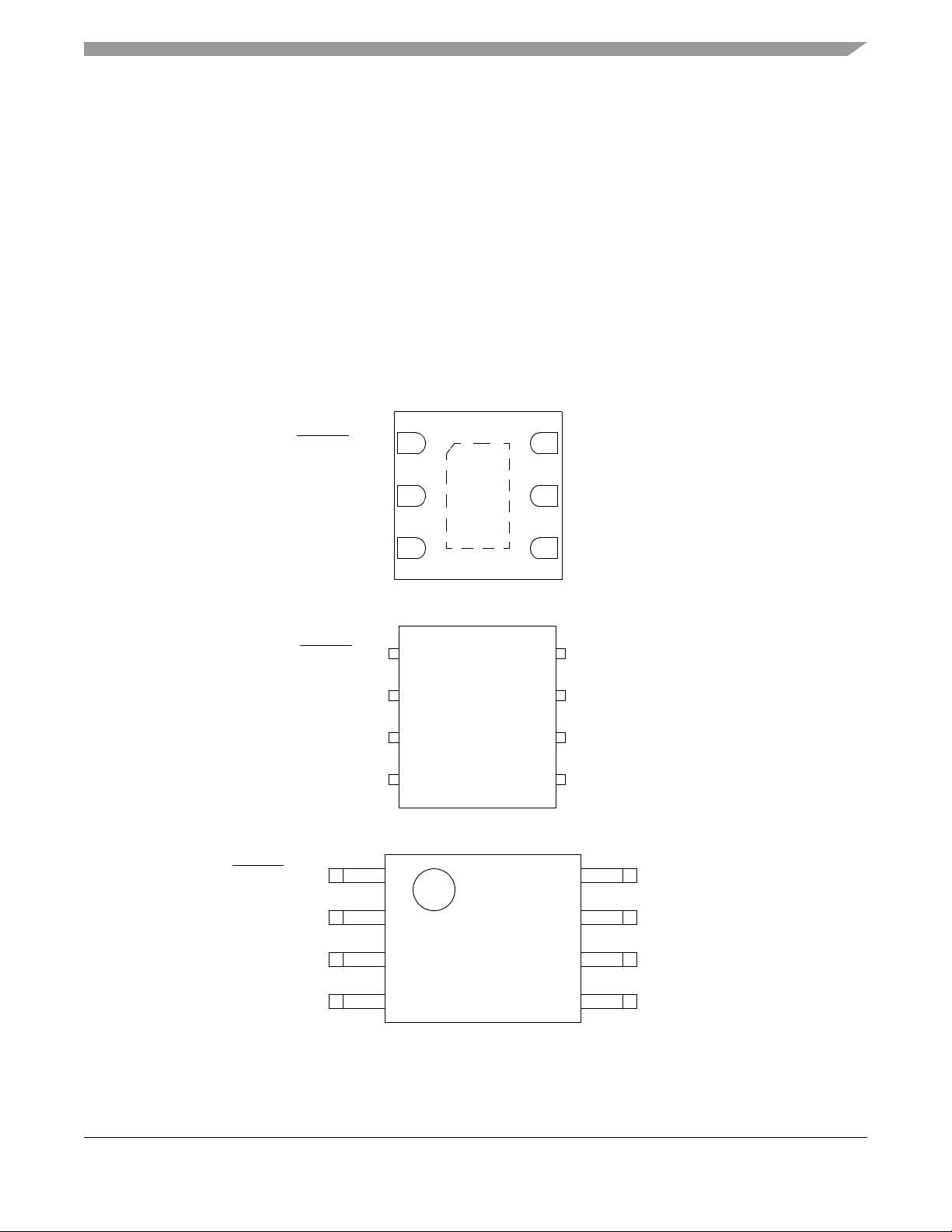

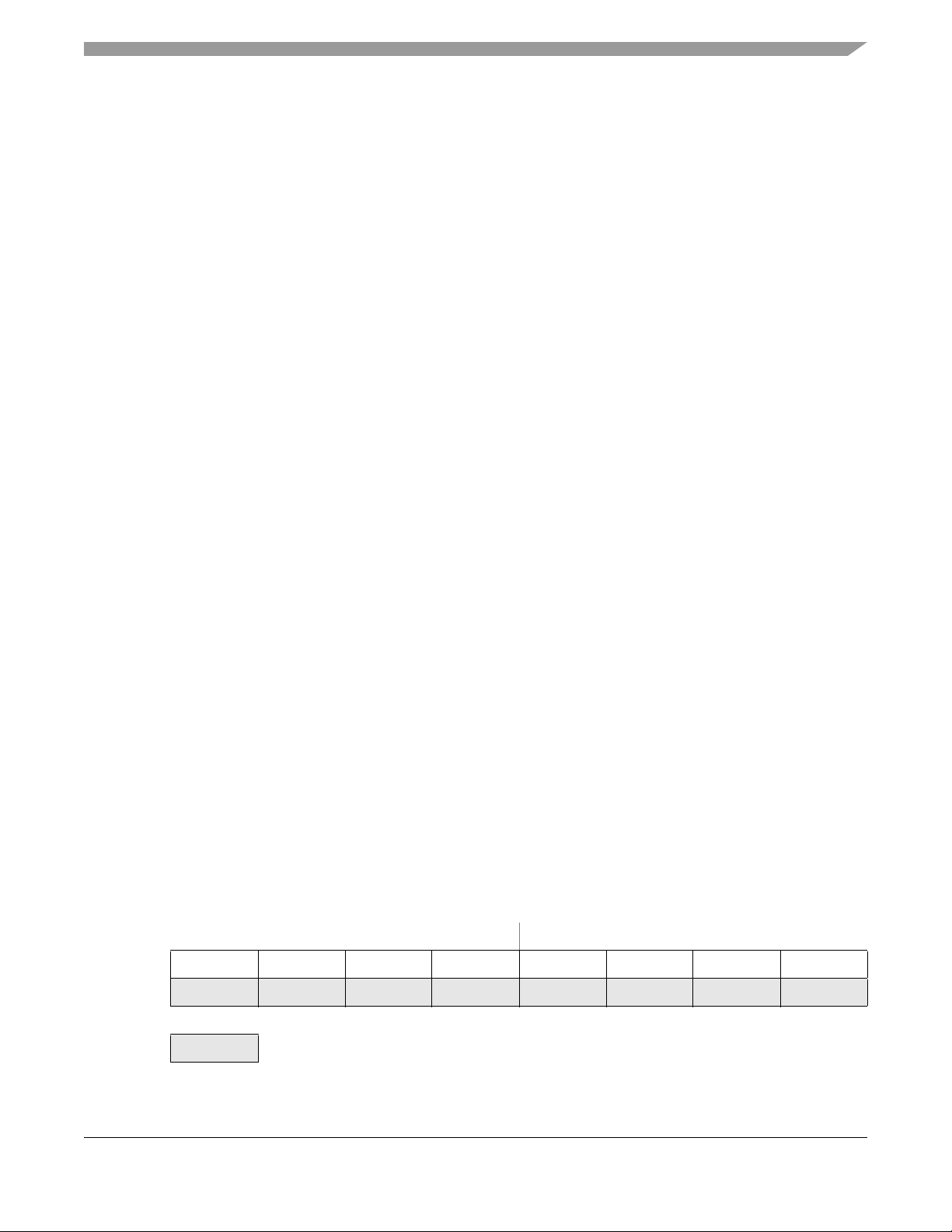

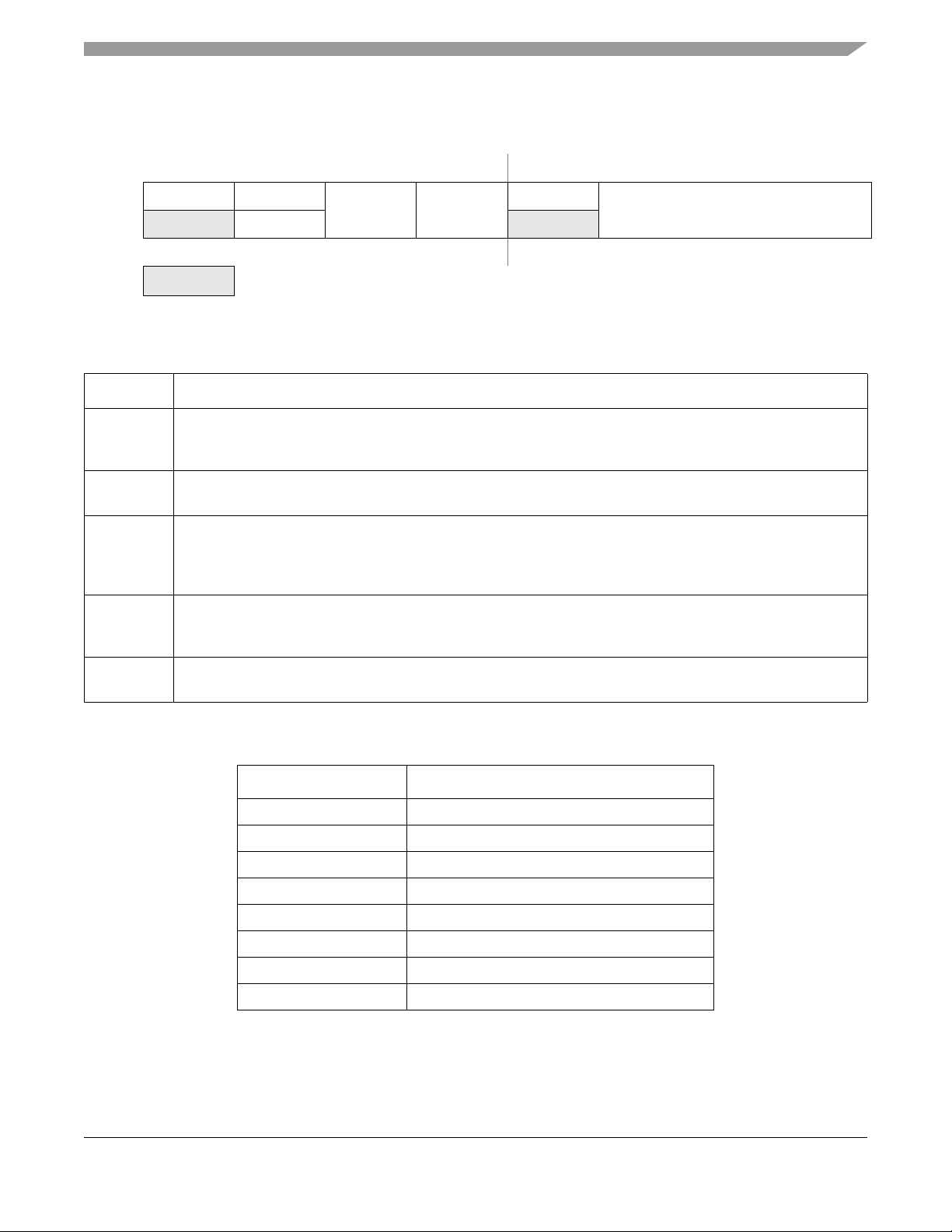

键盘中断 (RS08KBIV1)

7.1 介绍

键盘中断模块提供了独立的允许外部中断源。

7.1.1 特点

KBI 特点包括:

• 每个键盘中断管脚有一个独立的管脚允许位

• 每个键盘中断管脚可被编程作为只下降沿 ( 或上升沿 ) ,或既是下降沿又是低电平 ( 或既是上升沿又是

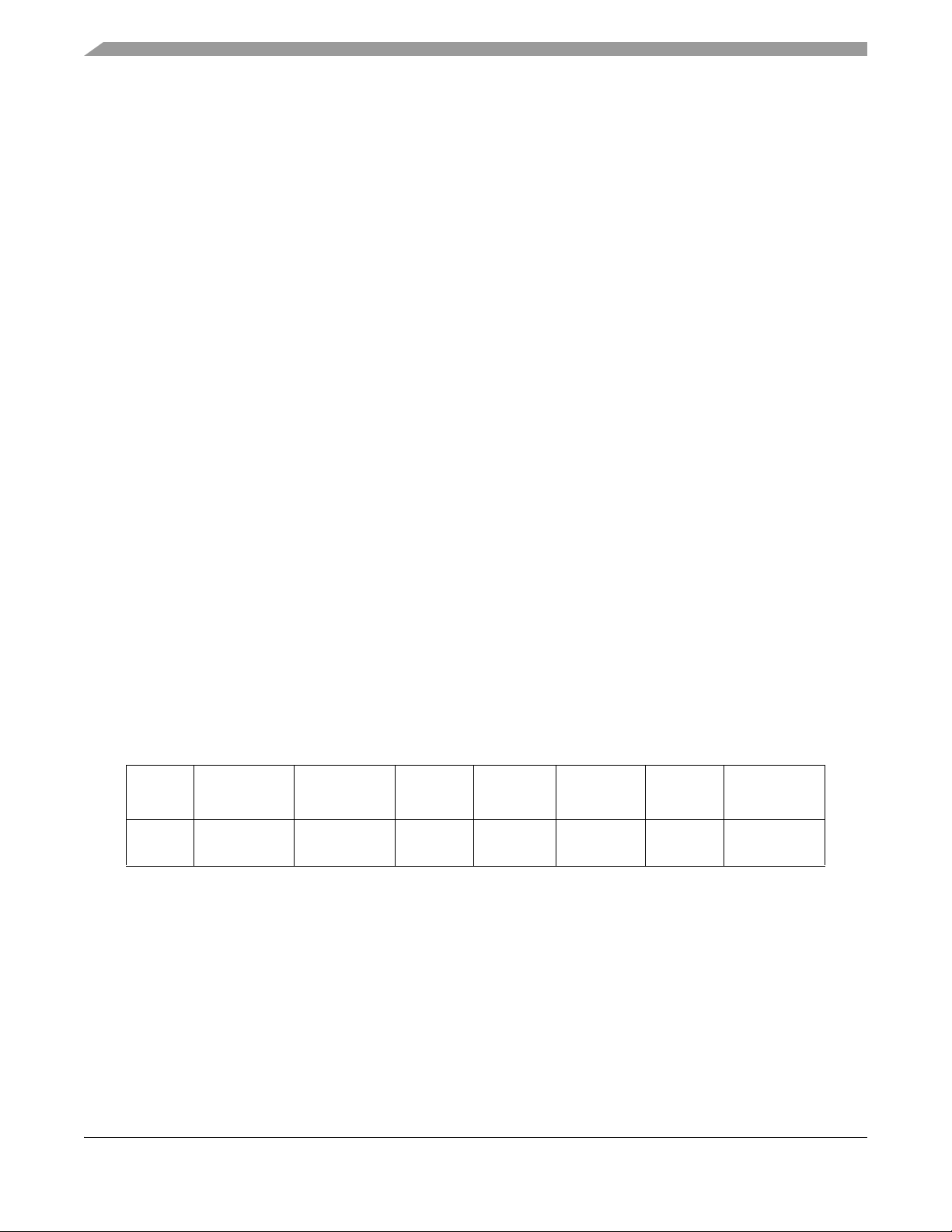

图 7-1. MC9RS08KA2 系列 Block Diagram with KBI Block and Pins Highlighted

高电平 ) 中断触发

• 一个软件允许键盘中断

• 从低功耗模式退出

飞思卡尔半导体 49

MC9RS08KA2 系列 数据手册 , 第 1 版

第 7 章 键盘中断 (RS08KBIV1)

DQ

CK

CLR

VDD

KBMOD

KBIE

KEYBOARD

INTERRUPT FF

KBACK

RESET

SYNCHRONIZER

KBF

STOP BYPASS

STOP

BUSCLK

KBIPEn

0

1

S

KBEDGn

KBIPE0

0

1

S

KBEDG0

KBIP0

KBIPn

KBI

INTERRU

PT

7.1.2 工作模式

此章定义了在等待、停止和后台调试模式下 KBI 工作。

7.1.2.1 等待模式下工作

假如执行 WAIT 指令之前被允许, KBI 在等待模式下可以继续工作。因此,假如 KBI 中断被允许 (KBIE =

1),一个被允许的 KBI 管脚 (KBPEn = 1) 可以用于将 MCU 退出等待模式。

7.1.2.2 停止模式下工作

假如执行 STOP指令前被允许,KBI 可以在停止模式工作。因此, 假如 KBI 中断允许 (KBIE = 1),一个允

许的 KBI 管脚 (KBPEn = 1) 能用于从停止模式唤醒 MCU 。

7.1.2.3 在活动后台模式下工作

当单片机工作在活动的后台模式, KBI 将继续正常工作。

7.1.3 方框图

键盘中断模块方框图如图 7-2 所示:

图 7-2. 键盘中断 (KBI) 方框图

7.2 外部信号描述

KBI 输入管脚可以用于检查下降沿,或既是下降沿又是低电平中断请求。 KBI 输入管脚也可以用于检查上

升沿,或既是上升沿有时高电平中断请求。

信号优先级见表 7-1。

表 7-1. 信号优先级

信号 功能

KBIPn

7.3 寄存器定义

KBI 包括三个寄存器:

• 一个 8 位管脚状态和控制寄存器

50 飞思卡尔半导体

键盘中断管脚

MC9RS08KA2 系列 数据手册 , 第 1 版

I/O

I

第 7 章 键盘中断 (RS08KBIV1)

• 一个 8 位管脚允许寄存器

• 一个 8 位边沿选择寄存器

参考第 4 章 存储器的直接页寄存器概要,包含所有 KBI 寄存器绝对地址分配。本节仅通过它们的名字涉

及到寄存器和控制位。

表 7-2 列出了 KBI 寄存器。

表 7-2. KBI 寄存器概述

Name

R0000KBF0

KBISC

W KBACK

R0 0

KBIPE

W

R0 0

KBIES

W

76543210

7.3.1 KBI 状态和控制寄存器 (KBISC)

KBISC 包含状态标志和控制位,用于配置 KBI。

76543210

R 0000KBF0

W KBACK

Reset:00000000

= Unimplemented

图 7-3. KBI 状态和控制寄存器 (KBISC)

KBIPE5 KBIPE4

KBEDG5 KBEDG4

KBIE KBMOD

0

KBIPE2 KBIPE1 KBIPE0

0

KBEDG2 KBEDG1 KBEDG0

KBIE KBMOD

表 7-3. KBISC 寄存器域描述

Field

3

KBF

2

KBACK

1

KBIE

0

KBMOD

飞思卡尔半导体 51

键盘中断标志 — KBF 指出有一个键盘中断被检测到。 对 KBF 写无效。

0 没有键盘中断被检测到

1 键盘中断被检测到

键盘应答 — 写一个 1 到 KBACK 是标志清除机制部分。读 KBACK 总是为 0 。

键盘中断允许 — KBIE 允许键盘中断请求

0 键盘中断请求不允许

1 键盘中断请求允许

键盘检测模式 — KBMOD ( 连同 KBEDG 位 ) 控制键盘中断管脚检测模式

0 键盘仅检测边沿

1 键盘既检测边沿又检测电平

MC9RS08KA2 系列 数据手册 , 第 1 版

描述

第 7 章 键盘中断 (RS08KBIV1)

7.3.2 KBI 管脚允许寄存器 (KBIPE)

KBIPE 包含管脚允许控制位。

76543210

R 00

KBIPE5 KBIPE4

W

Reset:00000000

图 7-4. KBI 管脚允许寄存器 (KBIPE)

表 7-4. KBIPE 寄存器域描述

0

KBIPE2 KBIPE1 KBIPE0

Field

5,4, 2:0

KBIPEn

键盘管脚允许 — 每个 KBIPEn 位允许相关的键盘中断管脚

0 相关管脚不允许作为键盘中断

1 相关管脚允许作为键盘中断

7.3.3 KBI 边沿选择寄存器 (KBIES)

KBIES 包含边沿选择控制位。

76543210

Field

5,4, 2:0

KBEDGn

R 00

W

Reset:00000000

键盘边沿选择 — 每个 KBEDGn 位选择下降沿 / 低电平或上升沿 / 高电平相关管脚的功能

0 下降沿 / 低电平

1 上升沿 / 高电平

KBEDG5 KBEDG4

图 7-5. KBI 边沿选择寄存器 (KBIES)

表 7-5. KBIES 寄存器域描述

描述

0

KBEDG2 KBEDG1 KBEDG0

描述

7.4 功能描述

此片内外设模块被称为键盘中断 (KBI)模块是因为 最初设计为了简化键盘开关行矩的连接和应用。然而,

这些输入也被用于作为额外外部中断输入和作为从停止或等待低功耗模式唤醒 MCU 的外部手段。

KBI 模块允许它的管脚担当附加的中断源。在键盘中断管脚允许寄存器 (KBIPE) 写 KBIPEn 位独立地允许

或禁止每个 KBI 管脚。 基于键盘中断状态和控制寄存器 (KBISC) 的 KBMOD 位,每个 KBI 管脚可以被配置位

边沿触发或边沿和电平触发 。边沿触发可以被软件编程上升沿或下降沿;电平是高或低。边沿极性或边沿和

电平触发的优先级通过键盘中断边沿选择寄存器 (KBIES) 的 KBEDGn 位选择。

异步逻辑用于检测边沿。检测一个边沿之前,允许键盘输入脚必须是被拉高的逻辑电平。当一个允许的

键盘输入信号被检测到在一个总线周期是逻辑 1 ( 被拉高的电平 ) 且在下个周期是逻辑 0 ( 拉低的电平 ) ,一个

下降沿被检测到。当输入信号被检测到在一个总线周期是逻辑 0 且下个周期是逻辑 1,上升沿被检测到。

MC9RS08KA2 系列 数据手册 , 第 1 版

52 飞思卡尔半导体

第 7 章 键盘中断 (RS08KBIV1)

7.4.1 仅边沿触发

在一个允许 KBI 管脚上的一次有效边沿将 KBISC 中的 KBF 位置 1。假如 KBISC 中的 KBIE 被置 1,中断

请求将被送到 CPU。通过写一个 1 到 KBISC 的 KBACK 位实现将 KBF 清零。

7.4.2 边沿和电平触发

在一个允许 KBI 管脚上的一次有效边沿或电平将 KBISC 中的 KBF 位置 1。假如 KBISC 中的 KBIE 被置

1,中断请求将被送到 CPU。倘若所有允许键盘输入管脚是被拉为高电平,通过写一个 1 到 KBISC 的

KBACK 位实现将 KBF 清零。写 1 到 KBACK 试图将 KBF 清零时,假如允许 KBI 管脚被拉低为低电平, KBF

将保持为 1。

7.4.3 KBI 上拉 / 下拉设备

当一个 KBI 管脚被使能, KBI 管脚不会自动配置内部上拉 / 下拉设备。通过配置相关联的 I/O 端口拉设备

允许寄存器和上拉 / 下拉控制寄存器 (PTAPUD) 内部拉设备被使用。

7.4.4 KBI 初始化

当一个键盘中断管脚刚开始被允许使用时,可能会产生一个错误的键盘中断标志。在键盘初始化时为了

避免错误的中断请求产生,用户应该按照以下步骤:

1. 将 KBISCM 中的 KBIE 为清零屏蔽键盘中断。

2. 假如使用内部上拉 / 下拉设备,配置相关联的 I/O 端口上拉 / 下拉设备 。

3. 通过设置 KBIES 中合适的 KBEDGn 位使能 KBI 优先级。

4. 通过设置 KBIPE 中合适的 KBIPEn 位使能 KBI 管脚。

5. 写 1 到 KBISC 中的 KBACK 位清除任何错误中断。

6. 将 KBISC 中的 KBIE 位置 1 允许中断 。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 53

第 7 章 键盘中断 (RS08KBIV1)

MC9RS08KA2 系列 数据手册 , 第 1 版

54 飞思卡尔半导体

第 8 章

PC

SPC

CARRY

ZERO

0

0

0

7

13

13

ACCUMULATOR

A

SHADOW PROGRAM COUNTER

87

PROGRAM COUNTER

CCR

CZ

CONDITION CODE REGISTER

中央处理器单元 (RS08CPUV1)

8.1 介绍

本章是 RS08 家族 CPU 的寄存器、寻址模式和指令集等信息介绍。更详细讨论参考 RS08 核参考手册第

一卷,飞思卡尔半导体文档单号 RS08RMv1。

RS08 CPU 被开发的目的是极低成本的嵌入式应用 ,用于一个独立处理的设计方法,允许它在半导体处

理技术快速发展步调保持一至。

RS08 核的主要特点是:

• 改进型的编程模型

• HCS08 指令集的子集 ,较少扩展指令

• 很小的指令集适用于价格敏感的嵌入式应用

• 用于屏蔽程序计数器处理的新指令, SHA 和 SLA

• 新的短型和小型寻址方式用于代码大小优化

• 最多 16K 字节存储器空间

• 复位将从 $3FFD 取出首条指令

• STOP 和 WAIT 指令支持低功耗模式

• 调试和 FLASH 编程支持使用后台调试控制器模块

• 非法地址和代码被检测导致复位

8.2 程序设计器模型和 CPU 寄存器

图 8-1 列出了 RS08 CPU 的程序设计器模型。这些寄存器不是位于微处理器的存储器中。它们直接建立

在 CPU 逻辑内部。

飞思卡尔半导体 55

MC9RS08KA2 系列 数据手册 , 第 1 版

图 8-1. CPU 寄存器

第 8 章 中央处理器单元 (RS08CPUV1)

07

07

07

INDEXED DATA REGISTER

D[X] (Œª”⁄$000E)

INDEX REGISTER

X (Œª”⁄ $000F)

PAGE SELECT REG

PAGESEL (Œª”⁄ $001F)

除 CPU 寄存器外,在数据读写操作期间,有三个存储器映象寄存器与内核地址产生紧紧联合在一起。它

们是变址数据寄存器 (D[X]),变址寄存器 (X) 和页选择寄存器 (PAGESEL)。这些寄存器地址分别位于

$000E、 $000F 和 $001F。

图 8-2. Memory Mapped Registers

累加器 (A)

此通用 8 位寄存器是 RS08 MCUs 的基本数据寄存器。通过一条装载累加器 (LDA) 指令数据能从存储器

被写入 A 。通过一条存储累加器 (STA) 指令在 A 中的数据可以被写入存储器。在指定存储器位置涉及到装载

或存储指令时不同的寻址方式变化,允许有很大的灵活性。交换指令允许值在 A 和 SPC 高 (SHA) 之间, A 和

SPC 低 (SLA) 之间交换。

通过 ADD, SUB, RORA, INCA, DECA, AND, ORA, EOR等指令, A 的值可以实现算术、位移和逻辑操

作。在一些指令中,例如 INCA 和 LSLA, A 的值是唯一的输入操作数且结果替换 A 的值。其它一些指令,例

如 ADD 和 AND,有两个操作数: A 的值和来自存储器的第二个数值。这些算术或逻辑运算的结果替代 A 的

值。

一些指令,例如存储器对存储器移动指令 (MOV),不能使用累加器。 DBNZ 也不用 A ,原因是它允许一

个循环计数器被执行在存储器中而不是累加器。

复位后,累加器被装载入 $00。

8.2.1 程序计数器 (PC)

程序计数器是一个 14 位的寄存器,它包含了下条指令或被取出的操作数的地址。

正常执行时,每次执行一条指令或取出操作数,程序计数器自动增加指向下个时序存储器位置。跳转、

分枝和返回操作载入程序计数器的地址不是下个时序存储器位置。这被称为流动改变。

复位期间,程序计数器被载入 $3FFD 且程序从这个指定位置开始执行。

8.2.2 影子程序计数器 (SPC)

影子程序计数器是一个 14 位寄存器。在子程序调用期间使用 JSR 或 BSR 指令,返回地址将被存入

SPC。在子程序完成前, RTS 指令将恢复程序计数器的内容,此值来自于 SPC。

复位期间,屏蔽程序计数器被载入 $3FFD。

56 飞思卡尔半导体

MC9RS08KA2 系列 数据手册 , 第 1 版

第 8 章 中央处理器单元 (RS08CPUV1)

CARRY

ZERO

CCR

CZ

条件代码寄存器

8.2.3 条件代码寄存器 (CCR)

2 位条件代码寄存器包含两个状态标志。 RS08 中 CCR 内容不是直接地被读出的。使用条件分枝指令例

如 BCC 和 BEQ 测试 CCR 位。寄存器的这两位直接受 BDC 接口影响。后面段落提供了关于 CCR 位详细信

息和如何使用它们。图 8-3 表明了 CCR 位和它们位的位置。

图 8-3. 条件代码寄存器 (CCR)

复位后状态位 (Z 和 C) 被清零。

这两个状态位显示了算术和其它指令的结果。条件转移指令将转移到一个新的程序位置或转移后依靠

CCR 状态位的值允许程序继续执行下条指令。条件转移指令,例如 BCC、 BCS 和 BNE,依靠一个单一的

CCR 位的值产生一个转移。

通常,条件转移立即跟随导致 CCR 位被更新的指令,如下面的顺序::

cmp #5 ; 比较累加器 A 和 5

blo lower ; 假如 A 小于 5 则转移

more: deca ; 假如 A 大于或等于 5 执行这行指令

lower:

在使用的指令没有扰乱 CCR 的影响条件转移的位的时候,其它指令也许在校验和条件转移之间被执行。

举例说明,一个校验在子程序或函数中被执行,条件转移直到子程序返回到主程序后才会被执行。这是个参数

传输的形成 ( 换句话说,在条件码位内信息被返回到调用的程序 )。

Z — 零标志

Z 位被置 1 表明一个操作结果是 $00。

假如等于 (BEQ) 则转移和假如不等于 (BNE) 则转移是简单的转移,此转移依赖于 Z 位的值。所有装

载、存储、移动、算术、逻辑、移位和旋转指令都会导致 Z 位被更新。

C — 进位

一个加法运算后,假如源操作数大于或等于 $80 或者操作数中的任何一个数大于或等于 $80 并且结果

小于 $80, C 位被置 1。这相当于无符号溢出。 一个存储器操作数作为被减数减去或比较一个 CPU 寄

存器的内容,减法操作后,假如存储器中无符号值大于 CPU 寄存器的无符号值 C 位被置 1。这相当于

一个无符号借入或下溢。

假如进位清零 (BCC) 则转移和进位置 1(BCS) 则转移是基于 C 位值独立的转移。 C 位也被用于无符号

转移 BLO 和 BHS。加、减、位移和旋转指令都会导致 C 位被更新。假如位置 1 (BRSET) 则转移和位

清零 (BRCLR) 则转移指令拷贝测试位到 C 位易于有效的串行转并行运算法则。 置进位 1(SEC) 和清零

进位 (CLC) 允许进位被直接置 1 或清零。结合位移和旋转指令这是很有用的,适合于通过状态信息返

回到主程序的子程序。

C 位包含在位移和旋转操作中因此这些操作可以很容易地扩展到多字节操作。移位和旋转操作被当作

9 位移位,包含一个 8 位操作数或 CPU 寄存器和 CCR 的进位。一个逻辑位移后, C 保存被移位出的

操作数的第 8 位。假如下次执行旋转指令, C 位被移入操作数,操作数最后一位移出代替 在 CI 中的

值。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 57

第 8 章 中央处理器单元 (RS08CPUV1)

8.2.4 变址数据寄存器 (D[X])

8 位变址数据寄存器允许用户访问在通过 X 被变址的直接页地址空间的数据。这个寄存器位于存储器映象

地址 $000E。关于 For D[X] 寄存器详细介绍,参考 8.3.8 节 变址寻址方式 (IX, 被伪指令执行 )。

8.2.5 变址寄存器 (X)

8 位变址寄存器允许用户索引或访问在直接页地址空间的任何地址。此寄存器位于存储器映象地址

$000F。关于 X 寄存器详细介绍,参考 8.3.8 节 变址寻址方式 (IX, 被伪指令执行 )。

8.2.6 页选择寄存器 (PAGESEL)

8 位页选择寄存器允许用户通过一个地址从 $00C0 到 $00FF 页窗口访问整个 16K 地址空间的所有存储器

地址。此寄存器位于存储器映象地址 $001F。关于 PAGESEL 寄存器详细信息,请参考 “the RS08 Core

Reference Manual”。

8.3 寻址方式

只要 MCU 读写存储器信息,一个寻址方式用于确定读写信息存储器的准确地址。本节介绍了几种寻址方

式和在不同编程情况下每种如何使用。

每种操作码都会告诉 CPU 通过某种方式执行某一种操作。许多指令,例如载入累加器 (LDA),允许几种

不同的方法指定存储器位置被载入,且每种寻址方式的变化需要独立的操作码。 所有这些变化使用相同指令助

记符号,且汇编程序依靠操作数域的语法和位置知道使用哪种操作码。在一些案例,一些特殊的字符用于表明

一种特殊的寻址方式 ( 例如 # [pound] 符号,表明立即数寻址方式 ). 在其它一些案例,操作数的值会告诉汇编

程序使用哪种寻址方式。例如,假如操作数地址从 $0000 到 $001F,汇编程序选择短地址方式代替直接寻址

方式。除允许汇编程序基于操作数地址选择寻址方式外,汇编程序也可以通过在操作数前使用 “>” 或 “<” 前缀

强迫为直接或小 / 短寻址方式。一些指令使用不止一种寻址方式。例如,移动 指令使用第一种寻址方式访问

存储器源值和第二种寻址方式访问目的存储器位置。对于这些移动指令,两种寻址方式在文档里都被列出。所

有跳转指令使用相对 (REL) 寻址方式确定跳转的目的地。但 BRCLR、 BRSET、 CBEQ 和 DBNZ 也必须访问

一个存储器操作数。这些指令通过用于存储器操作数的寻址方式被分类。

下面段落包含每个寻址方式如何工作和用于特别的寻址方式的汇编指令的语法。

8.3.1 隐含寻址方式 (INH)

此寻址方式用于当 CPU 内在地知道每件事情它必须完成的指令和在源代码没有寻址信息的时候。通常,

CPU 需要的操作数位于 CPU 的内部寄存器,例如 LSLA, CLRA, INCA, SLA, RTS 和其它指令。少数隐含指

令,包括空操作 (NOP) 和后台 (BGND),没有操作数。

8.3.2 相对寻址方式 (REL)

相对寻址方式用于指定跳转指令的偏移地址给程序计数器。典型地,程序员用一个标签或在跳转指令操

作数域用表达式指明目的地;汇编器计算位置计数器 ( 在跳转指令后指向下个地址 ) 和通过标签或操作数域表

达式表明的地址之间的差别,这个差被称为偏移量且是一个 8 位双符号补数。汇编器存储这个偏移量在跳转

指令的结果代码内。

MC9RS08KA2 系列 数据手册 , 第 1 版

58 飞思卡尔半导体

第 8 章 中央处理器单元 (RS08CPUV1)

在执行过程中, CPU 评价控制跳转的条件。假如跳转条件是真, CPU 信号扩展偏移量为一个 14 位的

值,将偏移量加到当前的 PC 中,使用它作为地址获取下条指令和继续执行,而不是执行跳转指令后面的指

令。由于偏移量是一个 8 位双符号补数,目的地必须在跳转指令结果代码地址从 –128 到 +127 地址范围内。

设计一个简单死循环的通用的方法是用一个跳转指令跳转到它自己。此方法有时用于在调试期间结束短

的代码段。典型地,为了跳出死循环,使用调试主机 ( 通过后台命令 ) 停止程序,检查寄存器和存储器,或从

一个新地址开始执行。 此结构不用在正常的应用程序,除非程序检查到一个错误,想强迫看门狗定时器溢出 (

在死循环中跳转反复执行直到看门狗定时器导致复位 )。

8.3.3 立即数寻址方式 (IMM)

在这种寻址方式中,操作数直接位于操作码后面。此寻址方式用于当程序员希望在某个时候程序被写入

一个已知的确定的值。 # ( 磅 ) 符号告诉汇编器使用的操作数作为一个数据而不是一个地址。

立即操作数大小总是 8 位。汇编器会自动切去或扩展需要的操作数与指令所需要的大小相匹配。假如提

供一个 16 位操作数,大多数汇编器将产生一个警告。

当使用立即数寻址时使用 # 符号告诉汇编器是程序员的职责。汇编器不会认为它是个错误或停止 # 符号,

因为声明结果依然是一个合法的指令 ( 尽管它可能意味与预订的程序有些不同 )。

8.3.4 小型寻址方式 (TNY)

TNY 寻址方式仅有能力寻址地址映象中的头 16 个字节,从 $0000 到 $000F。此寻址方式适合于 INC、

DEC、 ADD 和 SUB 指令。通过放置大部分精确计算的数据在这个存储器范围,系统可以被最优化。

由于在操作码中嵌入的是 4 位地址,仅有效的 4 位直到必须包含在指令中;这节省了程序空间和执行时

间。在执行过程中, CPU 增加高 10 位到 4 位操作数地址,结合成 14 位地址 ($000x) 访问预定的操作数。

8.3.5 短型寻址方式 (SRT)

SRT 寻址方式仅有能力寻址地址映象中的头 32 个字节,地址从 $0000 到 $001F。此寻址方式适用于

CLR、 LDA和 STA 指令。通过放置大部分精确计算的数据在这个存储器范围,系统可以被优化。

由于 5 位地址被嵌在操作码中,仅需有效的 5 位地址包含在指令中;这节省了程序空间和执行时间。在

执行期间, CPU 增加高 9 位到 5 位操作数地址,结合成 14 位地址 ($000x 或 $001x) 用于访问预订的操作数。

8.3.6 直接寻址方式 (DIR)

DIR 寻址方式用于访问位于直接地址空间 ($0000 through $00FF) 的操作数。

在执行期间, CPU 增加高 6 位到跟随操作码的直接地址操作数的低字节。 CPU 使用结合的 14 位地址

($00xx) 访问预定的操作数。

8.3.7 扩展寻址方式 (EXT)

在扩展寻址方式,操作数的 14 位地址包含在目标代码中,目标代码位于操作码后两个字节的低 14 位。

RS08 MCU 系列中此寻址方式仅被用于 JSR 和 JMP 指令用于跳转到目的地。

8.3.8 变址寻址方式 (IX, 被伪指令执行 )

变址寻址方式有时也被称为间接寻址方式,原因是变址寄存器被作为访问预定操作数的参考。

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 59

第 8 章 中央处理器单元 (RS08CPUV1)

变址寻址方式一个重要的特征是在执行期间,操作数地址被计算是基于在存储器映象 $000F 位置的 X 变

址寄存器的内容,而不是在程序汇编时确定的一个常数地址。这允许编程写可以依靠之前程序指令的结果访问

不同的操作数地址位置 ( 而不是访问程序被写时确定的地址位置 )。

RS08 家族使用地址位于 $000F 的寄存器 X 作为一个变址和地址位于 $000E 的 D[X] 寄存器作为变址数

据寄存器支持变址寻址方式。通过编程变址寄存器 X,直接页内的任何位置都可以通过变址数据寄存器 D[X]

读/写。

通过使用 D[X]作为操作数,这些伪指令可以被用于所有支持直接、短型和小型寻址方式的指令。

8.4 特殊操作

大部分 CPU 操作可以通过指令集描述,但是有些特殊的操作必须被考虑,例如上电后 CPU 如何开始执

行应用程序的。程序开始运行后,当前正常的指令明确 CPU 下一步做什么。两种意外事件会导致 CPU 临时

延缓正常程序执行:

• 复位事件强迫 CPU 工作在应用程序之初的前面,强迫从 $3FFD 地址开始执行。

• 一个主设备系统可以导致 CPU 转到后台模式而不是继续执行应用程序的下条指令。

8.4.1 复位顺序

程序开始于复位事件之后。产生复位事件的事情可以从一个到另一个变化。然而,大部分普通源是:上

电复位,外部 RESET

MCU 如何辨别复位事件和区分内部和外部导致复位的不同之处,更多的信息参考 复位和中断 章。

脚,低电压检测复位, COP 看门狗定时溢出,非法操作码检测,非法地址访问。关于

复位事件强迫 MCU 立即停止它正在做的工作,开始响应复位。在执行中的任何指令被立即异常中断,不

会完成任何剩余的时钟周期。一各短的工作次序是判定复位源是内部还是外部并记录导致复位的原因。在这残

余时间,复位源保持工作状态,内部时钟停止以节省功耗。在复位事件后期,时钟恢复, CPU 从复位状态退

出。在复位后,程序计数器复位指向地址 $3FFD,一条指令被取出开始执行。

复位后从 $3FFD 开始执行代码。注意不要强迫 BKDG 管脚在复位后被拉低,这将导致进入后台模式,

CPU 将等待从后台通讯接口传来的命令。

8.4.2 中断

RS08 的中断机制没有用于中断正常的指令流程;它用于从等待和停止模式唤醒 RS08。在正常工作模

式,中断事件必须被 CPU 记录。中断的特性与飞思卡尔的 HC05, HC08 或 HCS08 系列不兼容。

8.4.3 等待和停止模式

执行一条 WAIT 或 STOP 指令进入等待或停止模式。在这些模式, CPU 的时钟被关闭以节省功耗且 CPU

停止工作。 CPU 保持低功耗状态。直到一个中断或复位事件唤醒。关于等待和停止对其它外设的影响请参考

复位和中断章

8.4.4 工作后台模式

工作后台模式涉及到 CPU 已经停止执行用户程序指令并等待后台调试系统的串行命令。工作后台模式更

详细信息参考 开发支持章。

MC9RS08KA2 系列 数据手册 , 第 1 版

60 飞思卡尔半导体

8.5 指令表摘要

指令集摘要术语

列出的术语通过表 8-2 用于表 8-1 中的指令描述。

操作数

( ) = 圆括号内显示的是寄存器和存储单元内容

← = 被载入 ( 读:“得到” )

⇔ = 与 ... 交换

&=布尔与

|=布尔或

⊕ = 布尔异或

:=连接

+=加

CPU 寄存器

A=累加器

CCR = 条件代码寄存器

PC = 程序计数器

PCH = 程序计数器,更高顺序 ( 最高有效 ) 六位

PCL = 程序计数器,更低顺序 ( 最低有效 ) 八位

SPC = 影子程序计数器

SPCH = 影子程序计数器,更高顺序 ( 最高有效 ) 六位

SPCL = 影子程序计数器,更低顺序 ( 最低有效 ) 八位

第 8 章 中央处理器单元 (RS08CPUV1)

存储器和寻址方式

M=A 存储器地址或绝对数据,依靠寻址方式

rel = 相对偏移量,它是存储在相对一条分枝指令的机器代码最好字节内的两个补

数。

X=伪变址寄存器,存储单元 $000F

X or D[X] = 存储单元 $000E 指向被伪变址寄存器 ( 位于 $000F) 定义的存储单元

条件代码寄存器 (CCR) 位

Z=零标志器

C=进位/借位

CCR 行为符号

–=位不受影响

0=位强迫为 0

1=位强迫为 1

¦ = 依据操作结果,位置位或清零

U=操作后未定义

机器代码符号

dd = 一个直接地址 $0000–$00FF ( 高字节假定是 $00) 的低顺序八位

ii = 一个立即数字节

MC9RS08KA2 系列 数据手册 , 第 1 版

飞思卡尔半导体 61

第 8 章 中央处理器单元 (RS08CPUV1)

hh = 前缀2位为0的14位扩展地址的高顺序 6 位

ll = 14 位扩展地址的低顺序 8 位

rr = 相对偏移量

源表格

在源表格栏内的每个信息,是字面上的信息,它必须出现在精确显示的汇编源文件。头 3 到 5 个字母助

记符总是一个文字表达式。所有逗号,磅符 (#) 和加号 (+) 字面符号。

n — 任何标签或表达式用于表示一个在 0–7 范围内的单整型

x — 任何标签或表达式用于表示一个在 $0–$F 范围内的简单十六进制的整型。

opr8i — 任何标签或表达式用于表示一个 8 位立即数值。

opr4a — 任何标签或表达式用于表示一个小型地址 (4 位数值 )。指令对待这 4 位数值作为

在 16K 字节地址空间 ($0000–$000F) 的低四位。这 4 位数值被放入操作码内的

低四位。

opr5a — 任何标签或表达式用于表示一个短型地址 (5 位数值 )。指令对待这 5 位数值作为

在 16K 字节地址空间 ($0000–$001F) 的低五位。这 5 位数值被放入操作码内的

低五位。

opr8a — 任何标签或表达式用于表示一个8位数值。指令对待这8位数值作为在16K字节地

址空间 ($0000–$00FF) 的低八位。

opr16a — 任何标签或表达式用于表示一个 14 位数值。在 RS08 内核,头两位总是为 0。指

令对待这 16 位数值作为在 16K 字节地址空间。

rel — 在当前指令的目标代码的最后字节之后,任何标签或表达式涉及在 –128 to

+127 内来自下个地址的一个地址。汇编器将计算这 8 位有符号偏移量和算入它

在这条指令的目标代码内。

寻址方式

INH = 隐含 ( 没有操作数 )

IMD = 立即数到直接 ( 在 MOV 指令内 )

IMM = 立即数

DD = 直接到直接 ( 在 MOV 指令内 )

DIR = 直接

SRT = 短型