查询MC908QF4CFJ供应商

..

.

Freescale Semiconductor, Inc.

MC68HC908QF4

nc

Freescale Semiconductor, I

M68HC08

Microcontrollers

Data Sheet

MC68HC908QF4

Rev. 1.0

6/2004

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

MC68HC908QF4

Data Sheet

To provide the most up-to-date information, the revision of our documents on the

World Wide Web will be the most current. Your printed copy may be an earlier

nc...

I

revision. To verify you have the latest information available, refer to:

http://motorola.com/semiconductors/

cale Semiconductor,

Frees

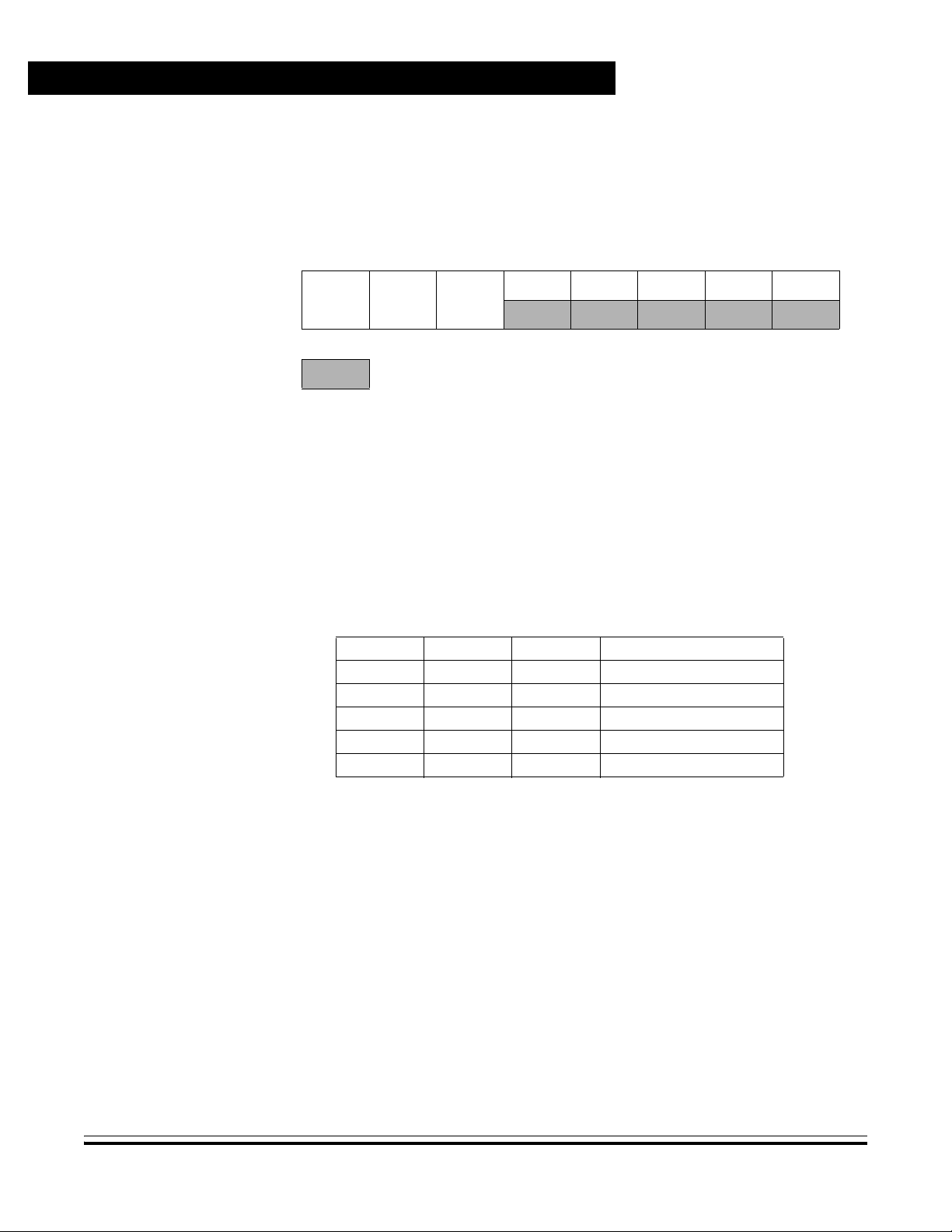

The following revision history table summarizes changes contained in this

document. For your convenience, the page number designators have been linked

to the appropriate location.

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA 3

For More Information On This Product,

Go to: www.freescale.com

Revision History

Freescale Semiconductor, Inc.

Revision History

Date

October,

2003

June,

2004

nc...

I

Revision

Level

N/A Initial release N/A

Removed references to MC68HC908QF3, MC68HC908QF2, and

MC68HC908QF1

1.0

17.4 Thermal Characteristics — Updated 32-pin TQFP value 176

18.2 MC Order Numbers — Updated table entries for MC order numbers 193

Description

cale Semiconductor,

Page

Number(s)

Throughout

Frees

Data Sheet MC68HC908QF4 — Rev. 1.0

4 Revision History MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Data Sheet — MC68HC908QF4

Section 1. General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Section 2. Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Section 3. Analog-to-Digital Converter (ADC) . . . . . . . . . . . . . . . . . . .37

Section 4. Auto Wakeup Module (AWU) . . . . . . . . . . . . . . . . . . . . . . . .45

List of Sections

nc...

I

cale Semiconductor,

Frees

Section 5. Configuration Register (CONFIG) . . . . . . . . . . . . . . . . . . . .51

Section 6. Computer Operating Properly (COP) . . . . . . . . . . . . . . . . .55

Section 7. Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . .59

Section 8. External Interrupt (IRQ) . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Section 9. Keyboard Interrupt Module (KBI) . . . . . . . . . . . . . . . . . . . .79

Section 10. Low-Voltage Inhibit (LVI) . . . . . . . . . . . . . . . . . . . . . . . . . .87

Section 11. Oscillator Module (OSC). . . . . . . . . . . . . . . . . . . . . . . . . . .91

Section 12. PLL Tuned UHF Transmitter Module. . . . . . . . . . . . . . . .101

Section 13. Input/Output (I/O) Ports . . . . . . . . . . . . . . . . . . . . . . . . . .111

Section 14. System Integration Module (SIM) . . . . . . . . . . . . . . . . . .119

Section 15. Timer Interface Module (TIM). . . . . . . . . . . . . . . . . . . . . .137

Section 16. Development Support. . . . . . . . . . . . . . . . . . . . . . . . . . . .155

Section 17. Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . .175

Section 18. Ordering Information and Mechanical

Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA List of Sections 5

For More Information On This Product,

Go to: www.freescale.com

List of Sections

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Data Sheet MC68HC908QF4 — Rev. 1.0

6 List of Sections MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Data Sheet — MC68HC908QF4

Table of Contents

Section 1. General Description

1.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.3 MCU Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.4 Pin Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.5 Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

nc...

I

Section 2. Memory

cale Semiconductor,

Frees

2.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.2 Unimplemented Memory Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.3 Reserved Memory Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.4 Input/Output (I/O) Section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.5 Random-Access Memory (RAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.6 FLASH Memory (FLASH). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.6.1 FLASH Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.6.2 FLASH Page Erase Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.3 FLASH Mass Erase Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.6.4 FLASH Program Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.6.5 FLASH Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.6.6 FLASH Block Protect Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.6.7 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.6.8 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Section 3. Analog-to-Digital Converter (ADC)

3.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.3.1 ADC Port I/O Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.3.2 Voltage Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.3.3 Conversion Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.3.4 Continuous Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.3.5 Accuracy and Precision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Table of Contents 7

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

Freescale Semiconductor, Inc.

3.5 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.5.1 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.6 Input/Output Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.7 Input/Output Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.7.1 ADC Status and Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.7.2 ADC Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.7.3 ADC Input Clock Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Section 4. Auto Wakeup Module (AWU)

4.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

nc...

I

cale Semiconductor,

Frees

4.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

4.4 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.5 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.6 Input/Output Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.6.1 Port A I/O Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.6.2 Keyboard Status and Control Register. . . . . . . . . . . . . . . . . . . . . . . 48

4.6.3 Keyboard Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . 49

Section 5. Configuration Register (CONFIG)

5.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Section 6. Computer Operating Properly (COP)

6.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6.3 I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

6.3.1 BUSCLKX4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

6.3.2 STOP Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

6.3.3 COPCTL Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

6.3.4 Power-On Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

6.3.5 Internal Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

6.3.6 COPD (COP Disable). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.3.7 COPRS (COP Rate Select) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.4 COP Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.6 Monitor Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Data Sheet MC68HC908QF4 — Rev. 1.0

8 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

6.7 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.7.1 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.7.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

6.8 COP Module During Break Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table of Contents

Section 7. Central Processor Unit (CPU)

7.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

7.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

7.3 CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

7.3.1 Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

7.3.2 Index Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

7.3.3 Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

nc...

I

7.3.4 Program Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

7.3.5 Condition Code Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

7.4 Arithmetic/Logic Unit (ALU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

cale Semiconductor,

Frees

7.5 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

7.5.1 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

7.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

7.6 CPU During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

7.7 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

7.8 Opcode Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Section 8. External Interrupt (IRQ)

8.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

8.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

8.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

8.4 IRQ

8.5 IRQ Module During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

8.6 IRQ Status and Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Section 9. Keyboard Interrupt Module (KBI)

9.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

9.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

9.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

9.3.1 Keyboard Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

9.3.2 Keyboard Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

9.4 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

9.5 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Table of Contents 9

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

9.6 Keyboard Module During Break Interrupts. . . . . . . . . . . . . . . . . . . . . . . 83

9.7 Input/Output Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

9.7.1 Keyboard Status and Control Register. . . . . . . . . . . . . . . . . . . . . . . 84

9.7.2 Keyboard Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . 85

Section 10. Low-Voltage Inhibit (LVI)

10.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

10.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

10.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

10.3.1 Polled LVI Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

10.3.2 Forced Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

10.3.3 Voltage Hysteresis Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

10.3.4 LVI Trip Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

10.4 LVI Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

cale Semiconductor,

Frees

10.5 LVI Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

10.6 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

10.6.1 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

10.6.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Section 11. Oscillator Module (OSC)

11.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

11.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

11.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

11.3.1 Internal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

11.3.1.1 Internal Oscillator Trimming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

11.3.1.2 Internal to External Clock Switching . . . . . . . . . . . . . . . . . . . . . . . 93

11.3.2 External Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

11.3.3 XTAL Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

11.3.4 RC Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

11.4 Oscillator Module Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

11.4.1 Crystal Amplifier Input Pin (OSC1). . . . . . . . . . . . . . . . . . . . . . . . . . 95

11.4.2 Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4). . . . . . . . . . 96

11.4.3 Oscillator Enable Signal (SIMOSCEN). . . . . . . . . . . . . . . . . . . . . . . 96

11.4.4 XTAL Oscillator Clock (XTALCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . 96

11.4.5 RC Oscillator Clock (RCCLK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

11.4.6 Internal Oscillator Clock (INTCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . 97

11.4.7 Oscillator Out 2 (BUSCLKX4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

11.4.8 Oscillator Out (BUSCLKX2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

11.5 Low Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

11.5.1 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

11.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Data Sheet MC68HC908QF4 — Rev. 1.0

10 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

11.6 Oscillator During Break Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

11.7 CONFIG2 Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

11.8 Input/Output (I/O) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

11.8.1 Oscillator Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

11.8.2 Oscillator Trim Register (OSCTRIM) . . . . . . . . . . . . . . . . . . . . . . . . 99

Table of Contents

Section 12. PLL Tuned UHF Transmitter Module

12.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

12.2 Transmitter Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

12.3 Phase-Lock Loop (PLL) and Local Oscillator. . . . . . . . . . . . . . . . . . . . 103

12.4 RF Output Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

nc...

I

cale Semiconductor,

Frees

12.5 Modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

12.6 Microcontroller Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

12.7 State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

12.8 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

12.9 Data Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

12.10 Application Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

12.10.1 Application Schematics in OOK and FSK Modulation . . . . . . . . . . 107

12.10.2 Complete Application Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Section 13. Input/Output (I/O) Ports

13.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

13.2 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

13.2.1 Port A Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

13.2.2 Data Direction Register A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

13.2.3 Port A Input Pullup Enable Register. . . . . . . . . . . . . . . . . . . . . . . . 114

13.3 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

13.3.1 Port B Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

13.3.2 Data Direction Register B. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

13.3.3 Port B Input Pullup Enable Register. . . . . . . . . . . . . . . . . . . . . . . . 116

Section 14. System Integration Module (SIM)

14.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

14.2 RST

14.3 SIM Bus Clock Control and Generation . . . . . . . . . . . . . . . . . . . . . . . . 121

14.3.1 Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

14.3.2 Clock Start-Up from POR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

14.3.3 Clocks in Stop Mode and Wait Mode . . . . . . . . . . . . . . . . . . . . . . . 122

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Table of Contents 11

and IRQ Pins Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

14.4 Reset and System Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

14.4.1 External Pin Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

14.4.2 Active Resets from Internal Sources . . . . . . . . . . . . . . . . . . . . . . . 123

14.4.2.1 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

14.4.2.2 Computer Operating Properly (COP) Reset . . . . . . . . . . . . . . . . 124

14.4.2.3 Illegal Opcode Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

14.4.2.4 Illegal Address Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

14.4.2.5 Low-Voltage Inhibit (LVI) Reset . . . . . . . . . . . . . . . . . . . . . . . . . 125

14.5 SIM Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

14.5.1 SIM Counter During Power-On Reset . . . . . . . . . . . . . . . . . . . . . . 126

14.5.2 SIM Counter During Stop Mode Recovery . . . . . . . . . . . . . . . . . . . 126

14.5.3 SIM Counter and Reset States. . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

14.6 Exception Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

14.6.1 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

14.6.1.1 Hardware Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

14.6.1.2 SWI Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

14.6.2 Interrupt Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

14.6.2.1 Interrupt Status Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

14.6.2.2 Interrupt Status Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

14.6.2.3 Interrupt Status Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

14.6.3 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

14.6.4 Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

14.6.5 Status Flag Protection in Break Mode . . . . . . . . . . . . . . . . . . . . . . 132

14.7 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

14.7.1 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

14.7.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

14.8 SIM Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

14.8.1 SIM Reset Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

14.8.2 Break Flag Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Section 15. Timer Interface Module (TIM)

15.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

15.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

15.3 Pin Name Conventions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

15.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

15.4.1 TIM Counter Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

15.4.2 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

15.4.3 Output Compare. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

15.4.3.1 Unbuffered Output Compare. . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

15.4.3.2 Buffered Output Compare. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

15.4.4 Pulse Width Modulation (PWM) . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

15.4.4.1 Unbuffered PWM Signal Generation. . . . . . . . . . . . . . . . . . . . . . 143

15.4.4.2 Buffered PWM Signal Generation. . . . . . . . . . . . . . . . . . . . . . . . 144

15.4.4.3 PWM Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Data Sheet MC68HC908QF4 — Rev. 1.0

12 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

15.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

15.6 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

15.7 TIM During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

15.8 Input/Output Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

15.8.1 TIM Clock Pin (PTA2/TCLK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

15.8.2 TIM Channel I/O Pins (PTA0/TCH0 and PTA1/TCH1). . . . . . . . . . 146

15.9 Input/Output Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

15.9.1 TIM Status and Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 147

15.9.2 TIM Counter Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

15.9.3 TIM Counter Modulo Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

15.9.4 TIM Channel Status and Control Registers . . . . . . . . . . . . . . . . . . 150

15.9.5 TIM Channel Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table of Contents

nc...

I

cale Semiconductor,

Frees

Section 16. Development Support

16.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

16.2 Break Module (BRK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

16.2.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

16.2.1.1 Flag Protection During Break Interrupts . . . . . . . . . . . . . . . . . . . 158

16.2.1.2 TIM During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

16.2.1.3 COP During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

16.2.2 Break Module Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

16.2.2.1 Break Status and Control Register . . . . . . . . . . . . . . . . . . . . . . . 159

16.2.2.2 Break Address Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

16.2.2.3 Break Auxiliary Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

16.2.2.4 Break Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

16.2.2.5 Break Flag Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

16.2.3 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

16.3 Monitor Module (MON). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

16.3.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

16.3.1.1 Normal Monitor Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

16.3.1.2 Forced Monitor Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

16.3.1.3 Monitor Vectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

16.3.1.4 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

16.3.1.5 Break Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

16.3.1.6 Baud Rate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

16.3.1.7 Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

16.3.2 Security. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Section 17. Electrical Specifications

17.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

17.2 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

17.3 Functional Operating Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Table of Contents 13

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

17.4 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

17.5 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

17.6 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

17.7 Typical 3.0-V Output Drive Characteristics. . . . . . . . . . . . . . . . . . . . . . 179

17.8 Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

17.9 Supply Current Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

17.10 Analog-to-Digital (ADC) Converter Characteristics. . . . . . . . . . . . . . . . 183

17.10.1 ADC Electrical Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . 183

17.10.2 ADC Performance Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 183

17.11 Timer Interface Module Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 184

17.12 Memory Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

17.13 UHF Transmitter Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

17.13.1 UHF Module Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . 186

17.13.2 UHF Module Output Power Measurement . . . . . . . . . . . . . . . . . . . 190

cale Semiconductor,

Frees

Section 18. Ordering Information

and Mechanical Specifications

18.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

18.2 MC Order Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

18.3 32-Pin Plastic Low-Profile Quad Flat Pack

(Case No. 873A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Data Sheet MC68HC908QF4 — Rev. 1.0

14 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Data Sheet — MC68HC908QF4

1.1 Introduction

nc...

I

Freescale Semiconductor, Inc.

Section 1. General Description

The MC68HC908QF4 MCU is a member of the low-cost, high-performance

M68HC08 Family of 8-bit microcontroller units (MCUs). Optimized for low-power

operation and available in a small 32-pin low-profile quad flat pack (LQFP), this

MCU is well suited for remote keyless entry (RKE) transmitter designs, tire

pressure monitoring (TPM), or other remote sensing and wireless RF data

transmission applications.

All MCUs in the M68HC908 Family use the enhanced M68HC08 central processor

unit (CPU08) and are available with a variety of modules, me mory sizes and types,

and package types.

1.2 Features

cale Semiconductor,

Frees

Features of the MC68HC908QF4 MCU include:

• High-performance M68HC08 architecture

• Fully upward-compatible object code with M6 805, M146805, and M68HC05

Families

• Operating voltage range of 2.2 to 3.6 V

• Maximum internal bus frequency of 2 MHz

• Trimmable internal oscillator

– 4-MHz operating frequency for a 1-MHz bus frequency

– 8-bit trim capability allows 0.4% accuracy

– ±25 percent accuracy untrimmed

• Auto wakeup from STOP capability

• 4096 bytes of on-chip FLASH memory

• FLASH program memory security

• 128 bytes of on-chip RAM

• 16-bit, 2-channel timer interface module (TIM)

• 4 channel, 8-bit analog-to-digital converter (ADC)

(2)

(1)

1. The oscillator frequency is guaranteed to ±5% over temperature and voltage range after trimming.

2. No security feature is absolutely secure. However, Motorola’s strategy is to make reading or

copying the FLASH difficult for unauthorized users.

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA General Description 15

For More Information On This Product,

Go to: www.freescale.com

General Description

Freescale Semiconductor, Inc.

• 13 general-purpose input/output (I/O) ports:

– Six shared with keyboard wakeup function

– Three shared with the timer module, IRQ

– Port A pins have 3-mA sink capabilities

• Low-voltage inhibit (LVI) module with selectable trip points:

– 2.12 V detection forces MCU into reset

– 2.32 V detection sets indicator flag

• 6-bit keyboard interrupt with wakeup feature (KBI)

• External asynchronous interrupt pin with internal pullup (IRQ

• Ultra high frequency (UHF) RF transmitter:

– Ultra low sleep mode current

nc...

I

Features of the CPU08 include:

cale Semiconductor,

– ASK and FSK modulation selectable

• System protection features:

– Computer operating properly (COP) reset

– Low-voltage detection with reset

– Illegal opcode detection with reset

– Illegal address detection with reset

• 32-pin plastic LQFP package

• Power saving stop and wait modes

• Master reset pin (RST

• Enhanced HC05 programming model

• Extensive loop control functions

• 16 addressing modes (eight more than the HC05)

• 16-bit index register and stack pointer

• Memory-to-memory data transfers

• Fast 8 × 8 multiply instruction

) shared with general-purpose I/O pin

)

Frees

• Fast 16/8 divide instruction

• Binary-coded decimal (BCD) instructions

• Optimization for controller applications

• Third party C language support

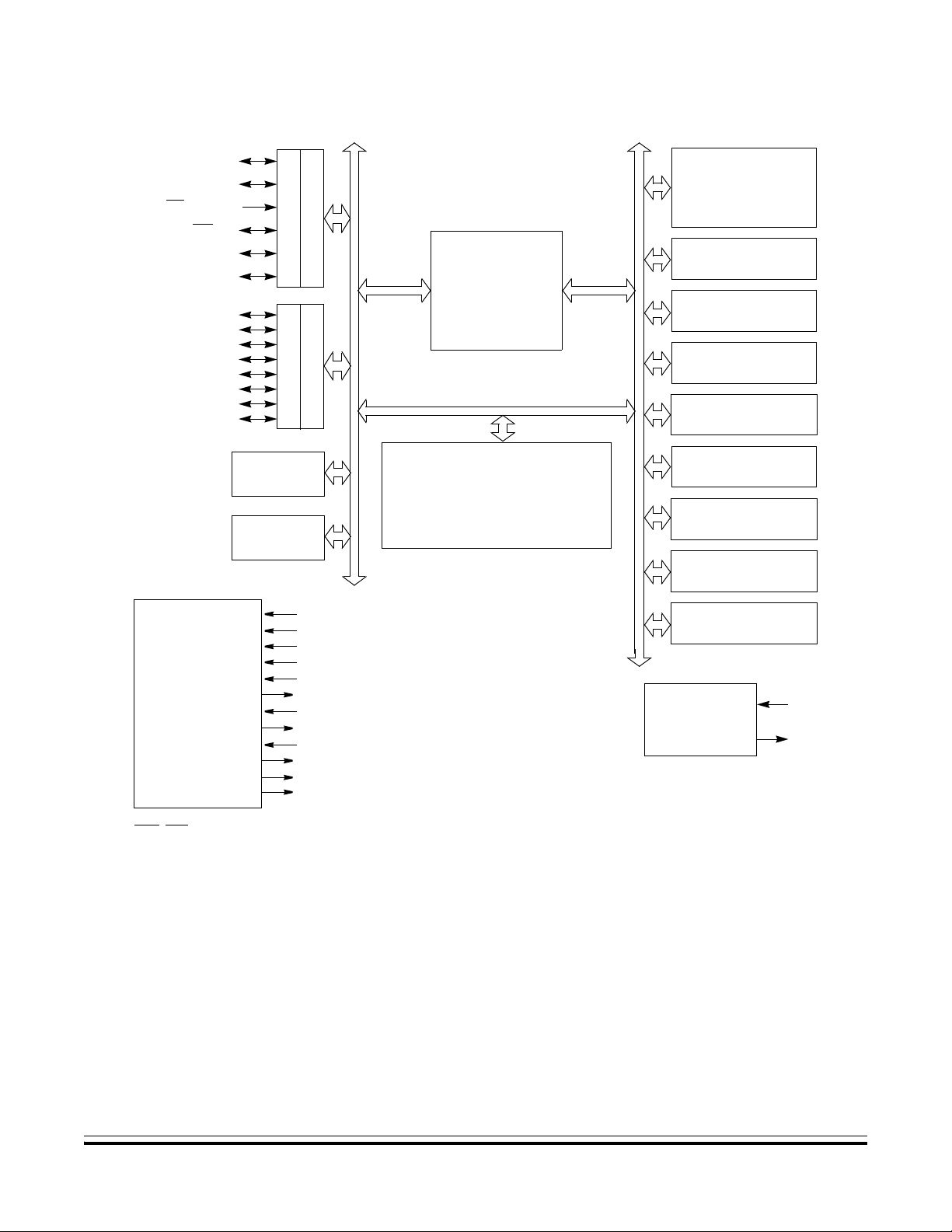

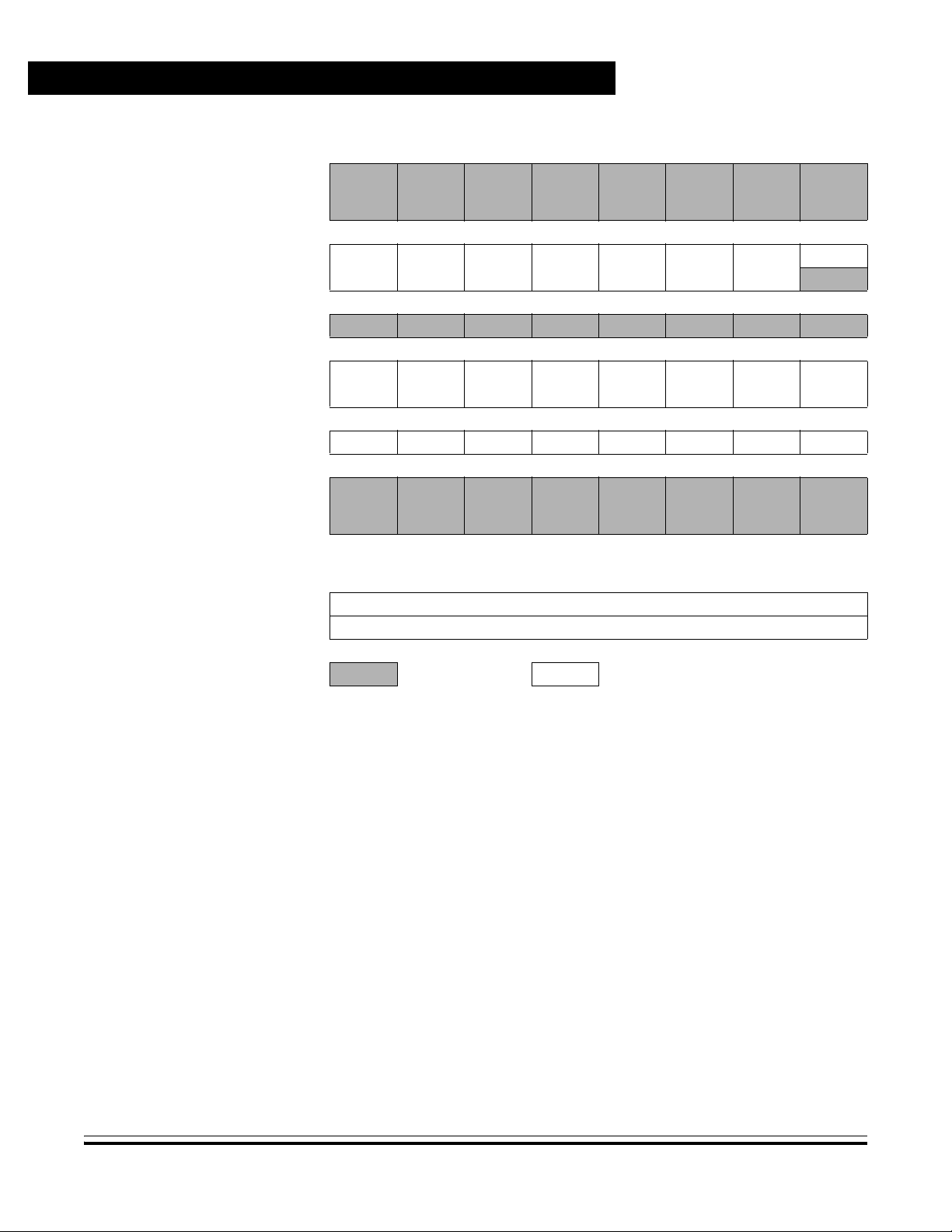

1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HC908QF4 MCU.

Data Sheet MC68HC908QF4 — Rev. 1.0

16 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

General Description

Pin Assignments

nc...

I

cale Semiconductor,

Frees

PTA0/AD0/TCH0/KBI0

PTA1/AD1/TCH1/KBI1

PTA2/IRQ

/KBI2/TCLK

PTA

PTB

V

MODE

PLLEN

DATA

BS

OP1

GND

REXT

XTAL1

XTAL0

UPCLK

PFD

DDRA

M68HC08 CPU

DDRB

MC68HC908QF4

4096 BYTES

USER FLASH

CC

PTA3/RST

PTA4/OSC2/AD2/KBI4

PTA5/OSC1/AD3/KBI5

TRANSMITTER

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

/KBI3

PTB0

PTB1

PTB2

PTB3

PTB4

PTB5

PTB6

PTB7

8-BIT ADC

128 BYTES RAM

UHF

CLOCK

GENERATOR

(OSCILLATOR)

SYSTEM INTEGRATION

MODULE

SINGLE INTERRUPT

MODULE

BREAK

MODULE

POWER-ON RESET

MODULE

KEYBOARD INTERRUPT

MODULE

16-BIT TIMER

MODULE

COP

MODULE

MONITOR ROM

POWER SUPPLY

V

DD

V

SS

Figure 1-1. Block Diagram

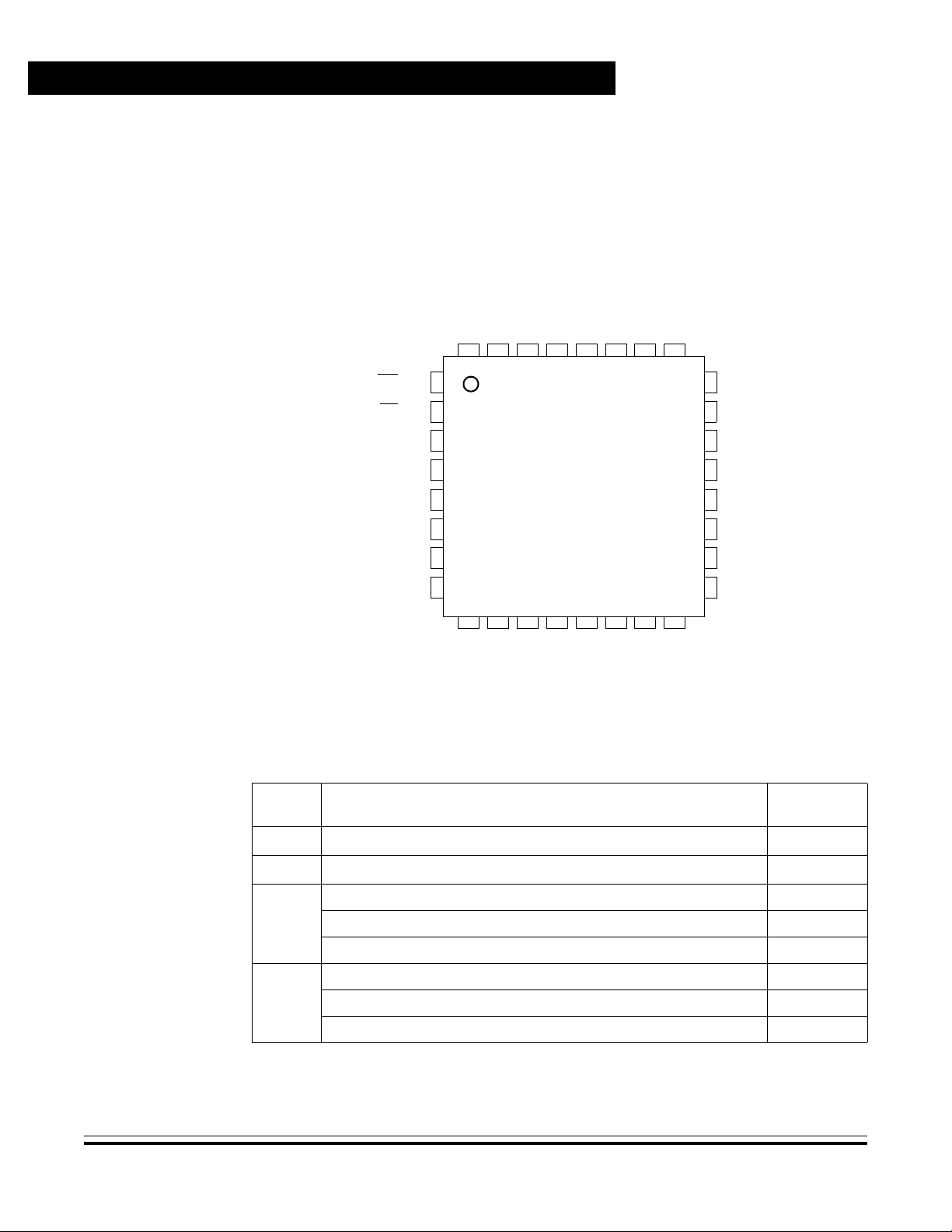

1.4 Pin Assignments

The MC68HC908QF4 is available in a 32-pin plastic low-profile quad flat pack

(LQFP). Figure 1-2 shows the pin assignment for this package.

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA General Description 17

For More Information On This Product,

Go to: www.freescale.com

General Description

1.5 Pin Functions

nc...

I

Freescale Semiconductor, Inc.

Table 1-1 provides a description of the pin functions other than those dedicated to

the UHF module which are shown in Table 1-2.

PTA5/OSC1/KBI5

PTB6

PTB7

26

25

V

24

DD

V

23

SS

PTB0

22

PTB1

21

PTA3/RST/KBI3

PTA2/IRQ/KBI2

PTB3

PTB2

PTB4

32

1

2

3

4

PTA4/OSC2/KBI4

PTB5

31

30

NC

29

NC

28

27

cale Semiconductor,

Frees

Pin

Name

V

DD

V

SS

PTA0

PTA1/TCH1/KBI1

GND

XTAL1

XTAL0

5

6

7

8

9

10

11

12

13

14

15

16

REXT

CFSK

CC

V

RFOUT

GNDRF

CC

V

ENABLE

20

19

18

17

MODE

PTA0/TCH0/KBI0

DATA CLK

DATA

BAND

Figure 1-2. MC68HC908QF4 Pin Assignments

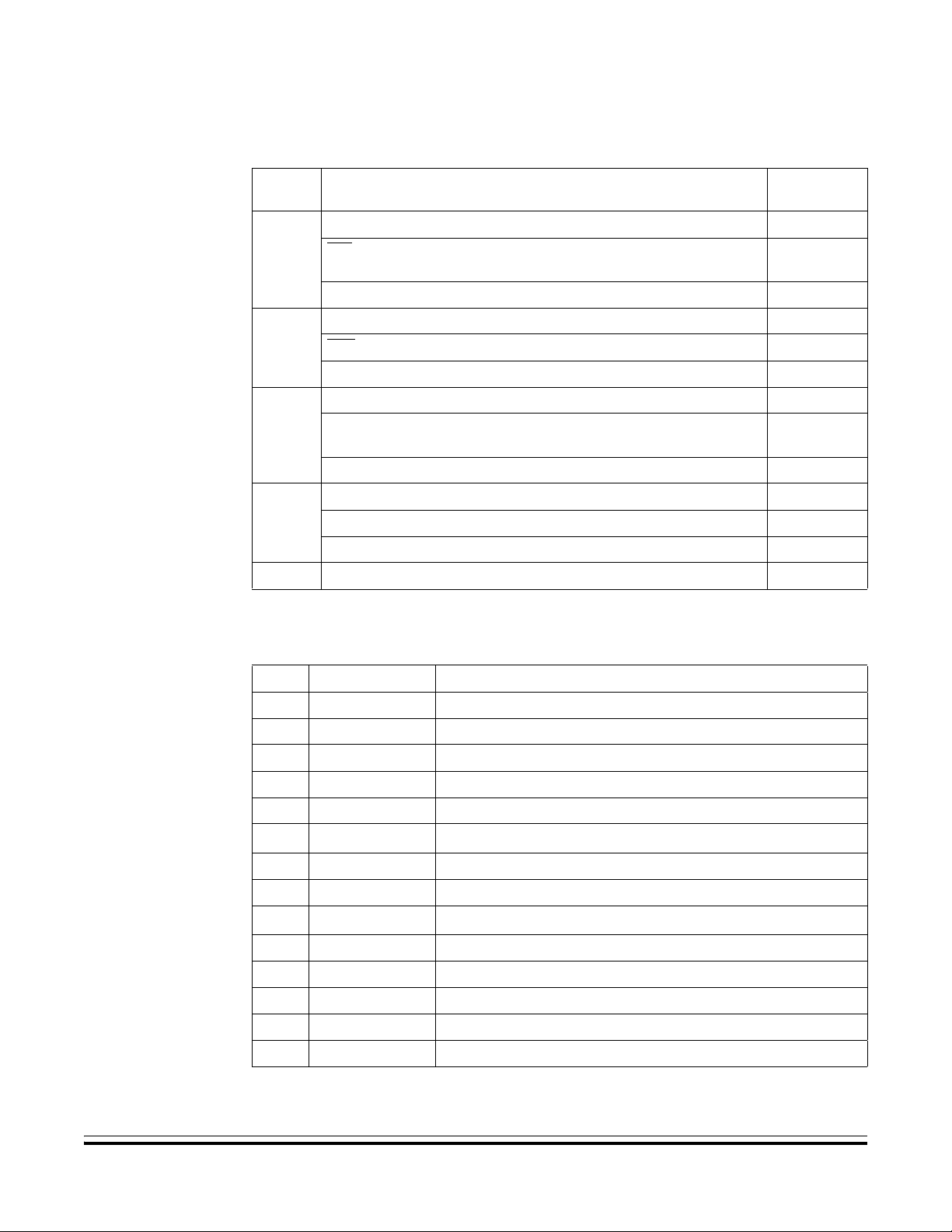

Table 1-1. Pin Functions

Description Input/Output

Pow er supply Pow er

Powe r supply ground Power

PTA0 — General purpose I/O port Input/Output

TCH0 — Timer Channel 0 I/O Input/Output

KBI0 — Keyboard interrupt input 0 Input

PTA1 — General purpose I/O port Input/Output

PTA1

Data Sheet MC68HC908QF4 — Rev. 1.0

18 General Description MOTOROLA

TCH1 — Timer Channel 1 I/O Input/Output

KBI1 — Keyboard interrupt input 1 Input

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Table 1-1. Pin Functions (Continued)

General Description

Pin Functions

nc...

I

cale Semiconductor,

Frees

Pin

Name

PTA2 — General purpose input-only port Input

— External interrupt with programmable pullup

PTA2

PTA3

PTA4

PTA5

PTB[0:7] 8 general-purpose I/O ports Input/Output

IRQ

and Schmitt trigger input

KBI2 — Keyboard interrupt input 2 Input

PTA3 — General purpose I/O port Input/Output

— Reset input, active low with internal pullup and Schmitt trigger Input

RST

KBI3 — Keyboard interrupt input 3 Input

PTA4 — General purpose I/O port Input/Output

OSC2 —XTAL oscillator output (XTAL option only)

RC or internal oscillator output (OSC2EN = 1 in PTAPUE register)

KBI4 — Keyboard interrupt input 4 Input

PTA5 — General purpose I/O port Input/Output

OSC1 —XTAL, RC, or external oscillator input Input

KBI5 — Keyboard interrupt input 5 Input

Description Input/Output

Input

Output

Output

Table 1-2. UHF Transmitter Pins

Pin Function Description

6 GND Ground

7 XTAL1 Reference oscillator input

8 XTAL0 Reference oscillator output

9 REXT Output amplifier current setting resistor

10 CFSK FSK switch output

11

12 RFOUT Power amplifier output

13 GNDRF Power amplifier ground

14

15 ENABLE Enable input

16 MODE Modulation type selection input

V

CC

V

CC

Power supply

Power supply

17 BAND Frequency band selection

18 DATA Data input

19 DATACLK Clock output to the microcontroller

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA General Description 19

For More Information On This Product,

Go to: www.freescale.com

General Description

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Data Sheet MC68HC908QF4 — Rev. 1.0

20 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Data Sheet — MC68HC908QF4

2.1 Introduction

nc...

I

Freescale Semiconductor, Inc.

Section 2. Memory

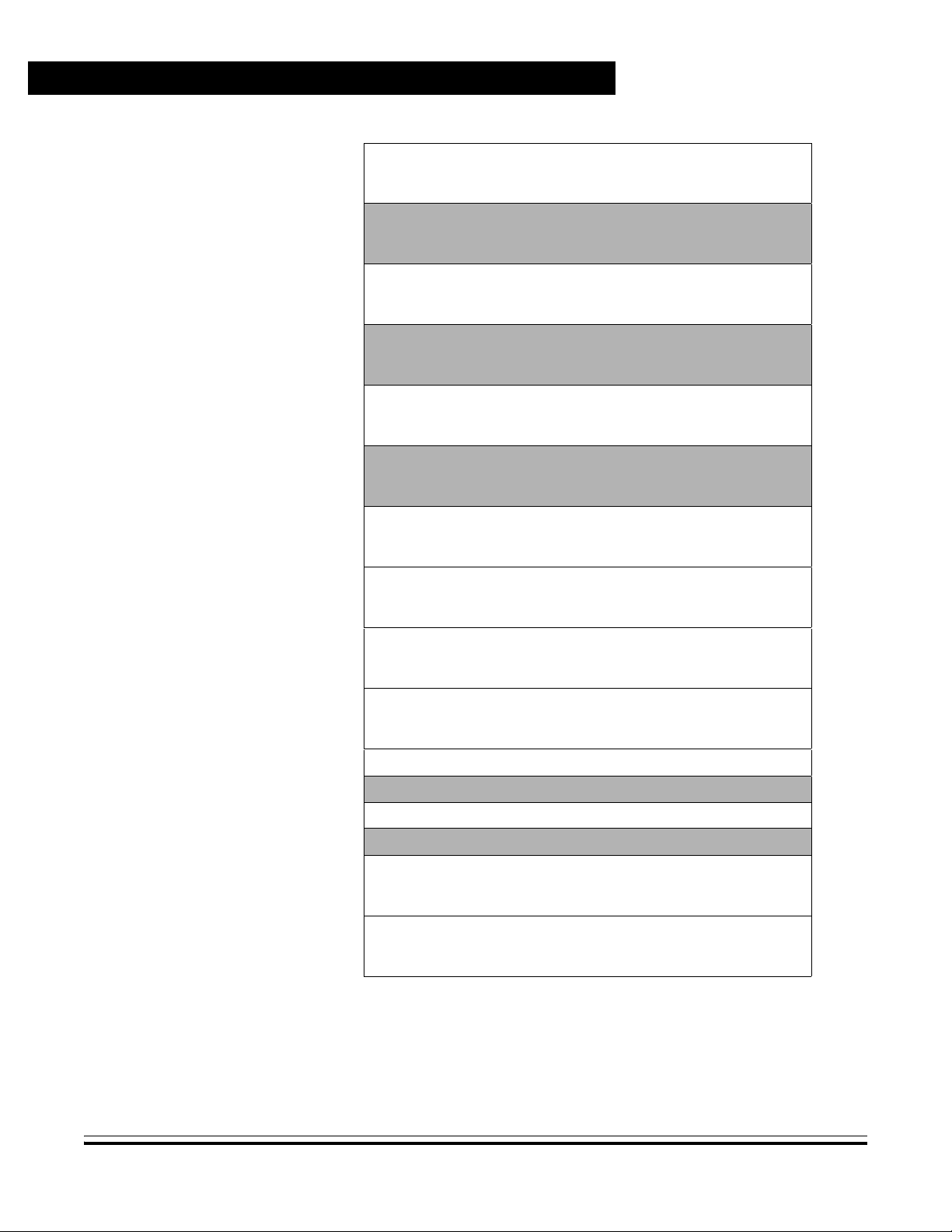

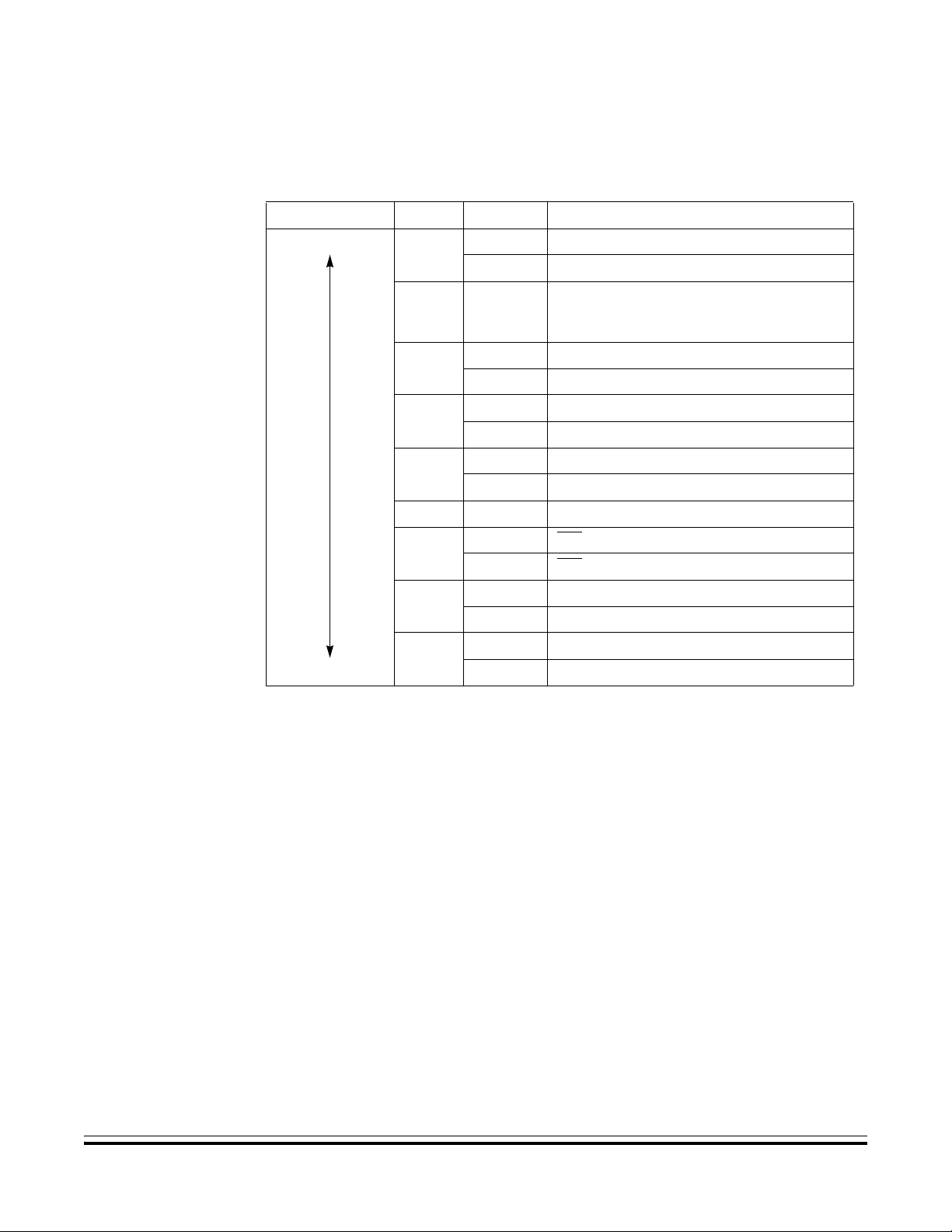

The central processor unit (CPU08) can address 64 Kbytes of memory space. The

memory map, shown in Figure 2-1, includes:

• 4096 bytes of user FLASH

• 128 bytes of random access memory (RAM)

• 48 bytes of user-defined vectors, located in FLASH

• 416 bytes of monitor read-only memory (ROM)

• 1536 bytes of FLASH program and erase routines, located in ROM

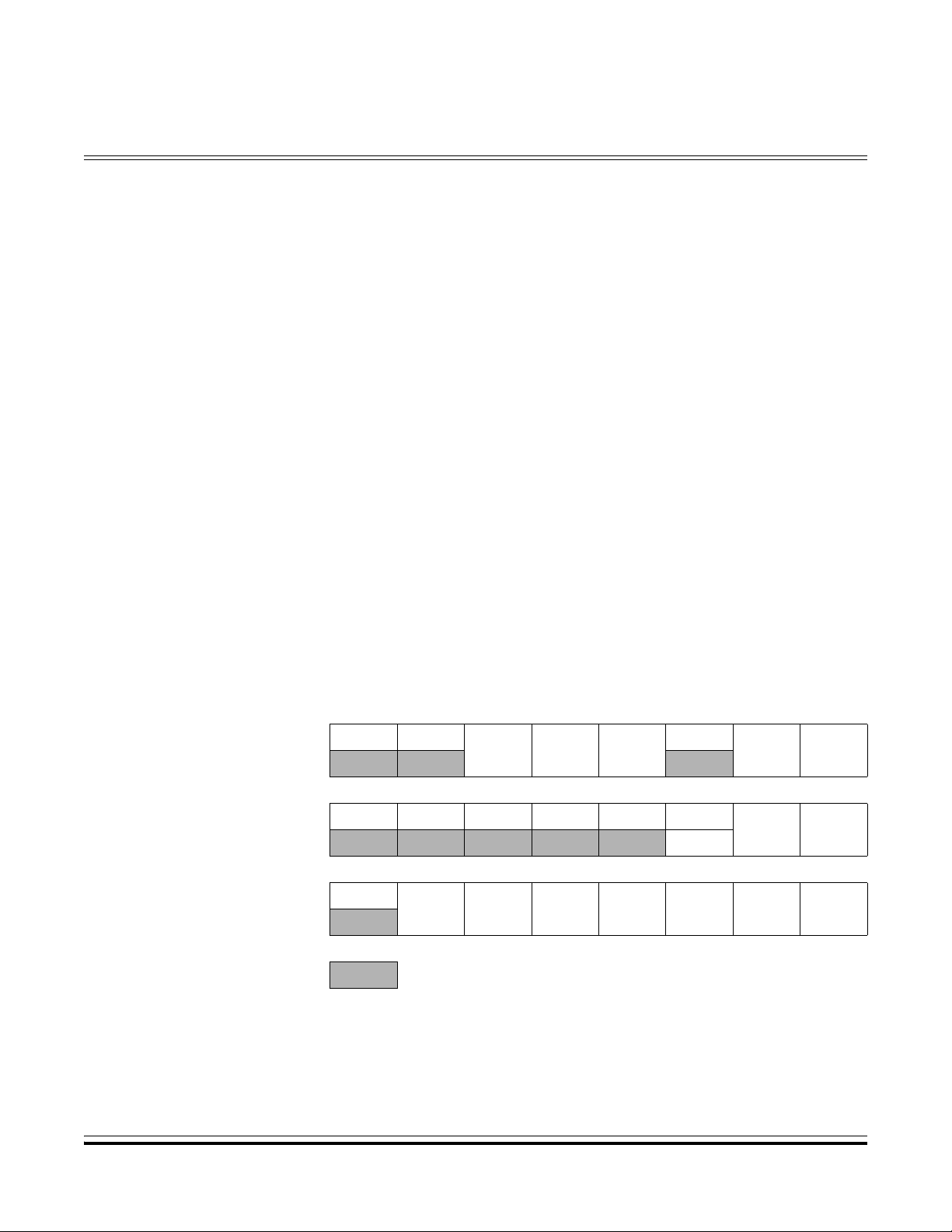

2.2 Unimplemented Memory Locations

Accessing an unimplemented location can have unpredictable effects on MCU

operation. In Figure 2-1 and in register figures in this document, unimplemented

locations are shaded.

2.3 Reserved Memory Locations

Accessing a reserved location can have unpredictable effects on MCU operation.

In Figure 2-1 and in register figures in this document, reserved locations are

marked with the word Reserved or with the letter R.

cale Semiconductor,

Frees

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Memory 21

For More Information On This Product,

Go to: www.freescale.com

Memory

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

$0000

↓

$003F

$0040

↓

$007F

$0080

↓

$00FF

$0100

↓

$27FF

$2800

↓

$2DFF

$2E00

↓

$EDFF

$EE00

↓

$FDFF

$FE00

↓

$FE0F

$FE10

↓

$FFAF

$FFB0

↓

$FFBD

$FFBE FLASH BLOCK PROTECT REGISTER (FLBPR)

$FFBF

$FFC0 INTERNAL OSCILLATOR TRIM VALUE

$FFC1 RESERVED FLASH

$FFC2

↓

$FFCF

$FFD0

↓

$FFFF

I/O REGISTERS

64 BYTES

RESERVED

64 BYTES

RAM

128 BYTES

UNIMPLEMENTED

9984 BYTES

AUXILIARY ROM

1536 BYTES

UNIMPLEMENTED

49152 BYTES

FLASH MEMORY

4096 BYTES

SYSTEM REGISTERS

MONITOR ROM 416 BYTES

FLASH

14 BYTES

RESERVED FLASH

FLASH

14 BYTES

USER VECTORS

48 BYTES

Figure 2-1. Memory Map

Data Sheet MC68HC908QF4 — Rev. 1.0

22 Memory MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

2.4 Input/Output (I/O) Section

Addresses $0000–$003F, shown in Figure 2-2, contain most of the control, status,

and data registers. Additional I/O registers have these addresses:

• $FE00 — Break status register, BSR

• $FE01 — Reset status register, SRSR

• $FE02 — Break auxiliary register, BRKAR

• $FE03 — Break flag control register, BFCR

• $FE04 — Interrupt status register 1, INT1

• $FE05 — Interrupt status register 2, INT2

• $FE06 — Interrupt status register 3, INT3

Memory

Input/Output (I/O) Section

nc...

I

cale Semiconductor,

Frees

• $FE07 — Reserved

• $FE08 — FLASH control register, FLCR

• $FE09 — Break address register high, BRKH

• $FE0A — Break address register low, BRKL

• $FE0B — Break status and control register, BRKSCR

• $FE0C — LVI status register, LVISR

•$FE0D — Reserved

• $FFBE — FLASH block protect register, FLBPR

• $FFC0 — Internal OSC trim value — Optional

• $FFFF — COP control register, COPCTL

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Memory 23

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Memory

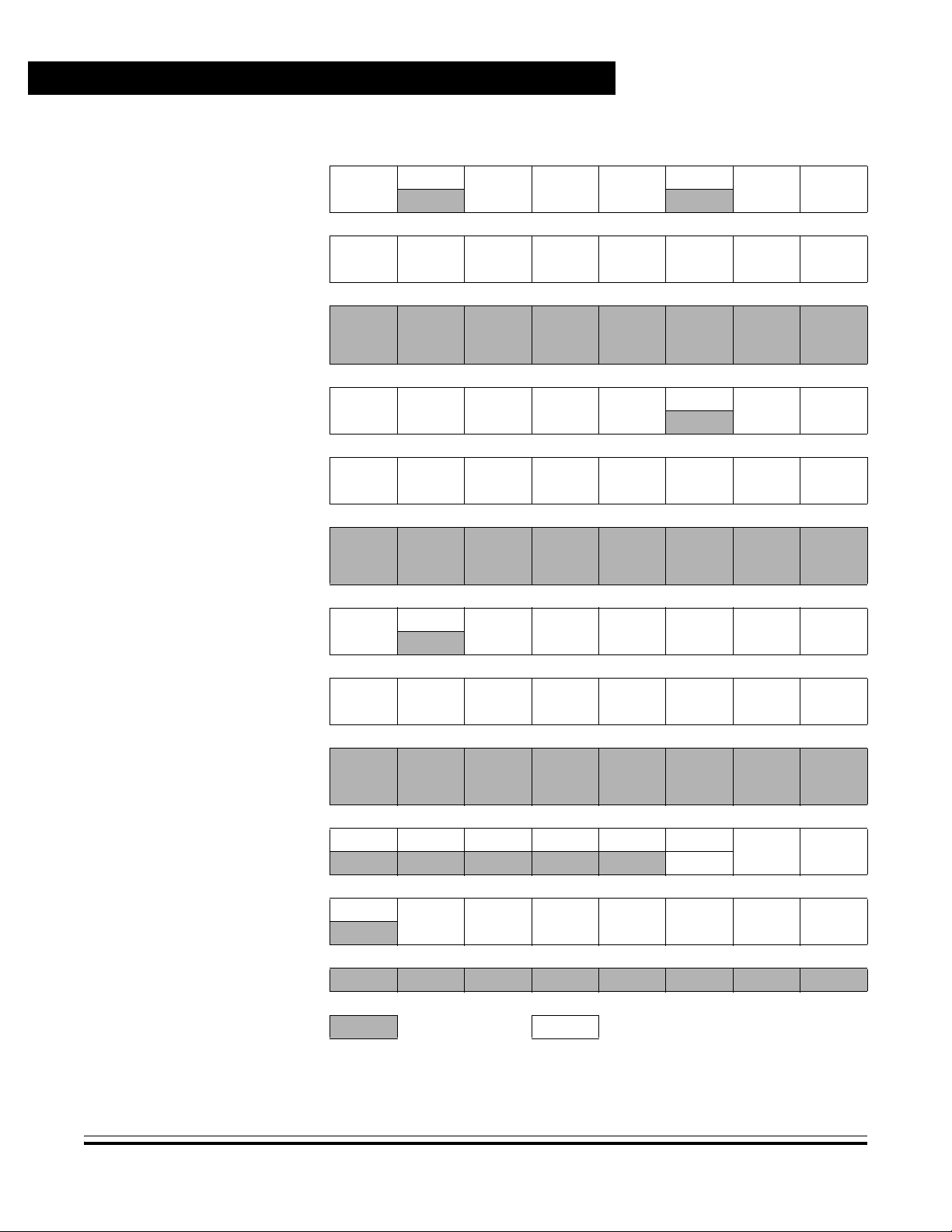

Addr.Register Name Bit 7654321Bit 0

$0000

$0001

$0002

↓

$0003

Port A Data Register

(PTA)

See page 112.

Port B Data Register

(PTB)

See page 115.

Unimplemented

Read:

Write:

Reset: UNAFFECTED BY RESET

Read:

Write:

Reset: Unaffected by reset

R

PTB7 PTB6 PTB5 PTB4 PTB3 PTB2 PTB1 PTB0

AWUL

PTA5 PTA4 PTA3

PTA2

PTA1 PTA0

nc...

I

cale Semiconductor,

Frees

Data Direction Register A

$0004

Data Direction Register B

$0005

$0006

↓

$000A

Port A Input Pullup Enable

$000B

$000C

$000D

↓

$0019

$001A

$001B

$001C Unimplemented

Register (PTAPUE)

Port B Input Pullup Enable

Register (PTBPUE)

Keyboard Status and

Control Register (KBSCR)

Keyboard Interrupt

Enable Register (KBIER)

(DDRA)

See page 113.

(DDRB)

See page 115.

Unimplemented

See page 114.

See page 116.

Unimplemented

See page 84.

See page 85.

Read:

Write:

Reset:00000000

Read:

Write:

Reset:00000000

Read:

Write:

Reset:00000000

Read:

Write:

Reset:00000000

Read:0000KEYF0

Write:

Reset:00000000

Read: 0

Write:

Reset:00000000

R R DDRA5 DDRA4 DDRA3

DDRB7 DDRB6 DDRB5 DDRB4 DDRB3 DDRB2 DDRB1 DDRB0

OSC2EN

PTBPUE7 PTBPUE6 PTBPUE5 PTBPUE4 PTBPUE3 PTBPUE2 PTBPUE1 PTBPUE0

0

PTAPUE5 PTAPUE4 PTAPUE3 PTAPUE2 PTAPUE1 PTAPUE0

AWUIE KBIE5 KBIE4 KBIE3 KBIE2 KBIE1 KBIE0

0

ACKK

DDRA1 DDRA0

IMASKK MODEK

= Unimplemented R = Reserved U = Unaffected

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 5)

Data Sheet MC68HC908QF4 — Rev. 1.0

24 Memory MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

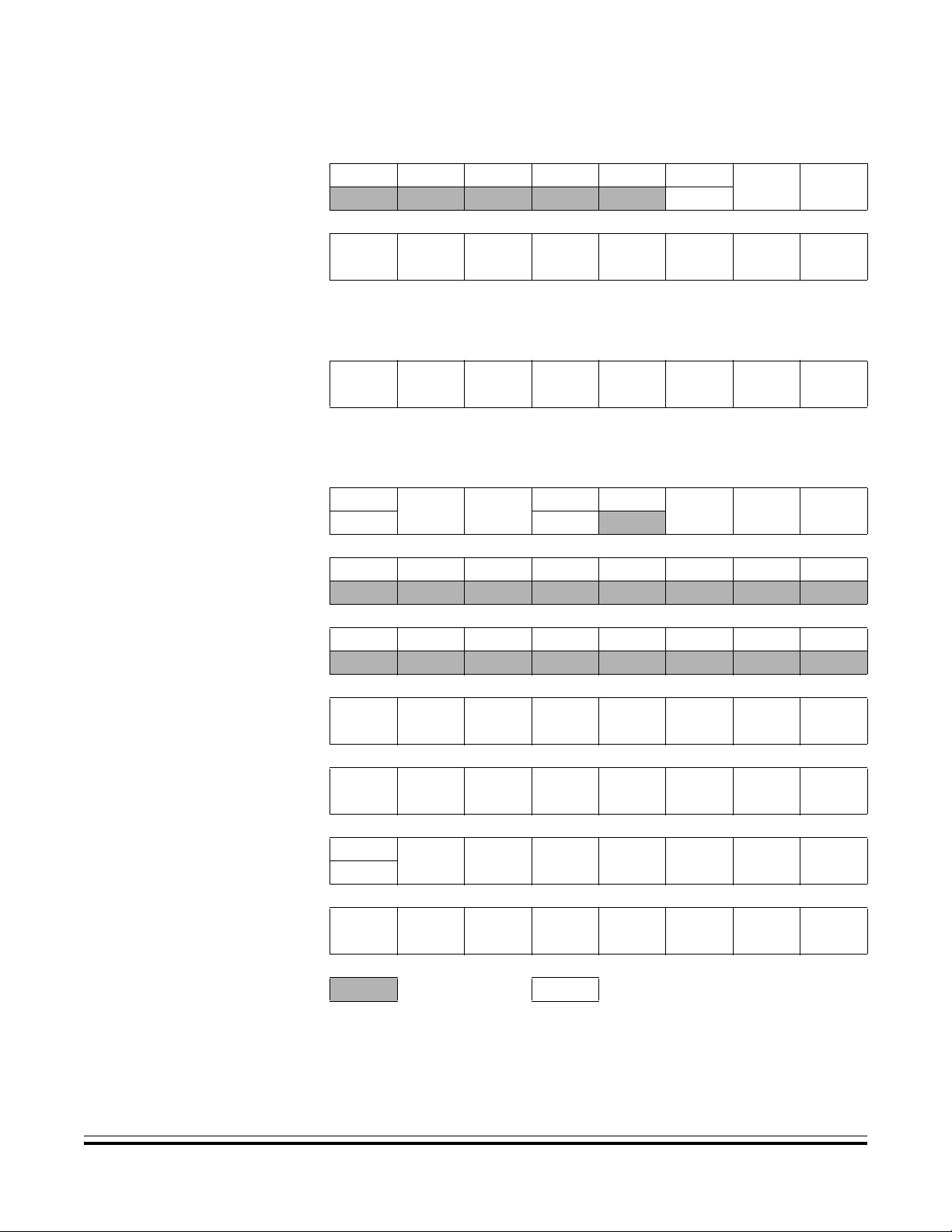

Addr.Register Name Bit 7654321Bit 0

Read:0000IRQF10

Write:

Reset:00000000

Read:

(1)

Write:

Reset:00000000

$001D

$001E

IRQ Status and Control

Register (INTSCR)

See page 77.

Configuration Register 2

(CONFIG2)

See page 51.

IRQPUD IRQEN R OSCOPT1 OSCOPT0

1. One-time writable register after each reset.

2. RSTEN reset to 0 by a power-on reset (POR) only.

Memory

Input/Output (I/O) Section

ACK1

R

IMASK1 MODE1

R RSTEN

(2)

nc...

I

cale Semiconductor,

Frees

$001F

$0020

$0021

$0022

$0023

$0024

$0025

$0026

Configuration Register 1

(CONFIG1)

See page 52.

TIM Status and Control

Register (TSC)

See page 147.

TIM Counter Register High

(TCNTH)

See page 149.

TIM Counter Register Low

(TCNTL)

See page 149.

TIM Counter Modulo

Register High (TMODH)

See page 149.

TIM Counter Modulo

Register Low (TMODL)

See page 149.

TIM Channel 0 Status and

Control Register (TSC0)

See page 150.

TIM Channel 0

Register High (TCH0H)

See page 153.

Read:

(1)

Write:

Reset:00000

Read: TOF

Write: 0 TRST

Reset:00100000

Read: Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

Write:

Reset:00000000

Read:Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

Write:

Reset:00000000

Read:

Write:

Reset:11111111

Read:

Write:

Reset:11111111

Read: CH0F

Write: 0

Reset:00000000

Read:

Write:

Reset: Indeterminate after reset

COPRS LVISTOP LVIRSTD LVIPWRD LVDLVR SSREC STOP COPD

(2)

1. One-time writable register after each reset. Exceptions are LVDLVR and LVIRSTD bits.

2. LVDLVR reset to 0 by a power-on reset (POR) only.

TOIE TSTOP

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

CH0IE MS0B MS0A ELS0B ELS0A TOV0 CH0MAX

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

= Unimplemented R = Reserved U = Unaffected

00

000

PS2 PS1 PS0

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 5)

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Memory 25

For More Information On This Product,

Go to: www.freescale.com

nc...

I

Freescale Semiconductor, Inc.

Memory

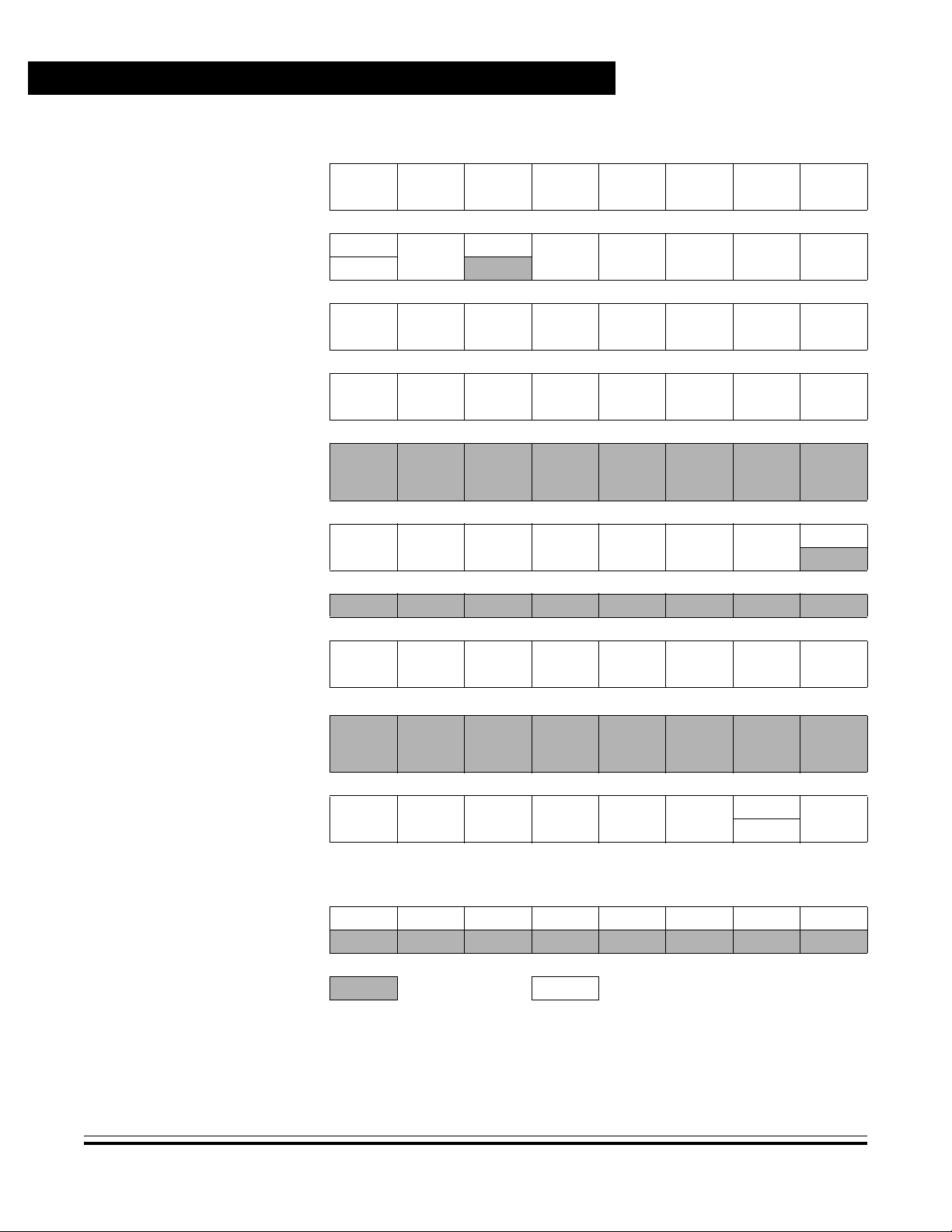

Addr.Register Name Bit 7654321Bit 0

Read:

Write:

Reset: Indeterminate after reset

Read: CH1F

Write: 0

Reset:00000000

Read:

Write:

Reset: Indeterminate after reset

Read:

Write:

Reset: Indeterminate after reset

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

CH1IE

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

0

MS1A ELS1B ELS1A TOV1 CH1MAX

$0027

$0028

$0029

$002A

$002B

↓

$0035

TIM Channel 0

Register Low (TCH0L)

See page 153.

TIM Channel 1 Status and

Control Register (TSC1)

See page 150.

TIM Channel 1

Register High (TCH1H)

See page 153.

TIM Channel 1

Register Low (TCH1L)

See page 153.

Unimplemented

cale Semiconductor,

Frees

Oscillator Status Register

$0036

$0037 Unimplemented Read:

Oscillator Trim Register

$0038

$0039

↓

$003F

Break Status Register

$FE00

SIM Reset Status Register

$FE01

(OSCSTAT)

See page 98.

(OSCTRIM)

See page 99.

Unimplemented

See page 161.

(SRSR)

See page 135.

Read:

Write:

Reset:00000000

Read:

Write:

Reset:10000000

Read:

Write: See note 1

(BSR)

Reset: 0

Read: POR PIN COP ILOP ILAD MODRST LVI 0

Write:

POR:10000000

RRRRRRECGON

TRIM7 TRIM6 TRIM5 TRIM4 TRIM3 TRIM2 TRIM1 TRIM0

RRRRRR

1. Writing a 0 clears SBSW.

= Unimplemented R = Reserved U = Unaffected

SBSW

ECGST

R

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 5)

Data Sheet MC68HC908QF4 — Rev. 1.0

26 Memory MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

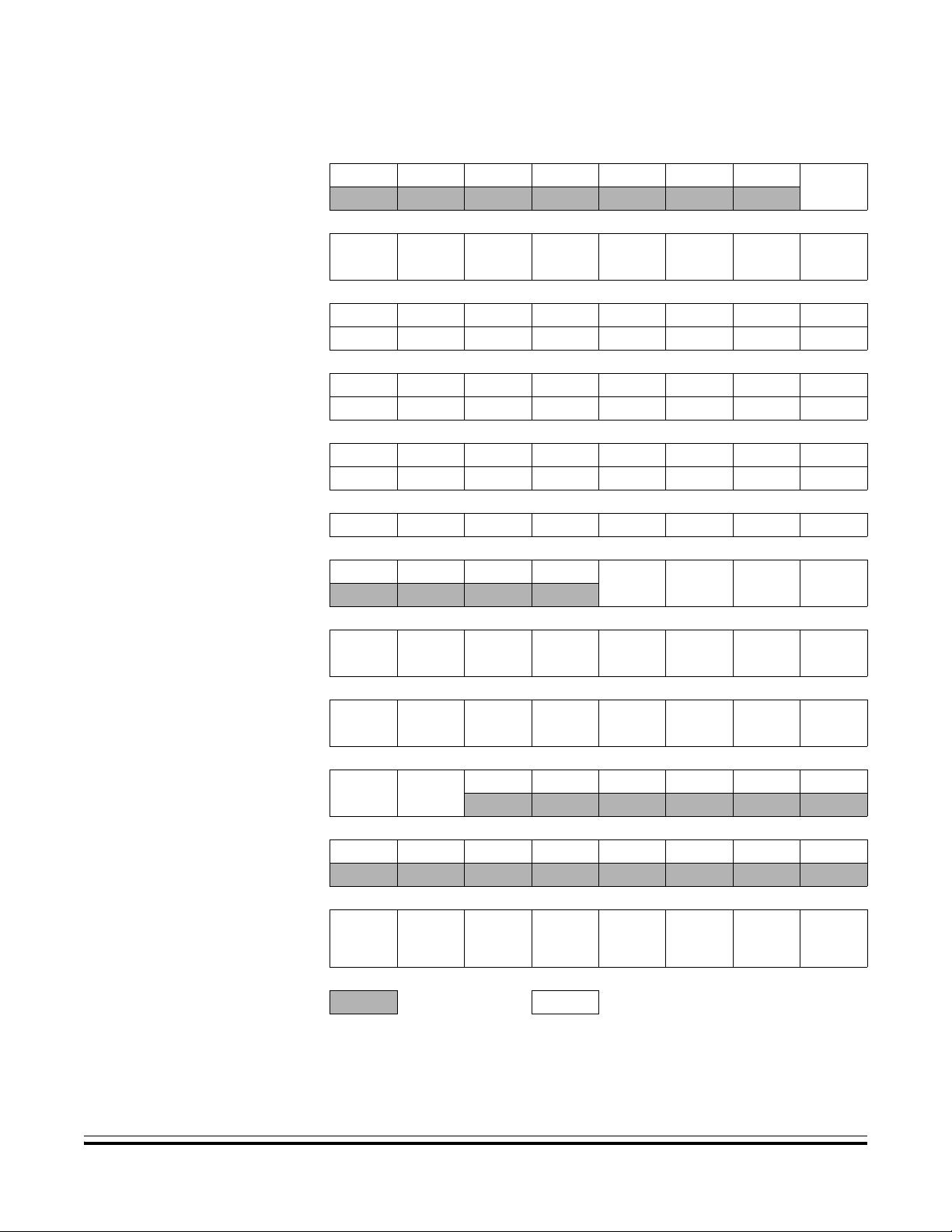

Addr.Register Name Bit 7654321Bit 0

Break Auxiliary

$FE02

$FE03

$FE04

$FE05

nc...

I

$FE06

$FE07 Reserved RRRRRRRR

Register (BRKAR)

See page 160.

Break Flag Control

Register (BFCR)

See page 161.

Interrupt Status Register 1

See page 77.

Interrupt Status Register 2

See page 77.

Interrupt Status Register 3

See page 77.

Read:0000000

Write:

Reset:00000000

Read:

Write:

Reset: 0

Read: 0 IF5 IF4 IF3 0 IF1 0 0

(INT1)

Write:RRRRRRRR

Reset:00000000

Read:IF140000000

(INT2)

Write:RRRRRRRR

Reset:00000000

Read:0000000IF15

(INT3)

Write:RRRRRRRR

Reset:00000000

Memory

Input/Output (I/O) Section

BDCOP

BCFERRRRRRR

cale Semiconductor,

Frees

$FE08

$FE09

$FE0A

$FE0B

$FE0C

$FE0D

↓

$FE0F

FLASH Control Register

(FLCR)

See page 30.

Break Address High

Register (BRKH)

See page 160.

Break Address low

Register (BRKL)

See page 160.

Break Status and Control

Register (BRKSCR)

See page 159.

LVI Status Register

(LVISR)

See page 89.

Reserved for FLASH Test RRRRRRRR

Read:0000

Write:

Reset:00000000

Read:

Write:

Reset:00000000

Read:

Write:

Reset:00000000

Read:

Write:

Reset:00000000

Read:LVIOUT000000R

Write:

Reset:00000000

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

BRKE BRKA

= Unimplemented R = Reserved U = Unaffected

000000

HVEN MASS ERASE PGM

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 5)

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Memory 27

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Memory

Addr.Register Name Bit 7654321Bit 0

$FFB0

↓

$FFBD

Unimplemented

FLASH Block Protect

$FFBE

$FFBF Unimplemented

Internal Oscillator Trim Value

$FFC0

nc...

I

$FFC1 Reserved RRRRRRRR

$FFC2

↓

$FFCF

$FFFF

Register (FLBPR)

See page 35.

(Optional)

Unimplemented

COP Control Register

(COPCTL)

See page 57.

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 5)

Read:

Write:

Reset:00000000

Read:

Write:

Reset:10000000

Read: LOW BYTE OF RESET VECTOR

Write: WRITING CLEARS COP COUNTER (ANY VALUE)

Reset: Unaffected by reset

BPR7 BPR6 BPR5 BPR4 BPR3 BPR2 BPR1

TRIM7 TRIM6 TRIM5 TRIM4 TRIM3 TRIM2 TRIM1 TRIM0

= Unimplemented R = Reserved U = Unaffected

cale Semiconductor,

0

Frees

Data Sheet MC68HC908QF4 — Rev. 1.0

28 Memory MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Table 2-1 shows the MC68HC908QF4 reset and interrupt vectors.

.

Vector Priority Vector Address Vector

Lowest

Table 2-1. Vector Addresses

IF14

IF13

↓

IF6

IF5

$FFE0 Keyboard vector (high)

$FFE1 Keyboard vector (low)

— Not used

$FFF2 TIM overflow vector (high)

$FFF3 TIM overflow vector (low)

Random-Access Memory (RAM)

Memory

nc...

I

2.5 Random-Access Memory (RAM)

cale Semiconductor,

NOTE: For correct operation, the stack pointer must point only to RAM locations.

Frees

Addresses $0080–$00FF are RAM locations. The location of the stack RAM is

programmable. The 16-bit stack pointer allows the stack to be anywhere in the

64-Kbyte memory space.

Before processing an interrupt, the central processor unit (CPU) uses five bytes of

the stack to save the contents of the CPU registers.

Highest

IF4

IF3

IF2 — Not used

IF1

—

—

$FFF4 TIM channel 1 vector (high)

$FFF5 TIM channel 1 vector (low)

$FFF6 TIM channel 0 vector (high)

$FFF7 TIM channel 0 vector (low)

$FFF A IRQ

$FFFB IRQ

$FFFC SWI vector (high)

$FFFD SWI vector (low)

$FFFE Reset vector (high)

$FFFF Reset vector (low)

vector (high)

vector (low)

NOTE: For M6805, M146805, and M68HC05 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return

address. The stack pointer decrements during pushes and increments during pulls.

NOTE: Be careful when using nested subroutines. The CPU may overwrite data in the

RAM during a subroutine or during the interrupt stacking operation.

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Memory 29

For More Information On This Product,

Go to: www.freescale.com

Memory

2.6 FLASH Memory (FLASH)

nc...

I

Freescale Semiconductor, Inc.

This subsection describes the operation of the embedded FLASH memory. The

FLASH memory can be read, programmed, and erased from a single external

supply. The program and erase operations are enabled through the use of an

internal charge pump.

The FLASH memory consists of an array of 4096 bytes with an additional 48 bytes

for user vectors. The minimum size of FLASH memory that can be erased is 64

bytes; and the maximum size of FLASH memory that can be programmed in a

program cycle is 32 bytes (a row). Program and erase operations are facilitated

through control bits in the FLASH control register (FLCR). Details for these

operations appear later in this section. The address ranges for the user memory

and vectors are:

• $EE00 – $FDFF; user memory, 4096 bytes

• $FFD0 – $FFFF; user interrupt vectors, 48 bytes.

NOTE: An erased bit reads as 1 and a programmed bit reads as 0. A security feature

2.6.1 FLASH Control Register

cale Semiconductor,

Frees

prevents viewing of the FLASH contents.

The FLASH control register (FLCR) controls FLASH program and erase

operations.

Address: $FE08

Bit 7654321Bit 0

Read:0000

Write:

Reset:00000000

= Unimplemented

Figure 2-3. FLASH Control Register (FLCR)

HVEN — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory

for either program or erase operation. It can only be set if either PGM =1 or

ERASE =1 and the proper sequence for program or erase is followed.

1 = High voltage enabled to array and charge pump on

0 = High voltage disabled to array and charge pump off

(1)

HVEN MASS ERASE PGM

MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation.

1 = Mass erase operation selected

0 = Mass erase operation unselected

1. No security feature is absolutely secure. However, Motorola’s strategy is to make reading or

copying the FLASH difficult for unauthorized users.

Data Sheet MC68HC908QF4 — Rev. 1.0

30 Memory MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

ERASE — Erase Control Bit

PGM — Program Control Bit

2.6.2 FLASH Page Erase Operation

nc...

I

cale Semiconductor,

NOTE: Programming and erasing of FLASH locations cannot be performed by code being

Frees

Use the following procedure to erase a page of FLASH memory. A page consists

of 64 consecutive bytes starting from addresses $XX00, $XX40, $XX80, or $XXC0.

The 48-byte user interrupt vectors area also forms a page. Any FLASH memory

page can be erased alone.

10. After time, t

executed from the FLASH memory. While these operations must be performed in

the order as shown, but other unrelated operations may occur between the steps.

Freescale Semiconductor, Inc.

This read/write bit configures the memory for erase operation. ERASE is

interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1

at the same time.

1 = Erase operation selected

0 = Erase operation unselected

This read/write bit configures the memory for program operation. PGM is

interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to

1 at the same time.

1 = Program operation selected

0 = Program operation unselected

1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

2. Read the FLASH block protect register.

3. Write any data to any FLASH location within the address range of the block

to be erased.

4. Wait for a time, t

5. Set the HVEN bit.

6. Wait for a time, t

7. Clear the ERASE bit.

8. Wait for a time, t

9. Clear the HVEN bit.

again.

FLASH Memory (FLASH)

(minimum 10 µs).

NVS

(minimum 1 ms or 4 ms).

Erase

(minimum 5 µs).

NVH

(typical 1 µs), the memory can be accessed in read mode

RCV

Memory

In applications that need up to 10,000 program/erase cycles, use the 4 ms page

erase specification to get improved long-term reliability. Any application can use

this 4 ms page erase specification. However, in applications where a FLASH

location will be erased and reprogrammed less than 1000 times, and speed is

important, use the 1 ms page erase specification to get a lower minimum erase

time.

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Memory 31

For More Information On This Product,

Go to: www.freescale.com

Memory

2.6.3 FLASH Mass Erase Operation

Use the following procedure to erase the entire FLASH memory to read as 1:

NOTE: Mass erase is disabled whenever any block is protected (FLBPR does not equal

$FF).

nc...

I

10. After time, t

Freescale Semiconductor, Inc.

1. Set both the ERASE bit and the MASS bit in the FLASH control register.

2. Read from the FLASH block protect register.

3. Write any data to any FLASH address

range.

4. Wait for a time, t

5. Set the HVEN bit.

6. Wait for a time, t

7. Clear the ERASE and MASS bits.

8. Wait for a time, t

9. Clear the HVEN bit.

again.

(1)

within the FLASH memory address

(minimum 10 µs).

NVS

(minimum 4 ms).

Erase

(minimum 100 µs).

NVH1

(typical 1 µs), the memory can be accessed in read mode

RCV

NOTE: Programming and erasing of FLASH locations cannot be performed by code being

2.6.4 FLASH Program Operation

cale Semiconductor,

NOTE: Only bytes which are currently $FF may be programmed.

Frees

executed from the FLASH memory. While these operations must be performed in

the order as shown, but other unrelated operations may occur between the steps.

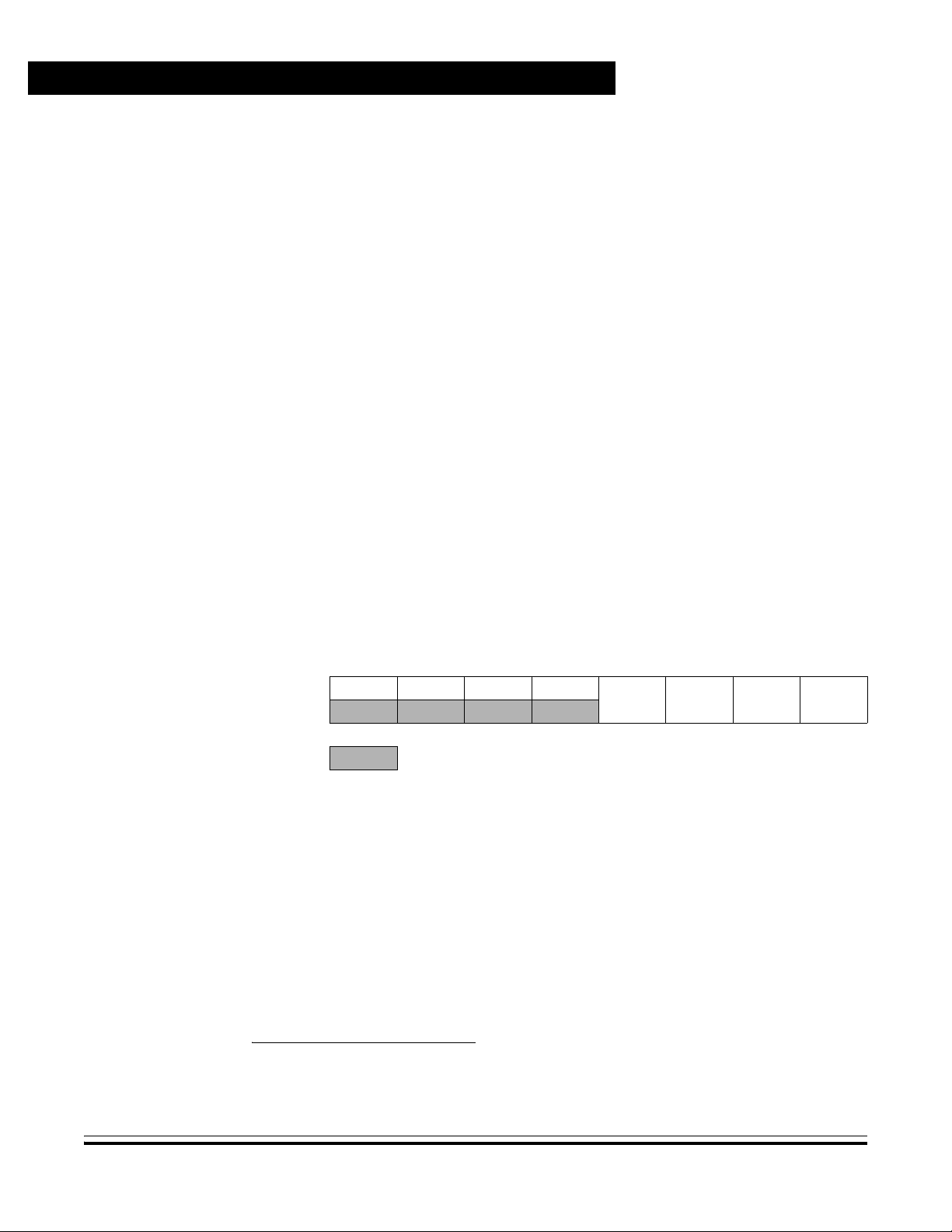

Programming of the FLASH memory is done on a row basis. A row consists of 32

consecutive bytes starting from addresses $XX00, $XX20, $XX40, $XX60, $XX80,

$XXA0, $XXC0, or $XXE0. Use the following step-by-step procedure to program a

row of FLASH memory

Figure 2-4 shows a flowchart of the programming algorithm.

1. Set the PGM bit. This configures the memory for program operation and

enables the latching of address and data for programming.

2. Read from the FLASH block protect register.

3. Write any data to any FLASH location within the address range desired.

4. Wait for a time, t

5. Set the HVEN bit.

6. Wait for a time, t

(minimum 10 µs).

NVS

(minimum 5 µs).

PGS

1. When in monitor mode, with security sequence failed (see 16.3.2 Security), write to the FLASH

block protect register instead of any FLASH address.

Data Sheet MC68HC908QF4 — Rev. 1.0

32 Memory MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Memory

FLASH Memory (FLASH)

NOTE: The COP register at location $FFFF should not be written between steps 5-12,

nc...

I

NOTE: Programming and erasing of FLASH locations cannot be performed by code being

2.6.5 FLASH Protection

cale Semiconductor,

NOTE: In performing a program or erase operation, the FLASH block protect register must

Frees

7. Write data to the FLASH address being programmed

8. Wait for time, t

9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

10. Clear the PGM bit

11. Wait for time, t

12. Clear the HVEN bit.

13. After time, t

again.

when the HVEN bit is set. Since this register is located at a valid FLASH address,

unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is

programmed.

executed from the FLASH memory. While these operations must be performed in

the order shown, other unrelated operations may occur between the steps. Do not

exceed t

Due to the ability of the on-board charge pump to erase and program the FLASH

memory in the target application, provision is made to protect blocks of memory

from unintentional erase or program operations due to system malfunction. This

protection is done by use of a FLASH block protect register (FLBPR). The FLBPR

determines the range of the FLASH memory which is to be protected. The range

of the protected area starts from a location defined by FLBPR and ends to the

bottom of the FLASH memory ($FFFF). When the memory is protected, the HVEN

bit cannot be set in either ERASE or PROGRAM operations.

be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from

being programmed and erased. When all the bits are erased (all 1’s), the entire

memory is accessible for program and erase.

PROG

RCV

maximum, see 17.12 Memory Characteristics.

(minimum 30 µs).

PROG

(1)

.

(minimum 5 µs).

NVH

(typical 1 µs), the memory can be accessed in read mode

(1)

.

1. The time between each FLASH address change, or the time between the last FLASH address

programmed to clearing PGM bit, must not exceed the maximum programming time, t

maximum.

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Memory 33

For More Information On This Product,

Go to: www.freescale.com

PROG

Memory

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

Algorithm for Programming

a Row (32 Bytes) of FLASH Memory

1

2

READ THE FLASH BLOCK PROTECT REGISTER

3

WRITE ANY DATA TO ANY FLASH ADDRESS

WITHIN THE ROW ADDRESS RANGE DESIRED

4

5

6

7

WRITE DATA TO THE FLASH ADDRESS

8

9

SET PGM BIT

WAIT FOR A TIME, t

SET HVEN BIT

WAIT FOR A TIME, t

TO BE PROGRAMMED

WAIT FOR A TIME, t

COMPLETED

PROGRAMMING

THIS ROW?

N

nvs

pgs

PROG

Y

10

11

CLEAR PGM BIT

WAIT FOR A TIME, t

nvh

Notes:

The time between each FLASH address change (step 6 to step 9), or the

time between the last FLASH address programmed to clearing PGM bit

(step 6 to step 9) must not exceed the maximum programming time, t

maximum. This row program algorithm assumes the row/s to be

programmed are initially erased.

PROG

12

13

,

CLEAR HVEN BIT

WAIT FOR A TIME, t

END OF PROGRAMMING

rcv

Figure 2-4. FLASH Programming Flowchart

Data Sheet MC68HC908QF4 — Rev. 1.0

34 Memory MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

When bits within the FLBPR are programmed, they lock a block of memory. The

address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the

FLBPR is programmed with a value other than $FF, any erase or program of the

FLBPR or the protected block of FLASH memory is prohibited. Mass erase is

disabled whenever any block is protected (FLBPR does not equal $FF). The

FLBPR itself can be erased or programmed only with an external voltage, V

present on the IRQ

mode.

2.6.6 FLASH Block Protect Register

The FLASH block protect register is implemented as a byte within the FLASH

memory, and therefore can only be written during a programming sequence of the

FLASH memory. The value in this register determines the starting address of the

nc...

I

protected range within the FLASH memory.

Freescale Semiconductor, Inc.

Address: $FFBE

pin. This voltage also allows entry from reset into the monitor

Memory

FLASH Memory (FLASH)

,

TST

cale Semiconductor,

Frees

Bit 7654321Bit 0

Read:

Write:

Reset:UUUUUUUU

U = Unaffected by reset. Initial value from factory is 1.

Write to this register is by a programming sequence to the FLASH memory.

BPR[7:0] — FLASH Protection Register Bits [7:0]

These eight bits in FLBPR represent bits [13:6] of a 16-bit memory a ddress. Bits

[15:14] are 1s and bits [5:0] are 0s.

The resultant 16-bit address is used for specifying the start address of the

FLASH memory for block protection. The FLASH is protected from this start

address to the end of FLASH memory, at $FFFF. With this mechanism, the

protect start address can be XX00, XX40, XX80, or XXC0 within the FLASH

memory. See Figure 2-6 and Table 2-2.

START ADDRESS OF

FLASH BLOCK PROTECT

BPR7 BPR6 BPR5 BPR4 BPR3 BPR2 BPR1 BPR0

Figure 2-5. FLASH Block Protect Register (FLBPR)

16-BIT MEMORY ADDRESS

11

FLBPR VALUE

0

0

000

0

Figure 2-6. FLASH Block Protect Start Address

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Memory 35

For More Information On This Product,

Go to: www.freescale.com

nc...

I

Memory

Freescale Semiconductor, Inc.

BPR[7:0] Start of Address of Protect Range

$00–$B8 The entire FLASH memory is protected.

$B9 (1011 1001)$EE40 (1110 1110 0100 0000)

$BA (1011 1010)$EE80 (1110 1110 1000 0000)

$BB (1011 1011) $EEC0 (1110 1110 1100 0000)

$BC (1011 1100)$EF00 (1110 1111 0000 0000)

$DE (1101 1110) $F780 (1111 0111 1000 0000)

$DF (1101 1111)$F7C0 (1111 0111 1100 0000)

$FE (1111 1110)

Table 2-2. Examples of Protect Start Address

and so on...

$FF80 (1111 1111 1000 0000)

FLBPR, OSCTRIM, and vectors are protected

$FF The entire FLASH memory is not protecte d.

2.6.7 Wait Mode

2.6.8 Stop Mode

cale Semiconductor,

Frees

Putting the MCU into wait mode while the FLASH is in read mode does not affect

the operation of the FLASH memory directly, but there will not be any memory

activity since the CPU is inactive.

The WAIT instruction should not be executed while performing a program or erase

operation on the FLASH, or the operation will discontinue and the FLASH will be

on standby mode.

Putting the MCU into stop mode while the FLASH is in read mode does not affect

the operation of the FLASH memory directly, but there will not be any memory

activity since the CPU is inactive.

The STOP instruction should not be executed while performing a program or erase

operation on the FLASH, or the operation will discontinue and the FLASH will be

on standby mode

NOTE: Standby mode is the power-saving mode of the FLASH module in which all internal

control signals to the FLASH are inactive and the current consumption of the

FLASH is at a minimum.

Data Sheet MC68HC908QF4 — Rev. 1.0

36 Memory MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Data Sheet — MC68HC908QF4

3.1 Introduction

3.2 Features

nc...

I

Freescale Semiconductor, Inc.

Section 3. Analog-to-Digital Converter (ADC)

This section describes the analog-to-digital converter (ADC). The ADC is an 8-bit,

4-channel analog-to-digital converter.

Features of the ADC module include:

• 4 channels with multiplexed input

• Linear successive approximation with monotonicity

cale Semiconductor,

Frees

• 8-bit resolution

• Single or continuous conversion

• Conversion complete flag or conversion complete interrupt

• Selectable ADC clock frequency

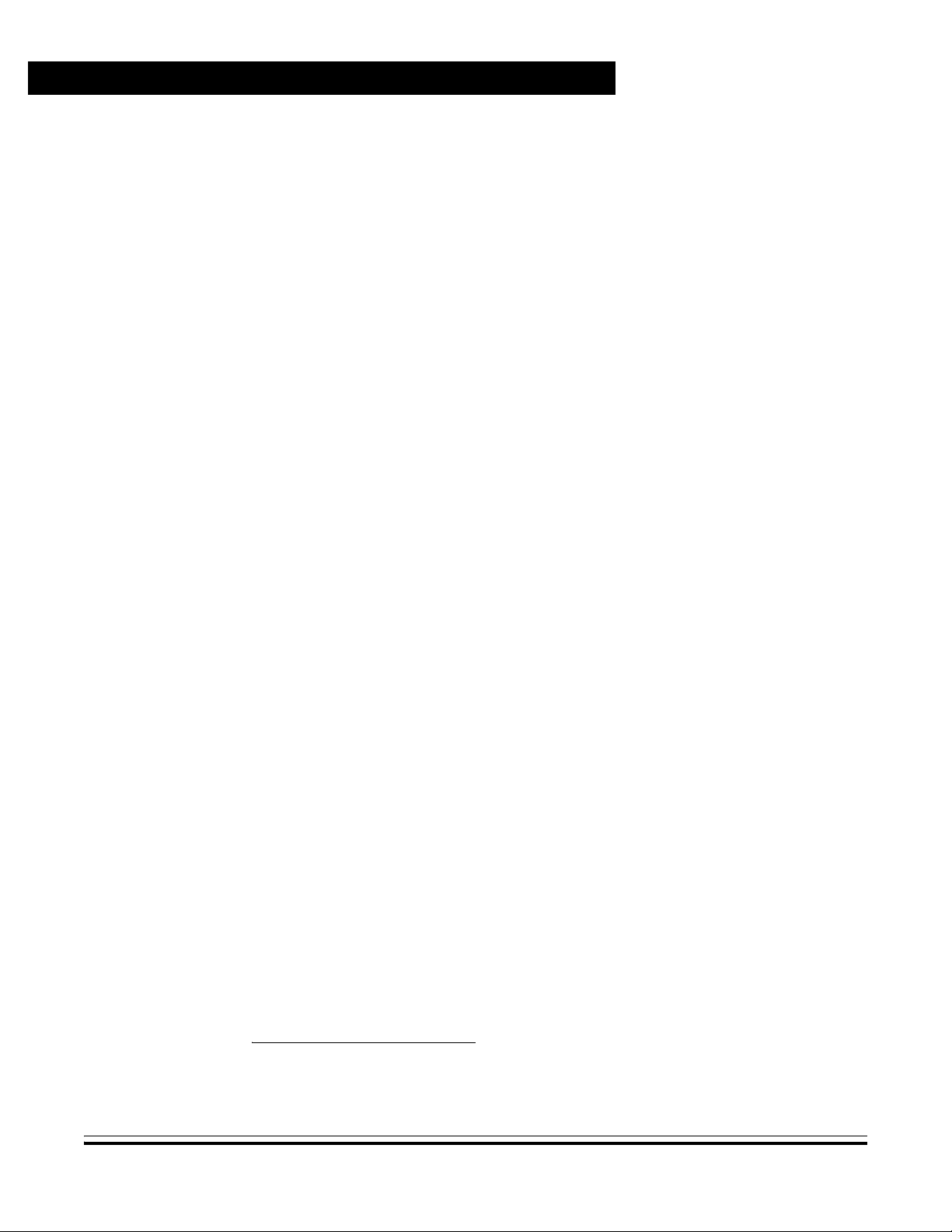

Figure 3-1 provides a summary of the input/output (I/O) registers.

Addr.Register Name Bit 7654321Bit 0

ADC Status and Control

$003C

$003D Unimplemented

$003E

$003F

Register (ADSCR)

See page 42.

ADC Data Register

(ADR)

See page 43.

ADC Input Clock Register

(ADICLK)

See page 44.

Read: COCO

Write:

Reset:00011111

Read:

Write:

Reset: Indeterminate after reset

Read:

Write:

Reset:00000000

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

ADIV2 ADIV1 ADIV0

AIEN ADCO CH4 CH3 CH2 CH1 CH0

00000

= Unimplemented

Figure 3-1. ADC I/O Register Summary

MC68HC908QF4 — Rev. 1.0 Data Sheet

MOTOROLA Analog-to-Digital Converter (ADC) 37

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Analog-to-Digital Converter (ADC)

nc...

I

cale Semiconductor,

Frees

PTA0/AD0/TCH0/KBI0

PTA1/AD1/TCH1/KBI1

PTA2/IRQ

/KBI2/TCLK

PTA

PTB

V

MODE

PLLEN

DATA

BS

OP1

GND

REXT

XTAL1

XTAL0

UPCLK

PFD

DDRA

M68HC08 CPU

DDRB

MC68HC908QF4

4096 BYTES

USER FLASH

CC

PTA3/RST

PTA4/OSC2/AD2/KBI4

PTA5/OSC1/AD3/KBI5

TRANSMITTER

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

/KBI3

PTB0

PTB1

PTB2

PTB3

PTB4

PTB5

PTB6

PTB7

8-BIT ADC

128 BYTES RAM

UHF

Figure 3-2. Block Diagram Highlighting ADC Block and Pins

CLOCK

GENERATOR

(OSCILLATOR)

SYSTEM INTEGRATION

MODULE

SINGLE INTERRUPT

MODULE

BREAK

MODULE

POWER-ON RESET

MODULE

KEYBOARD INTERRUPT

MODULE

16-BIT TIMER

MODULE

COP

MODULE

MONITOR ROM

POWER SUPPLY

V

DD

V

SS

Data Sheet MC68HC908QF4 — Rev. 1.0

38 Analog-to-Digital Converter (ADC) MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

3.3 Functional Description

INTERNAL

DATA BUS

READ DDRA

nc...

I

WRITE DDRA

Freescale Semiconductor, Inc.

Analog-to-Digital Converter (ADC)

Functional Description

Four ADC channels are available for sampling external sources at pins PTA0,