Freescale MC68HC908JL3E, MC68HC908JK3E, MC68HC908JK1E, MC68HRC908JL3E, MC68HRC908JK3E Technical Data

...

MC68HC908JL3E/JK3E/JK1E

MC68HRC908JL3E/JK3E/JK1E

MC68HLC908JL3E/JK3E/JK1E

MC68HC908KL3E/KK3E

MC68HC08JL3E/JK3E

MC68HRC08JL3E/JK3E

Data Sheet

M68HC08

Microcontrollers

MC68HC908JL3E

Rev. 3

11/2004

freescale.com

MC68HC908JL8/JK3E/JK1E

MC68HRC908JL8/JK3E/JK1E

MC68HLC908JL8/JK3E/JK1E

MC68HC908KL3E/KK3E

MC68HC08JL3E/JK3E

MC68HRC08JL3E/JK3E

Data Sheet

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be

the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://www.freescale.com

The following revision history table summarizes changes contained in this document. For your

convenience, the page number designators have been linked to the appropriate location.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 3

Revision History

Date

Nov 2004 3

Dec 2002 2

May 2002 2 First general release. —

Revision

Level

Description

Added appendix B for ROM parts. 159–166

Added appendix C for ADC-less parts. 167–170

Added appendix A for low-volt devices. 153–224

Updated Monitor Mode Circuit (Figure 7-1) and Monitor Mode Entry

Requirements and Options (Table 7-1) in Monitor ROM section.

Page

Number(s)

76, 77

MC68HC908JL3E Family Data Sheet, Rev. 3

4 Freescale Semiconductor

List of Chapters

Chapter 1 General Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Chapter 2 Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Chapter 3 Configuration Registers (CONFIG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Chapter 4 Central Processor Unit (CPU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Chapter 5 System Integration Module (SIM). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Chapter 6 Oscillator (OSC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Chapter 7 Monitor ROM (MON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Chapter 8 Timer Interface Module (TIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Chapter 9 Analog-to-Digital Converter (ADC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Chapter 10 Input/Output (I/O) Ports. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

Chapter 11 External Interrupt (IRQ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

Chapter 12 Keyboard Interrupt Module (KBI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

Chapter 13 Computer Operating Properly (COP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

Chapter 14 Low Voltage Inhibit (LVI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

Chapter 15 Break Module (BREAK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

Chapter 16 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

Chapter 17 Mechanical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

Chapter 18 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

Appendix A MC68HLC908JL3E/JK3E/JK1E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Appendix B MC68H(R)C08JL3E/JK3E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

Appendix C MC68HC908KL3E/KK3E. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 5

List of Chapters

MC68HC908JL3E Family Data Sheet, Rev. 3

6 Freescale Semiconductor

Table of Contents

Chapter 1

General Description

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.3 MCU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.4 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.5 Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Chapter 2

Memory

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.2 I/O Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.3 Monitor ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.4 Random-Access Memory (RAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.5 FLASH Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.6 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.7 FLASH Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.8 FLASH Page Erase Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.9 FLASH Mass Erase Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.10 FLASH Program Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.11 FLASH Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.12 FLASH Block Protect Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Chapter 3

Configuration Registers (CONFIG)

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.3 Configuration Register 1 (CONFIG1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.4 Configuration Register 2 (CONFIG2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Chapter 4

Central Processor Unit (CPU)

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.3 CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3.1 Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3.2 Index Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3.3 Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.3.4 Program Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 7

Table of Contents

4.3.5 Condition Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.4 Arithmetic/Logic Unit (ALU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.5 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.5.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.6 CPU During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4.7 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4.8 Opcode Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Chapter 5

System Integration Module (SIM)

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

5.2 SIM Bus Clock Control and Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5.2.1 Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5.2.2 Clock Start-Up from POR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5.2.3 Clocks in Stop Mode and Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5.3 Reset and System Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

5.3.1 External Pin Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

5.3.2 Active Resets from Internal Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

5.3.2.1 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.3.2.2 Computer Operating Properly (COP) Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.3.2.3 Illegal Opcode Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.3.2.4 Illegal Address Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.3.2.5 LVI Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.4 SIM Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.4.1 SIM Counter During Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.4.2 SIM Counter During Stop Mode Recovery. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.4.3 SIM Counter and Reset States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.5 Exception Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.5.1 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.5.1.1 Hardware Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.5.1.2 SWI Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.5.2 Interrupt Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.5.2.1 Interrupt Status Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.5.2.2 Interrupt Status Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.5.2.3 Interrupt Status Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.5.3 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.5.4 Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.5.5 Status Flag Protection in Break Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.6 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

5.6.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

5.6.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

5.7 SIM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

5.7.1 Break Status Register (BSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

5.7.2 Reset Status Register (RSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5.7.3 Break Flag Control Register (BFCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

MC68HC908JL3E Family Data Sheet, Rev. 3

8 Freescale Semiconductor

Chapter 6

Oscillator (OSC)

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.2 X-tal Oscillator (MC68HC908JL3E/JK3E/JK1E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.3 RC Oscillator (MC68HRC908JL3E/JK3E/JK1E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.4 I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.4.1 Crystal Amplifier Input Pin (OSC1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.4.2 Crystal Amplifier Output Pin (OSC2/PTA6/RCCLK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.4.3 Oscillator Enable Signal (SIMOSCEN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.4.4 X-tal Oscillator Clock (XTALCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.4.5 RC Oscillator Clock (RCCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.4.6 Oscillator Out 2 (2OSCOUT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.4.7 Oscillator Out (OSCOUT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.5 Low Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.5.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.6 Oscillator During Break Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Chapter 7

Monitor ROM (MON)

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

7.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

7.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

7.3.1 Entering Monitor Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

7.3.2 Baud Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

7.3.3 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

7.3.4 Echoing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.3.5 Break Signal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.3.6 Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.4 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Chapter 8

Timer Interface Module (TIM)

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

8.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

8.3 Pin Name Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

8.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

8.4.1 TIM Counter Prescaler. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

8.4.2 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

8.4.3 Output Compare. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

8.4.3.1 Unbuffered Output Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

8.4.3.2 Buffered Output Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

8.4.4 Pulse Width Modulation (PWM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

8.4.4.1 Unbuffered PWM Signal Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

8.4.4.2 Buffered PWM Signal Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

8.4.4.3 PWM Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 9

Table of Contents

8.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

8.6 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

8.6.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

8.6.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

8.7 TIM During Break Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

8.8 I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

8.9 I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

8.9.1 TIM Status and Control Register (TSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

8.9.2 TIM Counter Registers (TCNTH:TCNTL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

8.9.3 TIM Counter Modulo Registers (TMODH:TMODL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

8.9.4 TIM Channel Status and Control Registers (TSC0:TSC1). . . . . . . . . . . . . . . . . . . . . . . . . . 95

8.9.5 TIM Channel Registers (TCH0H/L:TCH1H/L) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Chapter 9

Analog-to-Digital Converter (ADC)

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

9.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

9.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

9.3.1 ADC Port I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

9.3.2 Voltage Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

9.3.3 Conversion Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

9.3.4 Continuous Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

9.3.5 Accuracy and Precision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

9.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

9.5 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

9.5.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

9.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

9.6 I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

9.6.1 ADC Voltage In (ADCVIN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

9.7 I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

9.7.1 ADC Status and Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

9.7.2 ADC Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

9.7.3 ADC Input Clock Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Chapter 10

Input/Output (I/O) Ports

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

10.2 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

10.2.1 Port A Data Register (PTA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

10.2.2 Data Direction Register A (DDRA). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

10.2.3 Port A Input Pull-up Enable Register (PTAPUE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

10.3 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

10.3.1 Port B Data Register (PTB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

10.3.2 Data Direction Register B (DDRB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

10.4 Port D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

10.4.1 Port D Data Register (PTD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

MC68HC908JL3E Family Data Sheet, Rev. 3

10 Freescale Semiconductor

10.4.2 Data Direction Register D (DDRD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

10.4.3 Port D Control Register (PDCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Chapter 11

External Interrupt (IRQ)

11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

11.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

11.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

11.3.1 IRQ1

11.4 IRQ Module During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

11.5 IRQ Status and Control Register (INTSCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Chapter 12

Keyboard Interrupt Module (KBI)

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

12.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

12.3 I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

12.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

12.4.1 Keyboard Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

12.5 Keyboard Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

12.5.1 Keyboard Status and Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

12.5.2 Keyboard Interrupt Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

12.6 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

12.6.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

12.6.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

12.7 Keyboard Module During Break Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Chapter 13

Computer Operating Properly (COP)

13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

13.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

13.3 I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

13.3.1 2OSCOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

13.3.2 COPCTL Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

13.3.3 Power-On Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

13.3.4 Internal Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

13.3.5 Reset Vector Fetch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

13.3.6 COPD (COP Disable). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

13.3.7 COPRS (COP Rate Select) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

13.4 COP Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

13.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

13.6 Monitor Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

13.7 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

13.7.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

13.7.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

13.8 COP Module During Break Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 11

Table of Contents

Chapter 14

Low Voltage Inhibit (LVI)

14.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

14.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

14.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

14.4 LVI Control Register (CONFIG2/CONFIG1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

14.5 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

14.5.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

14.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Chapter 15

Break Module (BREAK)

15.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

15.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

15.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

15.3.1 Flag Protection During Break Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

15.3.2 CPU During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

15.3.3 TIM During Break Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

15.3.4 COP During Break Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

15.4 Break Module Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

15.4.1 Break Status and Control Register (BRKSCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

15.4.2 Break Address Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

15.4.3 Break Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

15.4.4 Break Flag Control Register (BFCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

15.5 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

15.5.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

15.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Chapter 16

Electrical Specifications

16.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

16.2 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

16.3 Functional Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

16.4 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

16.5 5V DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

16.6 5V Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

16.7 5V Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

16.8 3V DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

16.9 3V Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

16.10 3V Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

16.11 Typical Supply Currents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

16.12 ADC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

16.13 Memory Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

MC68HC908JL3E Family Data Sheet, Rev. 3

12 Freescale Semiconductor

Chapter 17

Mechanical Specifications

17.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

17.2 20-Pin PDIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

17.3 20-Pin SOIC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

17.4 28-Pin PDIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

17.5 28-Pin SOIC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

17.6 48-Pin LQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Chapter 18

Ordering Information

18.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

18.2 MC Order Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Appendix A

MC68HLC908JL3E/JK3E/JK1E

A.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

A.2 FLASH Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

A.3 Low-Voltage Inhibit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

A.4 Oscillator Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

A.5 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

A.5.1 Functional Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

A.5.2 DC Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

A.5.3 Control Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

A.5.4 Oscillator Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

A.5.5 ADC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

A.5.6 Memory Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

A.6 MC Order Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Appendix B

MC68H(R)C08JL3E/JK3E

B.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

B.2 MCU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

B.3 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

B.4 Reserved Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

B.5 Monitor ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

B.6 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

B.6.1 DC Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

B.6.2 5V Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

B.6.3 Memory Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

B.7 MC Order Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 13

Table of Contents

Appendix C

MC68HC908KL3E/KK3E

C.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

C.2 MCU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

C.3 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

C.4 Reserved Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

C.5 Reserved Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

C.6 Order Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

MC68HC908JL3E Family Data Sheet, Rev. 3

14 Freescale Semiconductor

Chapter 1 General Description

1.1 Introduction

The MC68H(R)C908JL3E is a member of the low-cost, high-performance M68HC08 Family of 8-bit

microcontroller units (MCUs). The M68HC08 Family is based on the customer-specified integrated circuit

(CSIC) design strategy. All MCUs in the family use the enhanced M68HC08 central processor unit

(CPU08) and are available with a variety of modules, memory sizes and types, and package types.

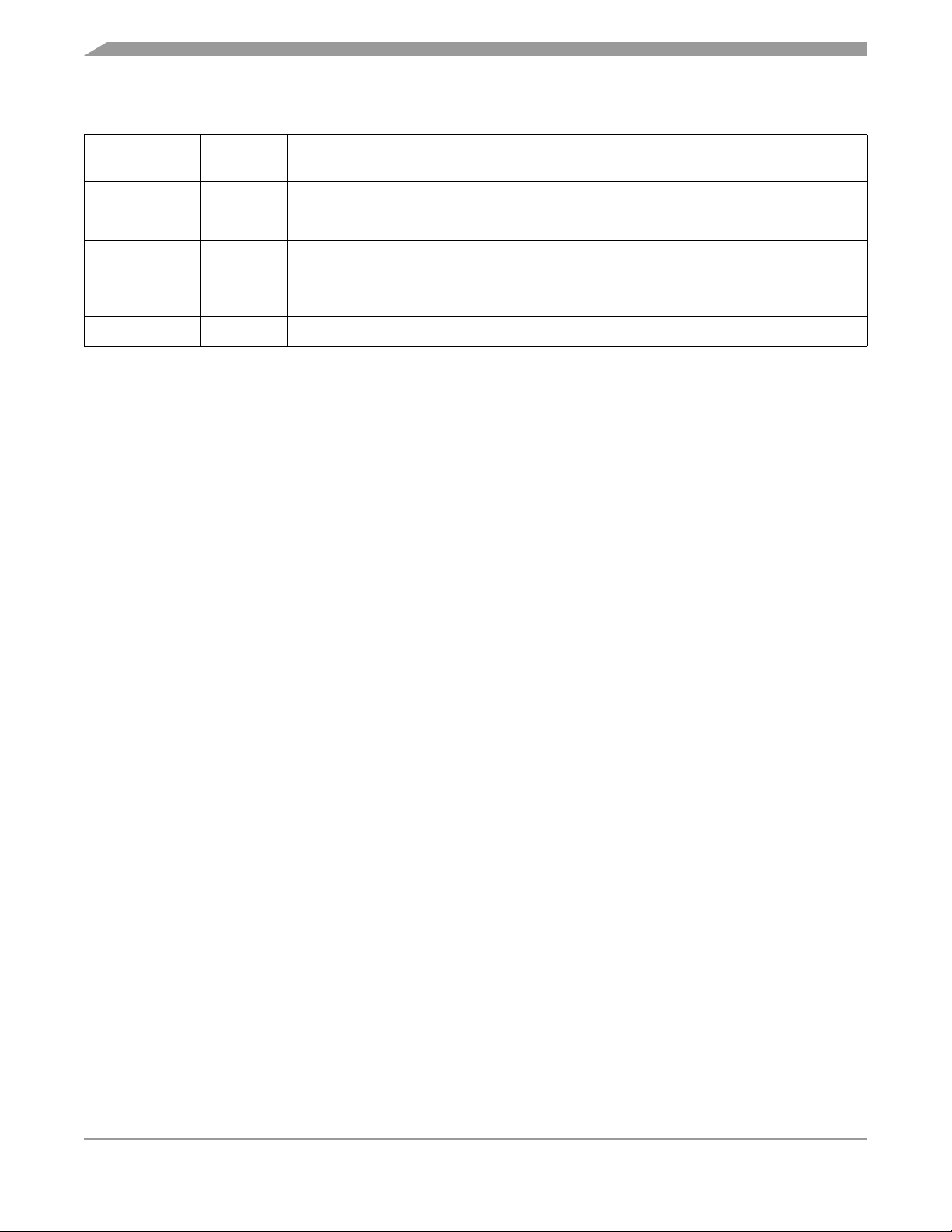

A list of MC68H(R)C908JL3E device variations is shown in Table 1-1.

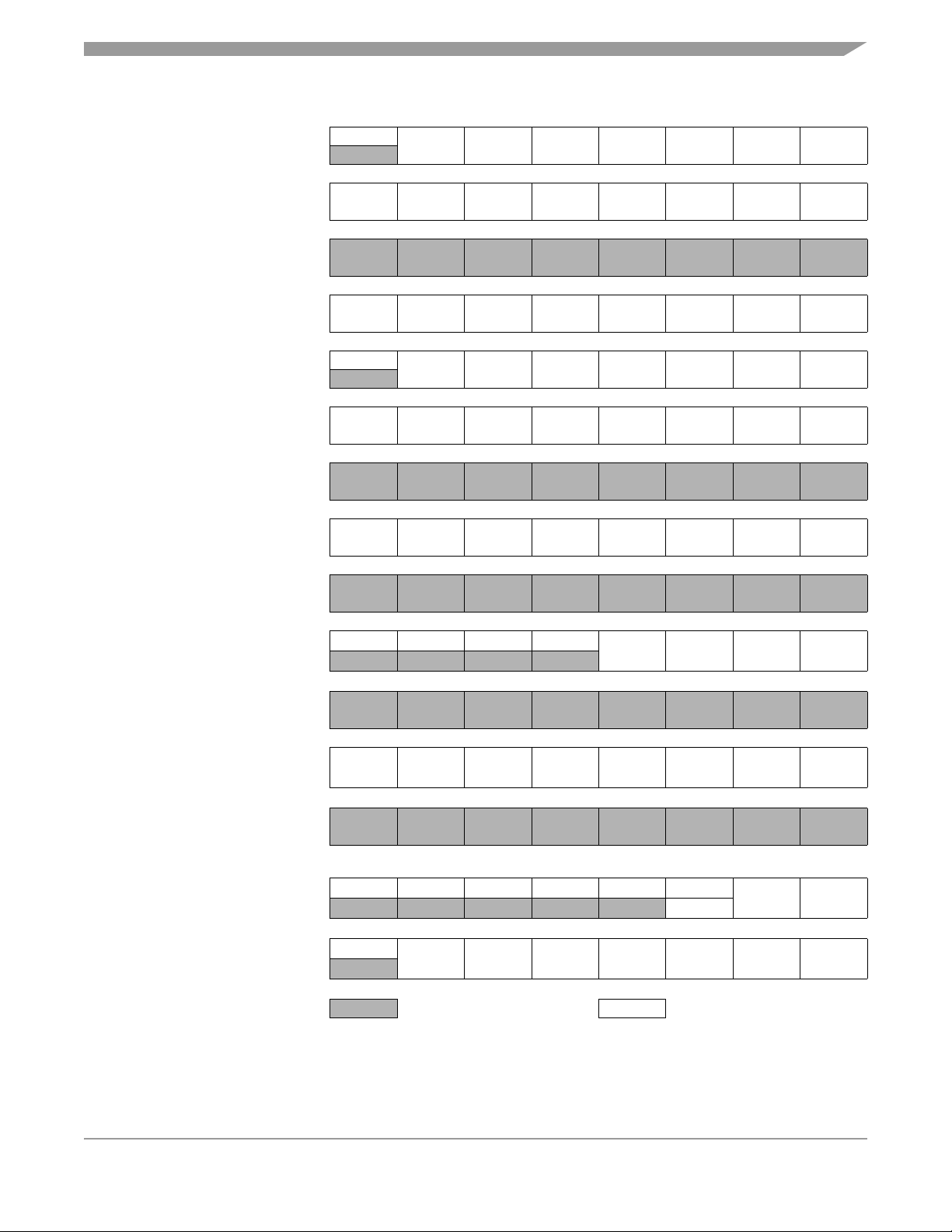

Table 1-1. Summary of Device Variations

Device

Type

FLASH 3V, 5V Yes Yes

Low Voltage

FLASH

(2)

ROM

FLASH,

ADC-less

Operating

Voltage

2.2 to 5.5V No Yes XTAL

(1)

3V, 5V Yes Yes

(3)

3V, 5 V Yes No XTAL 4,096 bytes FLASH

LVI ADC

Oscillator

Option

XTAL

RC

XTAL

RC

Memory

4,096 bytes FLASH

1,536 bytes FLASH 20 MC68HC908JK1E

4,096 bytes FLASH

1,536 bytes FLASH 20 MC68HRC908JK3E

4,096 bytes FLASH

1,536 bytes FLASH 20 MC68HLC908JK1E

4,096 bytes ROM

Pin

Count

28 MC68HC908JL3E

20 MC68HC908JK3E

28 MC68HRC908JL3E

20 MC68HRC908JK3E

28 MC68HLC908JL3E

20 MC68HLC908JK3E

28 MC68HC08JL3E

20 MC68HC08JK3E

28 MC68HRC08JL3E

20 MC68HRC08JK3E

28 MC68HC908KL3E

20 MC68HC908KK3E

Device

1. Low-voltage FLASH devices are documented in Appendix A MC68HLC908JL3E/JK3E/JK1E.

2. ROM devices are documented in Appendix B MC68H(R)C08JL3E/JK3E.

3. FLASH, ADC-less devices are documented in Appendix C MC68HC908KL3E/KK3E.

All references to the MC68H(R)C908JL3E in this data book apply equally to the MC68H(R)C908JK3E

and MC68H(R)C908JK1E, unless otherwise stated.

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 15

General Description

1.2 Features

Features of the MC68H(R)C908JL3E include the following:

• EMC enhanced version of MC68H(R)C908JL3/JK3/JK1

• High-performance M68HC08 architecture

• Fully upward-compatible object code with M6805, M146805, and M68HC05 Families

• Low-power design; fully static with stop and wait modes

• Maximum internal bus frequency:

– 8-MHz at 5V operating voltage

– 4-MHz at 3V operating voltage

• Oscillator options:

– Crystal oscillator for MC68HC908JL3E/JK3E/JK1E

– RC oscillator for MC68HRC908JL3E/JK3E/JK1E

• User program FLASH memory with security

– 4,096 bytes for MC68H(R)C908JL3E/JK3E

– 1,536 bytes for MC68H(R)C908JK1E

• 128 bytes of on-chip RAM

• 2-channel, 16-bit timer interface module (TIM)

• 12-channel, 8-bit analog-to-digital converter (ADC)

• 23 general purpose I/O ports for MC68H(R)C908JL3E:

– 7 keyboard interrupt with internal pull-up

(6 keyboard interrupt for MC68HC908JL3E)

– 10 LED drivers (sink)

–2 × 25mA open-drain I/O with pull-up

• 15 general purpose I/O ports for MC68H(R)C908JK3E/JK1E:

– 1 keyboard interrupt with internal pull-up

(MC68HRC908JK3E/JK1E only)

– 4 LED drivers (sink)

–2 × 25mA open-drain I/O with pull-up

– 10-channel ADC

• System protection features:

– Optional computer operating properly (COP) reset

– Optional low-voltage detection with reset and selectable trip points for 3V and 5V operation

– Illegal opcode detection with reset

– Illegal address detection with reset

• Master reset pin with internal pull-up and power-on reset

•IRQ1

with schmitt-trigger input and programmable pull-up

• 28-pin PDIP, 28-pin SOIC, and 48-pin LQFP packages for MC68H(R)C908JL3E

• 20-pin PDIP and 20-pin SOIC packages for MC68H(R)C908JK3E/JK1E

(1)

feature

1. No security feature is absolutely secure. However, Motorola’s strategy is to make reading or copying the FLASH difficult for

unauthorized users.

MC68HC908JL3E Family Data Sheet, Rev. 3

16 Freescale Semiconductor

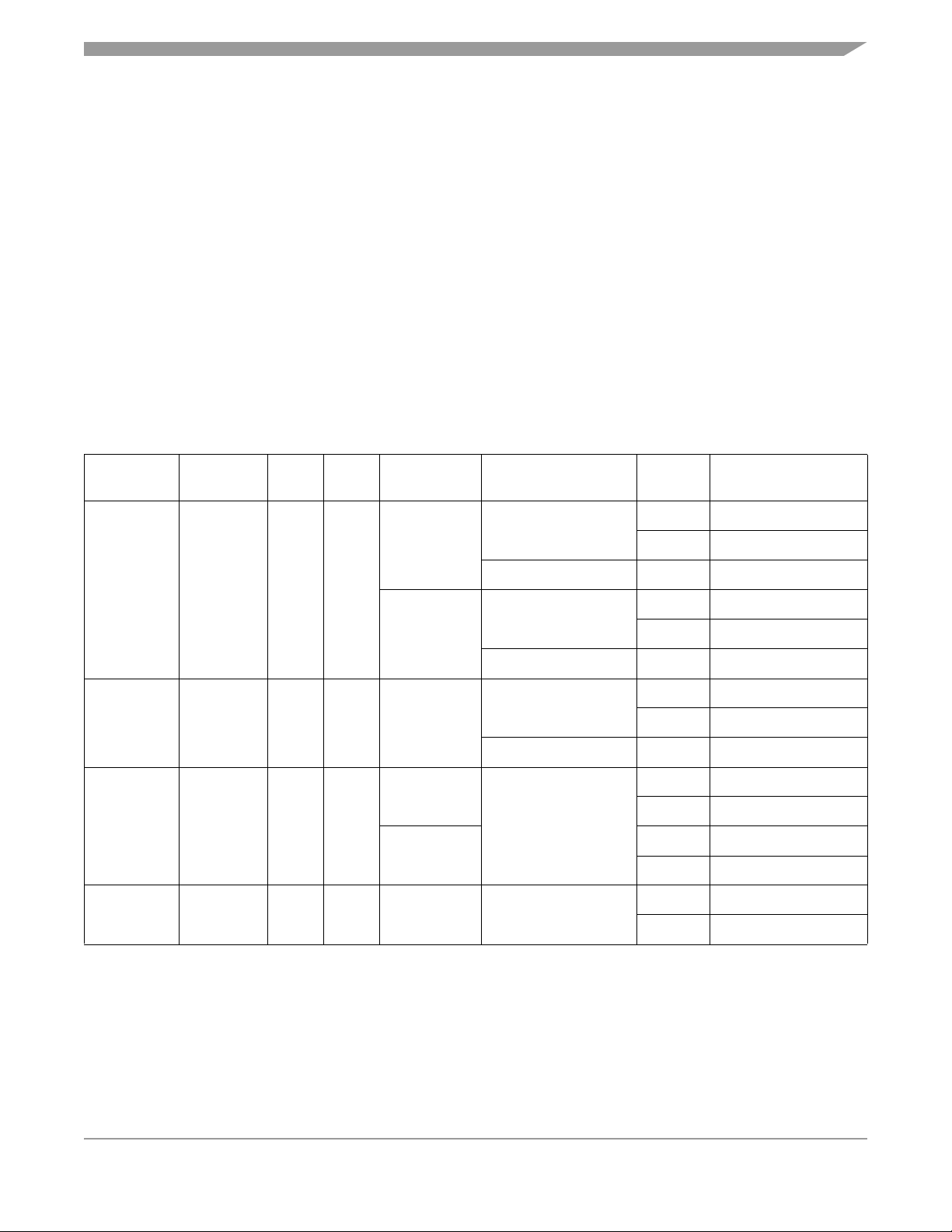

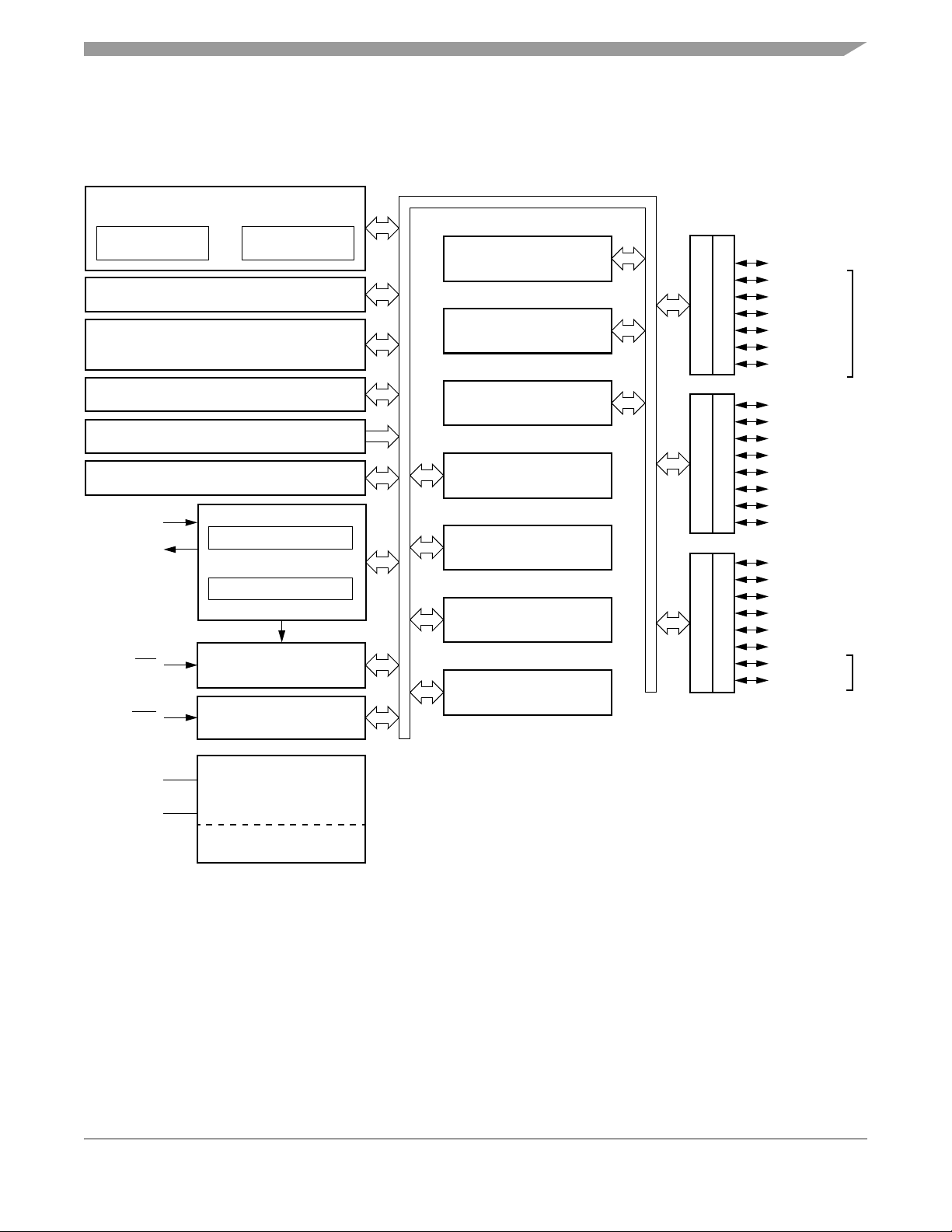

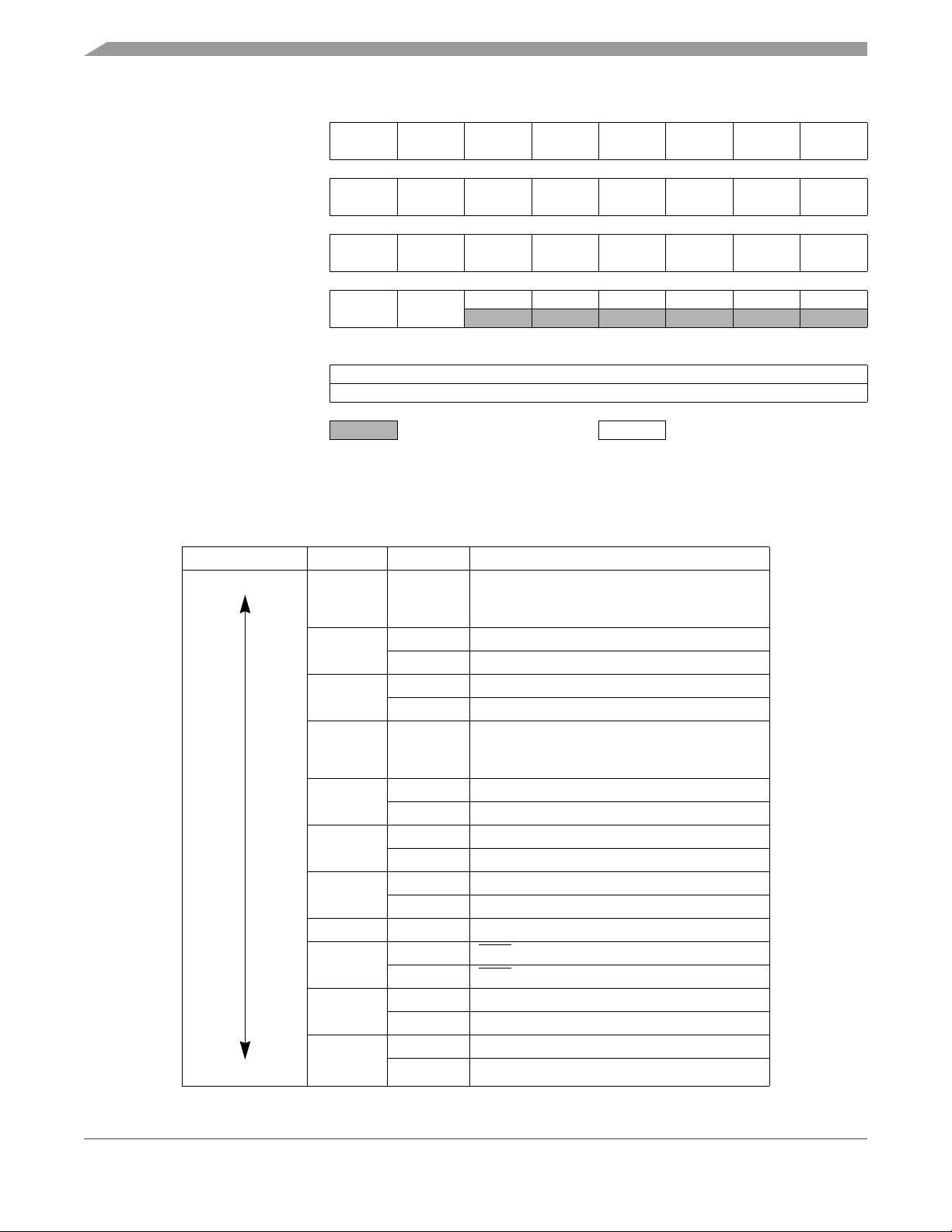

1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68H(R)C908JL3E.

INTERNAL BUS

M68HC08 CPU

MCU Block Diagram

CPU

REGISTERS

ARITHMETIC/LOGIC

UNIT (ALU)

CONTROL AND STATUS REGISTERS — 64 BYTES

USER FLASH:

MC68H(R)C908JK3E/JL3E — 4,096 BYTES

MC68H(R)C908JK1E — 1,536 BYTES

USER RAM — 128 BYTES

MONITOR ROM — 960 BYTES

USER FLASH VECTOR SPACE — 48 BYTES

MC68HC908JL3E/JK3E/JK1E

X-TAL OSCILLATOR

MC68HRC908JL3E/JK3E/JK1E

¥

OSC1

OSC2

RC OSCILLATOR

* RST

* IRQ1

SYSTEM INTEGRATION

MODULE

EXTERNAL INTERRUPT

MODULE

KEYBOARD INTERRUPT

MODULE

8-BIT ANALOG-TO-DIGITAL

CONVERTER MODULE

2-CHANNEL TIMER INTERFACE

MODULE

BREAK

MODULE

COMPUTER OPERATING

PROPERLY MODULE

POWER-ON RESET

MODULE

LOW-VOLTAGE INHIBIT

MODULE

DDRA

DDRB

DDRD

PORTA

PORTB

PORTD

PTA6/KBI6**

PTA5/KBI5**

PTA4/KBI4**

PTA3/KBI3**

PTA2/KBI2**

PTA1/KBI1**

PTA0/KBI0**

PTB7/ADC7

PTB6/ADC6

PTB5/ADC5

PTB4/ADC4

PTB3/ADC3

PTB2/ADC2

PTB1/ADC1

PTB0/ADC0

†‡

PTD7**

†‡

PTD6**

PTD5/TCH1

PTD4/TCH0

PTD3/ADC8

PTD2/ADC9

PTD1/ADC10

PTD0/ADC11

¥

‡

‡

‡

#

‡

‡

‡

‡

‡

#

* Pin contains integrated pull-up device.

VDD

POWER

VSS

** Pin contains programmable pull-up device.

† 25mA open-drain if output pin.

‡ LED direct sink pin.

# Pins available on MC68H(R)C908JL3E only.

ADC REFERENCE

¥ Shared pin:

MC68HC908JL3E/JK3E/JK1E — OSC2

MC68HRC908JL3E/JK3E/JK1E — RCCLK/PTA6/KBI6

Figure 1-1. MCU Block Diagram

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 17

General Description

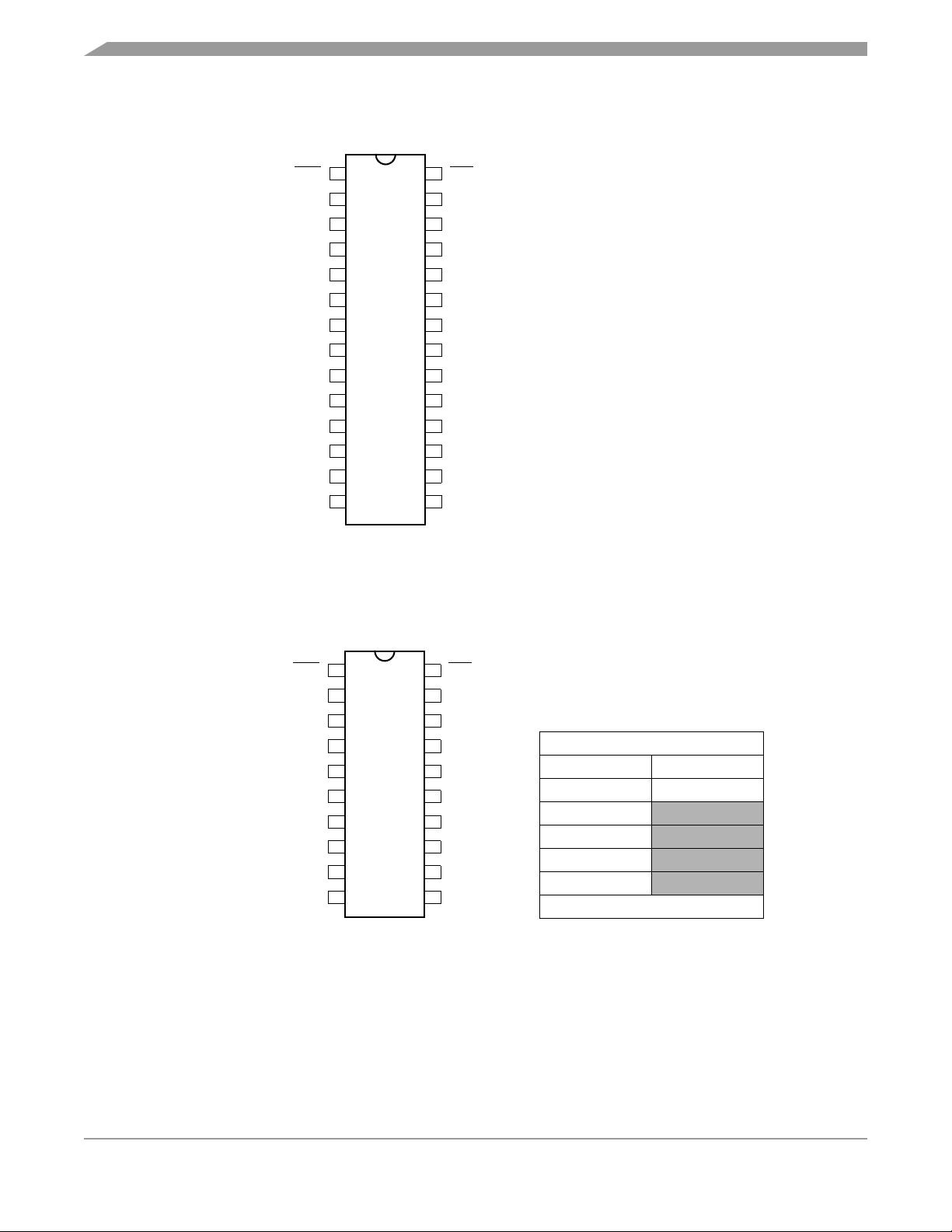

1.4 Pin Assignments

IRQ1

PTA0/KBI0

VSS

OSC1

OSC2/RCCLK/PTA6/KBI

PTA1/KBI1

VDD

PTA2/KBI2

PTA3/KBI3

PTB7/ADC7

PTB6/ADC6

PTB5/ADC5

PTD7

PTD6

MC68H(R)C908JL3E

Figure 1-2. 28-Pin PDIP/SOIC Pin Assignment

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RST

PTA5/KBI5

PTD4/TCH0

PTD5/TCH1

PTD2/ADC9

PTA4/KBI4

PTD3/ADC8

PTB0/ADC0

PTB1/ADC1

PTD1/ADC10

PTB2/ADC2

PTB3/ADC3

PTD0/ADC11

PTB4/ADC4

IRQ1

VSS

OSC1

OSC2/RCCLK/PTA6/KBI

VDD

PTB7/ADC7

PTB6/ADC6

PTB5/ADC5

PTD7

PTD6

MC68H(R)C908JK3E/JK1E

Figure 1-3. 20-Pin PDIP/SOIC Pin Assignment

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

RST

PTD4/TCH0

PTD5/TCH1

PTD2/ADC9

PTD3/ADC8

PTB0/ADC0

PTB1/ADC1

PTB2/ADC2

PTB3/ADC3

PTB4/ADC4

Pins not available on 20-pin packages

PTA0/KBI0 PTD0/ADC11

PTA1/KBI1 PTD1/ADC10

PTA2/KBI2

PTA3/KBI3

PTA4/KBI4

PTA5/KBI5

Internal pads are unconnected.

MC68HC908JL3E Family Data Sheet, Rev. 3

18 Freescale Semiconductor

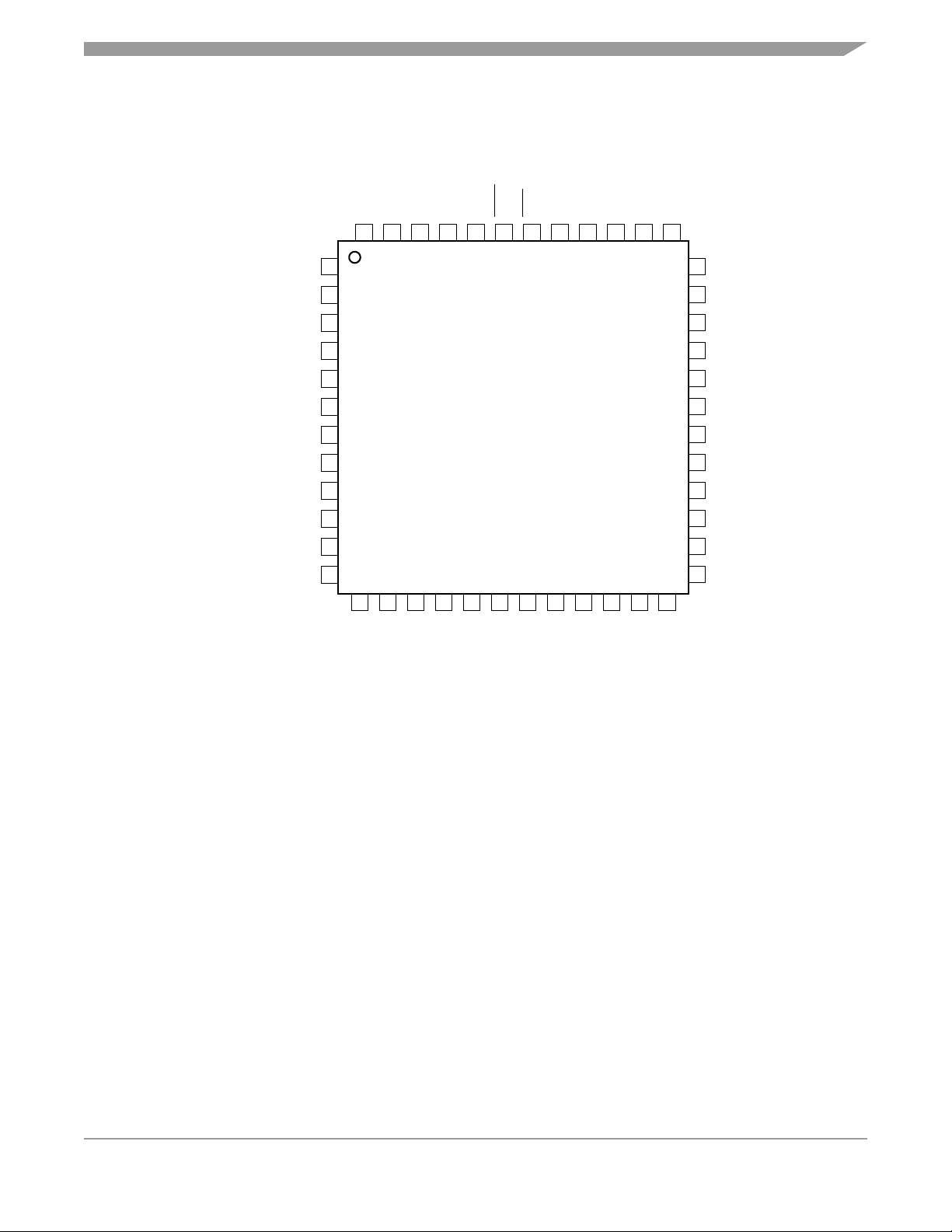

NC

Pin Assignments

RST

IRQ1

PTA0/KBI0

VSS

NC

NC

NC

48

47

46

45

44

1

43

42

PTA5/KBI5

41

PTD5/TCH1

PTD4/TCH0

40

39

NC

38

NC

37

36

NC

NC

OSC1

OSC2/RCCLK/PTA6/KBI6

PTA1/KBI1

NC

VDD

PTA2/KBI2

PTA3KBI3

PTB7/ADC7

NC

NC

NC: No connection

2

3

4

5

6

MC68H(R)C908JL3E

7

8

9

10

11

12

13

NC

14

15

NC

PTB6/ADC6

16

17

18

PTD7

PTD6

PTB5/ADC5

20

19

PTB4/ADC4

21

PTB3/ADC3

PTD0/ADC11

22

23

NC

PTB2/ADC2

35

34

33

32

31

30

29

28

27

26

25

24

NC

NC

NC

PTD2/ADC9

PTA4/KBI4

PTD3/ADC8

NC

PTB0/ADC0

PTB1/ADC1

PTD1/ADC10

NC

NC

Figure 1-4. 48-Pin LQFP Pin Assignment

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 19

General Description

1.5 Pin Functions

Description of the pin functions are provided in Table 1-2.

Table 1-2. Pin Functions

PIN NAME PIN DESCRIPTION IN/OUT VOLTAGE LEVEL

VDD Power supply. In 5V or 3V

VSS Power supply ground Out 0V

RST

IRQ1

OSC1 X-tal or RC oscillator input. In Analog

OSC2

PTA[0:6]

PTB[0:7]

RESET input, active low.

With Internal pull-up and schmitt trigger input.

External IRQ pin.

With software programmable internal pull-up and schmitt

trigger input.

This pin is also used for mode entry selection.

MC68HC908JL3E/JK3E/JK1E:

X-tal oscillator output, this is the inverting OSC1 signal.

MC68HRC908JL3E/JK3E/JK1E:

Default is RC oscillator clock output, RCCLK.

Shared with PTA6/KBI6, with programmable pull-up.

7-bit general purpose I/O port. In/Out VDD

Shared with 7 keyboard interrupts KBI[0:6]. In VDD

Each pin has programmable internal pull-up device. In VDD

PTA[0:5] have LED direct sink capability In VSS

8-bit general purpose I/O port. In/Out VDD

Shared with 8 ADC inputs, ADC[0:7]. In Analog

8-bit general purpose I/O port. In/Out VDD

Input VDD

Input

Out Analog

In/Out VDD

VDD to VDD+V

HI

PTD[3:0] shared with 4 ADC inputs, ADC[8:11]. Input Analog

PTD[0:7]

PTD[4:5] shared with TIM channels, TCH0 and TCH1. In/Out VDD

PTD[2:3], PTD[6:7] have LED direct sink capability In VSS

PTD[6:7] can be configured as 25mA open-drain output with

pull-up.

In/Out VDD

NOTE

On the MC68H(R)C908JK3E/JK1E, the following pins are not available:

PTA0, PTA1, PTA2, PTA3, PTA4, PTA5, PTD0, and PTD1.

MC68HC908JL3E Family Data Sheet, Rev. 3

20 Freescale Semiconductor

Chapter 2 Memory

2.1 Introduction

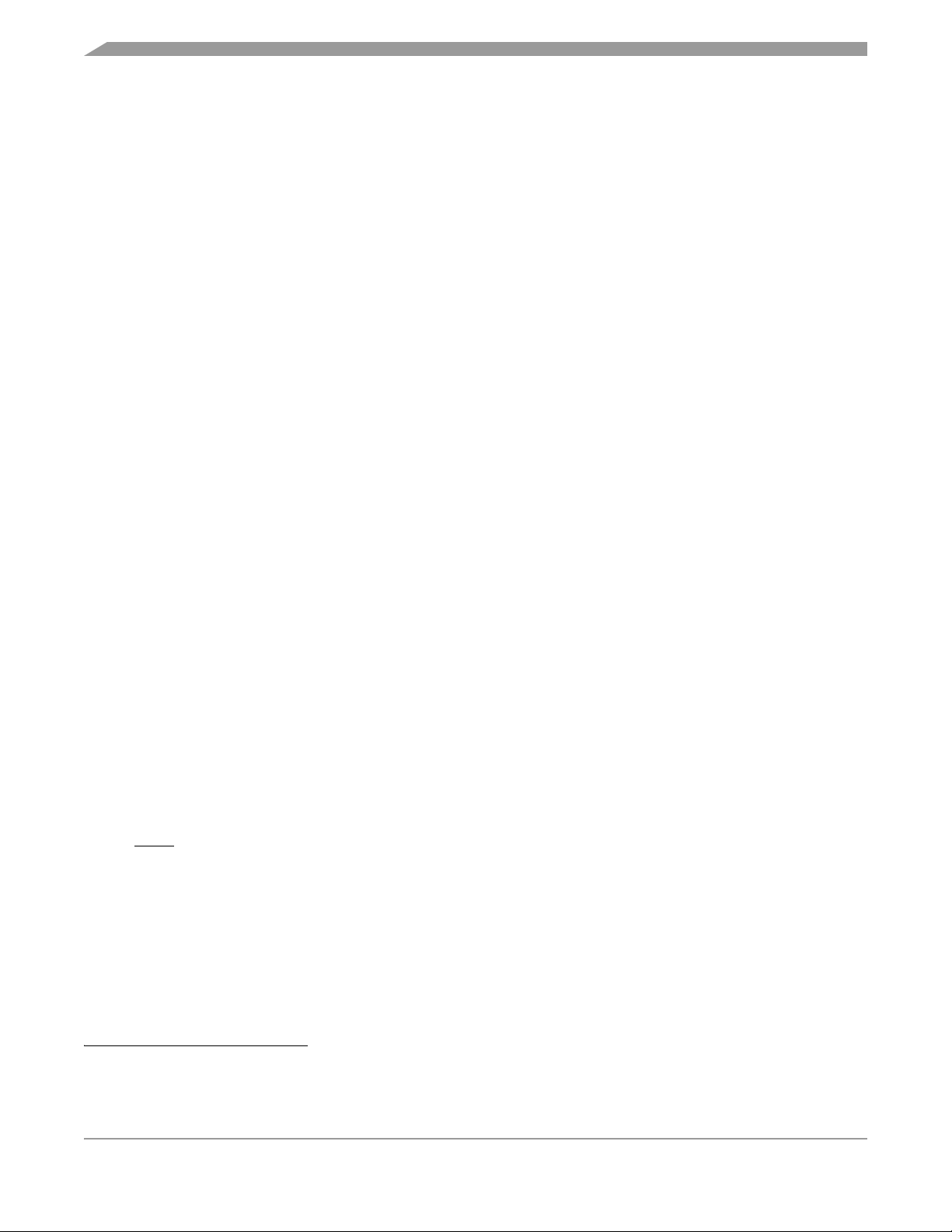

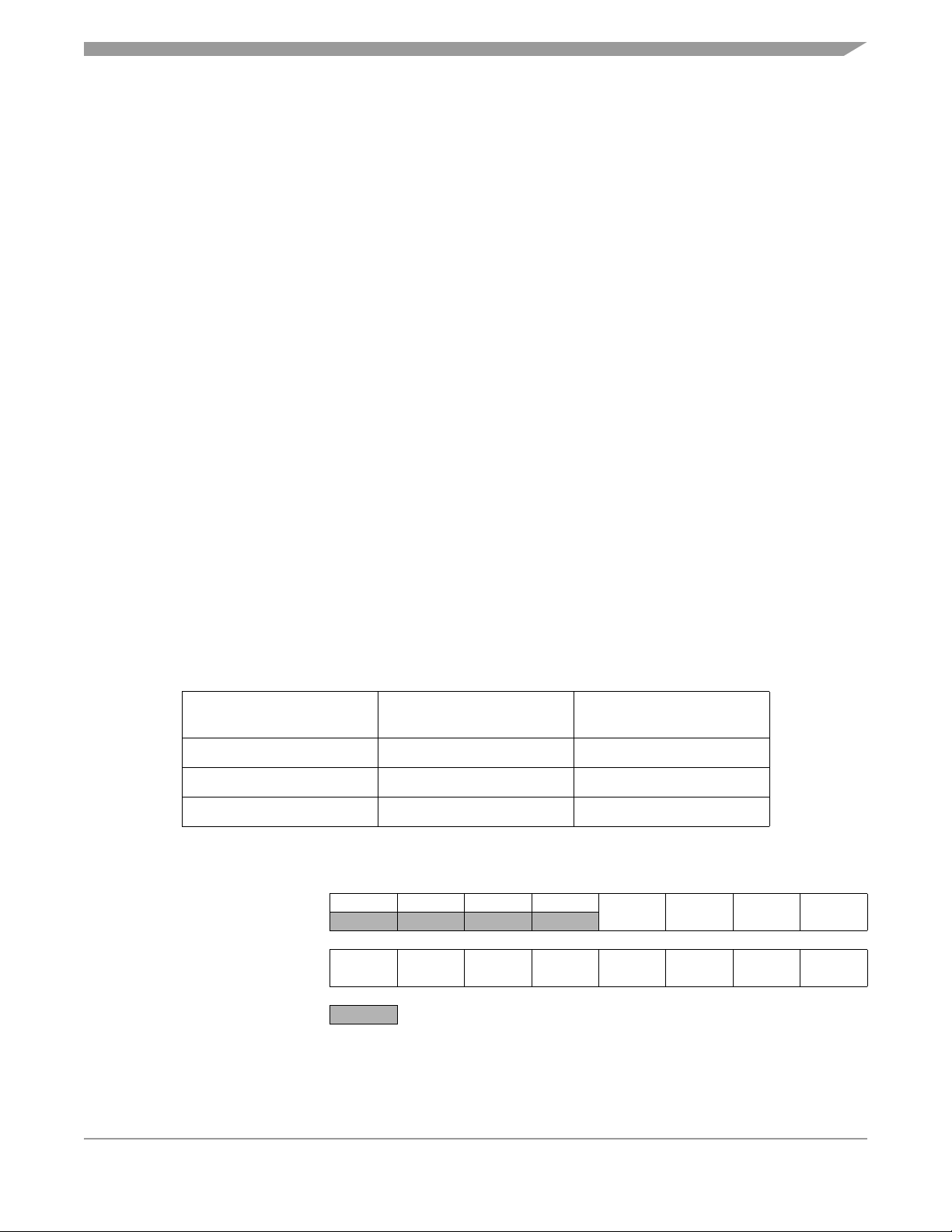

The CPU08 can address 64 Kbytes of memory space. The memory map, shown in Figure 2-1, includes:

• 4,096 bytes of user FLASH — MC68H(R)C908JL3E/JK3E

1,536 bytes of user FLASH — MC68H(R)C908JK1E

• 128 bytes of RAM

• 48 bytes of user-defined vectors

• 960 bytes of Monitor ROM

2.2 I/O Section

Addresses $0000–$003F, shown in Figure 2-2, contain most of the control, status, and data registers.

Additional I/O registers have the following addresses:

• $FE00; Break Status Register, BSR

• $FE01; Reset Status Register, RSR

•$FE02; Reserved

• $FE03; Break Flag Control Register, BFCR

• $FE04; Interrupt Status Register 1, INT1

• $FE05; Interrupt Status Register 2, INT2

• $FE06; Interrupt Status Register 3, INT3

•$FE07; Reserved

• $FE08; FLASH Control Register, FLCR

• $FE09; FLASH Block Protect Register, FLBPR

•$FE0A; Reserved

•$FE0B; Reserved

• $FE0C; Break Address Register High, BRKH

• $FE0D; Break Address Register Low, BRKL

• $FE0E; Break Status and Control Register, BRKSCR

•$FE0F; Reserved

• $FFFF; COP Control Register, COPCTL

2.3 Monitor ROM

The 960 bytes at addresses $FC00–$FDFF and $FE10–$FFCF are reserved ROM addresses that

contain the instructions for the monitor functions. (See Chapter 7 Monitor ROM (MON).)

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 21

Memory

$0000

↓

$003F

$0040

↓

$007F

$0080

↓

$00FF

$0100

↓

$EBFF

$EC00

↓

$FBFF

$FC00

↓

$FDFF

$FE00 BREAK STATUS REGISTER (BSR)

$FE01 RESET STATUS REGISTER (RSR)

$FE02 RESERVED (UBAR)

$FE03 BREAK FLAG CONTROL REGISTER (BFCR)

$FE04 INTERRUPT STATUS REGISTER 1 (INT1)

I/O REGISTERS

64 BYTES

RESERVED

64 BYTES

RAM

128 BYTES

UNIMPLEMENTED

60,160 BYTES

FLASH MEMORY

MC68H(R)C908JL3E/JK3E

4,096 BYTES

MONITOR ROM

512 BYTES

UNIMPLEMENTED

62,720 BYTES

FLASH MEMORY

MC68H(R)C908JK1E

1,536 BYTES

$0100

↓

$F5FF

$F600

↓

$FBFF

$FE05 INTERRUPT STATUS REGISTER 2 (INT2)

$FE06 INTERRUPT STATUS REGISTER 3 (INT3)

$FE07 RESERVED

$FE08 FLASH CONTROL REGISTER (FLCR)

$FE09 FLASH BLOCK PROTECT REGISTER (FLBPR)

$FE0A RESERVED

$FE0B RESERVED

$FE0C BREAK ADDRESS HIGH REGISTER (BRKH)

$FE0D BREAK ADDRESS LOW REGISTER (BRKL)

$FE0E BREAK STATUS AND CONTROL REGISTER (BRKSCR)

$FE0F RESERVED

$FE10

↓

$FFCF

$FFD0

↓

$FFFF

MONITOR ROM

448 BYTES

USER VECTORS

48 BYTES

Figure 2-1. Memory Map

MC68HC908JL3E Family Data Sheet, Rev. 3

22 Freescale Semiconductor

Monitor ROM

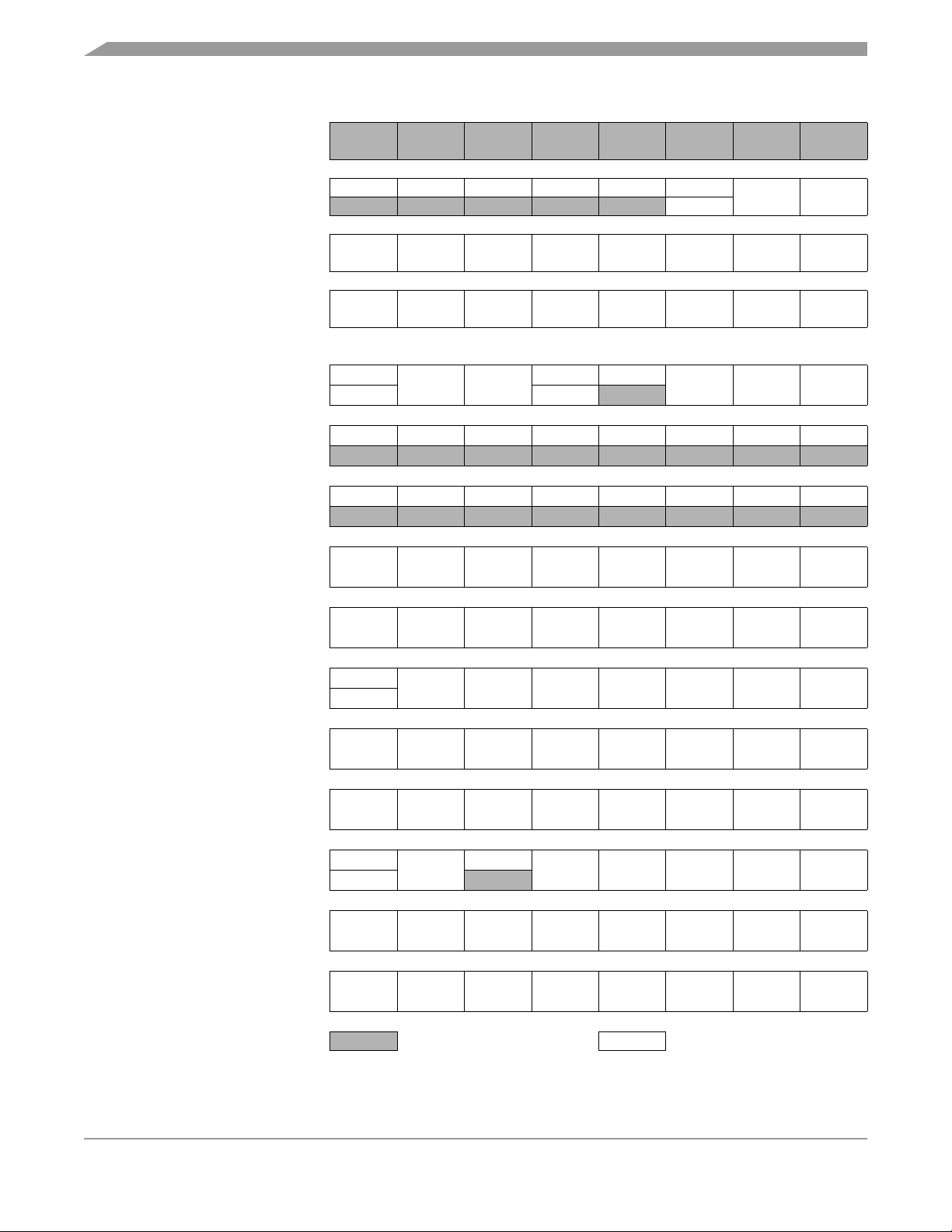

Addr.Register Name Bit 7654321Bit 0

$0000 Port A Data Register (PTA)

$0001 Port B Data Register (PTB)

$0002 Unimplemented

Read: 0

Write:

Reset: Unaffected by reset

Read:

Write:

Reset: Unaffected by reset

Read:

Write:

PTB7 PTB6 PTB5 PTB4 PTB3 PTB2 PTB1 PTB0

PTA6 PTA5 PTA4 PTA3 PTA2 PTA1 PTA0

$0003 Port D Data Register (PTD)

$0004

$0005

$0006 Unimplemented

$0007

$0008

$0009

$000A

$000B

$000C

Data Direction Register A

Data Direction Register B

Data Direction Register D

↓

Unimplemented

Port D Control Register

↓

Unimplemented

(DDRA)

(DDRB)

(DDRD)

(PDCR)

Port A Input Pull-up

$000D

Enable Register

(PTAPUE)

$000E

↓

$0019

Unimplemented

Read:

Write:

Reset: Unaffected by reset

Read: 0

Write:

Reset:00000000

Read:

Write:

Reset:00000000

Read:

Write:

Read:

Write:

Reset:00000000

Read:

Write:

Read: 0000

Write:

Reset:

Read:

Write:

Read:

Write:

Reset:

Read:

Write:

PTD7 PTD6 PTD5 PTD4 PTD3 PTD2 PTD1 PTD0

DDRA6 DDRA5 DDRA4 DDRA3 DDRA2 DDRA1 DDRA0

DDRB7 DDRB6 DDRB5 DDRB4 DDRB3 DDRB2 DDRB1 DDRB0

DDRD7 DDRD6 DDRD5 DDRD4 DDRD3 DDRD2 DDRD1 DDRD0

SLOWD7 SLOWD6 PTDPU7 PTDPU6

00000000

PTA6EN PTAPUE6 PTAPUE5 PTAPUE4 PTAPUE3 PTAPUE2 PTAPUE1 PTAPUE0

00000000

Read: 0000KEYF 0

Write:

Reset:

Read: 0

Write:

Reset:

00000000

KBIE6 KBIE5 KBIE4 KBIE3 KBIE2 KBIE1 KBIE0

00000000

= Unimplemented R = Reserved

ACKK

IMASKK MODEK

$001A

$001B

Keyboard Status and

Control Register

(KBSCR)

Keyboard Interrupt

Enable Register

(KBIER)

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 4)

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 23

Memory

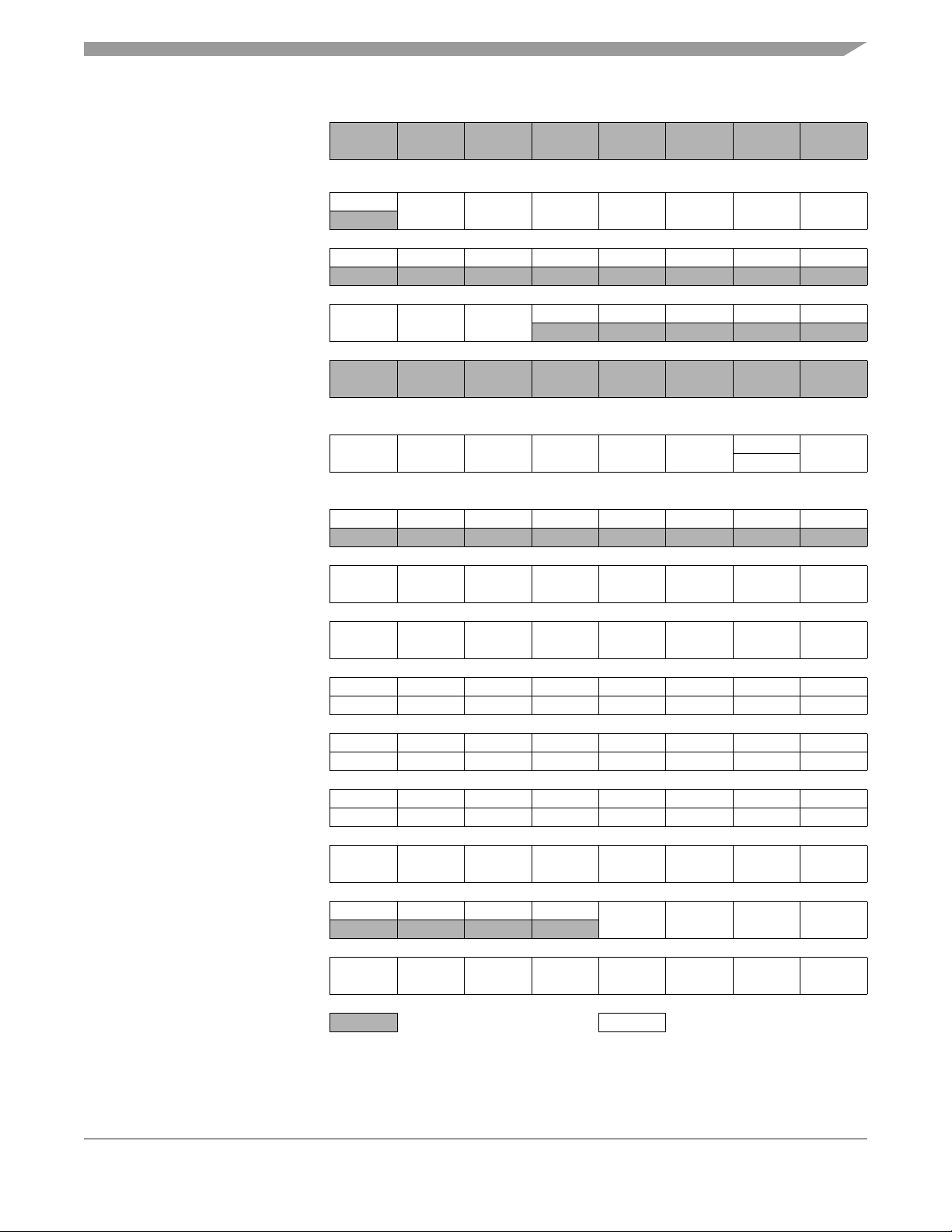

Addr.Register Name Bit 7654321Bit 0

$001C

Unimplemented

Read:

Write:

IRQ Status and Control

$001D

$001E

$001F

† One-time writable register after each reset. * LVIT1 and LVIT0 reset to logic 0 by a power-on reset (POR) only.

Configuration Register 2

Configuration Register 1

Register

(INTSCR)

(CONFIG2)

(CONFIG1)

TIM Status and Control

$0020

Register

TIM Counter Register

$0021

(TCNTH)

TIM Counter Register

$0022

(TCNTL)

TIM Counter Modulo

$0023

Register High

(TMODH)

TIM Counter Modulo

$0024

Register Low

(TMODL)

TIM Channel 0 Status and

$0025

Control Register

(TSC0)

TIM Channel 0

$0026

Register High

(TCH0H)

TIM Channel 0

$0027

Register Low

(TCH0L)

TIM Channel 1 Status and

$0028

Control Register

(TSC1)

TIM Channel 1

$0029

Register High

(TCH1H)

TIM Channel 1

$002A

Register Low

(TCH1L)

Read:0000IRQF10

Write:

Reset:00000000

Read:

IRQPUDRRLVIT1LVIT0RRR

Write:

†

Reset:0000*0*000

Read:

Write:

†

Reset:00000000

Read: TOF

Write: 0 TRST

(TSC)

Reset:

COPRS R R LVID R SSREC STOP COPD

TOIE TSTOP

00100000

00

Read: Bit15 Bit14 Bit13 Bit12 Bit11 Bit10 Bit9 Bit8

Write:

High

Reset:

00000000

Read: Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

Write:

Low

Reset:

Read:

Write:

Reset:

Read:

Write:

Reset:

Read: CH0F

Write: 0

Reset:

Read:

Write:

Reset:

Read:

Write:

Reset:

Read: CH1F

Write: 0

Reset:

Read:

Write:

Reset:

Read:

Write:

Reset:

00000000

Bit15 Bit14 Bit13 Bit12 Bit11 Bit10 Bit9 Bit8

11111111

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

11111111

CH0IE MS0B MS0A ELS0B ELS0A TOV0 CH0MAX

00000000

Bit15 Bit14 Bit13 Bit12 Bit11 Bit10 Bit9 Bit8

Indeterminate after reset

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

Indeterminate after reset

CH1IE

00000000

0

MS1A ELS1B ELS1A TOV1 CH1MAX

Bit15 Bit14 Bit13 Bit12 Bit11 Bit10 Bit9 Bit8

Indeterminate after reset

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

Indeterminate after reset

= Unimplemented R = Reserved

ACK1

IMASK1 MODE1

PS2 PS1 PS0

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 4)

MC68HC908JL3E Family Data Sheet, Rev. 3

24 Freescale Semiconductor

Monitor ROM

Addr.Register Name Bit 7654321Bit 0

$002B

$003B

↓

Unimplemented

Read:

Write:

ADC Status and Control

$003C

$003D

$003E

$003F

$FE00 Break Status Register (BSR)

$FE01 Reset Status Register (RSR)

$FE02 Reserved

$FE03

$FE04

$FE05

$FE06

$FE07 Reserved

ADC Data Register

ADC Input Clock Register

Note: Writing a logic 0 clears SBSW.

Break Flag Control

Interrupt Status Register 1

Interrupt Status Register 2

Interrupt Status Register 3

Register

(ADSCR)

(ADR)

(ADICLK)

Unimplemented

Register

(BFCR)

(INT1)

(INT2)

(INT3)

Read: COCO

Write:

Reset:00011111

Read:AD7AD6AD5AD4AD3AD2AD1AD0

Write:

Reset: Indeterminate after reset

Read:

Write:

Reset:00000000

Read:

Write:

Read:

Write: See note

Reset: 0

Read: POR PIN COP ILOP ILAD MODRST LVI 0

Write:

POR:10000000

Read:

Write:

Read:

Write:

Reset: 0

Read: 0 IF5 IF4 IF3 0 IF1 0 0

Write:RRRRRRRR

Reset:00000000

Read:IF140000000

Write:RRRRRRRR

Reset:00000000

Read:0000000IF15

Write:RRRRRRRR

Reset:00000000

Read:

Write:

ADIV2 ADIV1 ADIV0

RRRRRR

RRRRRRRR

BCFERRRRRRR

RRRRRRRR

AIEN ADCO ADCH4 ADCH3 ADCH2 ADCH1 ADCH0

00000

SBSW

R

$FE08

$FE09

FLASH Control Register

(FLCR)

FLASH Block Protect

Register (FLBPR)

Read:0000

Write:

Reset:00000000

Read:

Write:

Reset:00000000

BPR7 BPR6 BPR5 BPR4 BPR3 BPR2 BPR1 BPR0

= Unimplemented R = Reserved

HVEN MASS ERASE PGM

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 4)

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 25

Memory

Addr.Register Name Bit 7654321Bit 0

$FE0A

$FE0B

$FE0C

$FE0D

$FE0E

↓

Break Address High

Break Address low

Break Status and Control

Reserved

Register

(BRKH)

Register

(BRKL)

Register

(BRKSCR)

Read:

Write:

Read:

Write:

Reset:00000000

Read:

Write:

Reset:00000000

Read:

Write:

Reset:00000000

RRRRRRRR

Bit15 Bit14 Bit13 Bit12 Bit11 Bit10 Bit9 Bit8

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

BRKE BRKA

000000

$FFFF

COP Control Register

(COPCTL)

Read: Low byte of reset vector

Write: Writing clears COP counter (any value)

Reset: Unaffected by reset

= Unimplemented R = Reserved

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 4)

Table 2-1. Vector Addresses

Vector Priority INT Flag Address Vector

Lowest

—

IF15

IF14

IF13

↓

IF6

IF5

IF4

IF3

IF2 — Not Used

IF1

—

—

Highest

$FFD0

↓

$FFDD

$FFDE ADC Conversion Complete Vector (High)

$FFDF ADC Conversion Complete Vector (Low)

$FFE0 Keyboard Vector (High)

$FFE1 Keyboard Vector (Low)

— Not Used

$FFF2 TIM Overflow Vector (High)

$FFF3 TIM Overflow Vector (Low)

$FFF4 TIM Channel 1 Vector (High)

$FFF5 TIM Channel 1 Vector (Low)

$FFF6 TIM Channel 0 Vector (High)

$FFF7 TIM Channel 0 Vector (Low)

$FFFA IRQ1

$FFFB IRQ1

$FFFC SWI Vector (High)

$FFFD SWI Vector (Low)

$FFFE Reset Vector (High)

$FFFF Reset Vector (Low)

Not Used

Vector (High)

Vector (Low)

MC68HC908JL3E Family Data Sheet, Rev. 3

26 Freescale Semiconductor

Random-Access Memory (RAM)

2.4 Random-Access Memory (RAM)

Addresses $0080 through $00FF are RAM locations. The location of the stack RAM is programmable.

The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

NOTE

For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 128 bytes of RAM. Because the location of the stack RAM is programmable, all page

zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved

from its reset location at $00FF, direct addressing mode instructions can access efficiently all page zero

RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global

variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU

registers.

NOTE

For M6805 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack

pointer decrements during pushes and increments during pulls.

NOTE

Be careful when using nested subroutines. The CPU may overwrite data in

the RAM during a subroutine or during the interrupt stacking operation.

2.5 FLASH Memory

This sub-section describes the operation of the embedded FLASH memory. The FLASH memory can be

read, programmed, and erased from a single external supply. The program and erase operations are

enabled through the use of an internal charge pump.

Device

MC68H(R)C908JL3E 4,096 $EC00—$FBFF

MC68H(R)C908JK3E 4,096 $EC00—$FBFF

MC68H(R)C908JK1E 1,536 $F600—$FBFF

Addr.Register Name Bit 7654321Bit 0

Read:0000

Write:

Reset:00000000

Read:

Write:

Reset:00000000

BPR7 BPR6 BPR5 BPR4 BPR3 BPR2 BPR1 BPR0

$FE08

$FE09

FLASH Control Register

(FLCR)

FLASH Block Protect

Register

(FLBPR)

FLASH Memory Size

(Bytes)

= Unimplemented

Memory Address Range

HVEN MASS ERASE PGM

Figure 2-3. FLASH I/O Register Summary

MC68HC908JL3E Family Data Sheet, Rev. 3

Freescale Semiconductor 27

Memory

2.6 Functional Description

The FLASH memory consists of an array of 4,096 or 1,536 bytes with an additional 48 bytes for user

vectors. The minimum size of FLASH memory that can be erased is 64 bytes (a page); and the maximum

size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and

erase operations are facilitated through control bits in the Flash Control Register (FLCR). Details for these

operations appear later in this section. The address ranges for the user memory and vectors are:

• $EC00–$FBFF; user memory; 4,096 bytes; MC68H(R)C908JL3E/JK3E

$F600–$FBFF; user memory; 1,536 bytes;

MC68H(R)C908JK1E

• $FFD0–$FFFF; user interrupt vectors; 48 bytes

NOTE

An erased bit reads as logic 1 and a programmed bit reads as logic 0.

A security feature prevents viewing of the FLASH contents.

(1)

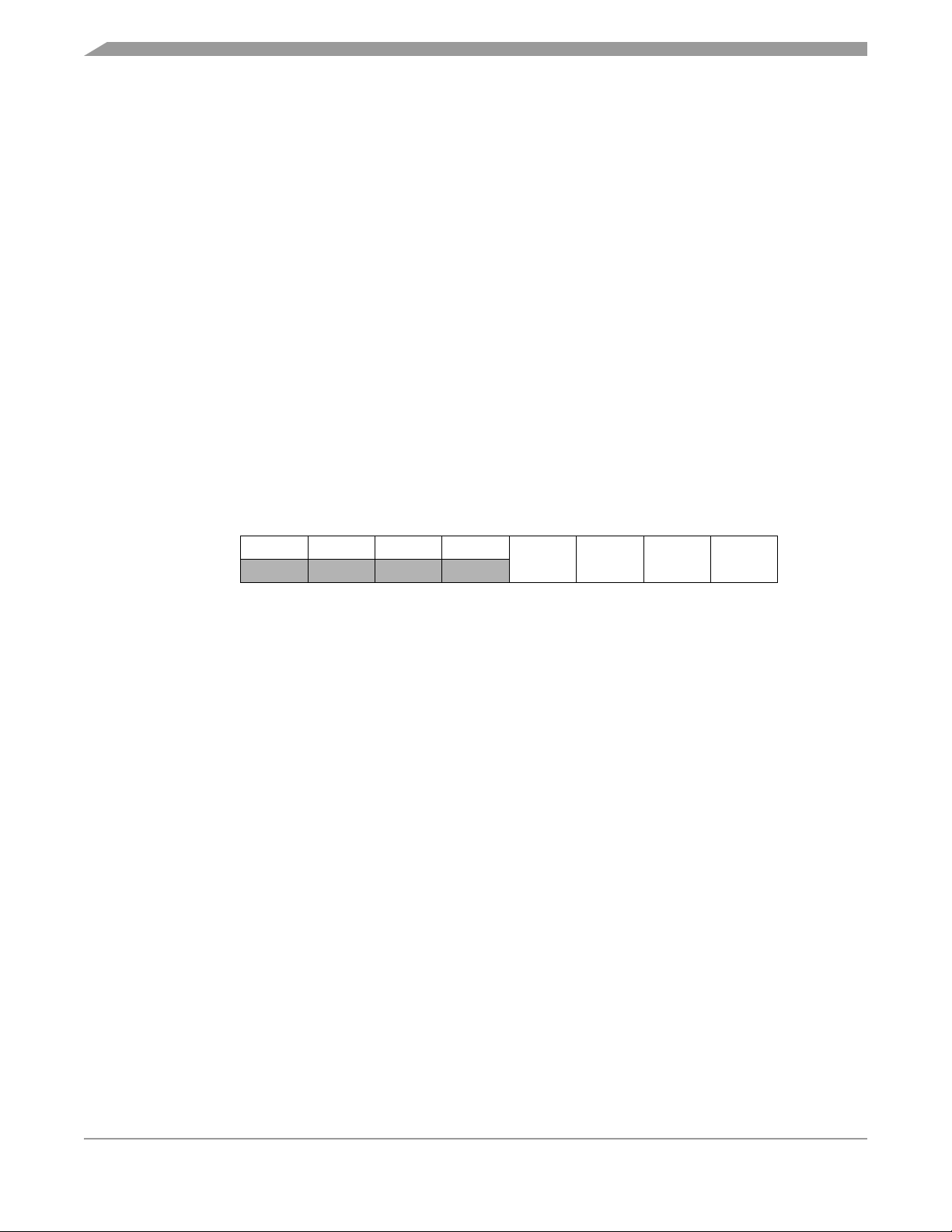

2.7 FLASH Control Register

The FLASH Control Register controls FLASH program and erase operations.

Address: $FE08

Bit 7654321Bit 0

Read:0000

Write:

Reset:00000000

HVEN MASS ERASE PGM

Figure 2-4. FLASH Control Register (FLCR)

HVEN — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or

erase operation. It can only be set if either PGM= 1 or ERASE=1 and the proper sequence for program

or erase is followed.

1 = High voltage enabled to array and charge pump on

0 = High voltage disabled to array and charge pump off

MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation or page erase operation when the

ERASE bit is set.

1 = Mass erase operation selected

0 = Page erase operation selected

ERASE — Erase Control Bit

This read/write bit configures the memory for erase operation. This bit and the PGM bit should not be

set to 1 at the same time.

1 = Erase operation selected

0 = Erase operation not selected

1. No security feature is absolutely secure. However, Motorola’s strategy is to make reading or copying the FLASH difficult for

unauthorized users.

MC68HC908JL3E Family Data Sheet, Rev. 3

28 Freescale Semiconductor

FLASH Page Erase Operation

PGM — Program Control Bit

This read/write bit configures the memory for program operation. This bit and the ERASE bit should

not be set to 1 at the same time.

1 = Program operation selected

0 = Program operation not selected

2.8 FLASH Page Erase Operation

Use the following procedure to erase a page of FLASH memory. A page consists of 64 consecutive bytes

starting from addresses $XX00, $XX40, $XX80 or $XXC0. The 48-byte user interrupt vectors area also

forms a page. Any page within the 4K bytes user memory area ($EC00–$FBFF) can be erased alone.

The 48-byte user interrupt vectors cannot be erased by the page erase operation because of security

reasons. Mass erase is required to erase this page.

1. Set the ERASE bit and clear the MASS bit in the FLASH Control Register.

2. Write any data to any FLASH address within the page address range desired.

3. Wait for a time, t

4. Set the HVEN bit.

5. Wait for a time t

6. Clear the ERASE bit.

7. Wait for a time, t

8. Clear the HVEN bit.

9. After time, t

rcv

Programming and erasing of FLASH locations cannot be performed by

code being executed from the FLASH memory. While these operations

must be performed in the order as shown, but other unrelated operations

may occur between the steps.

(10µs).

nvs

(1ms).

Erase

(5µs).

nvh

(1µs), the memory can be accessed in read mode again.

NOTE

2.9 FLASH Mass Erase Operation

Use the following procedure to erase the entire FLASH memory:

1. Set both the ERASE bit and the MASS bit in the FLASH Control Register.

2. Write any data to any FLASH location within the FLASH memory address range.

3. Wait for a time, t

4. Set the HVEN bit.

5. Wait for a time t

6. Clear the ERASE bit.

7. Wait for a time, t

8. Clear the HVEN bit.

9. After time, t

rcv

Programming and erasing of FLASH locations cannot be performed by

code being executed from the FLASH memory. While these operations

must be performed in the order as shown, but other unrelated operations

may occur between the steps.

Freescale Semiconductor 29

(10µs).

nvs

nvh1

(4ms).

(100µs).

MErase

(1µs), the memory can be accessed in read mode again.

NOTE

MC68HC908JL3E Family Data Sheet, Rev. 3

Memory

2.10 FLASH Program Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes

starting from addresses $XX00, $XX20, $XX40, $XX60, $XX80, $XXA0, $XXC0 or $XXE0. Use this

step-by-step procedure to program a row of FLASH memory:

(Figure 2-5 shows a flowchart of the programming algorithm.)

1. Set the PGM bit. This configures the memory for program operation and enables the latching of

address and data for programming.

2. Write any data to any FLASH location within the address range of the row to be programmed.

3. Wait for a time, t

4. Set the HVEN bit.

5. Wait for a time, t

6. Write data to the byte being programmed.

(10µs).

nvs

(5µs).

pgs

7. Wait for time, t

PROG

(30µs).

8. Repeat step 6 and 7 until all the bytes within the row are programmed.

9. Clear the PGM bit.

10. Wait for time, t

nvh

(5µs).

11. Clear the HVEN bit.

12. After time, t

(1µs), the memory can be accessed in read mode again.

rcv

This program sequence is repeated throughout the memory until all data is programmed.

NOTE

The time between each FLASH address change (step 6 to step 6), or the

time between the last FLASH addressed programmed to clearing the PGM

bit (step 6 to step 10), must not exceed the maximum programming time,

max.

t

PROG

NOTE

Programming and erasing of FLASH locations cannot be performed by

code being executed from the FLASH memory. While these operations

must be performed in the order shown, other unrelated operations may

occur between the steps.

MC68HC908JL3E Family Data Sheet, Rev. 3

30 Freescale Semiconductor

Loading...

Loading...