Page 1

HC16

HC16

HC16

Freescale Semiconductor, Inc.

nc...

I

Order this document by

MC68HC16ZUM/AD

cale Semiconductor,

Frees

M68HC16Z Series

MC68HC16Z1

MC68CK16Z1

MC68CM16Z1

MC68HC16Z2

MC68HC16Z3

MC68HC16Z4

MC68CK16Z4

User’s Manual

NON-DISCLOSURE AGREEMENT REQUIRED

For More Information On This Product,

Go to: www.freescale.com

Page 2

User’s Manual

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Motorola reserves the right to make changes without further notice to

any products herein to improve reliability, function or design. Motorola

does not assume any liability arising out of the application or use of any

product or circuit described herein; neither does it convey any license

under its patent rights nor the rights of others. Motorola products are not

designed, intended, or authorized for use as components in systems

intendedforsurgicalimplant intothe body,or otherapplications intended

to support or sustain life, or for any other application in which the failure

of the Motorola product could create a situation where personal injury or

death may occur. Should Buyer purchase or use Motorola products for

any such unintended or unauthorized application, Buyer shall indemnify

and hold Motorola and its officers, employees, subsidiaries, affiliates,

and distributors harmless against all claims, costs, damages, and

expenses, and reasonable attorney fees arising out of, directly or

indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Motorola

was negligent regarding the design or manufacture of the part.

© Motorola, Inc., 1997

NON-DISCLOSURE AGREEMENT REQUIRED

User’s Manual M68HC16Z Series

2 MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 3

Freescale Semiconductor, Inc.

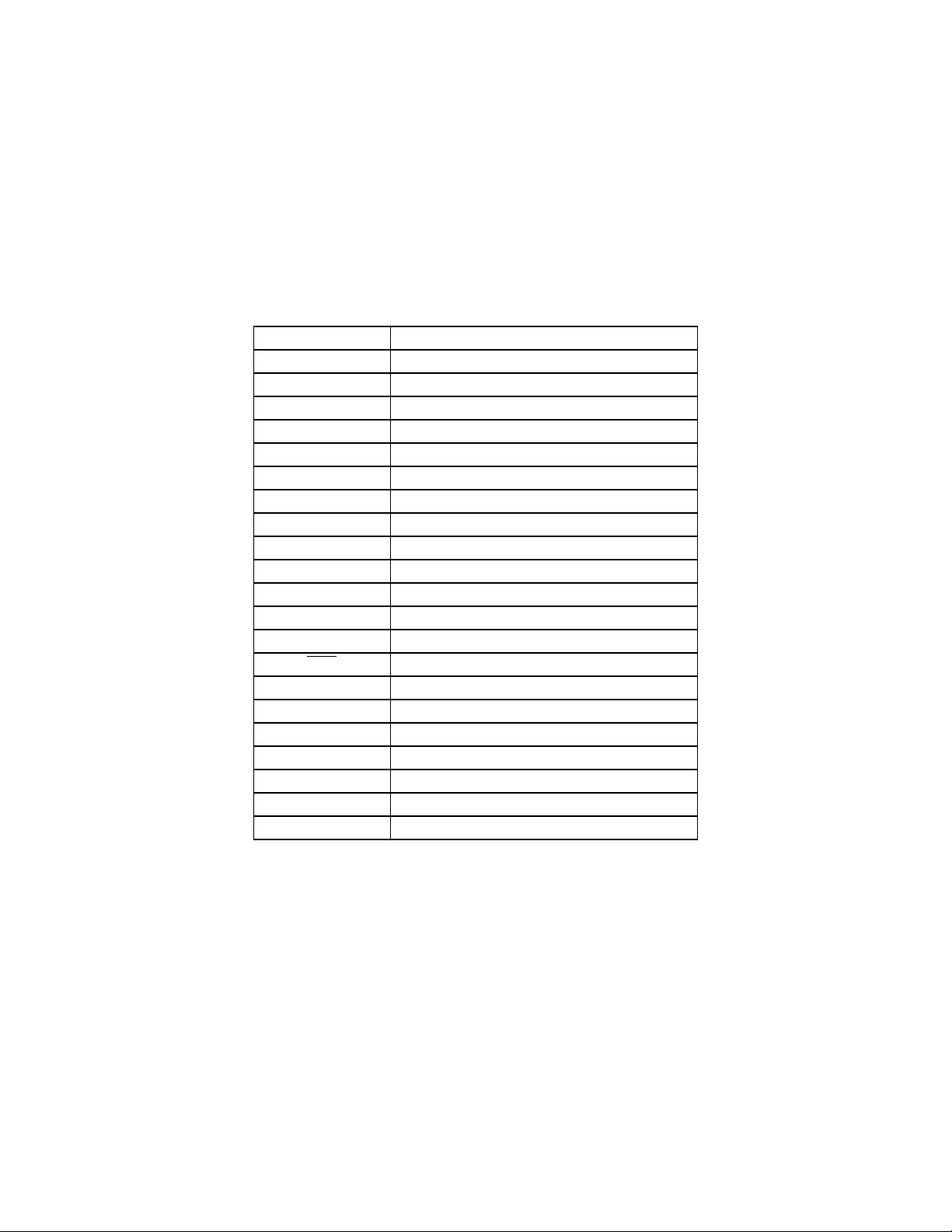

TABLE OF CONTENTS

Paragraph Title Page

SECTION 1

INTRODUCTION

SECTION 2

NOMENCLATURE

2.1 Symbols and Operators .............................................................................2-1

2.2 CPU16 Register Mnemonics .....................................................................2-2

2.3 Register Mnemonics ..................................................................................2-3

2.4 Conventions ..............................................................................................2-6

nc...

I

cale Semiconductor,

Frees

SECTION 3

OVERVIEW

3.1 M68HC16 Z-Series MCU Features ...........................................................3-1

3.1.1 Central Processor Unit (CPU16/CPU16L) .........................................3-1

3.1.2 System Integration Module (SIM/SIML) ............................................3-1

3.1.3 Standby RAM (SRAM) ......................................................................3-1

3.1.4 Masked ROM Module (MRM) — (MC68HC16Z2/Z3 Only) ...............3-2

3.1.5 Analog-to-Digital Converter (ADC) ....................................................3-2

3.1.6 Queued Serial Module (QSM) ...........................................................3-2

3.1.7 Multichannel Communication Interface (MCCI) —

(MC68HC16Z4/CKZ4 Only) ..............................................................3-2

3.1.8 General-Purpose Timer (GPT) ..........................................................3-2

3.2 Intermodule Bus ........................................................................................3-2

3.3 System Block Diagram and Pin Assignment Diagrams .............................3-2

3.4 Pin Descriptions ......................................................................................3-11

3.5 Signal Descriptions ..................................................................................3-13

3.6 Internal Register Map ..............................................................................3-16

3.7 Address Space Maps ..............................................................................3-19

SECTION 4

CENTRAL PROCESSOR UNIT

4.1 General ......................................................................................................4-1

4.2 Register Model ..........................................................................................4-1

4.2.1 Accumulators .....................................................................................4-3

4.2.2 Index Registers .................................................................................4-3

4.2.3 Stack Pointer .....................................................................................4-3

4.2.4 Program Counter ...............................................................................4-3

4.2.5 Condition Code Register ...................................................................4-4

4.2.6 Address Extension Register and Address Extension Fields .............4-5

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL i

For More Information On This Product,

Go to: www.freescale.com

Page 4

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

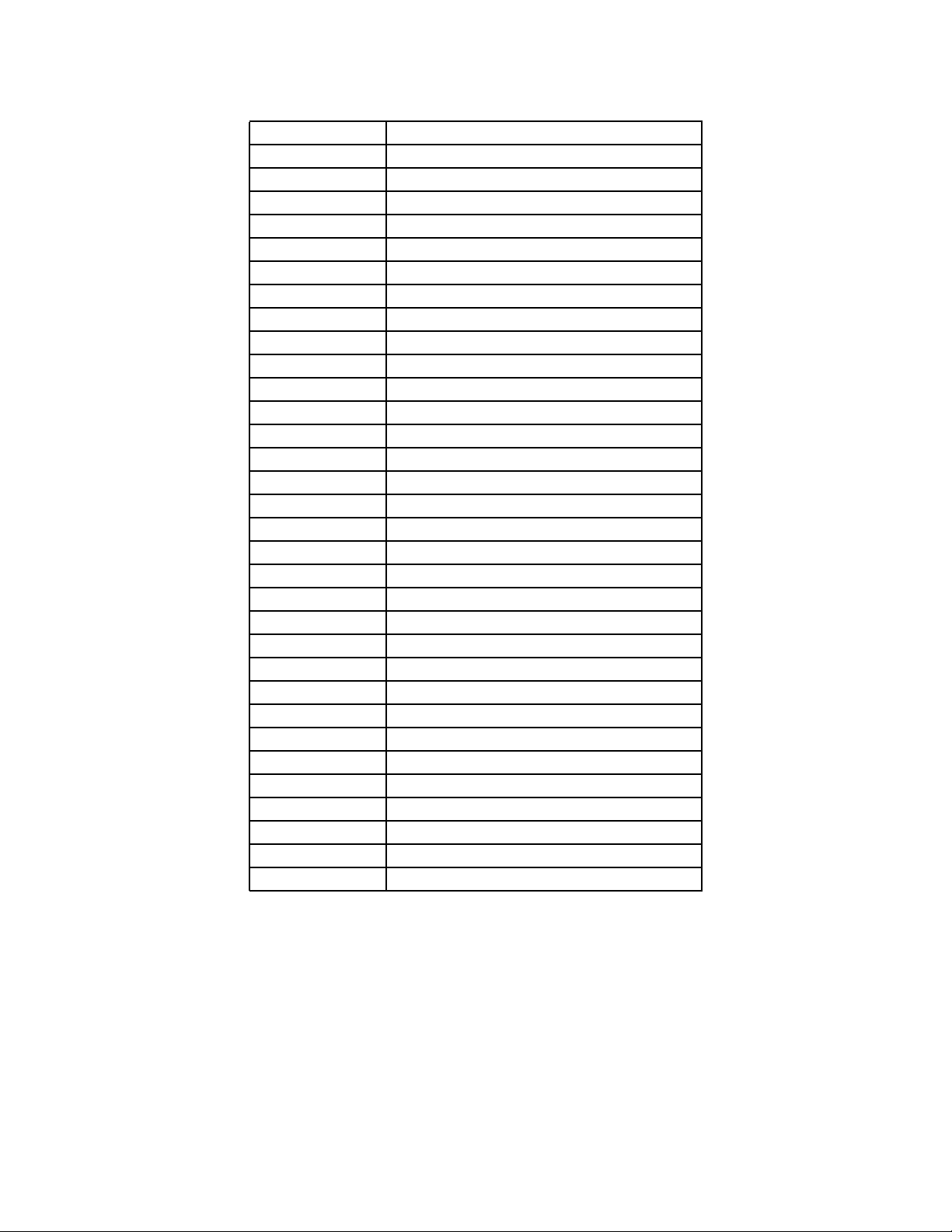

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

4.2.7 Multiply and Accumulate Registers ...................................................4-5

4.3 Memory Management ...............................................................................4-5

4.3.1 Address Extension ............................................................................4-6

4.3.2 Extension Fields ................................................................................4-6

4.4 Data Types ................................................................................................4-6

4.5 Memory Organization ................................................................................4-7

4.6 Addressing Modes .....................................................................................4-8

4.6.1 Immediate Addressing Modes ...........................................................4-9

4.6.2 Extended Addressing Modes ..........................................................4-10

4.6.3 Indexed Addressing Modes .............................................................4-10

4.6.4 Inherent Addressing Mode ..............................................................4-10

4.6.5 Accumulator Offset Addressing Mode .............................................4-10

4.6.6 Relative Addressing Modes .............................................................4-10

4.6.7 Post-Modified Index Addressing Mode ............................................4-10

4.6.8 Use of CPU16 Indexed Mode to Replace M68HC11 Direct Mode ..4-11

4.7 Instruction Set .........................................................................................4-11

4.7.1 Instruction Set Summary .................................................................4-11

4.8 Comparison of CPU16 and M68HC11 CPU Instruction Sets ..................4-31

4.9 Instruction Format ...................................................................................4-33

4.10 Execution Model ......................................................................................4-34

4.10.1 Microsequencer ...............................................................................4-35

4.10.2 Instruction Pipeline ..........................................................................4-35

4.10.3 Execution Unit .................................................................................4-35

4.11 Execution Process ...................................................................................4-36

4.11.1 Changes in Program Flow ...............................................................4-36

4.12 Instruction Timing ....................................................................................4-36

4.13 Exceptions ...............................................................................................4-37

4.13.1 Exception Vectors ...........................................................................4-37

4.13.2 Exception Stack Frame ...................................................................4-38

4.13.3 Exception Processing Sequence .....................................................4-39

4.13.4 Types of Exceptions ........................................................................4-39

4.13.4.1 Asynchronous Exceptions .......................................................4-39

4.13.4.2 Synchronous Exceptions .........................................................4-39

4.13.5 Multiple Exceptions .........................................................................4-40

4.13.6 RTI Instruction .................................................................................4-40

4.14 Development Support ..............................................................................4-40

4.14.1 Deterministic Opcode Tracking .......................................................4-40

4.14.1.1 IPIPE0/IPIPE1 Multiplexing .....................................................4-41

4.14.1.2 Combining Opcode Tracking with Other Capabilities ..............4-41

4.14.2 Breakpoints .....................................................................................4-41

4.14.3 Opcode Tracking and Breakpoints ..................................................4-42

MOTOROLA M68HC16 Z SERIES

ii USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 5

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

4.14.4 Background Debug Mode ................................................................4-42

4.14.4.1 Enabling BDM .........................................................................4-42

4.14.4.2 BDM Sources ..........................................................................4-42

4.14.4.3 Entering BDM ..........................................................................4-42

4.14.4.4 BDM Commands .....................................................................4-43

4.14.4.5 Returning from BDM ...............................................................4-43

4.14.4.6 BDM Serial Interface ...............................................................4-44

4.15 Recommended BDM Connection ............................................................4-45

4.16 Digital Signal Processing .........................................................................4-45

SECTION 5

SYSTEM INTEGRATION MODULE

5.1 General ......................................................................................................5-1

5.2 System Configuration ................................................................................5-2

5.2.1 Module Mapping ................................................................................5-2

5.2.2 Interrupt Arbitration ............................................................................5-3

5.2.3 Show Internal Cycles .........................................................................5-3

5.2.4 Register Access ................................................................................5-3

5.2.5 Freeze Operation ..............................................................................5-3

5.3 System Clock ............................................................................................5-4

5.3.1 Clock Sources ...................................................................................5-5

5.3.2 Clock Synthesizer Operation .............................................................5-6

5.3.3 External Bus Clock ..........................................................................5-21

5.3.4 Low-Power Operation ......................................................................5-21

5.4 System Protection ...................................................................................5-24

5.4.1 Reset Status ....................................................................................5-24

5.4.2 Bus Monitor .....................................................................................5-24

5.4.3 Halt Monitor .....................................................................................5-25

5.4.4 Spurious Interrupt Monitor ...............................................................5-25

5.4.5 Software Watchdog .........................................................................5-25

5.4.6 Periodic Interrupt Timer ...................................................................5-27

5.4.7 Interrupt Priority and Vectoring ........................................................5-28

5.4.8 Low-Power STOP Operation ...........................................................5-29

5.5 External Bus Interface .............................................................................5-29

5.5.1 Bus Control Signals .........................................................................5-31

5.5.1.1 Address Bus ............................................................................5-31

5.5.1.2 Address Strobe .......................................................................5-31

5.5.1.3 Data Bus .................................................................................5-31

5.5.1.4 Data Strobe .............................................................................5-31

5.5.1.5 Read/Write Signal ...................................................................5-32

5.5.1.6 Size Signals ............................................................................5-32

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL iii

For More Information On This Product,

Go to: www.freescale.com

Page 6

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

5.5.1.7 Function Codes .......................................................................5-32

5.5.1.8 Data Size Acknowledge Signals .............................................5-32

5.5.1.9 Bus Error Signal ......................................................................5-33

5.5.1.10 Halt Signal ...............................................................................5-33

5.5.1.11 Autovector Signal ....................................................................5-33

5.5.2 Dynamic Bus Sizing ........................................................................5-33

5.5.3 Operand Alignment .........................................................................5-35

5.5.4 Misaligned Operands ......................................................................5-35

5.5.5 Operand Transfer Cases .................................................................5-35

5.6 Bus Operation .........................................................................................5-36

5.6.1 Synchronization to CLKOUT ...........................................................5-36

5.6.2 Regular Bus Cycle ...........................................................................5-37

5.6.2.1 Read Cycle ..............................................................................5-37

5.6.2.2 Write Cycle ..............................................................................5-38

5.6.3 Fast Termination Cycles ..................................................................5-39

5.6.4 CPU Space Cycles ..........................................................................5-40

5.6.4.1 Breakpoint Acknowledge Cycle ...............................................5-41

5.6.4.2 LPSTOP Broadcast Cycle .......................................................5-42

5.6.5 Bus Exception Control Cycles .........................................................5-43

5.6.5.1 Bus Errors ...............................................................................5-44

5.6.5.2 Double Bus Faults ...................................................................5-45

5.6.5.3 Halt Operation .........................................................................5-45

5.6.6 External Bus Arbitration ...................................................................5-46

5.6.6.1 Show Cycles ...........................................................................5-47

5.7 Reset .......................................................................................................5-48

5.7.1 Reset Exception Processing ...........................................................5-48

5.7.2 Reset Control Logic .........................................................................5-48

5.7.3 Reset Mode Selection .....................................................................5-49

5.7.3.1 Data Bus Mode Selection ........................................................5-50

5.7.3.2 Clock Mode Selection .............................................................5-52

5.7.3.3 Breakpoint Mode Selection .....................................................5-52

5.7.4 MCU Module Pin Function During Reset ........................................5-52

5.7.5 Pin State During Reset ....................................................................5-53

5.7.5.1 Reset States of SIM Pins ........................................................5-54

5.7.5.2 Reset States of Pins Assigned to Other MCU Modules ..........5-54

5.7.6 Reset Timing ...................................................................................5-55

5.7.7 Power-On Reset ..............................................................................5-55

5.7.8 Use of the Three-State Control Pin .................................................5-56

5.7.9 Reset Processing Summary ............................................................5-57

5.7.10 Reset Status Register .....................................................................5-57

5.8 Interrupts .................................................................................................5-58

MOTOROLA M68HC16 Z SERIES

iv USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 7

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

5.8.1 Interrupt Exception Processing .......................................................5-58

5.8.2 Interrupt Priority and Recognition ....................................................5-58

5.8.3 Interrupt Acknowledge and Arbitration ............................................5-59

5.8.4 Interrupt Processing Summary ........................................................5-60

5.8.5 Interrupt Acknowledge Bus Cycles ..................................................5-61

5.9 Chip-Selects ............................................................................................5-61

5.9.1 Chip-Select Registers ......................................................................5-63

5.9.1.1 Chip-Select Pin Assignment Registers ...................................5-64

5.9.1.2 Chip-Select Base Address Registers ......................................5-65

5.9.1.3 Chip-Select Option Registers ..................................................5-66

5.9.1.4 PORTC Data Register .............................................................5-67

5.9.2 Chip-Select Operation .....................................................................5-67

5.9.3 Using Chip-Select Signals for Interrupt Acknowledge .....................5-68

5.9.4 Chip-Select Reset Operation ...........................................................5-69

5.10 Parallel Input/Output Ports ......................................................................5-70

5.10.1 Pin Assignment Registers ...............................................................5-70

5.10.2 Data Direction Registers .................................................................5-70

5.10.3 Data Registers .................................................................................5-71

5.11 Factory Test ............................................................................................5-71

SECTION 6

STANDBY RAM MODULE

6.1 SRAM Register Block ................................................................................6-1

6.2 SRAM Array Address Mapping .................................................................6-2

6.3 SRAM Array Address Space Type ............................................................6-2

6.4 Normal Access ..........................................................................................6-2

6.5 Standby and Low-Power Stop Operation ..................................................6-2

6.6 Reset .........................................................................................................6-3

SECTION 7

MASKED ROM MODULE

7.1 MRM Register Block ..................................................................................7-1

7.2 MRM Array Address Mapping ...................................................................7-1

7.3 MRM Array Address Space Type ..............................................................7-2

7.4 Normal Access ..........................................................................................7-2

7.5 Low-Power Stop Mode Operation .............................................................7-3

7.6 ROM Signature ..........................................................................................7-3

7.7 Reset .........................................................................................................7-3

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL v

For More Information On This Product,

Go to: www.freescale.com

Page 8

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

SECTION 8

ANALOG-TO-DIGITAL CONVERTER

8.1 General ......................................................................................................8-1

8.2 External Connections ................................................................................8-1

8.2.1 Analog Input Pins ..............................................................................8-2

8.2.2 Analog Reference Pins ......................................................................8-3

8.2.3 Analog Supply Pins ...........................................................................8-3

8.3 Programmer’s Model .................................................................................8-3

8.4 ADC Bus Interface Unit .............................................................................8-3

8.5 Special Operating Modes ..........................................................................8-3

8.5.1 Low-Power Stop Mode ......................................................................8-3

8.5.2 Freeze Mode .....................................................................................8-4

8.6 Analog Subsystem ....................................................................................8-4

8.6.1 Multiplexer .........................................................................................8-4

8.6.2 Sample Capacitor and Buffer Amplifier .............................................8-5

8.6.3 RC DAC Array ...................................................................................8-5

8.6.4 Comparator .......................................................................................8-6

8.7 Digital Control Subsystem .........................................................................8-6

8.7.1 Control/Status Registers ...................................................................8-6

8.7.2 Clock and Prescaler Control ..............................................................8-6

8.7.3 Sample Time .....................................................................................8-7

8.7.4 Resolution .........................................................................................8-7

8.7.5 Conversion Control Logic ..................................................................8-7

8.7.5.1 Conversion Parameters ............................................................8-8

8.7.5.2 Conversion Modes ....................................................................8-8

8.7.6 Conversion Timing ..........................................................................8-12

8.7.7 Successive Approximation Register ................................................8-13

8.7.8 Result Registers ..............................................................................8-13

8.8 Pin Considerations ..................................................................................8-14

8.8.1 Analog Reference Pins ....................................................................8-14

8.8.2 Analog Power Pins ..........................................................................8-14

8.8.3 Analog Supply Filtering and Grounding ...........................................8-16

8.8.4 Accommodating Positive/Negative Stress Conditions .....................8-18

8.8.5 Analog Input Considerations ...........................................................8-19

8.8.6 Analog Input Pins ............................................................................8-21

8.8.6.1 Settling Time for the External Circuit .......................................8-22

8.8.6.2 Error Resulting from Leakage .................................................8-23

MOTOROLA M68HC16 Z SERIES

vi USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 9

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

SECTION 9

QUEUED SERIAL MODULE

9.1 General ......................................................................................................9-1

9.2 QSM Registers and Address Map .............................................................9-2

9.2.1 QSM Global Registers .......................................................................9-2

9.2.1.1 Low-Power Stop Mode Operation .............................................9-2

9.2.1.2 Freeze Operation ......................................................................9-3

9.2.1.3 QSM Interrupts ..........................................................................9-3

9.2.2 QSM Pin Control Registers ...............................................................9-4

9.3 Queued Serial Peripheral Interface ...........................................................9-5

9.3.1 QSPI Registers ..................................................................................9-6

9.3.1.1 Control Registers ......................................................................9-6

9.3.1.2 Status Register ..........................................................................9-7

9.3.2 QSPI RAM .........................................................................................9-7

9.3.2.1 Receive RAM ............................................................................9-7

9.3.2.2 Transmit RAM ...........................................................................9-7

9.3.2.3 Command RAM .........................................................................9-8

9.3.3 QSPI Pins ..........................................................................................9-8

9.3.4 QSPI Operation .................................................................................9-8

9.3.5 QSPI Operating Modes .....................................................................9-9

9.3.5.1 Master Mode ...........................................................................9-16

9.3.5.2 Master Wrap-Around Mode .....................................................9-19

9.3.5.3 Slave Mode .............................................................................9-20

9.3.5.4 Slave Wrap-Around Mode .......................................................9-21

9.3.6 Peripheral Chip Selects ...................................................................9-21

9.4 Serial Communication Interface ..............................................................9-21

9.4.1 SCI Registers ..................................................................................9-24

9.4.1.1 Control Registers ....................................................................9-24

9.4.1.2 Status Register ........................................................................9-24

9.4.1.3 Data Register ..........................................................................9-24

9.4.2 SCI Pins ..........................................................................................9-25

9.4.3 SCI Operation ..................................................................................9-25

9.4.3.1 Definition of Terms ..................................................................9-25

9.4.3.2 Serial Formats .........................................................................9-25

9.4.3.3 Baud Clock ..............................................................................9-26

9.4.3.4 Parity Checking .......................................................................9-26

9.4.3.5 Transmitter Operation .............................................................9-27

9.4.3.6 Receiver Operation .................................................................9-28

9.4.3.7 Idle-Line Detection ..................................................................9-29

9.4.3.8 Receiver Wake-Up ..................................................................9-29

9.4.3.9 Internal Loop Mode .................................................................9-30

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL vii

For More Information On This Product,

Go to: www.freescale.com

Page 10

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

SECTION 10

MULTICHANNEL COMMUNICATION INTERFACE

10.1 General ....................................................................................................10-1

10.2 MCCI Registers and Address Map ..........................................................10-2

10.2.1 MCCI Global Registers ....................................................................10-2

10.2.1.1 Low-Power Stop Mode ............................................................10-2

10.2.1.2 Privilege Levels .......................................................................10-3

10.2.1.3 MCCI Interrupts .......................................................................10-3

10.2.2 Pin Control and General-Purpose I/O .............................................10-4

10.3 Serial Peripheral Interface (SPI) ..............................................................10-4

10.3.1 SPI Registers ..................................................................................10-6

10.3.1.1 SPI Control Register (SPCR) ..................................................10-6

10.3.1.2 SPI Status Register (SPSR) ....................................................10-6

10.3.1.3 SPI Data Register (SPDR) ......................................................10-6

10.3.2 SPI Pins ...........................................................................................10-6

10.3.3 SPI Operating Modes ......................................................................10-7

10.3.3.1 Master Mode ...........................................................................10-7

10.3.3.2 Slave Mode .............................................................................10-8

10.3.4 SPI Clock Phase and Polarity Controls ...........................................10-8

10.3.4.1 CPHA = 0 Transfer Format .....................................................10-9

10.3.4.2 CPHA = 1 Transfer Format ...................................................10-10

10.3.5 SPI Serial Clock Baud Rate ..........................................................10-11

10.3.6 Wired-OR Open-Drain Outputs .....................................................10-11

10.3.7 Transfer Size and Direction ...........................................................10-11

10.3.8 Write Collision ...............................................................................10-12

10.3.9 Mode Fault ....................................................................................10-12

10.4 Serial Communication Interface (SCI) ...................................................10-13

10.4.1 SCI Registers ................................................................................10-13

10.4.1.1 SCI Control Registers ...........................................................10-13

10.4.1.2 SCI Status Register ...............................................................10-16

10.4.1.3 SCI Data Register .................................................................10-16

10.4.2 SCI Pins ........................................................................................10-16

10.4.3 Receive Data Pins (RXDA, RXDB) ...............................................10-17

10.4.4 Transmit Data Pins (TXDA, TXDB) ...............................................10-17

10.4.5 SCI Operation ................................................................................10-17

10.4.5.1 Definition of Terms ................................................................10-17

10.4.5.2 Serial Formats .......................................................................10-18

10.4.5.3 Baud Clock ............................................................................10-18

10.4.5.4 Parity Checking .....................................................................10-19

10.4.5.5 Transmitter Operation ...........................................................10-19

10.4.5.6 Receiver Operation ...............................................................10-20

MOTOROLA M68HC16 Z SERIES

viii USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 11

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

10.4.5.7 Idle-Line Detection ................................................................10-21

10.4.5.8 Receiver Wake-Up ................................................................10-22

10.4.5.9 Internal Loop .........................................................................10-22

10.5 MCCI Initialization .................................................................................10-23

SECTION 11

GENERAL-PURPOSE TIMER

11.1 General ....................................................................................................11-1

11.2 GPT Registers and Address Map ............................................................11-2

11.3 Special Modes of Operation ....................................................................11-3

11.3.1 Low-Power Stop Mode ....................................................................11-3

11.3.2 Freeze Mode ...................................................................................11-3

11.3.3 Single-Step Mode ............................................................................11-4

11.3.4 Test Mode .......................................................................................11-4

11.4 Polled and Interrupt-Driven Operation .....................................................11-4

11.4.1 Polled Operation ..............................................................................11-4

11.4.2 GPT Interrupts .................................................................................11-5

11.5 Pin Descriptions ......................................................................................11-7

11.5.1 Input Capture Pins ...........................................................................11-7

11.5.2 Input Capture/Output Compare Pin .................................................11-7

11.5.3 Output Compare Pins ......................................................................11-7

11.5.4 Pulse Accumulator Input Pin ...........................................................11-7

11.5.5 Pulse-Width Modulation ..................................................................11-8

11.5.6 Auxiliary Timer Clock Input ..............................................................11-8

11.6 General-Purpose I/O ...............................................................................11-8

11.7 Prescaler .................................................................................................11-8

11.8 Capture/Compare Unit ..........................................................................11-10

11.8.1 Timer Counter ...............................................................................11-10

11.8.2 Input Capture Functions ................................................................11-10

11.8.3 Output Compare Functions ...........................................................11-13

11.8.3.1 Output Compare 1 .................................................................11-14

11.8.3.2 Forced Output Compare .......................................................11-14

11.9 Input Capture 4/Output Compare 5 .......................................................11-14

11.10 Pulse Accumulator ................................................................................11-14

11.11 Pulse-Width Modulation Unit .................................................................11-16

11.11.1 PWM Counter ................................................................................11-18

11.11.2 PWM Function ...............................................................................11-18

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL ix

For More Information On This Product,

Go to: www.freescale.com

Page 12

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

APPENDIX A

ELECTRICAL CHARACTERISTICS

APPENDIX B

MECHANICAL DATA AND ORDERING INFORMATION

B.1 Obtaining Updated M68HC16 Z-Series MCU Mechanical Information .... B-8

B.2 Ordering Information ................................................................................ B-8

APPENDIX C

DEVELOPMENT SUPPORT

nc...

I

cale Semiconductor,

Frees

C.1 M68MMDS1632 Modular Development System ...................................... C-1

C.2 M68MEVB1632 Modular Evaluation Board ..............................................C-2

APPENDIX D

REGISTER SUMMARY

D.1 Central Processing Unit ............................................................................D-1

D.1.1 Condition Code Register ..................................................................D-3

D.2 System Integration Module .......................................................................D-4

D.2.1 SIM Module Configuration Register ................................................. D-6

D.2.2 System Integration Test Register .....................................................D-7

D.2.3 Clock Synthesizer Control Register .................................................. D-7

D.2.4 Reset Status Register ...................................................................... D-8

D.2.5 System Integration Test Register E .................................................. D-9

D.2.6 Port E Data Register ........................................................................ D-9

D.2.7 Port E Data Direction Register .........................................................D-9

D.2.8 Port E Pin Assignment Register .....................................................D-10

D.2.9 Port F Data Register ....................................................................... D-10

D.2.10 Port F Data Direction Register ....................................................... D-11

D.2.11 Port F Pin Assignment Register .....................................................D-11

D.2.12 System Protection Control Register ...............................................D-12

D.2.13 Periodic Interrupt Control Register .................................................D-13

D.2.14 Periodic Interrupt Timer Register ................................................... D-14

D.2.15 Software Watchdog Service Register ............................................. D-15

D.2.16 Port C Data Register ......................................................................D-15

D.2.17 Chip-Select Pin Assignment Registers ........................................... D-15

D.2.18 Chip-Select Base Address Register Boot ....................................... D-17

D.2.19 Chip-Select Base Address Registers .............................................D-17

D.2.20 Chip-Select Option Register Boot .................................................. D-18

D.2.21 Chip-Select Option Registers .........................................................D-18

MOTOROLA M68HC16 Z SERIES

x USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 13

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

D.2.22 Master Shift Registers ....................................................................D-22

D.2.23 Test Module Shift Count Register .................................................. D-22

D.2.24 Test Module Repetition Count Register ......................................... D-22

D.2.25 Test Module Control Register ......................................................... D-22

D.2.26 Test Module Distributed Register ...................................................D-22

D.3 Standby RAM Module ............................................................................D-23

D.3.1 RAM Module Configuration Register .............................................. D-23

D.3.2 RAM Test Register .........................................................................D-24

D.3.3 Array Base Address Register High ................................................. D-24

D.3.4 Array Base Address Register Low ................................................. D-24

D.4 Masked ROM Module .............................................................................D-25

D.4.1 Masked ROM Module Configuration Register ................................ D-25

D.4.2 ROM Array Base Address Registers .............................................. D-27

D.4.3 ROM Signature Registers High ......................................................D-27

D.4.4 ROM Bootstrap Words ...................................................................D-28

D.5 Analog-to-Digital Converter Module ....................................................... D-29

D.5.1 ADC Module Configuration Register ..............................................D-30

D.5.2 ADC Test Register ......................................................................... D-30

D.5.3 Port ADA Data Register ................................................................. D-30

D.5.4 ADC Control Register 0 .................................................................. D-31

D.5.5 ADC Control Register 1 .................................................................. D-32

D.5.6 ADC Status Register ......................................................................D-36

D.5.7 Right Justified, Unsigned Result Register ......................................D-36

D.6 Queued Serial Module ............................................................................D-38

D.6.1 QSM Configuration Register .......................................................... D-38

D.6.2 QSM Test Register ......................................................................... D-39

D.6.3 QSM Interrupt Level Register/Interrupt Vector Register ................. D-39

D.6.4 SCI Control Register ...................................................................... D-40

D.6.5 SCI Control Register 1 ................................................................... D-41

D.6.6 SCI Status Register ........................................................................ D-43

D.6.7 SCI Data Register .......................................................................... D-44

D.6.8 Port QS Data Register .................................................................... D-44

D.6.9 Port QS Pin Assignment Register/Data Direction Register ............D-45

D.6.10 QSPI Control Register 0 ................................................................. D-46

D.6.11 QSPI Control Register 1 ................................................................. D-48

D.6.12 QSPI Control Register 2 ................................................................. D-49

D.6.13 QSPI Control Register 3 ................................................................. D-50

D.6.14 Receive Data RAM ......................................................................... D-51

D.6.15 Transmit Data RAM ........................................................................ D-52

D.6.16 Command RAM .............................................................................. D-52

D.7 Multichannel Communication Interface Module ..................................... D-54

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL xi

For More Information On This Product,

Go to: www.freescale.com

Page 14

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

D.7.1 MCCI Module Configuration Register ............................................. D-54

D.7.2 MCCI Test Register ........................................................................ D-55

D.7.3 SCI Interrupt Level Register/MCCI Interrupt Vector Register ......... D-55

D.7.4 MCCI Interrupt Vector Register ......................................................D-56

D.7.5 SPI Interrupt Level Register ...........................................................D-56

D.7.6 MCCI Pin Assignment Register ...................................................... D-57

D.7.7 MCCI Data Direction Register ........................................................D-58

D.7.8 MCCI Port Data Registers .............................................................. D-59

D.7.9 SCI Control Register 0 ................................................................... D-59

D.7.11 SCI Status Register ........................................................................ D-62

D.7.12 SCI Data Register .......................................................................... D-63

D.7.13 SPI Control Register ....................................................................... D-64

D.7.14 SPI Status Register ........................................................................D-65

D.7.15 SPI Data Register ........................................................................... D-66

D.8 General-Purpose Timer ..........................................................................D-67

D.8.1 GPT Module Configuration Register .............................................. D-67

D.8.2 GPT Test Register .......................................................................... D-68

D.8.3 GPT Interrupt Configuration Register ............................................. D-68

D.8.4 Port GP Data Direction Register/Data Register ............................. D-69

D.8.5 OC1 Action Mask Register/Data Register ......................................D-69

D.8.6 Timer Counter Register ..................................................................D-70

D.8.7 Pulse Accumulator Control Register/Counter ................................. D-70

D.8.8 Input Capture Registers 1–3 .......................................................... D-71

D.8.9 Output Compare Registers 1–4 ...................................................... D-71

D.8.10 Input Capture 4/Output Compare 5 Register .................................. D-72

D.8.11 Timer Control Registers 1 and 2 .................................................... D-72

D.8.12 Timer Interrupt Mask Registers 1 and 2 .........................................D-72

D.8.13 Timer Interrupt Flag Registers 1 and 2 ........................................... D-74

D.8.14 Compare Force Register/PWM Control Register C ........................ D-74

D.8.15 PWM Registers A/B ........................................................................ D-76

D.8.16 PWM Count Register ...................................................................... D-76

D.8.17 PWM Buffer Registers A/B .............................................................D-76

D.8.18 GPT Prescaler ................................................................................ D-77

APPENDIX E

INITIALIZATION AND PROGRAMMING EXAMPLES

E.1 Initialization Programs .............................................................................. E-1

E.1.1 EQUATES.ASM ............................................................................... E-2

E.1.2 ORG00000.ASM .............................................................................. E-6

E.1.3 ORG00008.ASM .............................................................................. E-6

E.1.4 INITSYS.ASM ................................................................................. E-11

MOTOROLA M68HC16 Z SERIES

xii USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 15

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

E.1.5 INITRAM.ASM ................................................................................ E-11

E.1.6 INITSCI.ASM .................................................................................. E-12

E.2 Programming Examples ......................................................................... E-12

E.2.1 SIM Programming Examples .......................................................... E-13

E.2.1.1 Example 1 - Using Ports E and F ........................................... E-13

E.2.1.2 Example 2 - Using Chip-Selects ............................................ E-14

E.2.1.3 Example 3 - Changing Clock Frequencies ............................. E-16

E.2.1.4 Example 4 - Software Watchdog, Periodic Interrupt,

and Autovector Demo ............................................................ E-18

E.2.2 CPU16 Programming Example ...................................................... E-23

E.2.2.1 Example 5 - Indexed and Extended Addressing .................... E-23

nc...

I

E.2.3 QSM/SCI Programming Example ................................................... E-24

E.2.3.1 Example 6 - Using an SCI Port .............................................. E-24

E.2.4 GPT Programming Example .......................................................... E-25

E.2.4.1 Example 7 - Basic GPT Functions ......................................... E-25

cale Semiconductor,

Frees

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL xiii

For More Information On This Product,

Go to: www.freescale.com

Page 16

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

MOTOROLA M68HC16 Z SERIES

xiv USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 17

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

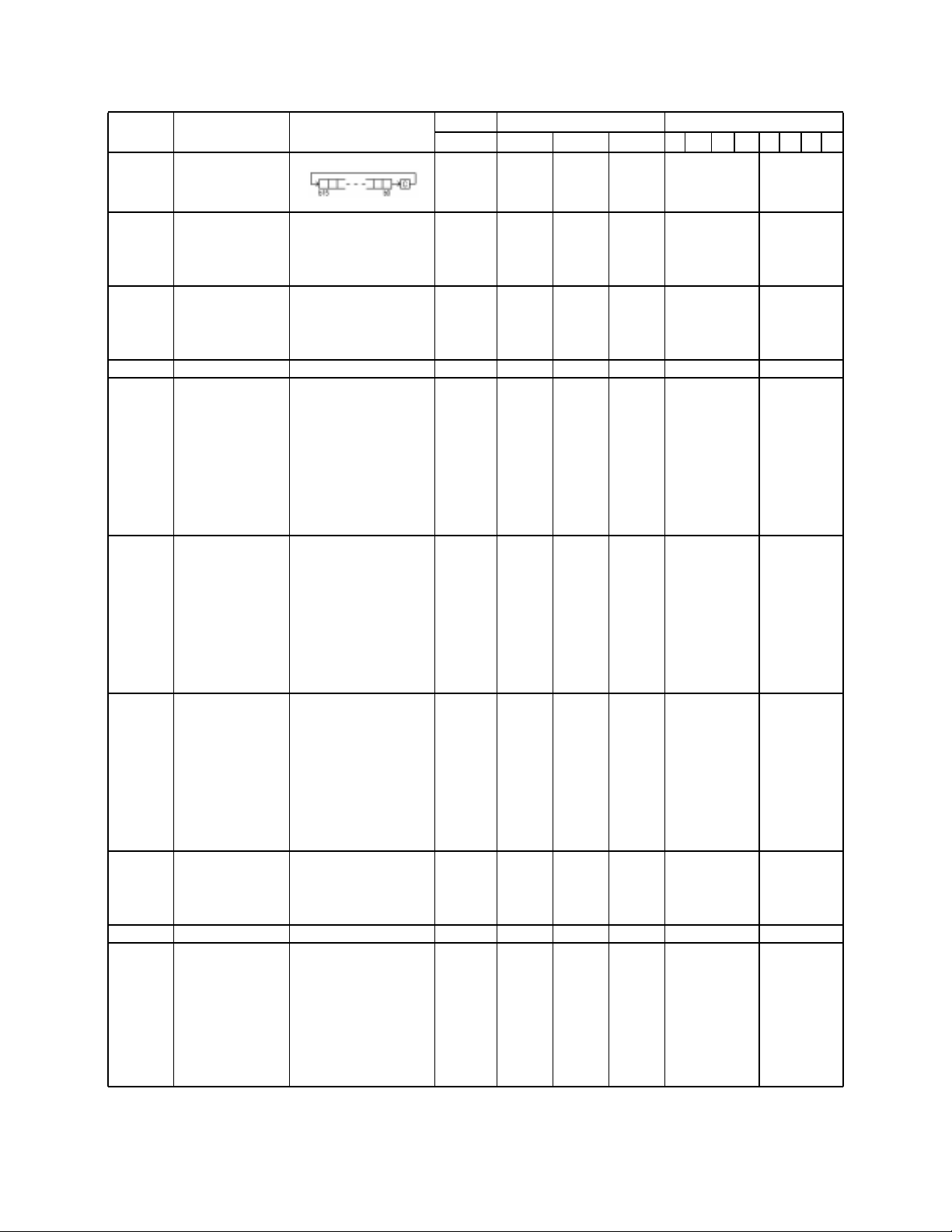

LIST OF ILLUSTRATIONS

Figure Title Page

3-1 MC68HC16Z1/CK16Z1/CM16Z1 Block Diagram ...........................................3-4

3-2 MC68HC16Z2/Z3 Block Diagram ...................................................................3-5

3-3 MC68HC16Z4/CK16Z4 Block Diagram ..........................................................3-6

3-4 MC68HC16Z1/CKZ1/CMZ1/Z2/Z3 Pin Assignments

for 132-Pin Package .......................................................................................3-7

3-5 MC68HC16Z1/CKZ1/CMZ1/Z2/Z3 Pin Assignments

for 144-Pin Package .......................................................................................3-8

3-6 MC68HC16Z4/CKZ4 Pin Assignments for 132-Pin Package .........................3-9

3-7 MC68HC16Z4/CKZ4 Pin Assignments for 144-Pin Package .......................3-10

3-8 MC68HC16Z1/CKZ1/CMZ1 Address Map ................................................... 3-17

3-9 MC68HC16Z2/Z3 Address Map ...................................................................3-18

3-10 MC68HC16Z4/CKZ4 Address Map ..............................................................3-18

3-11 MC68HC16Z1/CKZ1/CMZ1 Combined Program

and Data Space Map ....................................................................................3-20

3-12 MC68HC16Z2/Z3 Combined Program and Data Space Map ...................... 3-21

3-13 MC68HC16Z4/CKZ4 Combined Program and Data Space Map ................. 3-22

3-14 MC68HC16Z1/CKZ1/CMZ1 Separate Program

and Data Space Map ....................................................................................3-23

3-15 MC68HC16Z2/Z3 Separate Program and Data Space Map ........................3-24

3-16 MC68HC16Z4/CKZ4 Separate Program and Data Space Map ...................3-25

4-1 CPU16 Register Model ...................................................................................4-2

4-2 Condition Code Register ................................................................................ 4-4

4-3 Data Types and Memory Organization ...........................................................4-8

4-4 Basic Instruction Formats .............................................................................4-34

4-5 Instruction Execution Model ......................................................................... 4-35

4-6 Exception Stack Frame Format ....................................................................4-38

4-7 BDM Serial I/O Block Diagram .....................................................................4-44

4-8 BDM Connector Pinout .................................................................................4-45

5-1 System Integration Module Block Diagram .................................................... 5-2

5-2 System Clock Block Diagram .........................................................................5-4

5-3 Slow Reference Crystal Circuit .......................................................................5-5

5-4 Fast Reference Crystal Circuit .......................................................................5-5

5-5 System Clock Filter Networks ........................................................................5-7

5-6 SIM LPSTOP Flowchart ............................................................................... 5-22

5-7 SIML LPSTOP Flowchart ............................................................................. 5-23

5-8 System Protection ........................................................................................ 5-24

5-9 Periodic Interrupt Timer and Software Watchdog Timer .............................. 5-27

5-10 MCU Basic System ......................................................................................5-30

5-11 Operand Byte Order .....................................................................................5-34

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL xv

For More Information On This Product,

Go to: www.freescale.com

Page 18

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

LIST OF ILLUSTRATIONS

(Continued)

Figure Title Page

5-12 Word Read Cycle Flowchart .........................................................................5-38

5-13 Write Cycle Flowchart ..................................................................................5-39

5-14 CPU Space Address Encoding ....................................................................5-41

5-15 Breakpoint Operation Flowchart ...................................................................5-42

5-16 LPSTOP Interrupt Mask Level ......................................................................5-43

5-17 Bus Arbitration Flowchart for Single Request ...............................................5-47

5-18 Preferred Circuit for Data Bus Mode Select Conditioning ............................ 5-50

5-19 Alternate Circuit for Data Bus Mode Select Conditioning .............................5-51

5-20 Power-On Reset ...........................................................................................5-56

5-21 Basic MCU System ......................................................................................5-62

5-22 Chip-Select Circuit Block Diagram ............................................................... 5-63

5-23 CPU Space Encoding for Interrupt Acknowledge .........................................5-68

8-1 ADC Block Diagram .......................................................................................8-2

8-2 8-Bit Conversion Timing ...............................................................................8-12

8-3 10-Bit Conversion Timing .............................................................................8-13

8-4 Analog Input Circuitry ...................................................................................8-15

8-5 Errors Resulting from Clipping .....................................................................8-16

8-6 Star-Ground at the Point of Power Supply Origin .........................................8-17

8-7 Input Pin Subjected to Negative Stress ........................................................8-18

8-8 Voltage Limiting Diodes in a Negative Stress Circuit ................................... 8-19

8-9 External Multiplexing of Analog Signal Sources ...........................................8-20

8-10 Electrical Model of an A/D Input Pin .............................................................8-21

9-1 QSM Block Diagram .......................................................................................9-1

9-2 QSPI Block Diagram ......................................................................................9-5

9-3 QSPI RAM ......................................................................................................9-7

9-4 Flowchart of QSPI Initialization Operation ....................................................9-10

9-5 Flowchart of QSPI Master Operation (Part 1) ..............................................9-11

9-6 Flowchart of QSPI Master Operation (Part 2) ..............................................9-12

9-7 Flowchart of QSPI Master Operation (Part 3) ..............................................9-13

9-8 Flowchart of QSPI Slave Operation (Part 1) ................................................9-14

9-9 Flowchart of QSPI Slave Operation (Part 2) ................................................9-15

9-10 SCI Transmitter Block Diagram ....................................................................9-22

9-11 SCI Receiver Block Diagram ........................................................................9-23

10-1 MCCI Block Diagram ....................................................................................10-1

10-2 SPI Block Diagram ....................................................................................... 10-5

10-3 CPHA = 0 SPI Transfer Format .................................................................... 10-9

10-4 CPHA = 1 SPI Transfer Format .................................................................. 10-10

10-5 SCI Transmitter Block Diagram ..................................................................10-14

MOTOROLA M68HC16 Z SERIES

xvi USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 19

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

LIST OF ILLUSTRATIONS

(Continued)

Figure Title Page

10-6 SCI Receiver Block Diagram ......................................................................10-15

11-1 GPT Block Diagram ......................................................................................11-2

11-2 Prescaler Block Diagram ..............................................................................11-9

11-3 Capture/Compare Unit Block Diagram .......................................................11-11

11-4 Input Capture Timing Example ...................................................................11-13

11-5 Pulse Accumulator Block Diagram .............................................................11-15

11-6 PWM Block Diagram .................................................................................. 11-17

A-1 CLKOUT Output Timing Diagram .................................................................A-28

A-2 External Clock Input Timing Diagram ...........................................................A-28

A-3 ECLK Output Timing Diagram ......................................................................A-28

A-4 Read Cycle Timing Diagram ........................................................................A-29

A-5 Write Cycle Timing Diagram .........................................................................A-30

A-6 Fast Termination Read Cycle Timing Diagram ............................................A-31

A-7 Fast Termination Write Cycle Timing Diagram .............................................A-32

A-8 Bus Arbitration Timing Diagram — Active Bus Case ...................................A-33

A-9 Bus Arbitration Timing Diagram — Idle Bus Case .......................................A-34

A-10 Show Cycle Timing Diagram ........................................................................A-35

A-11 Chip-Select Timing Diagram ........................................................................A-36

A-12 Reset and Mode Select Timing Diagram ......................................................A-36

A-13 Background Debug Mode Timing Diagram (Serial Communication) ............A-39

A-14 Background Debug Mode Timing Diagram (Freeze Assertion) ....................A-39

A-15 ECLK Timing Diagram ..................................................................................A-44

A-16 QSPI Timing — Master, CPHA = 0 ..............................................................A-47

A-17 QSPI Timing — Master, CPHA = 1 ..............................................................A-47

A-18 QSPI Timing — Slave, CPHA = 0 ................................................................A-48

A-19 QSPI Timing — Slave, CPHA = 1 ................................................................A-48

A-20 SPI Timing — Master, CPHA = 0 .................................................................A-51

A-21 SPI Timing — Master, CPHA = 1 .................................................................A-51

A-22 SPI Timing — Slave, CPHA = 0 ...................................................................A-52

A-23 SPI Timing — Slave, CPHA = 1 ...................................................................A-52

A-24 Input Signal Conditioner Timing ...................................................................A-53

A-25 Pulse Accumulator — Event Counting Mode (Leading Edge) ......................A-54

A-26 Pulse Accumulator — Gated Mode (Count While Pin High) ........................A-55

A-27 Pulse Accumulator — Using TOF as Gated Mode Clock .............................A-56

A-28 PWMx (PWMx Register = 01, Fast Mode) ...................................................A-56

A-29 Output Compare (Toggle Pin State) .............................................................A-57

A-30 Input Capture (Capture on Rising Edge) ......................................................A-58

A-31 General-Purpose Input .................................................................................A-59

A-32 General-Purpose Output (Causes Input Capture) ........................................A-60

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL xvii

For More Information On This Product,

Go to: www.freescale.com

Page 20

Freescale Semiconductor, Inc.

LIST OF ILLUSTRATIONS

(Continued)

Figure Title Page

A-33 Force Compare (CLEAR) .............................................................................A-61

A-34 Low Voltage 8-Bit ADC Conversion Accuracy ..............................................A-68

A-35 8-Bit ADC Conversion Accuracy ..................................................................A-69

A-36 Low Voltage 10-Bit ADC Conversion Accuracy ............................................A-70

A-37 10-Bit ADC Conversion Accuracy ................................................................A-71

B-1 MC68HC16Z1/CKZ1/CMZ1/Z2/Z3 Pin Assignments

for 132-Pin Package .......................................................................................B-2

B-2 MC68HC16Z4/CKZ4 Pin Assignments for 132-Pin Package .........................B-3

B-3 Case 831A-01 — 132-Pin Package Dimensions ............................................B-4

B-4 MC68HC16Z1/CKZ1/CMZ1/Z2/Z3 Pin Assignments

nc...

I

B-5 MC68HC16Z4/CKZ4 Pin Assignments for 144-Pin Package .........................B-6

B-6 Case 918 — 144-Pin Package Dimensions ...................................................B-7

for 144-Pin Package .......................................................................................B-5

cale Semiconductor,

Frees

D-1 CPU16 Register Model ...................................................................................D-2

MOTOROLA M68HC16 Z SERIES

xviii USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 21

Freescale Semiconductor, Inc.

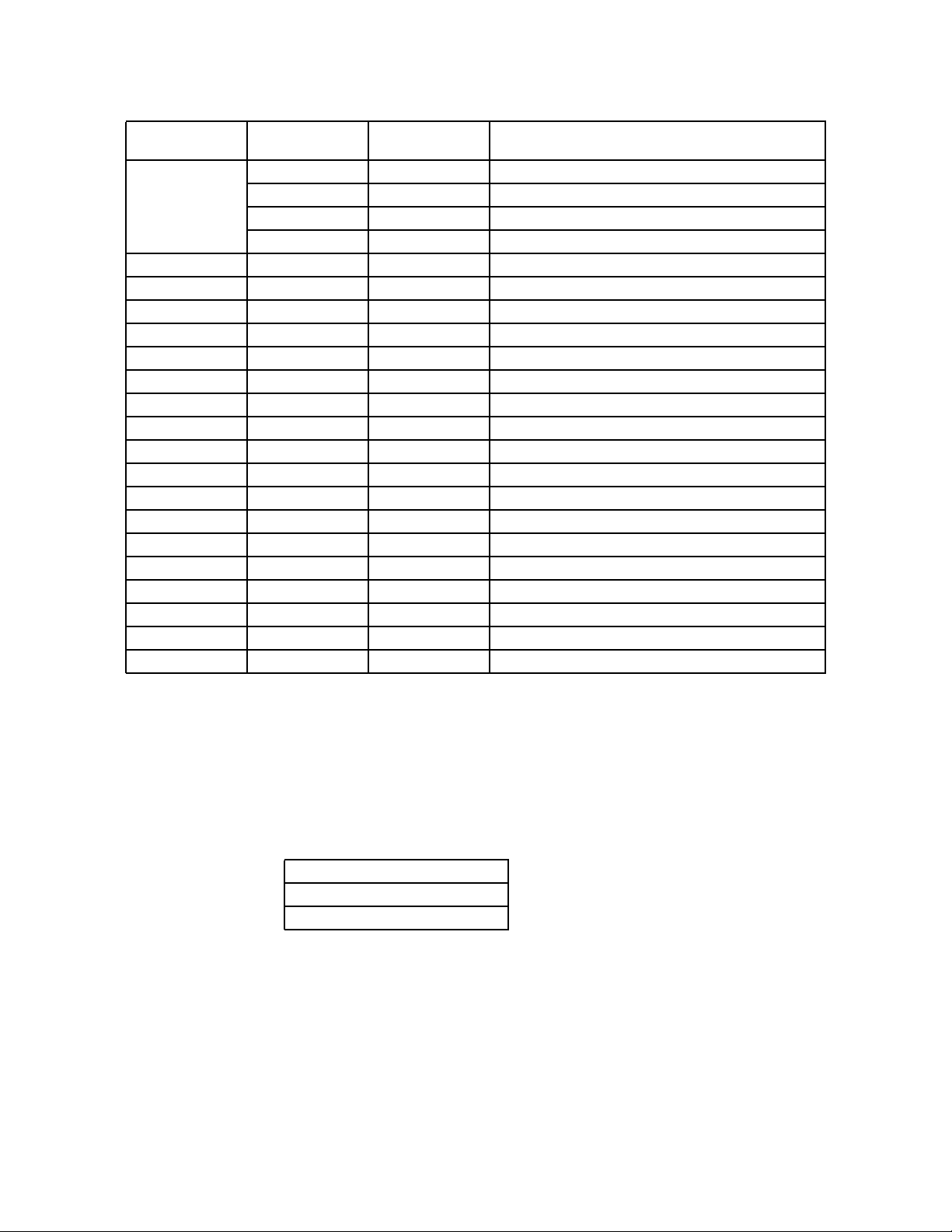

LIST OF TABLES

Table Title Page

1-1 M68HC16 Z-Series MCUs...............................................................................1-1

1-2 Z-Series MCU Reference Frequencies...........................................................1-2

3-1 M68HC16 Z-Series Pin Characteristics.........................................................3-11

3-2 M68HC16 Z-Series Driver Types..................................................................3-12

3-3 M68HC16 Z-Series Power Connections....................................................... 3-13

3-4 M68HC16 Z-Series Signal Characteristics.................................................... 3-13

3-5 M68HC16 Z-Series Signal Function.............................................................. 3-15

4-1 Addressing Modes...........................................................................................4-9

4-2 Instruction Set Summary...............................................................................4-12

nc...

I

4-3 Instruction Set Abbreviations and Symbols................................................... 4-30

4-4 CPU16 Implementation of M68HC11 CPU Instructions................................4-32

4-5 Exception Vector Table.................................................................................4-38

4-6 IPIPE0/IPIPE1 Encoding...............................................................................4-41

4-7 Command Summary.....................................................................................4-43

cale Semiconductor,

Frees

5-1 Show Cycle Enable Bits..................................................................................5-3

5-2 16.78-MHz Clock Control Multipliers...............................................................5-9

5-3 20.97-MHz Clock Control Multipliers.............................................................5-11

5-4 25.17-MHz Clock Control Multipliers.............................................................5-13

5-5 16.78-MHz System Clock Frequencies.........................................................5-15

5-6 System Clock Frequencies for a 20.97-MHz System.................................... 5-17

5-7 System Clock Frequencies for a 25.17-MHz System.................................... 5-19

5-8 Bus Monitor Period........................................................................................ 5-25

5-9 MODCLK Pin and SWP Bit During Reset..................................................... 5-26

5-10 Software Watchdog Divide Ratio...................................................................5-27

5-11 MODCLK Pin and PTP Bit at Reset..............................................................5-28

5-12 Periodic Interrupt Priority............................................................................... 5-29

5-13 Size Signal Encoding....................................................................................5-32

5-14 Address Space Encoding..............................................................................5-32

5-15 Effect of

5-16 Operand Alignment.......................................................................................5-36

5-17

5-18 Reset Source Summary................................................................................5-49

5-19 Reset Mode Selection...................................................................................5-49

5-20 Module Pin Functions.................................................................................... 5-53

5-21 SIM Pin Reset States....................................................................................5-54

5-22 Chip-Select Pin Functions.............................................................................5-64

5-23 Pin Assignment Field Encoding.....................................................................5-64

5-24 Block Size Encoding......................................................................................5-65

DSACK, BERR, and HALT Assertion Results ...............................................5-44

DSACK Signals...............................................................................5-34

M68HC16 Z SERIES MOTOROLA

USER’S MANUAL xix

For More Information On This Product,

Go to: www.freescale.com

Page 22

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

LIST OF TABLES

(Continued)

Table Title Page

5-25 Chip-Select Base and Option Register Reset Values...................................5-69

5-26

6-1 SRAM Configuration........................................................................................6-1

6-2 SRAM Array Address Space Type..................................................................6-2

7-1 ROM Array Space Field..................................................................................7-2

7-2 Wait States Field.............................................................................................7-3

8-1 FRZ Field Selection......................................................................................... 8-4

8-2 Multiplexer Channel Sources..........................................................................8-5

8-3 Prescaler Output.............................................................................................8-7

8-4 TS Field Selection...........................................................................................8-7

8-5 Conversion Parameters Controlled by ADCTL1..............................................8-8

8-6 ADC Conversion Modes.................................................................................. 8-8

8-7 Single-Channel Conversions (MULT = 0)......................................................8-10

8-8 Multiple-Channel Conversions (MULT = 1)................................................... 8-11

8-9 Result Register Formats................................................................................8-14

8-10 External Circuit Settling Time (10-Bit Conversions)......................................8-23

8-11 Error Resulting From Input Leakage (IOFF)..................................................8-23

9-1 Effect of DDRQS on QSM Pin Function..........................................................9-4

9-2 QSPI Pins........................................................................................................ 9-8

9-3 Bits Per Transfer...........................................................................................9-18

9-4 Serial Frame Formats....................................................................................9-26

9-5 Effect of Parity Checking on Data Size.........................................................9-27

10-1 MCCI Interrupt Vectors..................................................................................10-3

10-2 Pin Assignments............................................................................................10-4

10-3 SPI Pin Functions.......................................................................................... 10-7

10-4 SCK Frequencies........................................................................................10-11

10-5 SCI Pins......................................................................................................10-17

10-6 Serial Frame Formats..................................................................................10-18

10-7 Effect of Parity Checking on Data Size.......................................................10-19

CSBOOT Base and Option Register Reset Values....................................... 5-70

11-1 GPT Status Flags..........................................................................................11-5

11-2 GPT Interrupt Sources..................................................................................11-6

11-3 PWM Frequency Ranges............................................................................11-18

A-1 Maximum Ratings............................................................................................A-1

A-2 Typical Ratings, 2.7 to 3.6V, 16.78-MHz Operation........................................A-2

MOTOROLA M68HC16 Z SERIES

xx USER’S MANUAL

For More Information On This Product,

Go to: www.freescale.com

Page 23

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

LIST OF TABLES

(Continued)

Table Title Page

A-3 Typical Ratings, 5V, 16.78-MHz Operation.....................................................A-3

A-4 Typical Ratings, 20.97-MHz Operation ...........................................................A-3

A-5 Typical Ratings, 25.17-MHz ............................................................................A-4

A-6 Thermal Characteristics ..................................................................................A-5

A-7 Low Voltage Clock Control Timing ..................................................................A-6

A-8 16.78-MHz Clock Control Timing ....................................................................A-7

A-9 20.97-MHz Clock Control Timing ....................................................................A-8

A-10 25.17-MHz Clock Control Timing ....................................................................A-9

A-11 Low Voltage 16.78-MHz DC Characteristics.................................................A-10

A-12 16.78-MHz DC Characteristics......................................................................A-12

A-13 20.97-MHz DC Characteristics......................................................................A-14