Page 1

M68060 User’s Manual

Including the

MC68060,

MC68LC060,

and

MC68EC060

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different

applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not

convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems

intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola

product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or

unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims,

costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are

registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© MOTOROLA, 1994

µ

Page 2

68K FAX-IT

Documentation Comments

FAX 512-891-8593—Documentation Comments Only

The Motorola High-End Technical Publications Department provides a fax number for you

to submit any questions or comments about this document or how to order other documents.

We welcome your suggestions for improving our documentation. Please do not fax technical

questions.

Please provide the part number and revision number (located in upper right-hand corner of

the cover) and the title of the document. When referring to items in the manual, please reference by the page number, paragraph number, figure number, table number, and line number if needed.

When sending a fax, please provide your name, company, fax number, and phone number

including area code.

Applications and Technical Information

For questions or comments pertaining to technical information, questions, and applications,

please contact one of the following sales offices nearest you.

MOTOROLA

M68060 USER’S MANUAL

iii

Page 3

iv

—

Sales Offices —

Field Applications Engineering Available Through All Sales Offices

ALABAMA , Huntsville (205) 464-6800

UNITED STATES

ARIZONA , Tempe (602) 897-5056

CALIFORNIA , Agoura Hills (818) 706-1929

CALIFORNIA , Los Angeles (310) 417-8848

CALIFORNIA , Irvine (714) 753-7360

CALIFORNIA , Rosevllle (916) 922-7152

CALIFORNIA , San Diego (619) 541-2163

CALIFORNIA , Sunnyvale (408) 749-0510

COLORADO , Colorado Springs (719) 599-7497

COLORADO , Denver (303) 337-3434

CONNECTICUT , Wallingford (203) 949-4100

FLORIDA , Maitland (407) 628-2636

FLORIDA , Pompano Beach/

Fort Lauderdale (305) 486-9776

FLORIDA , Clearwater (813) 538-7750

GEORGlA , Atlanta (404) 729-7100

IDAHO , Boise (208) 323-9413

ILLINOIS , Chicago/Hoffman Estates (708) 490-9500

INDlANA , Fort Wayne (219) 436-5818

INDIANA , Indianapolis (317) 571-0400

INDIANA , Kokomo (317) 457-6634

IOWA , Cedar Rapids (319) 373-1328

KANSAS , Kansas City/Mission (913) 451-8555

MARYLAND , Columbia (410) 381-1570

MASSACHUSETTS , Marborough (508) 481-8100

MASSACHUSETTS , Woburn (617) 932-9700

MICHIGAN , Detroit (313) 347-6800

MINNESOTA , Minnetonka (612) 932-1500

MISSOURI , St. Louis (314) 275-7380

NEW JERSEY , Fairfield (201) 808-2400

NEW YORK , Fairport (716) 425-4000

NEW YORK , Hauppauge (516) 361-7000

NEW YORK , Poughkeepsie/Fishkill (914) 473-8102

NORTH CAROLINA , Raleigh (919) 870-4355

OHIO , Cleveland (216) 349-3100

OHIO , Columbus/Worthington (614) 431-8492

OHIO , Dayton (513) 495-6800

OKLAHOMA , Tulsa (800) 544-9496

OREGON , Portland (503) 641-3681

PENNSYLVANIA , Colmar (215) 997-1020

Philadelphia/Horsham (215) 957-4100

TENNESSEE , Knoxville (615) 690-5593

TEXAS , Austin (512) 873-2000

TEXAS , Houston (800) 343-2692

TEXAS , Plano (214) 516-5100

VIRGINIA , Richmond (804) 285-2100

WASHINGTON , Bellevue (206) 454-4160

Seattle Access (206) 622-9960

WISCONSIN , Milwaukee/Brookfield (414) 792-0122

BRITISH COLUMBIA , Vancouver (604) 293-7605

ONTARIO , Toronto (416) 497-8181

ONTARIO , Ottawa (613) 226-3491

QUEBEC , Montreal (514) 731-6881

AUSTRALIA , Melbourne (61-3)887-0711

AUSTRALIA , Sydney (61(2)906-3855

BRAZIL , Sao Paulo 55(11)815-4200

CHINA , Beijing 86 505-2180

FINLAND , Helsinki 358-0-35161191

Car Phone 358(49)211501

FRANCE , Paris/Vanves 33(1)40 955 900

CANADA

INTERNATIONAL

GERMANY , Langenhagen/ Hanover 49(511)789911

GERMANY , Munich 49 89 92103-0

GERMANY , Nuremberg 49 911 64-3044

GERMANY , Sindelfingen 49 7031 69 910

GERMANY , Wiesbaden 49 611 761921

HONG KONG , Kwai Fong 852-4808333

Tai Po 852-6668333

INDIA , Bangalore (91-812)627094

ISRAEL , Tel Aviv 972(3)753-8222

ITALY , Milan 39(2)82201

JAPAN , Aizu 81(241)272231

JAPAN , Atsugi 81(0462)23-0761

JAPAN , Kumagaya 81(0485)26-2600

JAPAN , Kyushu 81(092)771-4212

JAPAN , Mito 81(0292)26-2340

JAPAN , Nagoya 81(052)232-1621

JAPAN , Osaka 81(06)305-1801

JAPAN, Sendai 81(22)268-4333

JAPAN,

JAPAN,

JAPAN

KOREA , Pusan 82(51)4635-035

KOREA , Seoul 82(2)554-5188

MALAYSIA , Penang 60(4)374514

MEXICO , Mexico City 52(5)282-2864

MEXICO , Guadalajara 52(36)21-8977

Marketing 52(36)21-9023

Customer Service 52(36)669-9160

NETHERLANDS , Best (31)49988 612 11

PUERTO RICO , San Juan (809)793-2170

SINGAPORE

SPAIN , Madrid 34(1)457-8204

or 34(1)457-8254

SWEDEN , Solna 46(8)734-8800

SWITZERLAND , Geneva 41(22)7991111

SWITZERLAND , Zurich 41(1)730 4074

TAlWAN , Taipei 886(2)717-7089

THAILAND , Bangkok (66-2)254-4910

UNITED KINGDOM , Aylesbury 44(296)395-252

COLORADO , Grand Junction

Cheryl Lee Whltely (303) 243-9658

KANSAS , Wichita

Melinda Shores/Kelly Greiving (316) 838 0190

NEVADA , Reno

Galena Technology Group (702) 746 0642

NEW MEXICO , Albuquerque

S&S Technologies, lnc. (505) 298-7177

UTAH , Salt Lake City

Utah Component Sales, Inc. (801) 561-5099

WASHINGTON , Spokane

Doug Kenley (509) 924-2322

ARGENTINA , Buenos Aires

Argonics, S.A. (541) 343-1787

Elmo Semiconductor (818) 768-7400

Minco Technology Labs Inc. (512) 834-2022

Semi Dice Inc. (310) 594-4631

Tachikawa 81(0425)23-6700

Tokyo 81(03)3440-3311

, Yokohama 81(045)472-2751

(65)2945438

FULL LINE REPRESENTATIVES

HYBRID COMPONENTS RESELLERS

M68060 USER’S MANUAL

MOTOROLA

Page 4

PREFACE

The complete documentation package for the MC68060, MC68LC060, and MC68EC060

(collectively called M68060) consists of the M68060UM/AD,

the M68000PM/AD,

Manual

32-bit microprocessors. The

complete instruction set for the M68000 family.

The introduction of this manual includes general information concerning the MC68060 and

summarizes the differences among the M68060 family devices. Additionally, appendices

provide detailed information on how these M68060 derivatives operate differently from the

MC68060.

When reading this manual, disregard information concerning the floating-point unit in reference to the MC68LC060, and disregard information concerning the floating-point unit and

memory management unit in reference to the MC68EC060.

describes the capabilities, operation, and programming of the M68060 superscalar

M68000 Family Programmer’s Reference Manual

M68000 Family Programmer’s Reference Manual

M68060 User’s Manual

. The

M68060 User’s

contains the

, and

The organization of this manual is as follows:

Section 1 Introduction

Section 2 Signal Description

Section 3 Integer Unit

Section 4 Memory Management Unit

Section 5 Caches

Section 6 Floating-Point Unit

Section 7 Bus Operation

Section 8 Exception Processing

Section 9 IEEE 1149.1 Test (JTAG) and Debug Pipe Control Modes

Section 10 Instruction Timings

Section 11 Applications

Section 12 Electrical and Thermal Characteristics

Section 13 Ordering Information and Mechanical Data

Appendix A MC68LC060

Appendix B MC68EC060

Appendix C MC68060 Software Package

Appendix D M68060 Instructions

MOTOROLA

M68060 USER’S MANUAL

v

Page 5

MC68060 ACRONYM LIST

AGU—address generation unit

ALU—arithmetic logic unit

ATC—address translation cache

BUSCR—bus control register

CACR—cache control register

CCR—condition code register

CM—cache mode

CPU—central processing unit

DFC—destination function code

DTTx—data transparent translation register

DRAM—dynamic random access memory

FPIAR—floating-point instruction address register

FPCR—floating-point control register

FPSP—floating-point software package

FPSR—floating-point status register

FPU—floating-point unit

FP7–FP0—floating-point data registers 7–0

FSLW—fault status long word

IEE—integer execute unit

IFP—instruction fetch pipeline

IFU—instruction fetch unit

IPU—instruction pipe unit

ISP—interrupt stack pointer

ITTR—instruction transparent translation register

IU—integer unit

JTAG—Joint Test Action Group

MMU—memory management unit

MOTOROLA

M68060 USER’S MANUAL

vii

Page 6

MC68060 Acronym List

MMUSR—memory management unit status register

M68060SP—M68060 software package

NANs—not-a-numbers

NOP—no operation

OEP—operand execution pipeline

OPU—operand pipe unit

PC—program counter

PCR—processor configuration register

PGI—page index field

PI—pointer index field

PLL—phase-locked loop

pOEP—primary operand execution pipeline

RI—root index field

SFC—source function code

SNAN—signaling not-a-number

sOEP—secondary operand execution pipeline

SP—stack pointer

SR—status register

SRP—supervisor root pointer register

SSP—supervisor stack pointer

TAP—test access port

TCR—translation control register

TTL—transistor-transistor logic

TTR—transparent translation register

UPA—user page attribute

URP—user root pointer register

USP—user stack pointer

VBR—vector base register

VLSI—very large-scale integration

viii

M68060 USER’S MANUAL

MOTOROLA

Page 7

TABLE OF CONTENTS

Section 1

Introduction

1.1 Differences Among M68060 Family Members..............................................1-3

1.1.1 MC68LC060................................................................................................1-3

1.1.2 MC68EC060...............................................................................................1-3

1.1.2.1 Address Translation Differences ..............................................................1-3

1.1.2.2 Instruction Differences..............................................................................1-3

1.2 Features........................................................................................................1-4

1.3 Architecture...................................................................................................1-4

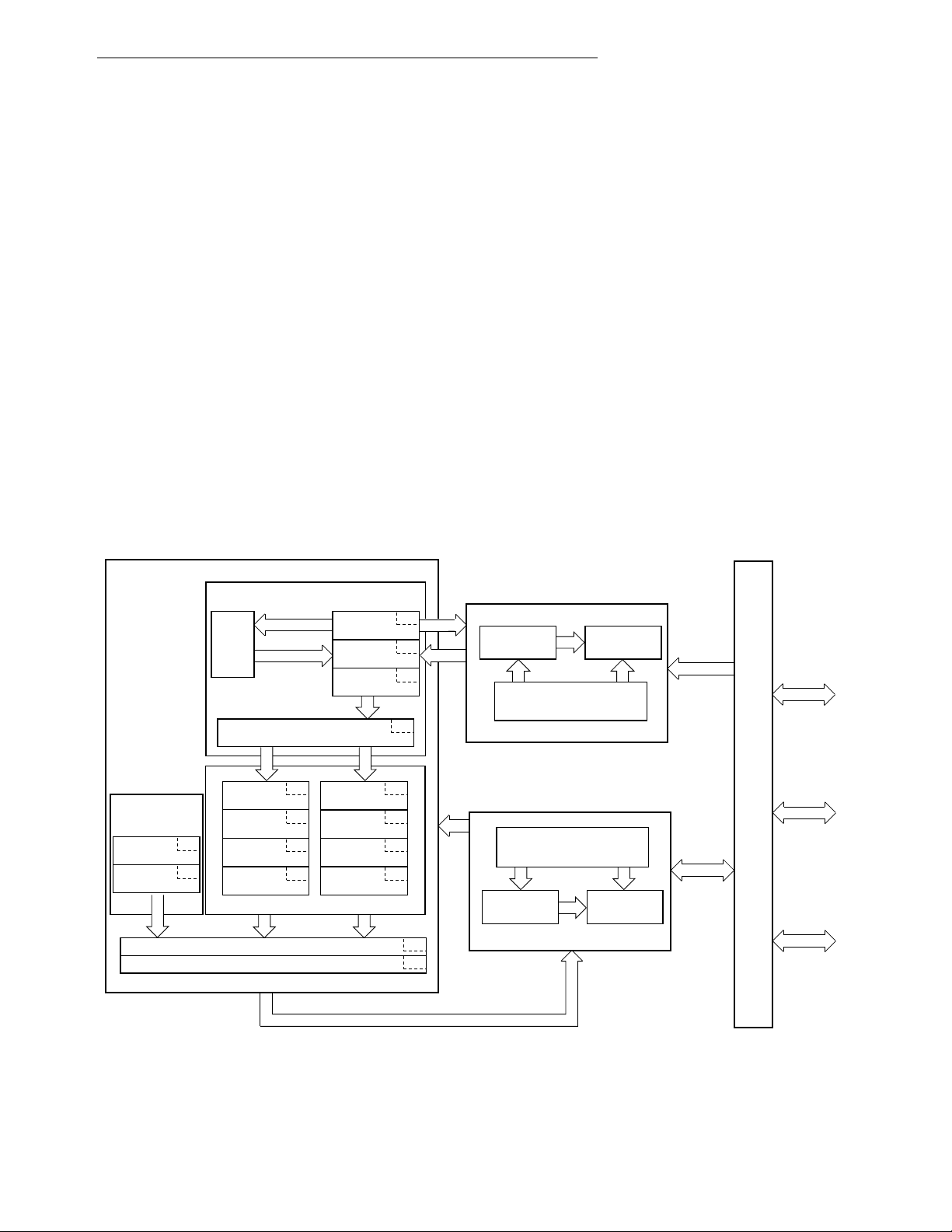

1.4 Processor Overview......................................................................................1-5

1.4.1 Functional Blocks........................................................................................1-5

1.4.2 Integer Unit.................................................................................................1-7

1.4.2.1 Instruction Fetch Unit................................................................................1-7

1.4.2.2 Integer Unit...............................................................................................1-8

1.4.2.3 Floating-Point Unit....................................................................................1-8

1.4.2.4 Memory Units ...........................................................................................1-9

1.4.2.5 Address Translation Caches ....................................................................1-9

1.4.2.6 Instruction and Data Caches ....................................................................1-9

1.4.2.6.1 Cache Organization..............................................................................1-10

1.4.2.6.2 Cache Coherency.................................................................................1-10

1.4.3 Bus Controller...........................................................................................1-10

1.5 Processing States.......................................................................................1-10

1.6 Programming Model....................................................................................1-11

1.7 Data Format Summary................................................................................1-14

1.8 Addressing Capabilities Summary..............................................................1-14

1.9 Instruction Set Overview.............................................................................1-15

1.10 Notational Conventions...............................................................................1-21

Section 2

Signal Description

2.1 Address and Control Signals ........................................................................2-3

2.1.1 Address Bus (A31–A0)...............................................................................2-3

2.1.2 Cycle Long-Word Address (CLA

) ...............................................................2-4

2.2 Data Bus (D31–D0).......................................................................................2-4

2.3 Transfer Attribute Signals .............................................................................2-4

2.3.1 Transfer Cycle Type (TT1, TT0).................................................................2-4

2.3.2 Transfer Cycle Modifier (TM2–TM0)...........................................................2-4

2.3.3 Transfer Line Number (TLN1, TLN0)..........................................................2-5

2.3.4 User-Programmable Page Attributes (UPA1, UPA0)..................................2-5

2.3.5 Read/Write (R/W

MOTOROLA

) .......................................................................................2-6

M68060 USER’S MANUAL

ix

Page 8

x

Table of Contents

2.3.6 Transfer Size (SIZ1, SIZ0)..........................................................................2-6

2.3.7 Bus Lock (LOCK

2.3.8 Bus Lock End (LOCKE

2.3.9 Cache Inhibit Out (CIOUT

2.3.10 Byte Select Lines (BS3

)........................................................................................ 2-6

)..............................................................................2-6

)......................................................................... 2-7

–BS0).....................................................................2-7

2.4 Master Transfer Control Signals................................................................... 2-7

2.4.1 Transfer Start (TS

2.4.2 Transfer in Progress (TIP

2.4.3 Starting Termination Acknowledge Signal Sampling (SAS

)...................................................................................... 2-8

).......................................................................... 2-8

)....................... 2-8

2.5 Slave Transfer Control Signals..................................................................... 2-8

2.5.1 Transfer Acknowledge (TA

2.5.2 Transfer Retry Acknowledge (TRA

)........................................................................2-8

)............................................................ 2-8

2.5.3 Transfer Error Acknowledge (TEA) ............................................................2-9

2.5.4 Transfer Burst Inhibit (TBI

2.5.5 Transfer Cache Inhibit (TCI

2.6 Snoop Control (SNOOP

)......................................................................... 2-9

)....................................................................... 2-9

) ..............................................................................2-9

2.7 Arbitration Signals....................................................................................... 2-10

2.7.1 Bus Request (BR

2.7.2 Bus Grant (BG

2.7.3 Bus Grant Relinquish Control (BGR

2.7.4 Bus Tenure Termination (BTT

2.7.5 Bus Busy (BB

)..................................................................................... 2-10

).........................................................................................2-10

)........................................................2-10

).................................................................2-10

)..........................................................................................2-11

2.8 Processor Control Signals.......................................................................... 2-11

2.8.1 Cache Disable (CDIS

2.8.2 MMU Disable (MDIS

2.8.3 Reset In (RSTI

)......................................................................................... 2-12

2.8.4 Reset Out (RSTO

).............................................................................. 2-11

)................................................................................ 2-12

).................................................................................... 2-12

2.9 Interrupt Control Signals............................................................................. 2-12

2.9.1 Interrupt Priority Level (IPL2

2.9.2 Interrupt Pending Status (IPEND

2.9.3 Autovector (AVEC

)................................................................................... 2-13

–IPL0)..........................................................2-12

) ............................................................2-12

2.10 Status and Clock Signals............................................................................2-13

2.10.1 Processor Status (PST4–PST0)...............................................................2-13

2.10.2 MC68060 Processor Clock (CLK) ............................................................2-14

2.10.3 Clock Enable (CLKEN

)............................................................................. 2-14

2.11 Test Signals................................................................................................2-15

2.11.1 JTAG Enable (JTAG

)................................................................................ 2-15

2.11.2 Test Clock (TCK)...................................................................................... 2-15

2.11.3 Test Mode Select (TMS)........................................................................... 2-15

2.11.4 Test Data In (TDI).....................................................................................2-16

2.11.5 Test Data Out (TDO)................................................................................ 2-16

2.11.6 Test Reset (TRST) ...................................................................................2-16

2.12 Thermal Sensing Pins (THERM1, THERM0)..............................................2-16

2.13 Power Supply Connections.........................................................................2-16

2.14 Signal Summary .........................................................................................2-16

M68060 USER’S MANUAL

MOTOROLA

Page 9

Table of Contents

Section 3

Integer Unit

3.1 Integer Unit Execution Pipelines...................................................................3-1

3.2 Integer Unit Register Description..................................................................3-2

3.2.1 Integer Unit User Programming Model.......................................................3-2

3.2.1.1 Data Registers (D7–D0) ...........................................................................3-2

3.2.1.2 Address Registers (A6–A0)......................................................................3-2

3.2.1.3 User Stack Pointer (A7)............................................................................3-2

3.2.1.4 Program Counter......................................................................................3-3

3.2.1.5 Condition Code Register ..........................................................................3-3

3.2.2 Integer Unit Supervisor Programming Model..............................................3-3

3.2.2.1 Supervisor Stack Pointer..........................................................................3-4

3.2.2.2 Status Register.........................................................................................3-4

3.2.2.3 Vector Base Register................................................................................3-4

3.2.2.4 Alternate Function Code Registers...........................................................3-5

3.2.2.5 Processor Configuration Register.............................................................3-5

Section 4

Memory Management Unit

4.1 Memory Management Programming Model..................................................4-3

4.1.1 User and Supervisor Root Pointer Registers..............................................4-3

4.1.2 Translation Control Register.......................................................................4-4

4.1.3 Transparent Translation Registers .............................................................4-6

4.2 Logical Address Translation..........................................................................4-7

4.2.1 Translation Tables......................................................................................4-7

4.2.2 Descriptors................................................................................................4-12

4.2.2.1 Table Descriptors....................................................................................4-12

4.2.2.2 Page Descriptors....................................................................................4-12

4.2.2.3 Descriptor Field Definitions.....................................................................4-13

4.2.3 Translation Table Example.......................................................................4-15

4.2.4 Variations in Translation Table Structure..................................................4-16

4.2.4.1 Indirect Action.........................................................................................4-16

4.2.4.2 Table Sharing Between Tasks................................................................4-17

4.2.4.3 Table Paging ..........................................................................................4-17

4.2.4.4 Dynamically Allocated Tables.................................................................4-17

4.2.5 Table Search Accesses............................................................................4-19

4.2.6 Address Translation Protection.................................................................4-20

4.2.6.1 Supervisor and User Translation Tables ................................................4-21

4.2.6.2 Supervisor Only......................................................................................4-22

4.2.6.3 Write Protect...........................................................................................4-22

4.3 Address Translation Caches.......................................................................4-24

4.4 Transparent Translation..............................................................................4-27

4.5 Address Translation Summary....................................................................4-28

4.6 RSTI

4.6.1 Effect of RSTI

and MDIS Effect on the MMU............................................................4-28

on the MMUs.....................................................................4-28

MOTOROLA

M68060 USER’S MANUAL

xi

Page 10

Table of Contents

4.6.2 Effect of MDIS on Address Translation .................................................... 4-30

4.7 MMU Instructions........................................................................................4-30

4.7.1 MOVEC ....................................................................................................4-30

4.7.2 PFLUSH ...................................................................................................4-30

4.7.3 PLPA ........................................................................................................4-30

Section 5

Caches

5.1 Cache Operation........................................................................................... 5-1

5.2 Cache Control Register ................................................................................5-5

5.3 Cache Management .....................................................................................5-6

5.4 Caching Modes.............................................................................................5-7

5.4.1 Cachable Accesses.................................................................................... 5-7

5.4.1.1 Writethrough Mode...................................................................................5-7

5.4.1.2 Copyback Mode .......................................................................................5-8

5.4.2 Cache-Inhibited Accesses.......................................................................... 5-8

5.4.3 Special Accesses .......................................................................................5-9

5.5 Cache Protocol.............................................................................................5-9

5.5.1 Read Miss...................................................................................................5-9

5.5.2 Write Miss...................................................................................................5-9

5.5.3 Read Hit......................................................................................................5-9

5.5.4 Write Hit....................................................................................................5-10

5.6 Cache Coherency....................................................................................... 5-10

5.7 Memory Accesses for Cache Maintenance................................................ 5-11

5.7.1 Cache Filling.............................................................................................5-11

5.7.2 Cache Pushes..........................................................................................5-13

5.8 Push Buffer................................................................................................. 5-13

5.9 Store Buffer................................................................................................. 5-13

5.10 Push Buffer and Store Buffer Bus Operation..............................................5-14

5.11 Branch Cache.............................................................................................5-14

5.12 Cache Operation Summary ........................................................................ 5-15

5.12.1 Instruction Cache...................................................................................... 5-15

5.12.2 Data Cache............................................................................................... 5-16

Section 6

Floating-Point Unit

6.1 Floating-Point User Programming Model...................................................... 6-2

6.1.1 Floating-Point Data Registers (FP7–FP0).................................................. 6-3

6.1.2 Floating-Point Control Register (FPCR).....................................................6-3

6.1.2.1 Exception Enable Byte ............................................................................. 6-3

6.1.2.2 Mode Control Byte.................................................................................... 6-3

6.1.3 Floating-Point Status Register (FPSR).......................................................6-4

6.1.3.1 Floating-Point Condition Code Byte ......................................................... 6-5

6.1.3.2 Quotient Byte............................................................................................ 6-5

6.1.3.3 Exception Status Byte .............................................................................. 6-5

xii

M68060 USER’S MANUAL

MOTOROLA

Page 11

Table of Contents

6.1.3.4 Accrued Exception Byte ...........................................................................6-6

6.1.4 Floating-Point Instruction Address Register (FPIAR) .................................6-7

6.2 Floating-Point Data Formats and Data Types...............................................6-7

6.3 Computational Accuracy.............................................................................6-11

6.3.1 Intermediate Result...................................................................................6-12

6.3.2 Rounding the Result.................................................................................6-13

6.4 Postprocessing Operation...........................................................................6-15

6.4.1 Underflow, Round, and Overflow..............................................................6-15

6.4.2 Conditional Testing...................................................................................6-16

6.5 Floating-Point Exceptions...........................................................................6-19

6.5.1 Unimplemented Floating-Point Instructions..............................................6-19

6.5.2 Unsupported Floating-Point Data Types...................................................6-21

6.5.3 Unimplemented Effective Address Exception...........................................6-22

6.6 Floating-Point Arithmetic Exceptions..........................................................6-22

6.6.1 Branch/Set on Unordered (BSUN)............................................................6-24

6.6.1.1 Trap Disabled Results (FPCR BSUN Bit Cleared) .................................6-24

6.6.1.2 Trap Enabled Results (FPCR BSUN Bit Set) .........................................6-24

6.6.2 Signaling Not-a-Number (SNAN)..............................................................6-25

6.6.2.1 Trap Disabled Results (FPCR SNAN Bit Cleared) .................................6-25

6.6.2.2 Trap Enabled Results (FPCR SNAN Bit Set) .........................................6-26

6.6.3 Operand Error...........................................................................................6-26

6.6.3.1 Trap Disabled Results (FPCR OPERR Bit Cleared)...............................6-27

6.6.3.2 Trap Enabled Results (FPCR OPERR Bit Set).......................................6-27

6.6.4 Overflow....................................................................................................6-28

6.6.4.1 Trap Disabled Results (FPCR OVFL Bit Cleared)..................................6-29

6.6.4.2 Trap Enabled Results (FPCR OVFL Bit Set)..........................................6-29

6.6.5 Underflow..................................................................................................6-30

6.6.5.1 Trap Disabled Results (FPCR UNFL Bit Cleared)..................................6-31

6.6.5.2 Trap Enabled Results (FPCR UNFL Bit Set)..........................................6-31

6.6.6 Divide-by-Zero..........................................................................................6-32

6.6.6.1 Trap Disabled Results (FPCR DZ Bit Cleared).......................................6-33

6.6.6.2 Trap Enabled Results (FPCR DZ Bit Set)...............................................6-33

6.6.7 Inexact Result...........................................................................................6-33

6.6.7.1 Trap Disabled Results (FPCR INEX1 Bit and INEX2 Bit Cleared...........6-34

6.6.7.2 Trap Enabled Results (Either FPCR INEX1 Bit or INEX2 Bit Set)..........6-34

6.7 Floating-Point State Frames.......................................................................6-35

Section 7

Bus Operation

7.1 Bus Characteristics.......................................................................................7-1

7.2 Full-, Half-, and Quarter-Speed Bus Operation and BCLK...........................7-3

7.3 Acknowledge Termination Ignore State Capability.......................................7-4

7.4 Bus Control Register.....................................................................................7-4

7.5 Data Transfer Mechanism.............................................................................7-5

7.6 Misaligned Operands....................................................................................7-9

MOTOROLA

M68060 USER’S MANUAL

xiii

Page 12

Table of Contents

7.7 Processor Data Transfers...........................................................................7-12

7.7.1 Byte, Word, and Long-Word Read Transfer Cycles.................................7-12

7.7.2 Line Read Transfer...................................................................................7-15

7.7.3 Byte, Word, and Long-Word Write Cycles................................................7-20

7.7.4 Line Write Cycles.....................................................................................7-25

7.7.5 Locked Read-Modify-Write Cycles..........................................................7-28

7.7.6 Emulating CAS2 and CAS Misaligned......................................................7-31

7.7.7 Using CLA

to Increment A3 and A2.......................................................... 7-32

7.8 Acknowledge Cycles................................................................................... 7-32

7.8.1 Interrupt Acknowledge Cycles................................................................. 7-32

7.8.1.1 Interrupt Acknowledge Cycle (Terminated Normally).............................7-35

7.8.1.2 Autovector Interrupt Acknowledge Cycle ...............................................7-35

7.8.1.3 Spurious Interrupt Acknowledge Cycle ..................................................7-35

7.8.2 Breakpoint Acknowledge Cycle................................................................ 7-36

7.8.2.1 LPSTOP Broadcast Cycle......................................................................7-38

7.9 Bus Exception Control Cycles ....................................................................7-46

7.9.1 Bus Errors.................................................................................................7-46

7.9.2 Retry Operation........................................................................................7-48

7.9.3 Double Bus Fault...................................................................................... 7-51

7.10 Bus Synchronization...................................................................................7-52

7.11 Bus Arbitration ............................................................................................ 7-52

7.11.1 MC68040-Arbitration Protocol (BB Protocol)............................................7-53

7.11.2 MC68060-Arbitration Protocol (BTT Protocol)..........................................7-58

7.11.3 External Arbiter Considerations................................................................7-65

7.12 Bus Snooping Operation............................................................................7-68

7.13 Reset Operation.........................................................................................7-71

7.14 Special Modes of Operation .......................................................................7-74

7.14.1 Acknowledge Termination Ignore State Capability...................................7-74

7.14.2 Acknowledge Termination Protocol.......................................................... 7-76

7.14.3 Extra Data Write Hold Time Mode............................................................7-76

Section 8

Exception Processing

8.1 Exception Processing Overview...................................................................8-1

8.2 Integer Unit Exceptions................................................................................. 8-4

8.2.1 Access Error Exception..............................................................................8-5

8.2.2 Address Error Exception.............................................................................8-7

8.2.3 Instruction Trap Exception..........................................................................8-7

8.2.4 Illegal Instruction and Unimplemented Instruction Exceptions...................8-8

8.2.5 Privilege Violation Exception....................................................................8-10

8.2.6 Trace Exception........................................................................................8-10

8.2.7 Format Error Exception ............................................................................8-11

8.2.8 Breakpoint Instruction Exception.............................................................. 8-11

8.2.9 Interrupt Exception ...................................................................................8-12

8.2.10 Reset Exception .......................................................................................8-14

xiv

M68060 USER’S MANUAL

MOTOROLA

Page 13

Table of Contents

8.3 Exception Priorities.....................................................................................8-17

8.4 Return from Exceptions ..............................................................................8-19

8.4.1 Four-Word Stack Frame (Format $0) .......................................................8-19

8.4.2 Six-Word Stack Frame (Format $2)..........................................................8-20

8.4.3 Floating-Point Post-Instruction Stack Frame (Format $3) ........................8-20

8.4.4 Eight-Word Stack Frame (Format $4).......................................................8-21

8.4.4.1 Program Counter (PC)............................................................................8-21

8.4.4.2 Fault Address .........................................................................................8-22

8.4.4.3 Fault Status Long Word (FSLW).............................................................8-22

8.4.5 Recovering from an Access Error.............................................................8-25

8.4.6 Bus Errors and Pending Memory Writes .................................................8-27

8.4.7 Branch Prediction Error ............................................................................8-29

Section 9

IEEE 1149.1 Test (JTAG) and Debug Pipe Control Modes

9.1 IEEE 1149.1 Test Access Port (Normal JTAG) Mode ..................................9-1

9.1.1 Overview.....................................................................................................9-2

9.1.2 JTAG Instruction Shift Register ..................................................................9-3

9.1.2.1 EXTEST....................................................................................................9-4

9.1.2.2 LPSAMPLE...............................................................................................9-5

9.1.2.3 Private Instructions...................................................................................9-5

9.1.2.4 SAMPLE/PRELOAD.................................................................................9-5

9.1.2.5 IDCODE....................................................................................................9-5

9.1.2.6 CLAMP .....................................................................................................9-6

9.1.2.7 HIGHZ.......................................................................................................9-6

9.1.2.8 BYPASS ...................................................................................................9-6

9.1.3 JTAG Test Data Registers..........................................................................9-7

9.1.3.1 Idcode Register ........................................................................................9-7

9.1.3.2 Boundary Scan Register...........................................................................9-7

9.1.3.3 Bypass Register .....................................................................................9-15

9.1.4 Restrictions...............................................................................................9-15

9.1.5 Disabling the IEEE 1149.1 Standard Operation .......................................9-15

9.1.6 Motorola MC68060 BSDL Description......................................................9-17

9.2 Debug Pipe Control Mode...........................................................................9-24

9.2.1 Debug Command Interface.......................................................................9-25

9.2.2 Debug Pipe Control Mode Commands.....................................................9-27

9.2.3 Emulator Mode .........................................................................................9-31

9.3 Switching between JTAG and Debug Pipe ControlModes of Operation.....9-33

Section 10

Instruction Execution Timing

10.1 Superscalar Operand Execution Pipelines .................................................10-1

10.1.1 Dispatch Test 1: sOEP Opword and Required

Extension Words Are Valid.......................................................................10-2

10.1.2 Dispatch Test 2: Instruction Classification................................................10-2

MOTOROLA

M68060 USER’S MANUAL

xv

Page 14

Table of Contents

10.1.3 Dispatch Test 3: Allowable Effective Addressing Mode in the sOEP.......10-8

10.1.4 Dispatch Test 4: Allowable Operand Data Memory Reference................ 10-8

10.1.5 Dispatch Test 5: No Register Conflicts on sOEP.AGU Resources ..........10-8

10.1.6 Dispatch Test 6: No Register Conflicts on sOEP.IEE Resources ............10-9

10.2 Timing Assumptions .................................................................................10-10

10.3 Cache and ATC Performance Degradation Times ................................... 10-12

10.3.1 Instruction ATC Miss ..............................................................................10-12

10.3.2 Data ATC Miss .......................................................................................10-13

10.3.3 Instruction Cache Miss...........................................................................10-13

10.3.4 Data Cache Miss....................................................................................10-13

10.4 Effective Address Calculation Times ........................................................ 10-14

10.5 Move Instruction Execution Times............................................................10-14

10.6 Standard Instruction Execution Times......................................................10-16

10.7 Immediate Instruction Execution Times....................................................10-17

10.8 Single-Operand Instruction Execution Times ...........................................10-18

10.9 Shift/Rotate Execution Times ...................................................................10-19

10.10 Bit Manipulation and Bit Field Execution Times........................................ 10-19

10.11 Branch Instruction Execution Times.........................................................10-21

10.12 LEA, PEA, and MOVEM Execution Times................................................ 10-22

10.13 Multiprecision Instruction Execution Times............................................... 10-22

10.14 Status Register, MOVES, and Miscellaneous

Instruction Execution Times...................................................................... 10-22

10.15 FPU Instruction Execution Times .............................................................10-24

10.16 Exception Processing Times ....................................................................10-26

Section 11

Applications Information

11.1 Guidelines for Porting Software to the MC68060 .......................................11-1

11.1.1 User Code ................................................................................................11-1

11.1.2 Supervisor Code.......................................................................................11-1

11.1.2.1 Initialization Code (Reset Exception Handler)........................................11-2

11.1.2.1.1 Processor Configuration Register (PCR) (MOVEC of PCR)................11-2

11.1.2.1.2 Default Transparent Translation Register (MOVEC of TCR) ............... 11-2

11.1.2.1.3 MC68060 Software Package (M68060SP). ......................................... 11-2

11.1.2.1.4 Cache Control Register (CACR) (MOVEC of CACR)..........................11-3

11.1.2.1.5 Resource Checking (Access Error Handler) ........................................ 11-3

11.1.2.2 Virtual Memory Software........................................................................11-3

11.1.2.2.1 Translation Control Register (MOVEC of TCR)....................................11-3

11.1.2.2.2 Descriptors in Cacheable Copyback Pages Prohibited........................11-4

11.1.2.2.3 Page and Descriptor Faults (Access Error Handler)............................11-4

11.1.2.2.4 PTEST, MOVEC of MMUSR, and PLPA..............................................11-4

11.1.2.3 Context Switch Interrupt Handlers.......................................................... 11-5

11.1.2.4 Trace Handlers.......................................................................................11-5

11.1.2.5 I/O Device Driver Software.....................................................................11-5

11.1.3 Precise Vs. Imprecise Exception Mode.................................................... 11-6

xvi

M68060 USER’S MANUAL

MOTOROLA

Page 15

Table of Contents

11.1.4 Other Considerations................................................................................11-6

11.2 Using an MC68060 in an Existing MC68040 System .................................11-6

11.2.1 Power Considerations...............................................................................11-6

11.2.1.1 DC to DC Voltage Conversion................................................................11-6

11.2.1.1.1 Linear Voltage Regulator Solution........................................................11-7

11.2.1.1.2 Switching Regulator Solution................................................................11-7

11.2.1.2 Input Signals During Power-Up Requirement.......................................11-11

11.2.2 Output Hold Time Differences ................................................................11-11

11.2.3 Bus Arbitration........................................................................................11-13

11.2.4 Snooping.................................................................................................11-13

11.2.5 Special Modes........................................................................................11-13

11.2.6 Clocking..................................................................................................11-14

11.2.7 PSTx Encoding.......................................................................................11-14

11.2.8 Miscellaneous Pullup Resistors..............................................................11-15

11.3 Example DRAM Access............................................................................11-15

11.4 Thermal Management..............................................................................11-17

11.5 Support Devices.......................................................................................11-20

Section 12

Electrical and Thermal Characteristics

12.1 Maximum Ratings .......................................................................................12-1

12.2 Thermal Characteristics..............................................................................12-1

12.3 Power Dissipation .......................................................................................12-1

12.4 DC Electrical Specifications (Vcc = 3.3 Vdc ± 5%).....................................12-2

12.5 Clock Input Specifications (Vcc = 3.3 Vdc ± 5%)........................................12-3

12.6 Output AC Timing Specifications (Vcc = 3.3 Vdc ± 5%).............................12-4

12.7 Input AC Timing Specifications (Vcc = 3.3 Vdc ± 5%)................................12-6

Section 13

Ordering Information and Mechanical Data

13.1 Ordering Information...................................................................................13-1

13.2 Pin Assignments .........................................................................................13-1

13.2.1 MC68060, MC68LC060, and MC68EC060 Pin Grid Array (RC Suffix) ....13-2

13.2.2 MC68060, MC68LC060, and MC68EC060 Quad Flat Pack (FE Suffix)...13-3

13.3 Mechanical Data .........................................................................................13-4

Appendix A

MC68LC060

Appendix B

MC68EC060

B.1 Address Translation Differences...................................................................B-1

B.2 Instruction Differences..................................................................................B-1

MOTOROLA

M68060 USER’S MANUAL

xvii

Page 16

Table of Contents

Appendix C

MC68060 Software Package

C.1 Module Format..............................................................................................C-2

C.2 Unimplemented Integer Instructions.............................................................C-4

C.2.1 Integer Emulation Results ..........................................................................C-5

C.2.2 Module 1: Unimplemented Integer Instruction Exception

(MC68060ISP)............................................................................................C-5

C.2.2.1 Unimplemented Integer Instruction Exception Module Entry Points ........C-6

C.2.2.2 Unimplemented Integer Instruction Exception Module Call-Outs.............C-6

C.2.2.3 CAS Misaligned Address and CAS2

Emulation-Related Call-Outs and Entry Points ........................................C-6

C.2.3 Module 2: Unimplemented Integer Instruction Library (MC68060ILSP).....C-9

C.3 Floating-Point Emulation Package (MC68060FPSP) .................................C-11

C.3.1 Floating-Point Emulation Results .............................................................C-13

C.3.2 Module 3: Full Floating-Point Kernel ........................................................C-14

C.3.2.1 Full Floating-Point Kernel Module Entry Points......................................C-14

C.3.2.2 Full Floating-Point Kernel Module Call-Outs..........................................C-14

C.3.2.2.1 The F-Line Exception Call-Outs...........................................................C-14

C.3.2.2.2 System-Supplied Floating-Point Arithmetic

Exception Handler Call-Outs................................................................C-15

C.3.2.2.3 Exception-Related Call-Outs...............................................................C-15

C.3.2.2.4 Exit Point Call-Outs..............................................................................C-15

C.3.2.3 Bypassing Module-Supplied Floating-Point Arithmetic Handlers...........C-15

C.3.2.3.1 Overflow/Underflow..............................................................................C-16

C.3.2.3.2 Signalling Not-A-Number, Operand Error.............................................C-17

C.3.2.3.3 Inexact Exception.................................................................................C-18

C.3.2.3.4 Divide-by-Zero Exception.....................................................................C-19

C.3.2.3.5 Branch/Set on Unordered Exception....................................................C-19

C.3.2.4 Exceptions During Emulation.................................................................C-20

C.3.2.4.1 Trap-Disabled Operation......................................................................C-20

C.3.2.4.2 Trap-Enabled Operation.......................................................................C-21

C.3.3 Module 4: Partial Floating-Point Kernel....................................................C-21

C.3.4 Module 5: Floating-Point Library (M68060FPLSP)...................................C-22

C.4 Operating System Dependencies...............................................................C-23

C.4.1 Instruction and Data Fetches....................................................................C-23

C.4.2 Instructions Not Recommended...............................................................C-26

C.5 Installation Notes ........................................................................................C-27

C.5.1 Installing the Library Modules...................................................................C-27

C.5.2 Installing the Kernel Modules ...................................................................C-27

C.5.3 Release Notes and Module Offset Assignments......................................C-28

C.5.4 AESOP Electronic Bulletin Board.............................................................C-29

xviii

Appendix D

MC68060 Instructions

M68060 USER’S MANUAL

MOTOROLA

Page 17

LIST OF ILLUSTRATIONS

1-1 MC68060 Block Diagram ...................................................................................1-6

1-2 Programming Model.........................................................................................1-12

2-1 Functional Signal Groups...................................................................................2-3

3-1 MC68060 Integer Unit Pipeline ..........................................................................3-1

3-2 Integer Unit User Programming Model...............................................................3-2

3-3 Integer Unit Supervisor Programming Model.....................................................3-3

3-4 Status Register...................................................................................................3-4

3-5 Processor Configuration Register ......................................................................3-5

4-1 Memory Management Unit.................................................................................4-2

4-2 Memory Management Programming Model.......................................................4-3

4-3 URP and SRP Register Formats........................................................................4-3

4-4 Translation Control Register Format..................................................................4-4

4-5 Transparent Translation Register Format ..........................................................4-6

4-6 Translation Table Structure................................................................................4-8

4-7 Logical Address Format .....................................................................................4-8

4-8 Detailed Flowchart of Table Search Operation ................................................4-10

4-9 Detailed Flowchart of Descriptor Fetch Operation ...........................................4-11

4-10 Table Descriptor Formats.................................................................................4-12

4-11 Page Descriptor Formats .................................................................................4-12

4-12 Example Translation Table...............................................................................4-15

4-13 Translation Table Using Indirect Descriptors ...................................................4-16

4-14 Translation Table Using Shared Tables...........................................................4-18

4-15 Translation Table with Nonresident Tables......................................................4-19

4-16 Translation Table Structure for Two Tasks ......................................................4-21

4-17 Logical Address Map with Shared Supervisor and User Address Spaces.......4-22

4-18 Translation Table Using S-Bit and W-Bit To Set Protection.............................4-23

4-19 ATC Organization.............................................................................................4-24

4-20 ATC Entry and Tag Fields................................................................................4-25

4-21 Address Translation Flowchart.........................................................................4-29

5-1 MC68060 Instruction and Data Caches .............................................................5-2

5-2 Instruction Cache Line Format...........................................................................5-2

5-3 Data Cache Line Format....................................................................................5-2

5-4 Caching Operation .............................................................................................5-3

5-5 Cache Control Register......................................................................................5-5

5-6 Instruction Cache Line State Diagram..............................................................5-16

5-7 Data Cache Line State Diagrams.....................................................................5-18

6-1 Floating-Point Unit Block Diagram .....................................................................6-2

6-2 Floating-Point User Programming Model...........................................................6-3

6-3 Floating-Point Control Register Format..............................................................6-4

MOTOROLA

M68060 USER’S MANUAL

xix

Page 18

xx

List of Illustrations

6-4 Floating-Point Condition Code (FPSR)..............................................................6-5

6-5 Floating-Point Quotient Byte (FPSR).................................................................6-5

6-6 Floating-Point Exception Status Byte (FPSR)....................................................6-6

6-7 Floating-Point Accrued Exception Byte (FPSR).................................................6-6

6-8 Intermediate Result Format.............................................................................. 6-12

6-9 Rounding Algorithm Flowchart......................................................................... 6-14

6-10 Floating-Point State Frame..............................................................................6-35

6-11 Status Word Contents...................................................................................... 6-36

7-1 Signal Relationships to Clocks...........................................................................7-2

7-2 Full-Speed Clock................................................................................................7-2

7-3 Half-Speed Clock...............................................................................................7-2

7-4 Quarter-Speed Clock .........................................................................................7-3

7-5 Bus Control Register Format.............................................................................. 7-4

7-6 Internal Operand Representation.......................................................................7-5

7-7 Data Multiplexing................................................................................................ 7-6

7-8 Byte Select Signal Generation and PAL Equation.............................................7-8

7-9 Example of a Misaligned Long-Word Transfer.................................................7-10

7-10 Example of Misaligned Word Transfer............................................................. 7-10

7-11 Misaligned Long-Word Read Bus Cycle Timing............................................... 7-11

7-12 Byte, Word, and Long-Word Read Cycle Flowchart ........................................7-13

7-13 Byte, Word, and Long-Word Read Bus Cycle Timing...................................... 7-14

7-14 Line Read Cycle Flowchart..............................................................................7-17

7-15 Line Read Transfer Timing............................................................................... 7-18

7-16 Burst-Inhibited Line Read Cycle Flowchart...................................................... 7-20

7-17 Burst-Inhibited Line Read Bus Cycle Timing.................................................... 7-21

7-18 Byte, Word, and Long-Word Write Transfer Flowchart....................................7-22

7-19 Long-Word Write Bus Cycle Timing................................................................. 7-23

7-20 Line Write Cycle Flowchart ..............................................................................7-26

7-21 Line Write Burst-Inhibited Cycle Flowchart......................................................7-27

7-22 Line Write Bus Cycle Timing............................................................................ 7-28

7-23 Locked Bus Cycle for TAS Instruction Timing..................................................7-30

7-24 Using CLA

in a High-Speed DRAM Design .....................................................7-33

7-25 Interrupt Pending Procedure............................................................................ 7-33

7-26 Assertion of IPEND

..........................................................................................7-34

7-27 Interrupt Acknowledge Cycle Flowchart...........................................................7-36

7-28 Interrupt Acknowledge Bus Cycle Timing ........................................................7-37

7-29 Autovector Interrupt Acknowledge Bus Cycle Timing......................................7-38

7-30 Breakpoint Interrupt Acknowledge Cycle Flowchart......................................... 7-39

7-31 Breakpoint Interrupt Acknowledge Bus Cycle Timing......................................7-40

7-32 LPSTOP Broadcast Cycle Flowchart...............................................................7-41

7-33 LPSTOP Broadcast Bus Cycle Timing, BG Negated....................................... 7-42

7-34 LPSTOP Broadcast Bus Cycle Timing, BG Asserted ......................................7-43

7-35 Exiting LPSTOP Mode Flowchart..................................................................... 7-44

7-36 Exiting LPSTOP Mode Timing Diagram...........................................................7-45

7-37 Word Write Access Bus Cycle Terminated with TEA

Timing........................... 7-48

M68060 USER’S MANUAL

MOTOROLA

Page 19

List of Illustrations

7-38 Line Read Access Bus Cycle Terminated with TEA Timing.............................7-49

7-39 Retry Read Bus Cycle Timing..........................................................................7-50

7-40 Line Write Retry Bus Cycle Timing...................................................................7-51

7-41 MC68040-Arbitration Protocol State Diagram..................................................7-57

7-42 MC68060-Arbitration Protocol State Diagram..................................................7-64

7-43 Processor Bus Request Timing........................................................................7-67

7-44 Arbitration During Relinquish and Retry Timing...............................................7-68

7-45 Implicit Bus Ownership Arbitration Timing........................................................7-69

7-46 Effect of BGR

on Locked Sequences...............................................................7-70

7-47 Snooped Bus Cycle..........................................................................................7-71

7-48 Initial Power-On Reset Timing..........................................................................7-72

7-49 Normal Reset Timing........................................................................................7-73

7-50 Data Bus Usage During Reset.........................................................................7-74

7-51 Acknowledge Termination Ignore State Example ............................................7-75

7-52 Extra Data Write Hold Example........................................................................7-77

8-1 General Exception Processing Flowchart ..........................................................8-2

8-2 General Form of Exception Stack Frame...........................................................8-3

8-3 Interrupt Recognition Examples.......................................................................8-13

8-4 Interrupt Exception Processing Flowchart........................................................8-15

8-5 Reset Exception Processing Flowchart............................................................8-16

8-6 Fault Status Long-Word Format.......................................................................8-22

9-1 JTAG Test Logic Block Diagram........................................................................9-3

9-2 JTAG Idcode Register Format............................................................................9-7

9-3 Output Pin Cell (O.Pin).......................................................................................9-8

9-4 Observe-Only Input Pin Cell (I.Obs)...................................................................9-8

9-5 Input Pin Cell (I.Pin) ...........................................................................................9-9

9-6 Output Control Cell (IO.Ctl)................................................................................9-9

9-7 General Arrangement of Bidirectional Pin Cells...............................................9-10

9-8 JTAG Bypass Register.....................................................................................9-15

9-9 Circuit Disabling IEEE Standard 1149.1...........................................................9-16

9-10 Debug Command Interface Schematic ............................................................9-25

9-11 Interface Timing................................................................................................9-26

9-12 Transition from JTAG to Debug Mode Timing Diagram...................................9-34

9-13 Transition from Debug to JTAG Mode Timing Diagram...................................9-35

11-1 Linear Voltage Regulator Solution....................................................................11-7

11-2 LTC1147 Voltage Regulator Solution...............................................................11-8

11-3 LTC1148 Voltage Regulator Solution...............................................................11-9

11-4 MAX767 Voltage Regulator Solution..............................................................11-10

11-5 MC68040 Address Hold Time........................................................................11-11

11-6 MC68060 Address Hold Time........................................................................11-12

11-7 MC68060 Address Hold Time Fix ..................................................................11-12

11-8 Simple CLK Generation..................................................................................11-14

11-9 Generic CLK Generation................................................................................11-14

11-10 MC68040 BCLK to CLKEN

Relationship........................................................11-15

11-11 DRAM Timing Analysis...................................................................................11-15

MOTOROLA

M68060 USER’S MANUAL

xxi

Page 20

List of Illustrations

12-12 Clock Input Timing Diagram.............................................................................12-3

12-13 Drive Levels and Test Points for AC Specifications......................................... 12-7

12-14 Reset Configuration Timing.............................................................................. 12-8

12-15 Read/Write Timing ...........................................................................................12-9

12-16 Bus Arbitration Timing....................................................................................12-10

12-17 Bus Arbitration Timing (Continued)................................................................ 12-11

12-18 CLA

Timing ....................................................................................................12-12

12-19 Snoop Timing................................................................................................. 12-13

12-20 Other Signals Timing...................................................................................... 12-14

13-1 PGA Package Dimensions (RC Suffix)............................................................13-4

13-2 QFP Package Dimensions (FE Suffix)............................................................. 13-5

C-1 Call-Out Dispatch Table Example......................................................................C-2

C-2 Example Pseudo-Assembly File ........................................................................C-3

C-3 Module Call-In, Call-Out Example......................................................................C-4

C-4 CAS and CAS2 Call-Outs and Entry Points.......................................................C-9

C-5 C-Code Representation of Integer Library Routines........................................C-10

C-6 MUL Instruction Call Example..........................................................................C-11

C-7 CMP2 Instruction Call Example .......................................................................C-11

C-8 SNAN/OPERR Exception Handler Pseudo-Code............................................C-18

C-9 Disabled vs. Enabled Exception Actions..........................................................C-20

C-10 _mem_read Pseudo-Code...............................................................................C-23

C-11 Register Usage of {i,d}mem_{read,write}_{b,w,l}.............................................C-25

C-12 Vector Table and M68060SP Relationship......................................................C-28

xxii

M68060 USER’S MANUAL

MOTOROLA

Page 21

LIST OF TABLES

1-1 Data Formats....................................................................................................1-14

1-2 Effective Addressing Modes.............................................................................1-15

1-3 Instruction Set Summary..................................................................................1-16

1-4 Notational Conventions....................................................................................1-21

2-1 Signal Index........................................................................................................2-1

2-2 Transfer-Type Encoding.....................................................................................2-4

2-3 Normal and MOVE16 Access TMx Encoding.....................................................2-5

2-4 Alternate Access TMx Encoding ........................................................................2-5

2-5 SIZx Encoding....................................................................................................2-6

2-6 Data Bus Byte Select Signals.............................................................................2-7

2-7 PSTx Encoding.................................................................................................2-14

2-8 Signal Summary...............................................................................................2-17

4-1 Updating U-Bit and M-Bit for Page Descriptors................................................4-20

4-2 SFC and DFC Values.......................................................................................4-20

5-1 TLNx Encoding.................................................................................................5-11

5-2 Instruction Cache Line State Transitions..........................................................5-15

5-3 Data Cache Line State Transitions...................................................................5-18

6-1 RND Encoding....................................................................................................6-4

6-2 PREC Encoding .................................................................................................6-4

6-3 MC68060 FPU Data Formats and Data Types ..................................................6-7

6-4 Single-Precision Real Format Summary............................................................6-8

6-5 Double-Precision Real Format Summary...........................................................6-9

6-6 Extended-Precision Real Format Summary.....................................................6-10

6-7 Packed Decimal Real Format Summary..........................................................6-11

6-8 Floating-Point Condition Code Encoding .........................................................6-16

6-9 Floating-Point Conditional Tests ......................................................................6-18

6-10 Floating-Point Exception Vectors.....................................................................6-19

6-11 Unimplemented Instructions.............................................................................6-20

6-12 Possible Operand Errors Exceptions ...............................................................6-27

6-13 Overflow Rounding Mode Values.....................................................................6-29

6-14 Underflow Rounding Mode Values...................................................................6-31

6-15 Possible Divide-by-Zero Exceptions.................................................................6-33

6-16 Rounding Mode Values....................................................................................6-34

7-1 Data Bus Requirements for Read and Write Cycles..........................................7-7

7-2 Summary of Access Types vs. Bus Signal Encoding.........................................7-9

7-3 Memory Alignment Influence on Noncachable and

Writethrough Bus Cycles..................................................................................7-12

7-4 Interrupt Acknowledge Termination Summary.................................................7-34

7-5 Termination Result Summary...........................................................................7-46

7-6 MC68040-Arbitration Protocol Transition Conditions.......................................7-55

MOTOROLA

M68060 USER’S MANUAL

xxiii

Page 22