Page 1

M68HC11E Family

Data Sheet

HC11

Microcontrollers

M68HC11E

Rev. 5.1

07/2005

freescale.com

Page 2

Page 3

MC68HC11E Family

Data Sheet

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be

the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document. For your

convenience, the page number designators have been linked to the appropriate location.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 3

Page 4

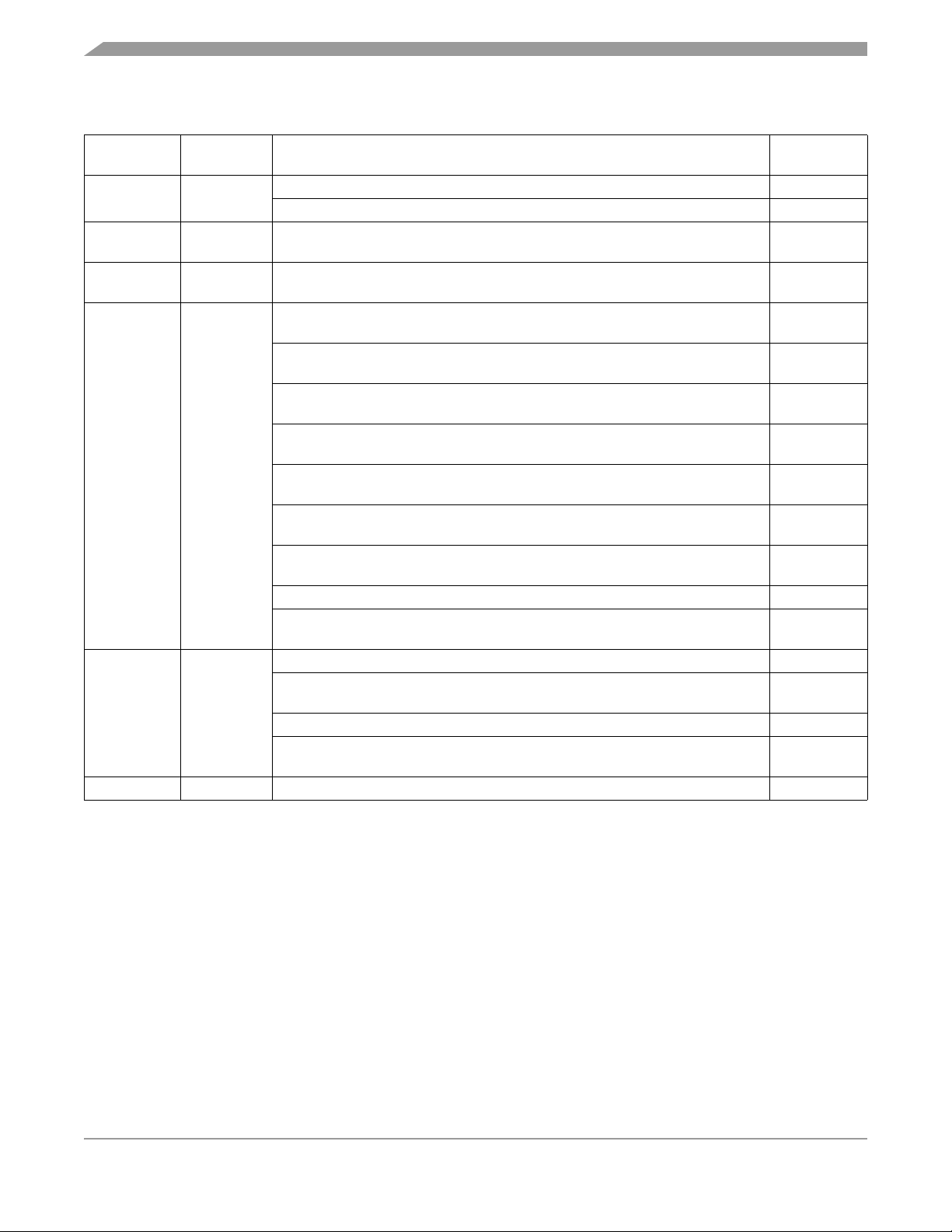

Revision History

Revision History

Date

May, 2001 3.1

June, 2001 3.2

December,

2001

July, 2002 4

June, 2003 5

July, 2005 5.1 Updated to meet Freescale identity guidelines. Throughout

Revision

Level

3.3

Description

2.3.3.1 System Configuration Register — Addition to NOCOP bit description 44

Added 10.21 EPROM Characteristics 175

10.21 EPROM Characteristics — For clarity, addition to note 2 following the

table

7.7.2 Serial Communications Control Register 1 — SCCR1 bit 4 (M)

description corrected

10.7 MC68L11E9/E20 DC Electrical Characteristics — Title changed to

include the MC68L11E20

10.8 MC68L11E9/E20 Supply Currents and Power Dissipation — Title

changed to include the MC68L11E20

10.10 MC68L11E9/E20 Control Timing — Title changed to include the

MC68L11E20

10.12 MC68L11E9/E20 Peripheral Port Timing — Title changed to include the

MC68L11E20

10.14 MC68L11E9/E20 Analog-to-Digital Converter Characteristics — Title

changed to include the MC68L11E20

10.16 MC68L11E9/E20 Expansion Bus Timing Characteristics — Title

changed to include the MC68L11E20

10.18 MC68L11E9/E20 Serial Peirpheral Interface Characteristics — Title

changed to include the MC68L11E20

— Title changed to include the MC68L11E20 175

11.4 Extended Voltage Device Ordering Information (3.0 Vdc to 5.5 Vdc) —

Updated table to include MC68L1120

Format updated to current publications standards Throughout

1.4.6 Non-Maskable Interrupt (XIRQ/VPPE) — Added Caution note pertaining

to EPROM programming of the MC68HC711E9 device only.

6.4 Port C — Clarified description of DDRC[7:0] bits 100

10.21 EPROM Characteristics — Added note pertaining to EPROM

programming of the MC68HC711E9 device only.

Page

Number(s)

175

110

153

154

157

163

167

169

172

181

23

175

M68HC11E Family Data Sheet, Rev. 5.1

4 Freescale Semiconductor

Page 5

List of Chapters

Chapter 1 General Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Chapter 2 Operating Modes and On-Chip Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Chapter 3 Analog-to-Digital (A/D) Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Chapter 4 Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Chapter 5 Resets and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Chapter 6 Parallel Input/Output (I/O) Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

Chapter 7 Serial Communications Interface (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

Chapter 8 Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Chapter 9 Timing Systems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

Chapter 10 Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

Chapter 11 Ordering Information and Mechanical Specifications . . . . . . . . . . . . . . . . . .177

Appendix A Development Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

Appendix B EVBU Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

AN1060 — M68HC11 Bootstrap Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

EB184 — Enabling the Security Feature on the MC68HC711E9 Devices

with PCbug11 on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

EB188 — Enabling the Security Feature on M68HC811E2 Devices

with PCbug11 on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

EB296 — Programming MC68HC711E9 Devices with PCbug11

and the M68HC11EVBU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 5

Page 6

List of Chapters

M68HC11E Family Data Sheet, Rev. 5.1

6 Freescale Semiconductor

Page 7

Table of Contents

Chapter 1

General Description

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.3 Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.4 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.4.1 V

1.4.2 RESET

1.4.3 Crystal Driver and External Clock Input (XTAL and EXTAL) . . . . . . . . . . . . . . . . . . . . . . . . 22

1.4.4 E-Clock Output (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.4.5 Interrupt Request (IRQ

1.4.6 Non-Maskable Interrupt (XIRQ

1.4.7 MODA and MODB (MODA/LIR

1.4.7.1 V

1.4.8 STRA/AS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.4.9 STRB/R/W

1.4.10 Port Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.4.10.1 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.4.10.2 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4.10.3 Port C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4.10.4 Port D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

1.4.10.5 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

and VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

DD

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

/V

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

PPE

and MODB/V

and VRH. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

RL

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

STBY

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Chapter 2

Operating Modes and On-Chip Memory

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.2 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.2.1 Single-Chip Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.2.2 Expanded Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.2.3 Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.2.4 Bootstrap Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.3 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.3.1 RAM and Input/Output Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.3.2 Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.3.3 System Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.3.3.1 System Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.3.3.2 RAM and I/O Mapping Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

2.3.3.3 System Configuration Options Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.4 EPROM/OTPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.4.1 Programming an Individual EPROM Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.4.2 Programming the EPROM with Downloaded Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 7

Page 8

Table of Contents

2.4.3 EPROM and EEPROM Programming Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

2.5 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.5.1 EEPROM and CONFIG Programming and Erasure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.5.1.1 Block Protect Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.5.1.2 EPROM and EEPROM Programming Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 53

2.5.1.3 EEPROM Bulk Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

2.5.1.4 EEPROM Row Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

2.5.1.5 EEPROM Byte Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

2.5.1.6 CONFIG Register Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

2.5.2 EEPROM Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Chapter 3

Analog-to-Digital (A/D) Converter

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.2.1 Multiplexer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.2.2 Analog Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.2.3 Digital Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.2.4 Result Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.2.5 A/D Converter Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.2.6 Conversion Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.3 A/D Converter Power-Up and Clock Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.4 Conversion Process. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.5 Channel Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.6 Single-Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.7 Multiple-Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

3.8 Operation in Stop and Wait Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

3.9 A/D Control/Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

3.10 A/D Converter Result Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Chapter 4

Central Processor Unit (CPU)

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.2 CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.2.1 Accumulators A, B, and D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.2.2 Index Register X (IX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.2.3 Index Register Y (IY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.2.4 Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.2.5 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.2.6 Condition Code Register (CCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.2.6.1 Carry/Borrow (C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.2.6.2 Overflow (V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.2.6.3 Zero (Z). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.2.6.4 Negative (N) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.2.6.5 Interrupt Mask (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.2.6.6 Half Carry (H) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.2.6.7 X Interrupt Mask (X) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.2.6.8 STOP Disable (S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

M68HC11E Family Data Sheet, Rev. 5.1

8 Freescale Semiconductor

Page 9

4.3 Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.4 Opcodes and Operands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.5 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.5.1 Immediate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.5.2 Direct . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.5.3 Extended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.5.4 Indexed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.5.5 Inherent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.5.6 Relative . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.6 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Chapter 5

Resets and Interrupts

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.2 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.2.1 Power-On Reset (POR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.2.2 External Reset (RESET

5.2.3 Computer Operating Properly (COP) Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.2.4 Clock Monitor Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.2.5 System Configuration Options Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.2.6 Configuration Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3 Effects of Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3.1 Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3.3 Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3.4 Real-Time Interrupt (RTI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3.5 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3.6 Computer Operating Properly (COP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3.7 Serial Communications Interface (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3.8 Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3.9 Analog-to-Digital (A/D) Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.3.10 System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.4 Reset and Interrupt Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.4.1 Highest Priority Interrupt and Miscellaneous Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

5.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.5.1 Interrupt Recognition and Register Stacking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

5.5.2 Non-Maskable Interrupt Request (XIRQ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.5.3 Illegal Opcode Trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.5.4 Software Interrupt (SWI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.5.5 Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.5.6 Reset and Interrupt Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.6 Low-Power Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.6.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.6.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 9

Page 10

Table of Contents

Chapter 6

Parallel Input/Output (I/O) Ports

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

6.2 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.3 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.4 Port C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.5 Port D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

6.6 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

6.7 Handshake Protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

6.8 Parallel I/O Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Chapter 7

Serial Communications Interface (SCI)

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.2 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.3 Transmit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.4 Receive Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

7.5 Wakeup Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

7.5.1 Idle-Line Wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

7.5.2 Address-Mark Wakeup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

7.6 SCI Error Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

7.7 SCI Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

7.7.1 Serial Communications Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

7.7.2 Serial Communications Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

7.7.3 Serial Communications Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.7.4 Serial Communication Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.7.5 Baud Rate Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

7.8 Status Flags and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

7.9 Receiver Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Chapter 8

Serial Peripheral Interface (SPI)

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

8.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

8.3 SPI Transfer Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

8.4 Clock Phase and Polarity Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

8.5 SPI Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

8.5.1 Master In/Slave Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

8.5.2 Master Out/Slave In . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

8.5.3 Serial Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

8.5.4 Slave Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

8.6 SPI System Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

8.7 SPI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

8.7.1 Serial Peripheral Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

8.7.2 Serial Peripheral Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

8.7.3 Serial Peripheral Data I/O Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

M68HC11E Family Data Sheet, Rev. 5.1

10 Freescale Semiconductor

Page 11

Chapter 9

Timing Systems

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

9.2 Timer Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

9.3 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

9.3.1 Timer Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

9.3.2 Timer Input Capture Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

9.3.3 Timer Input Capture 4/Output Compare 5 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

9.4 Output Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

9.4.1 Timer Output Compare Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

9.4.2 Timer Compare Force Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

9.4.3 Output Compare Mask Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

9.4.4 Output Compare Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

9.4.5 Timer Counter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

9.4.6 Timer Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

9.4.7 Timer Interrupt Mask 1 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

9.4.8 Timer Interrupt Flag 1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

9.4.9 Timer Interrupt Mask 2 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

9.4.10 Timer Interrupt Flag Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

9.5 Real-Time Interrupt (RTI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

9.5.1 Timer Interrupt Mask Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

9.5.2 Timer Interrupt Flag Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

9.5.3 Pulse Accumulator Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

9.6 Computer Operating Properly (COP) Watchdog Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

9.7 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

9.7.1 Pulse Accumulator Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

9.7.2 Pulse Accumulator Count Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

9.7.3 Pulse Accumulator Status and Interrupt Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Chapter 10

Electrical Characteristics

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

10.2 Maximum Ratings for Standard and Extended Voltage Devices . . . . . . . . . . . . . . . . . . . . . . . 149

10.3 Functional Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

10.4 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

10.5 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

10.6 Supply Currents and Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

10.7 MC68L11E9/E20 DC Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

10.8 MC68L11E9/E20 Supply Currents and Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

10.9 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

10.10 MC68L11E9/E20 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

10.11 Peripheral Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

10.12 MC68L11E9/E20 Peripheral Port Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

10.13 Analog-to-Digital Converter Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

10.14 MC68L11E9/E20 Analog-to-Digital Converter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 167

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 11

Page 12

Table of Contents

10.15 Expansion Bus Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

10.16 MC68L11E9/E20 Expansion Bus Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

10.17 Serial Peripheral Interface Timing Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

10.18 MC68L11E9/E20 Serial Peirpheral Interface Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 172

10.19 EEPROM Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

10.20 MC68L11E9/E20 EEPROM Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

10.21 EPROM Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Chapter 11

Ordering Information and Mechanical Specifications

11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

11.2 Standard Device Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

11.3 Custom ROM Device Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

11.4 Extended Voltage Device Ordering Information (3.0 Vdc to 5.5 Vdc) . . . . . . . . . . . . . . . . . . . 181

11.5 52-Pin Plastic-Leaded Chip Carrier (Case 778). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

11.6 52-Pin Windowed Ceramic-Leaded Chip Carrier (Case 778B) . . . . . . . . . . . . . . . . . . . . . . . . 183

11.7 64-Pin Quad Flat Pack (Case 840C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

11.8 52-Pin Thin Quad Flat Pack (Case 848D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

11.9 56-Pin Dual in-Line Package (Case 859). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

11.10 48-Pin Plastic DIP (Case 767) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Appendix A

Development Support

A.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

A.2 M68HC11 E-Series Development Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

A.3 EVS — Evaluation System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

A.4 Modular Development System (MMDS11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

A.5 SPGMR11 — Serial Programmer for M68HC11 MCUs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Appendix B

EVBU Schematic

AN1060 — M68HC11 Bootstrap Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

EB184 — Enabling the Security Feature on the MC68HC711E9 Devices with PCbug11 on the

M68HC711E9PGMR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

EB188 — Enabling the Security Feature on M68HC811E2 Devices

with PCbug11 on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

EB296 — Programming MC68HC711E9 Devices with PCbug11

and the M68HC11EVBU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

M68HC11E Family Data Sheet, Rev. 5.1

12 Freescale Semiconductor

Page 13

Chapter 1 General Description

1.1 Introduction

This document contains a detailed description of the M68HC11 E series of 8-bit microcontroller units

(MCUs). These MCUs all combine the M68HC11 central processor unit (CPU) with high-performance,

on-chip peripherals.

The E series is comprised of many devices with various configurations of:

• Random-access memory (RAM)

• Read-only memory (ROM)

• Erasable programmable read-only memory (EPROM)

• Electrically erasable programmable read-only memory (EEPROM)

• Several low-voltage devices are also available.

With the exception of a few minor differences, the operation of all E-series MCUs is identical. A fully static

design and high-density complementary metal-oxide semiconductor (HCMOS) fabrication process allow

the E-series devices to operate at frequencies from 3 MHz to dc with very low power consumption.

1.2 Features

Features of the E-series devices include:

• M68HC11 CPU

• Power-saving stop and wait modes

• Low-voltage devices available (3.0–5.5 Vdc)

• 0, 256, 512, or 768 bytes of on-chip RAM, data retained during standby

• 0, 12, or 20 Kbytes of on-chip ROM or EPROM

• 0, 512, or 2048 bytes of on-chip EEPROM with block protect for security

• 2048 bytes of EEPROM with selectable base address in the MC68HC811E2

• Asynchronous non-return-to-zero (NRZ) serial communications interface (SCI)

• Additional baud rates available on MC68HC(7)11E20

• Synchronous serial peripheral interface (SPI)

• 8-channel, 8-bit analog-to-digital (A/D) converter

• 16-bit timer system:

– Three input capture (IC) channels

– Four output compare (OC) channels

– One additional channel, selectable as fourth IC or fifth OC

• 8-bit pulse accumulator

• Real-time interrupt circuit

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 13

Page 14

General Description

• Computer operating properly (COP) watchdog system

• 38 general-purpose input/output (I/O) pins:

– 16 bidirectional I/O pins

– 11 input-only pins

– 11 output-only pins

• Several packaging options:

– 52-pin plastic-leaded chip carrier (PLCC)

– 52-pin windowed ceramic leaded chip carrier (CLCC)

– 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

– 64-pin quad flat pack (QFP)

– 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

– 56-pin plastic shrink dual in-line package, .070-inch lead spacing (SDIP)

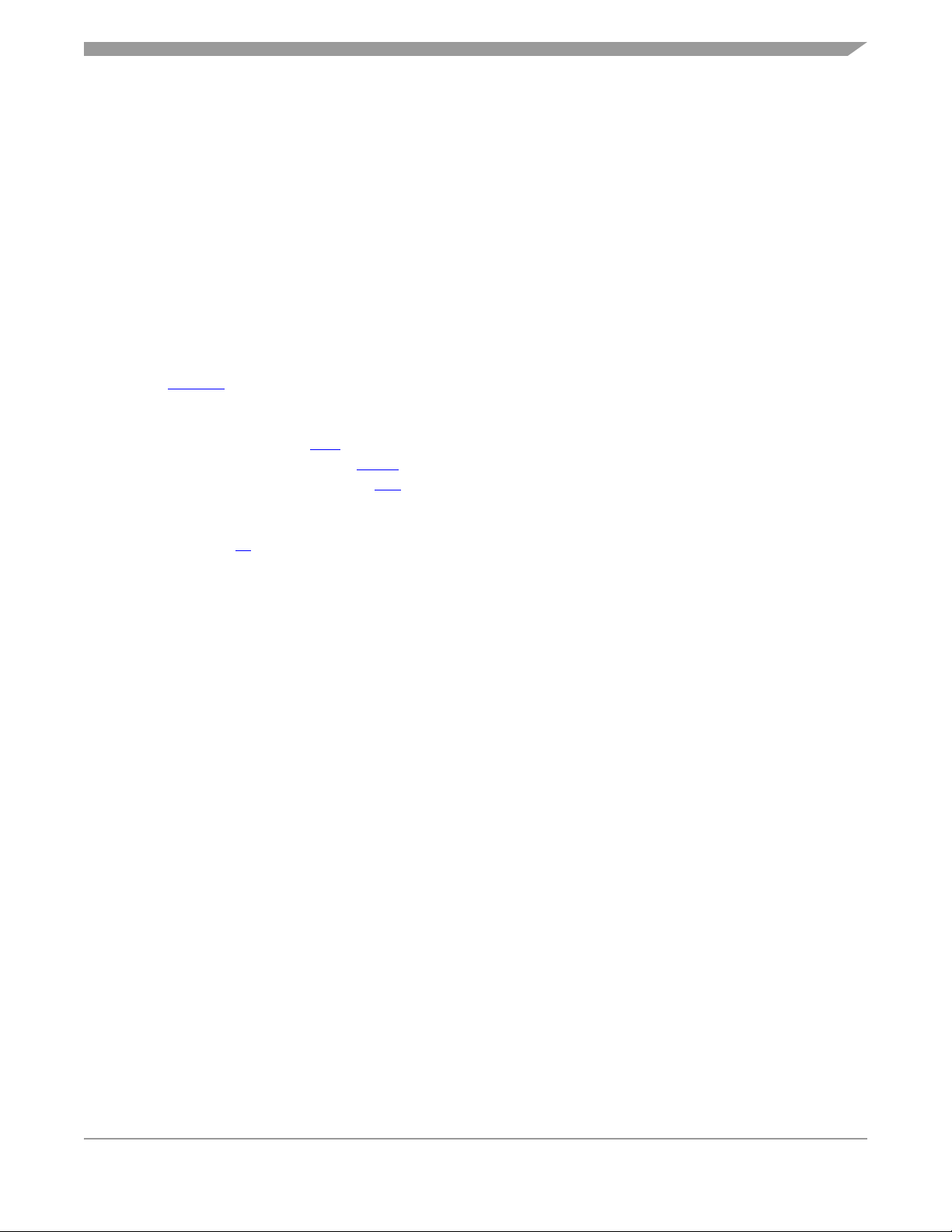

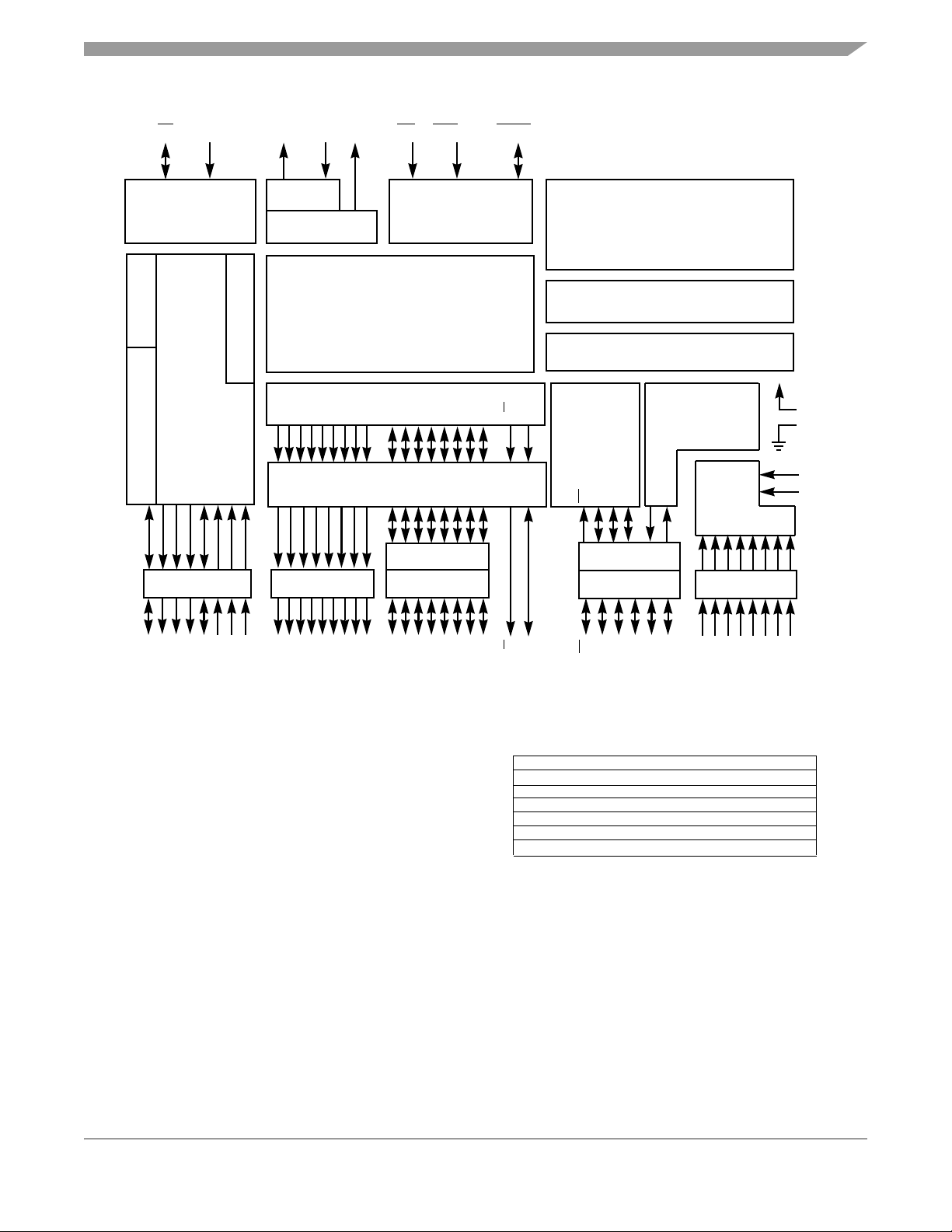

1.3 Structure

See Figure 1-1 for a functional diagram of the E-series MCUs. Differences among devices are noted in

the table accompanying Figure 1-1.

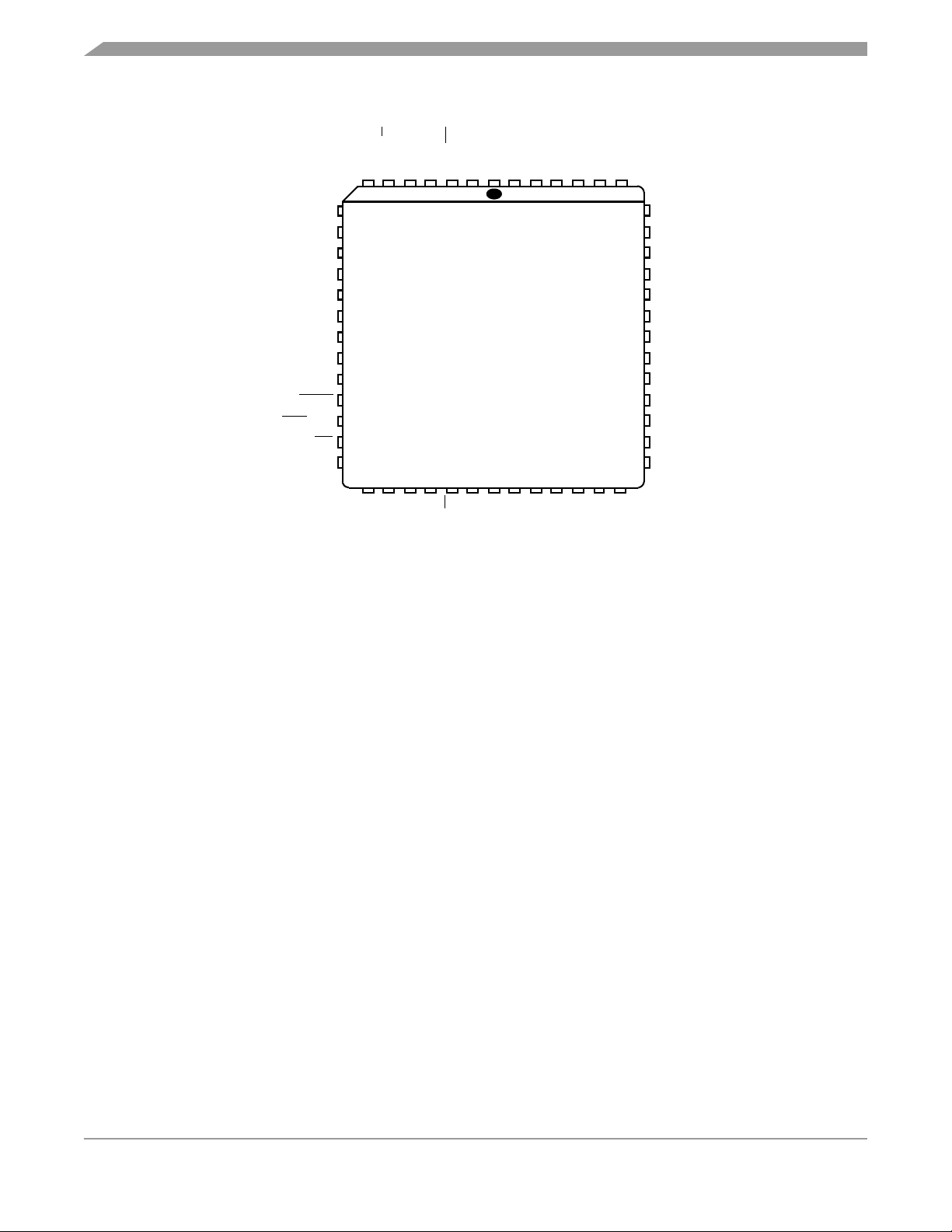

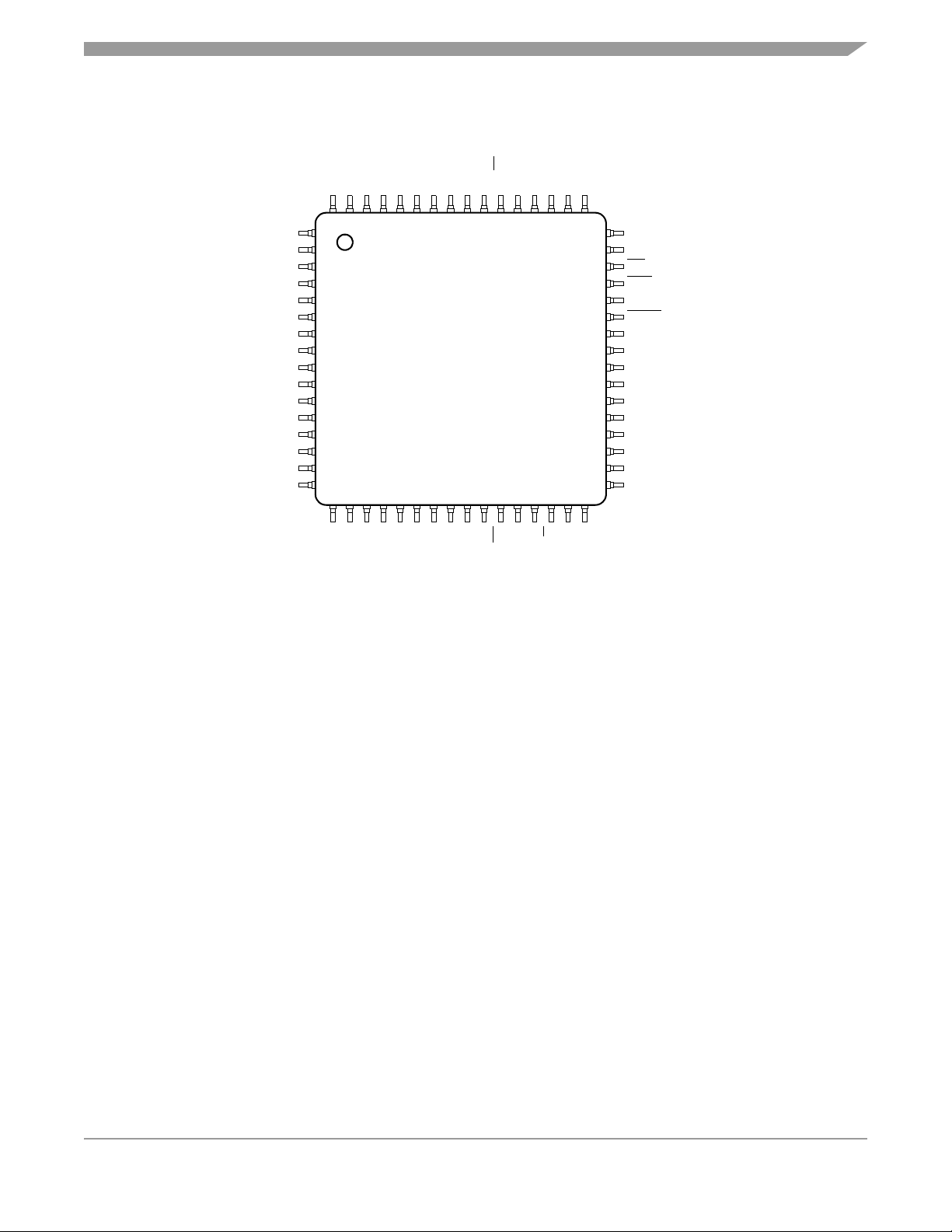

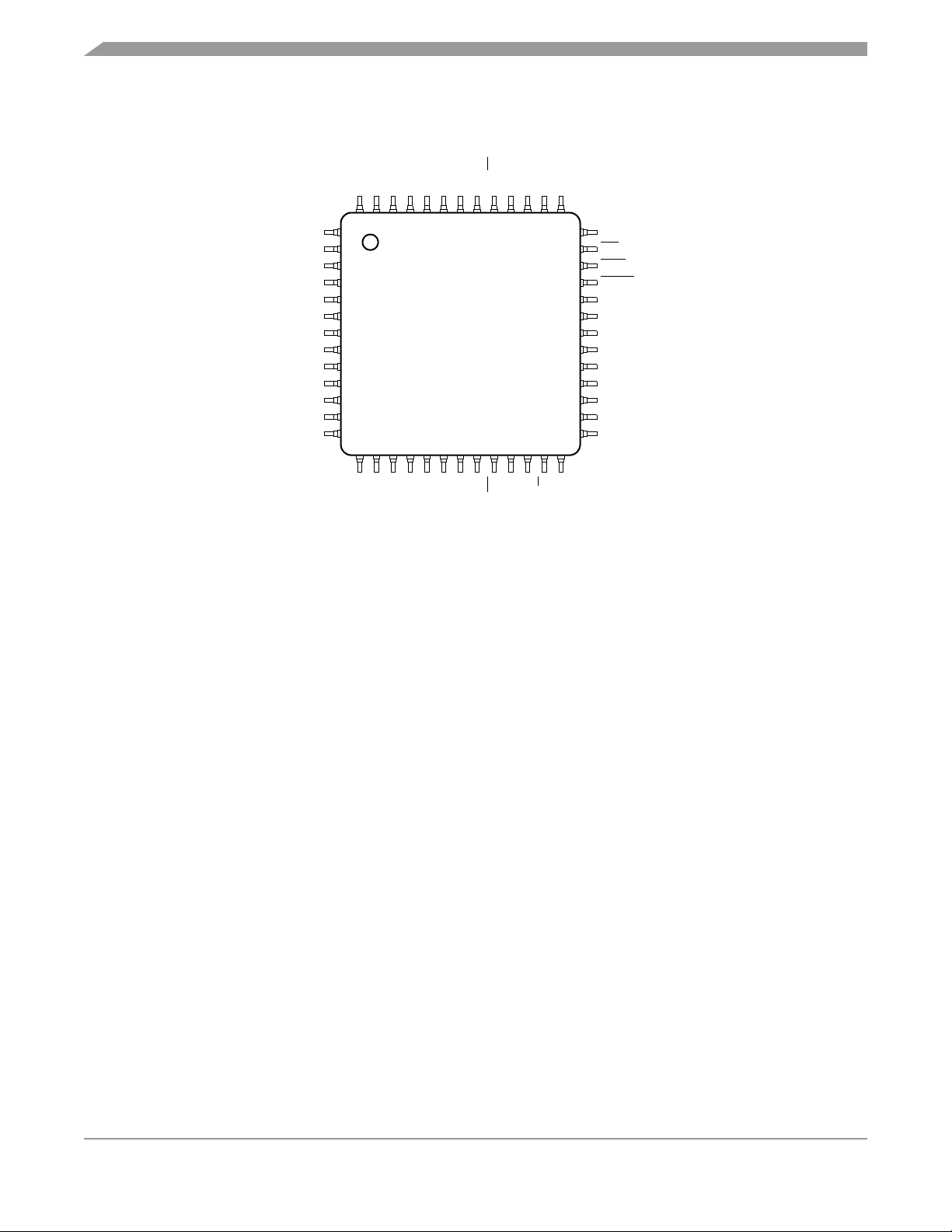

1.4 Pin Descriptions

M68HC11 E-series MCUs are available packaged in:

• 52-pin plastic-leaded chip carrier (PLCC)

• 52-pin windowed ceramic leaded chip carrier (CLCC)

• 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

• 64-pin quad flat pack (QFP)

• 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

• 56-pin plastic shrink dual in-line package, .070-inch lead spacing (SDIP)

Most pins on these MCUs serve two or more functions, as described in the following paragraphs. Refer

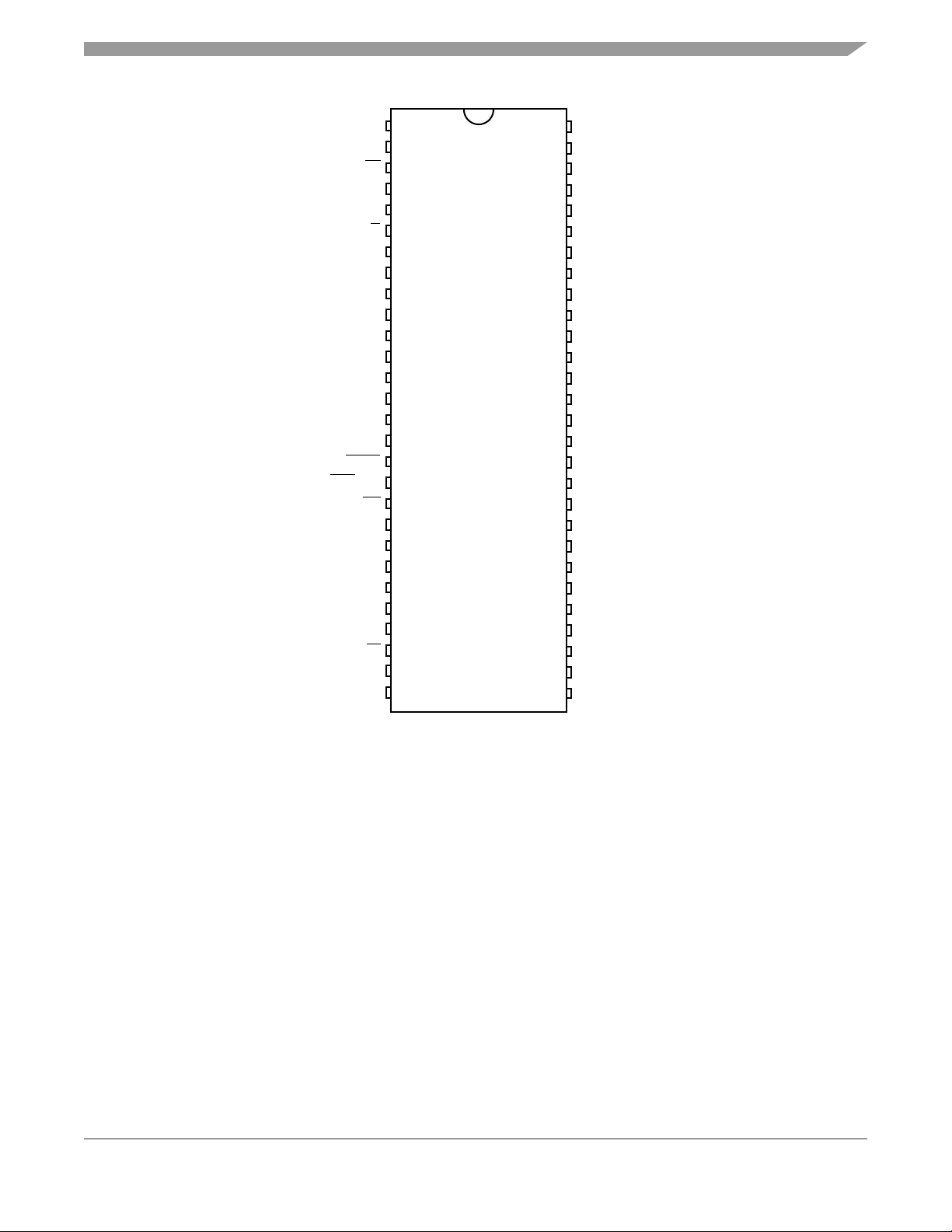

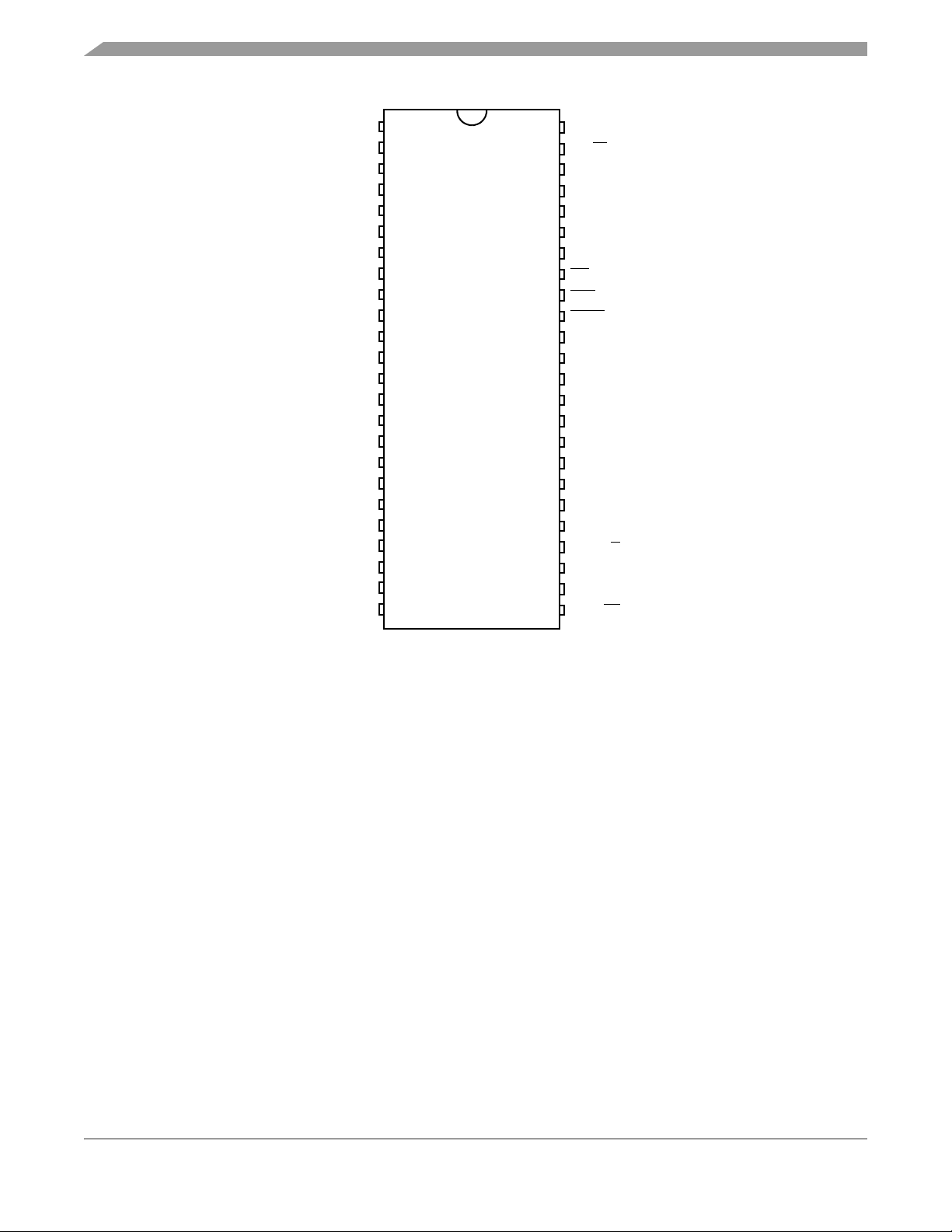

to Figure 1-2, Figure 1-3, Figure 1-4, Figure 1-5, and Figure 1-6 which show the M68HC11 E-series pin

assignments for the PLCC/CLCC, QFP, TQFP, SDIP, and DIP packages.

M68HC11E Family Data Sheet, Rev. 5.1

14 Freescale Semiconductor

Page 15

MODA/

LIR

MODB/

V

STBY

XTAL EXTAL E IRQ XIRQ/V

PPE*

Pin Descriptions

RESET

MODE CONTROL

TIMER

SYSTEM

COPPULSE ACCUMULATOR

OC2

OC3

OC4

PAI

OC5/IC4/OC1

PORT A

PERIODIC INTERRUPT

IC1

IC2

IC3

OSC

CLOCK LOGIC

BUS EXPANSION

ADDRESS

STROBE AND HANDSHAKE

PORT B

M68HC11 CPU

ADDRESS/DATA

PARALLEL I/O

CONTROL

PORT C

INTERRUPT

LOGIC

R/W

STRB

STRA

AS

SERIAL

PERIPHERAL

INTERFACE

SPI

SCK

SS

CONTROL

PORT D

ROM OR EPROM

(SEE TABLE)

EEPROM

(SEE TABLE)

RAM

(SEE TABLE)

COMMUNICATION

INTERFACE

MOSI

MISO

TxD

RxD

SERIAL

SCI

A/D CONVERTER

PORT E

V

DD

V

SS

V

RH

V

RL

PA2/IC1

PA1/IC2

PA7/PAI

PA6/OC2/OC1

PA5/OC3/OC1

PA4/OC4/OC1

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PA3/OC5/IC4/OC1

* V

applies only to devices with EPROM/OTPROM.

PPE

Figure 1-1. M68HC11 E-Series Block Diagram

PD5/SS

STRA/AS

PC1/ADDR1/DATA1

STRB/R/W

PC0/ADDR0/DATA0

PB1/ADDR9

PB5/ADDR13

PB4/ADDR12

PB0/ADDR8

PB3/ADDR11

PB2/ADDR10

PC7/ADDR7/DATA7

PC6/ADDR6/DATA6

PC5/ADDR5/DATA5

PC4/ADDR4/DATA4

PC3/ADDR3/DATA3

PC2/ADDR2/DATA2

PD4/SCK

DEVICE

MC68HC11E0

MC68HC11E1

MC68HC11E9

MC68HC711E9

MC68HC11E20

MC68HC711E20

PD3/MOSI

RAM

512

512

512

512

768

768

PD2/MISO

PD1/TxD

PD0/RxD

ROM

—

—

12 K

—

20 K

—

PE7/AN7

PE6/AN6

EPROM

—

—

—

12 K

—

20 K

PE5/AN5

PE4/AN4

PE3/AN3

EEPROM

PE2/AN2

—

512

512

512

512

512

PE1/AN1

PE0/AN0

256 — — 2048MC68HC811E2

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 15

Page 16

General Description

STBY

EXTAL

STRB/R/WESTRA/AS

7

6

XTAL

8

PC0/ADDR0/DATA0

PC1/ADDR1/DATA1

PC2/ADDR2/DATA2

PC3/ADDR3/DATA3

PC4/ADDR4/DATA4

PC5/ADDR5/DATA5

PC6/ADDR6/DATA6

PC7/ADDR7/DATA7

RESET

* XIRQ/V

PD0/RxD

* V

applies only to devices with EPROM/OTPROM.

PPE

PPE

IRQ

9

10

11

12

13

14

15

16

17

18

19

20

2122232425262728293031

PD1/TxD

PD2/MISO

MODA/LIR

MODB/V

VSSVRHVRLPE7/AN7

5

4

312

M68HC11 E SERIES

DD

V

PD5/SS

PD4/SCK

PD3/MOSI

52

PA7/PAI/OC1

PA6/OC2/OC1

PE3/AN3

51

50

49

PA5/OC3/OC1

PA4/OC4/OC1

PA3/OC5/IC4/OC1

PE6/AN648PE2/AN2

47

45

44

43

42

41

40

39

38

37

36

35

34

33

PA2/IC132PA1/IC2

PE5/AN546

PE1/AN1

PE4/AN4

PE0/AN0

PB0/ADDR8

PB1/ADDR9

PB2/ADDR10

PB3/ADDR11

PB4/ADDR12

PB5/ADDR13

PB6/ADDR14

PB7/ADDR15

PA0/IC3

Figure 1-2. Pin Assignments for 52-Pin PLCC and CLCC

M68HC11E Family Data Sheet, Rev. 5.1

16 Freescale Semiconductor

Page 17

Pin Descriptions

PA1/IC2

PA2/IC1

PA0/IC3

NC

NC

NC

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

PB2/ADDR10

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE4/AN4

PE1/AN1

PE5/AN5

PA3/OC5/IC4/OC1NCNC

64

63626160595857

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

PA4/OC4/OC1

PA5/OC3/OC1

M68HC11 E SERIES

17181920212223

RL

RH

V

VSSV

V

PE2/AN2

PE6/AN6

PE3/AN3

PE7/AN7

1. V

applies only to devices with EPROM/OTPROM.

PPE

Figure 1-3. Pin Assignments for 64-Pin QFP

PA6/OC2/OC1

PA7/PAI/OC1

PD5/SS

VDDPD4/SCK

55

56

54

26

25

STBY

MODB/V

27

NC

MODA/LIR

24

SS

PD3/MOSI

PD2/MISO

PD1/TxD

V

5352515049

2829303132

E

STRA/AS

EXTAL

STRB/R/W

SS

NC

48

PD0/RxD

47

IRQ

46

45

XIRQ/V

NC

44

RESET

43

PC7/ADDR7/DATA7

42

PC6/ADDR6/DATA6

41

PC5/ADDR5/DATA5

40

PC4/ADDR4/DATA4

39

PC3/ADDR3/DATA3

38

37

PC2/ADDR2/DATA2

36

PC1/ADDR1/DATA1

35

NC

34

PC0/ADDR0/DATA0

33

XTAL

NC

PPE

(1)

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 17

Page 18

General Description

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

PB2/ADDR10

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE4/AN4

PE1/AN1

PE5/AN5

PA1/IC2

PA2/IC1

PA3/OC5/IC4/OC1

PA4/OC4/OC1

PA5/OC3/OC1

PA6/OC2/OC1

PA7/PAI/OC1

52

51504948474645

1

2

3

4

5

6

7

M68HC11 E SERIES

8

9

10

11

12

13

1415161718192021222423

PD5/SS

VDDPD4/SCK

44

PD3/MOSI

PD2/MISO

PD1/TxD

42

43

41

40

PD0/RxD

39

IRQ

38

XIRQ/V

37

36

RESET

35

PC7/ADDR7/DATA7

PC6/ADDR6/DATA6

34

PC5/ADDR5/DATA5

33

32

PC4/ADDR4/DATA4

31

PC3/ADDR3/DATA3

PC2/ADDR2/DATA2

30

PC1/ADDR1/DATA1

29

28

PC0/ADDR0/DATA0

27

25

XTAL

26

PPE

(1)

RL

SS

RH

V

V

V

PE2/AN2

PE6/AN6

PE3/AN3

PE7/AN7

1. V

applies only to devices with EPROM/OTPROM.

PPE

STBY

MODB/V

E

STRA/AS

MODA/LIR

EXTAL

STRB/R/W

Figure 1-4. Pin Assignments for 52-Pin TQFP

M68HC11E Family Data Sheet, Rev. 5.1

18 Freescale Semiconductor

Page 19

Pin Descriptions

V

MODB/V

STBY

MODA/LIR

STRA/AS

STRB/R/W

EXTAL

XTAL

PC0/ADDR0/DATA0

PC1/ADDR1/DATA1

PC2/ADDR2/DATA2

PC3/ADDR3/DATA3

PC4/ADDR4/DATA4

PC5/ADDR5/DATA5

PC6/ADDR6/DATA6

PC7/ADDR7/DATA7

RESET

* XIRQ/V

PPE

IRQ

PD0/RxD

EV

SS

PD1/TxD

PD2/MISO

PD3/MOSI

PD4/SCK

PD5/SS

V

DD

V

SS

SS

1

2

3

4

E

5

6

7

8

9

10

11

12

13

14

15

M68HC11 E SERIES

16

17

18

19

20

21

22

23

24

25

26

27

28

EV

56

SS

V

RH

55

V

54

RL

PE7/AN7

53

PE3/AN3

52

PE6/AN6

51

PE2/AN2

50

PE5/AN5

49

PE1/AN1

48

PE4/AN4

47

PE0/AN0

46

PB0/ADDR8

45

PB1/ADDR9

44

PB2/ADDR10

43

PB3/ADDR11

42

PB4/ADDR12

41

PB5/ADDR13

40

PB6/ADDR14

39

PB7/ADDR15

38

PA0/IC3

37

PA1/IC2

36

PA2/IC1

35

PA3/OC5/IC4/OC1

34

PA4/OC4/OC1

33

PA5/OC3/OC1

32

PA6/OC2/OC1

31

PA7/PAI/OC1

30

EV

29

DD

* V

applies only to devices with EPROM/OTPROM.

PPE

Figure 1-5. Pin Assignments for 56-Pin SDIP

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 19

Page 20

General Description

PA7/PAI/OC1

PA6/OC2/OC1

PA5/OC3/OC1

PA4/OC4/OC1

PA3/OC5/IC4/OC1

PA2/IC1

PA1/IC2

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

PB2/ADDR10

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE1/AN1

PE2/AN2

PE3/AN3

V

V

RH

V

SS

MODB/V

STBY

V

1

2

3

4

5

6

7

8

9

10

11

MC68HC811E2

12

13

14

15

16

17

18

19

20

21

RL

22

23

24

48

DD

PD5/SS

47

PD4/SCK46

PD3/MOSI

45

PD2/MISO44

PD1/TxD

43

PD0/RxD42

IRQ

41

XIRQ

40

RESET

39

PC7/ADDR7/DATA7

38

PC6/ADDR6/DATA6

37

PC5/ADDR5/DATA5

36

PC4/ADDR4/DATA4

35

PC3/ADDR3/DATA3

34

PC2/ADDR2/DATA2

33

PC1/ADDR1/DATA1

32

PC0/ADDR0/DATA0

31

XTAL

30

EXTAL

29

STRB/R/W

28

E27

STRA/AS26

25

MODA/LIR

Figure 1-6. Pin Assignments for 48-Pin DIP (MC68HC811E2)

M68HC11E Family Data Sheet, Rev. 5.1

20 Freescale Semiconductor

Page 21

Pin Descriptions

1.4.1 VDD and VSS

Power is supplied to the MCU through VDD and VSS. VDD is the power supply, VSS is ground. The MCU

operates from a single 5-volt (nominal) power supply. Low-voltage devices in the E series operate at

3.0–5.5 volts.

Very fast signal transitions occur on the MCU pins. The short rise and fall times place high, short duration

current demands on the power supply. To prevent noise problems, provide good power supply bypassing

at the MCU. Also, use bypass capacitors that have good

high-frequency characteristics and situate them as close to the MCU as possible. Bypass requirements

vary, depending on how heavily the MCU pins are loaded.

MANUAL

RESET SWITCH

4.7 kΩ

V

DD

2

IN

RESET

MC34(0/1)64

GND

3

V

DD

4.7 kΩ

1

TO RESET

OF M68HC11

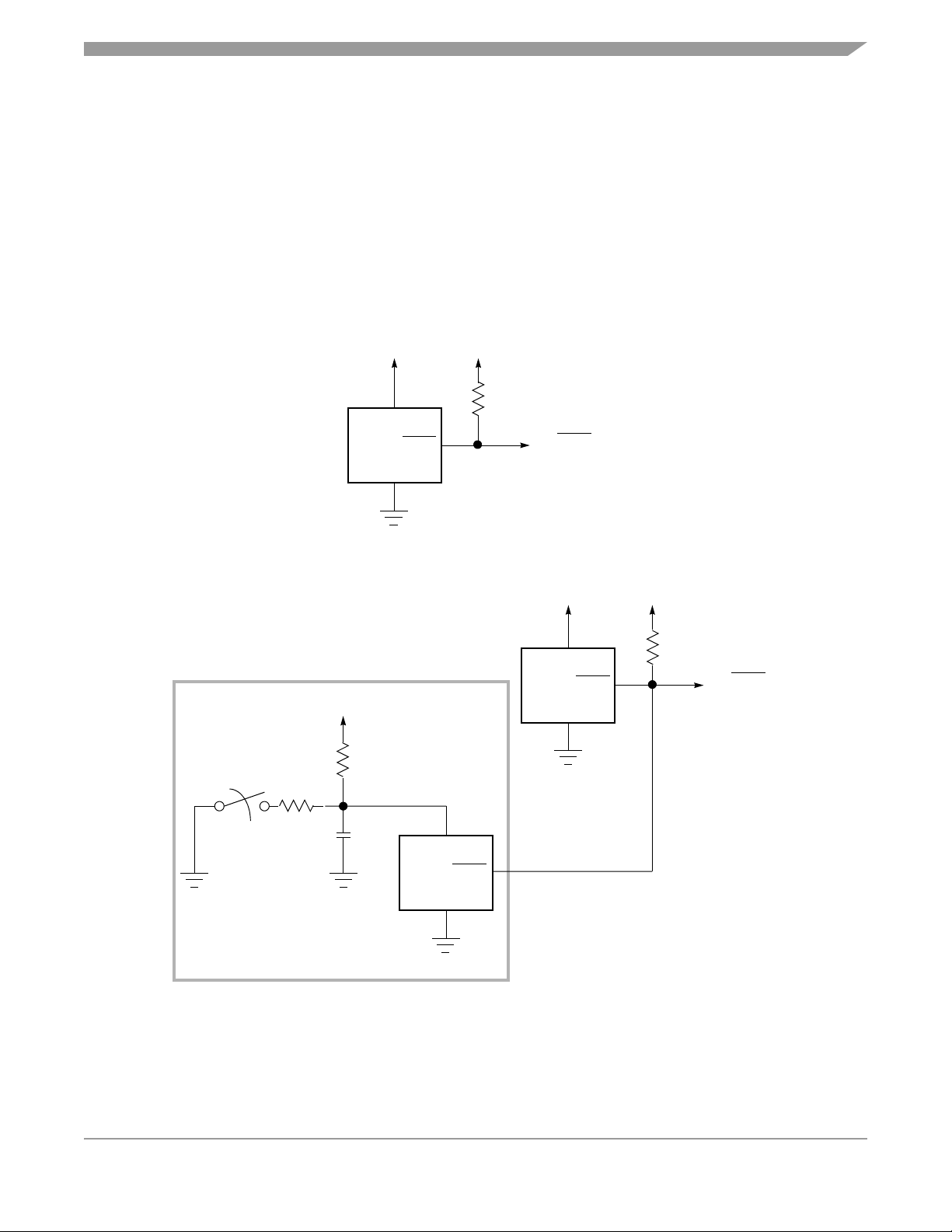

Figure 1-7. External Reset Circuit

V

DD

IN

RESET

V

DD

4.7 kΩ

MC34064

GND

V

DD

4.7 kΩ

TO RESET

OF M68HC11

1.0 µF

IN

RESET

MC34164

GND

OPTIONAL POWER-ON DELAY AND MANUAL RESET SWITCH

Figure 1-8. External Reset Circuit with Delay

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 21

Page 22

General Description

1.4.2 RESET

A bidirectional control signal, RESET, acts as an input to initialize the MCU to a known startup state. It

also acts as an open-drain output to indicate that an internal failure has been detected in either the clock

monitor or computer operating properly (COP) watchdog circuit. The CPU distinguishes between internal

and external reset conditions by sensing whether the reset pin rises to a logic 1 in less than two E-clock

cycles after a reset has occurred. See Figure 1-7 and Figure 1-8.

CAUTION

Do not connect an external resistor capacitor (RC) power-up delay circuit

to the reset pin of M68HC11 devices because the circuit charge time

constant can cause the device to misinterpret the type of reset that

occurred.

Because the CPU is not able to fetch and execute instructions properly when V

falls below the minimum

DD

operating voltage level, reset must be controlled. A low-voltage inhibit (LVI) circuit is required primarily for

protection of EEPROM contents. However, since the configuration register (CONFIG) value is read from

the EEPROM, protection is required even if the EEPROM array is not being used.

Presently, there are several economical ways to solve this problem. For example, two good external

components for LVI reset are:

1. The Seiko S0854HN (or other S805 series devices):

a. Extremely low power (2 µA)

a. TO-92 package

a. Limited temperature range, –20°C to +70°C

a. Available in various trip-point voltage ranges

2. The Freescale MC34064:

a. TO-92 or SO-8 package

a. Draws about 300 µA

a. Temperature range –40°C to 85°C

a. Well controlled trip point

a. Inexpensive

Refer to Chapter 5 Resets and Interrupts for further information.

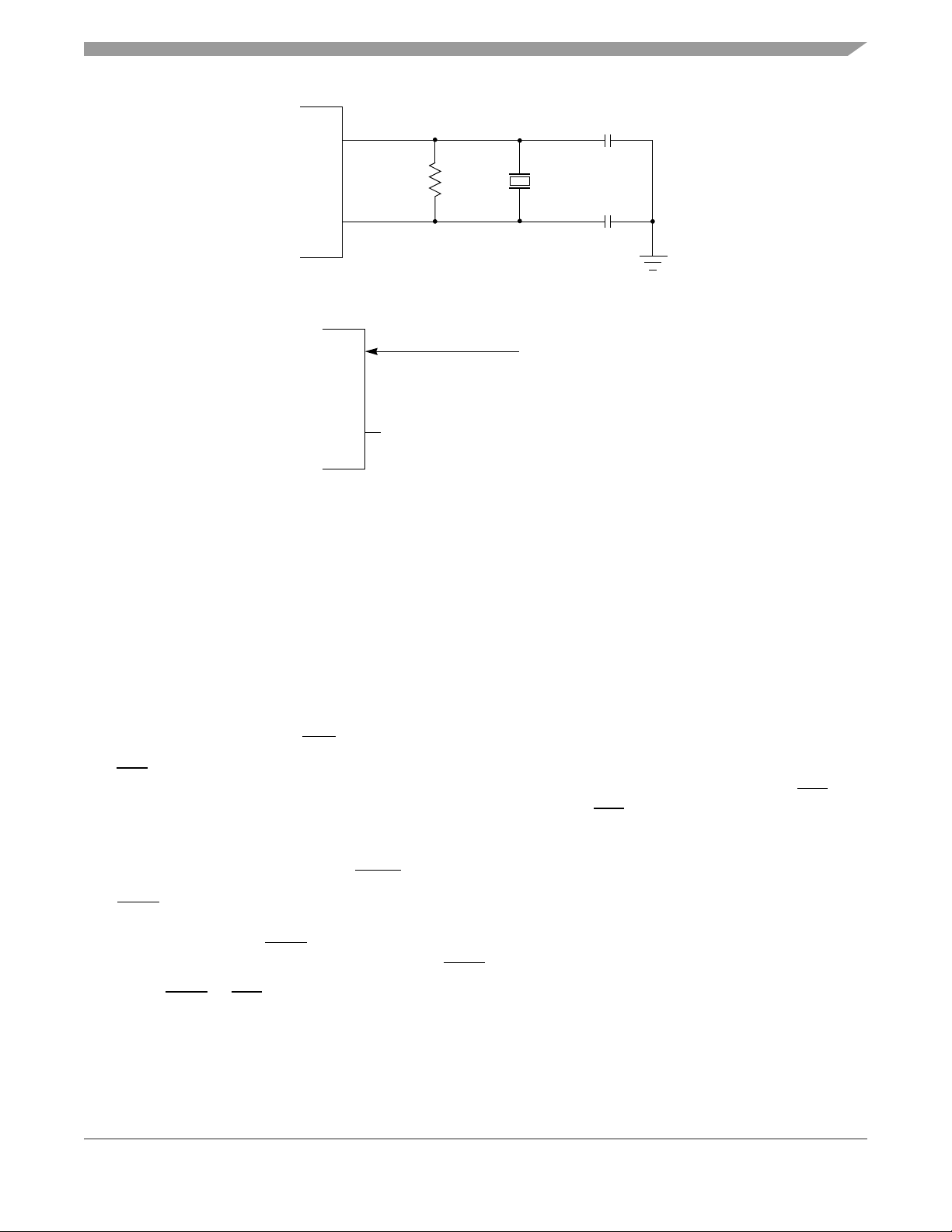

1.4.3 Crystal Driver and External Clock Input (XTAL and EXTAL)

These two pins provide the interface for either a crystal or a CMOS- compatible clock to control the

internal clock generator circuitry. The frequency applied to these pins is four times higher than the desired

E-clock rate.

The XTAL pin must be left unterminated when an external CMOS- compatible clock input is connected to

the EXTAL pin. The XTAL output is normally intended to drive only a crystal. Refer to Figure 1-9 and

Figure 1-10.

CAUTION

In all cases, use caution around the oscillator pins. Load capacitances

shown in the oscillator circuit are specified by the crystal manufacturer and

should include all stray layout capacitances.

M68HC11E Family Data Sheet, Rev. 5.1

22 Freescale Semiconductor

Page 23

EXTAL

Pin Descriptions

C

L

MCU

10 MΩ

XTAL

4 x E

CRYSTAL

C

L

Figure 1-9. Common Parallel Resonant Crystal Connections

4 x E

CMOS-COMPATIBLE

MCU

EXTAL

XTAL

EXTERNAL OSCILLATOR

NC

Figure 1-10. External Oscillator Connections

1.4.4 E-Clock Output (E)

E is the output connection for the internally generated E clock. The signal from E is used as a timing

reference. The frequency of the E-clock output is one fourth that of the input frequency at the XTAL and

EXTAL pins. When E-clock output is low, an internal process is taking place. When it is high, data is being

accessed.

All clocks, including the E clock, are halted when the MCU is in stop mode. To reduce RFI emissions, the

E-clock output of most E-series devices can be disabled while operating in single-chip modes.

The E-clock signal is always enabled on the MC68HC811E2.

1.4.5 Interrupt Request (IRQ)

The IRQ input provides a means of applying asynchronous interrupt requests to the MCU. Either negative

edge-sensitive triggering or level-sensitive triggering is program selectable (OPTION register). IRQ

always configured to level-sensitive triggering at reset. When using IRQ

configuration, connect an external pullup resistor, typically 4.7 kΩ, to V

1.4.6 Non-Maskable Interrupt (XIRQ/V

PPE

)

in a level-sensitive wired-OR

.

DD

The XIRQ input provides a means of requesting a non-maskable interrupt after reset initialization. During

reset, the X bit in the condition code register (CCR) is set and any interrupt is masked until MCU software

enables it. Because the XIRQ

network with an external pullup resistor to V

Whenever XIRQ

or IRQ is used with multiple interrupt sources each source must drive the interrupt input

input is level-sensitive, it can be connected to a multiple-source wired-OR

. XIRQ is often used as a power loss detect interrupt.

DD

with an open-drain type of driver to avoid contention between outputs.

is

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 23

Page 24

General Description

NOTE

must be configured for level-sensitive operation if there is more than

IRQ

one source of IRQ

interrupt.

There should be a single pullup resistor near the MCU interrupt input pin (typically 4.7 kΩ). There must

also be an interlock mechanism at each interrupt source so that the source holds the interrupt line low

until the MCU recognizes and acknowledges the interrupt request. If one or more interrupt sources are

still pending after the MCU services a request, the interrupt line will still be held low and the MCU will be

interrupted again as soon as the interrupt mask bit in the MCU is cleared (normally upon return from an

interrupt). Refer to Chapter 5 Resets and Interrupts.

V

is the input for the 12-volt nominal programming voltage required for EPROM/OTPROM

PPE

programming. On devices without EPROM/OTPROM, this pin is only an XIRQ

input.

CAUTION

During EPROM programming of the MC68HC711E9 device, the V

PPE

pin

circuitry may latch-up and be damaged if the input current is not limited to

10 mA. For more information please refer to MC68HC711E9 8-Bit

Microcontroller Unit Mask Set Errata 3 (Freescale document order number

68HC711E9MSE3.

1.4.7 MODA and MODB (MODA/LIR and MODB/V

STBY

)

During reset, MODA and MODB select one of the four operating modes:

• Single-chip mode

• Expanded mode

• Test mode

• Bootstrap mode

Refer to Chapter 2 Operating Modes and On-Chip Memory.

After the operating mode has been selected, the load instruction register (LIR

) pin provides an open-drain

output to indicate that execution of an instruction has begun. A series of E-clock cycles occurs during

execution of each instruction. The LIR

signal goes low during the first E-clock cycle of each instruction

(opcode fetch). This output is provided for assistance in program debugging.

The V

pin is more than one MOS threshold (about 0.7 volts) above the V

of the reset logic are powered from this signal rather than the V

retained without V

must remain low until V

pin is used to input random-access memory (RAM) standby power. When the voltage on this

STBY

voltage, the internal RAM and part

DD

input. This allows RAM contents to be

DD

power applied to the MCU. Reset must be driven low before VDD is removed and

DD

has been restored to a valid level.

DD

1.4.8 VRL and VRH

These two inputs provide the reference voltages for the analog-to-digital (A/D) converter circuitry:

•V

•V

For proper A/D converter operation:

•V

•V

is the low reference, typically 0 Vdc.

RL

is the high reference.

RH

should be at least 3 Vdc greater than VRL.

RH

and VRH should be between VSS and VDD.

RL

M68HC11E Family Data Sheet, Rev. 5.1

24 Freescale Semiconductor

Page 25

Pin Descriptions

1.4.9 STRA/AS

The strobe A (STRA) and address strobe (AS) pin performs either of two separate functions, depending

on the operating mode:

• In single-chip mode, STRA performs an input handshake (strobe input) function.

• In the expanded multiplexed mode, AS provides an address strobe function.

AS can be used to demultiplex the address and data signals at port C. Refer to Chapter 2 Operating

Modes and On-Chip Memory.

1.4.10 STRB/R/W

The strobe B (STRB) and read/write (R/W) pin act as either an output strobe or as a data bus direction

indicator, depending on the operating mode.

In single-chip operating mode, STRB acts as a programmable strobe for handshake with other parallel

devices. Refer to Chapter 6 Parallel Input/Output (I/O) Ports for further information.

In expanded multiplexed operating mode, R/W

data bus. A low on the R/W

pin indicates data is being written to the external data bus. A high on this pin

indicates that a read cycle is in progress. R/W

is used to indicate the direction of transfers on the external

stays low during consecutive data bus write cycles, such

as a double-byte store. It is possible for data to be driven out of port C, if internal read visibility (IRV) is

enabled and an internal address is read, even though R/W

is in a high-impedance state. Refer to

Chapter 2 Operating Modes and On-Chip Memory for more information about IRVNE (internal read

visibility not E).

1.4.11 Port Signals

Port pins have different functions in different operating modes. Pin functions for port A, port D, and port

E are independent of operating modes. Port B and port C, however, are affected by operating mode. Port

B provides eight general-purpose output signals in single-chip operating modes. When the microcontroller

is in expanded multiplexed operating mode, port B pins are the eight high-order address lines.

Port C provides eight general-purpose input/output signals when the MCU is in the single-chip operating

mode. When the microcontroller is in the expanded multiplexed operating mode, port C pins are a

multiplexed address/data bus.

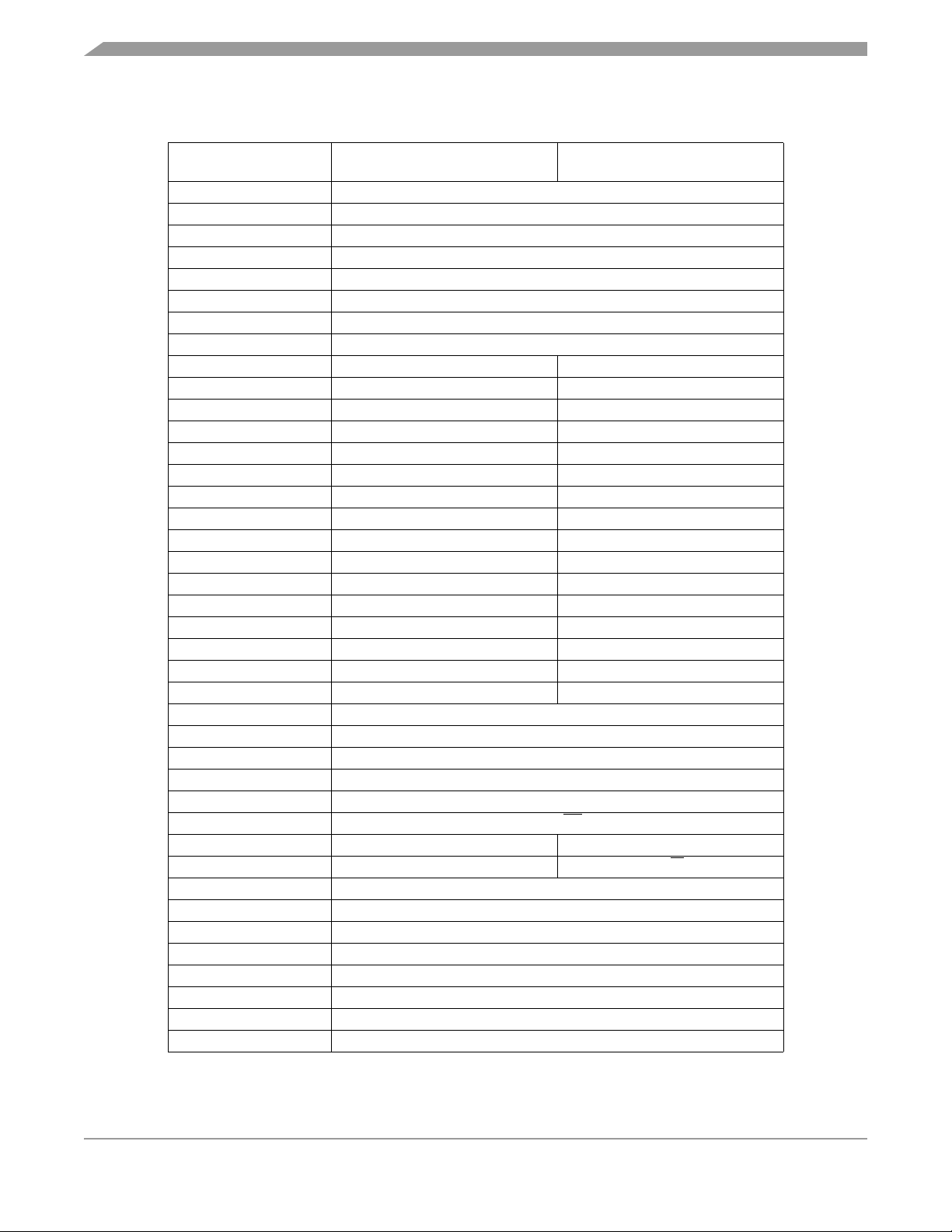

Refer to Table 1-1 for a functional description of the 40 port signals within different operating modes.

Terminate unused inputs and input/output (I/O) pins configured as inputs high or low.

1.4.12 Port A

In all operating modes, port A can be configured for three timer input capture (IC) functions and four timer

output compare (OC) functions. An additional pin can be configured as either the fourth IC or the fifth OC.

Any port A pin that is not currently being used for a timer function can be used as either a general-purpose

input or output line. Only port A pins PA7 and PA3 have an associated data direction control bit that allows

the pin to be selectively configured as input or output. Bits DDRA7 and DDRA3 located in PACTL register

control data direction for PA7 and PA3, respectively. All other port A pins are fixed as either input or

output.

PA7 can function as general-purpose I/O or as timer output compare for OC1. PA7 is also the input to the

pulse accumulator, even while functioning as a general-purpose I/O or an OC1 output.

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 25

Page 26

General Description

Table 1-1. Port Signal Functions

Port/Bit

PA 0 PA 0/ I C3

PA 1 PA 1/ I C2

PA 2 PA 2/ I C1

PA3 PA3/OC5/IC4/OC1

PA4 PA4/OC4/OC1

PA5 PA5/OC3/OC1

PA6 PA6/OC2/OC1

PA7 PA7/PAI/OC1

PB0 PB0 ADDR8

PB1 PB1 ADDR9

PB2 PB2 ADDR10

PB3 PB3 ADDR11

PB4 PB4 ADDR12

PB5 PB5 ADDR13

PB6 PB6 ADDR14

PB7 PB7 ADDR15

PC0 PC0 ADDR0/DATA0

PC1 PC1 ADDR1/DATA1

PC2 PC2 ADDR2/DATA2

PC3 PC3 ADDR3/DATA3

PC4 PC4 ADDR4/DATA4

PC5 PC5 ADDR5/DATA5

PC6 PC6 ADDR6/DATA6

PC7 PC7 ADDR7/DATA7

PD0 PD0/RxD

PD1 PD1/TxD

PD2 PD2/MISO

PD3 PD3/MOSI

PD4 PD4/SCK

PD5 PD5/SS

— STRA AS

—STRB R/W

PE0 PE0/AN0

PE1 PE1/AN1

PE2 PE3/AN2

PE3 PE3/AN3

PE4 PE4/AN4

PE5 PE5/AN5

PE6 PE6/AN6

PE7 PE7/AN7

Single-Chip and

Bootstrap Modes

Expanded and

Test Modes

M68HC11E Family Data Sheet, Rev. 5.1

26 Freescale Semiconductor

Page 27

Pin Descriptions

PA6–PA4 serve as either general-purpose outputs, timer input captures, or timer output compare 2–4. In

addition, PA6–PA4 can be controlled by OC1.

PA3 can be a general-purpose I/O pin or a timer IC/OC pin. Timer functions associated with this pin

include OC1 and IC4/OC5. IC4/OC5 is software selectable as either a fourth input capture or a fifth output

compare. PA3 can also be configured to allow OC1 edges to trigger IC4 captures.

PA2–PA0 serve as general-purpose inputs or as IC1–IC3.

PORTA can be read at any time. Reads of pins configured as inputs return the logic level present on the

pin. Pins configured as outputs return the logic level present at the pin driver input. If written, PORTA

stores the data in an internal latch, bits 7 and 3. It drives the pins only if they are configured as outputs.

Writes to PORTA do not change the pin state when pins are configured for timer input captures or output

compares. Refer to Chapter 6 Parallel Input/Output (I/O) Ports.

1.4.13 Port B

During single-chip operating modes, all port B pins are general-purpose output pins. During MCU reads

of this port, the level sensed at the input side of the port B output drivers is read. Port B can also be used

in simple strobed output mode. In this mode, an output pulse appears at the STRB signal each time data

is written to port B.

In expanded multiplexed operating modes, all of the port B pins act as high order address output signals.

During each MCU cycle, bits 15–8 of the address bus are output on the PB7–PB0 pins. The PORTB

register is treated as an external address in expanded modes.

1.4.14 Port C

While in single-chip operating modes, all port C pins are general-purpose I/O pins. Port C inputs can be

latched into an alternate PORTCL register by providing an input transition to the STRA signal. Port C can

also be used in full handshake modes of parallel I/O where the STRA input and STRB output act as

handshake control lines.

When in expanded multiplexed modes, all port C pins are configured as multiplexed address/data signals.

During the address portion of each MCU cycle, bits 7–0 of the address are output on the PC7–PC0 pins.

During the data portion of each MCU cycle (E high), PC7–PC0 are bidirectional data signals,

DATA7–DATA0. The direction of data at the port C pins is indicated by the R/W

The CWOM control bit in the PIOC register disables the port C P-channel output driver. CWOM

simultaneously affects all eight bits of port C. Because the N-channel driver is not affected by CWOM,

setting CWOM causes port C to become an open-drain type output port suitable for wired-OR operation.

In wired-OR mode:

• When a port C bit is at logic level 0, it is driven low by the N-channel driver.

• When a port C bit is at logic level 1, the associated pin has high-impedance, as neither the

N-channel nor the P-channel devices are active.

It is customary to have an external pullup resistor on lines that are driven by open-drain devices. Port C

can only be configured for wired-OR operation when the MCU is in single-chip mode. Refer to Chapter 6

Parallel Input/Output (I/O) Ports for additional information about port C functions.

signal.

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 27

Page 28

General Description

1.4.15 Port D

Pins PD5–PD0 can be used for general-purpose I/O signals. These pins alternately serve as the serial

communication interface (SCI) and serial peripheral interface (SPI) signals when those subsystems are

enabled.

• PD0 is the receive data input (RxD) signal for the SCI.

• PD1 is the transmit data output (TxD) signal for the SCI.

• PD5–PD2 are dedicated to the SPI:

– PD2 is the master in/slave out (MISO) signal.

– PD3 is the master out/slave in (MOSI) signal.

– PD4 is the serial clock (SCK) signal.

– PD5 is the slave select (SS

) input.

1.4.16 Port E

Use port E for general-purpose or analog-to-digital (A/D) inputs.

CAUTION

If high accuracy is required for A/D conversions, avoid reading port E during

sampling, as small disturbances can reduce the accuracy of that result.

M68HC11E Family Data Sheet, Rev. 5.1

28 Freescale Semiconductor

Page 29

Chapter 2 Operating Modes and On-Chip Memory

2.1 Introduction

This section contains information about the operating modes and the on-chip memory for M68HC11

E-series MCUs. Except for a few minor differences, operation is identical for all devices in the E series.

Differences are noted where necessary.

2.2 Operating Modes

The values of the mode select inputs MODB and MODA during reset determine the operating mode.

Single-chip and expanded multiplexed are the normal modes.

• In single-chip mode only on-chip memory is available.

• Expanded mode, however, allows access to external memory.

Each of the two normal modes is paired with a special mode:

• Bootstrap, a variation of the single-chip mode, is a special mode that executes a bootloader

program in an internal bootstrap ROM.

• Test is a special mode that allows privileged access to internal resources.

2.2.1 Single-Chip Mode

In single-chip mode, ports B and C and strobe pins A (STRA) and B (STRB) are available for

general-purpose parallel input/output (I/O). In this mode, all software needed to control the MCU is

contained in internal resources. If present, read-only memory (ROM) and/or erasable, programmable

read-only memory (EPROM) will always be enabled out of reset, ensuring that the reset and interrupt

vectors will be available at locations $FFC0–$FFFF.

NOTE

For the MC68HC811E2, the vector locations are the same; however, they

are contained in the 2048-byte EEPROM array.

2.2.2 Expanded Mode

In expanded operating mode, the MCU can access the full 64-Kbyte address space. The space includes:

• The same on-chip memory addresses used for single-chip mode

• Addresses for external peripherals and memory devices

The expansion bus is made up of ports B and C, and control signals AS (address strobe) and R/W

(read/write). R/W

same pins. During the first half of each bus cycle address information is present. During the second half

of each bus cycle the pins become the bidirectional data bus. AS is an active-high latch enable signal for

an external address latch. Address information is allowed through the transparent latch while AS is high

and is latched when AS drives low.

and AS allow the low-order address and the 8-bit data bus to be multiplexed on the

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 29

Page 30

Operating Modes and On-Chip Memory

The address, R/W, and AS signals are active and valid for all bus cycles, including accesses to internal

memory locations. The E clock is used to enable external devices to drive data onto the internal data bus

during the second half of a read bus cycle (E clock high). R/W

drives low when data is being written to the internal data bus. R/W

controls the direction of data transfers. R/W

will remain low during consecutive data

bus write cycles, such as when a double-byte store occurs.

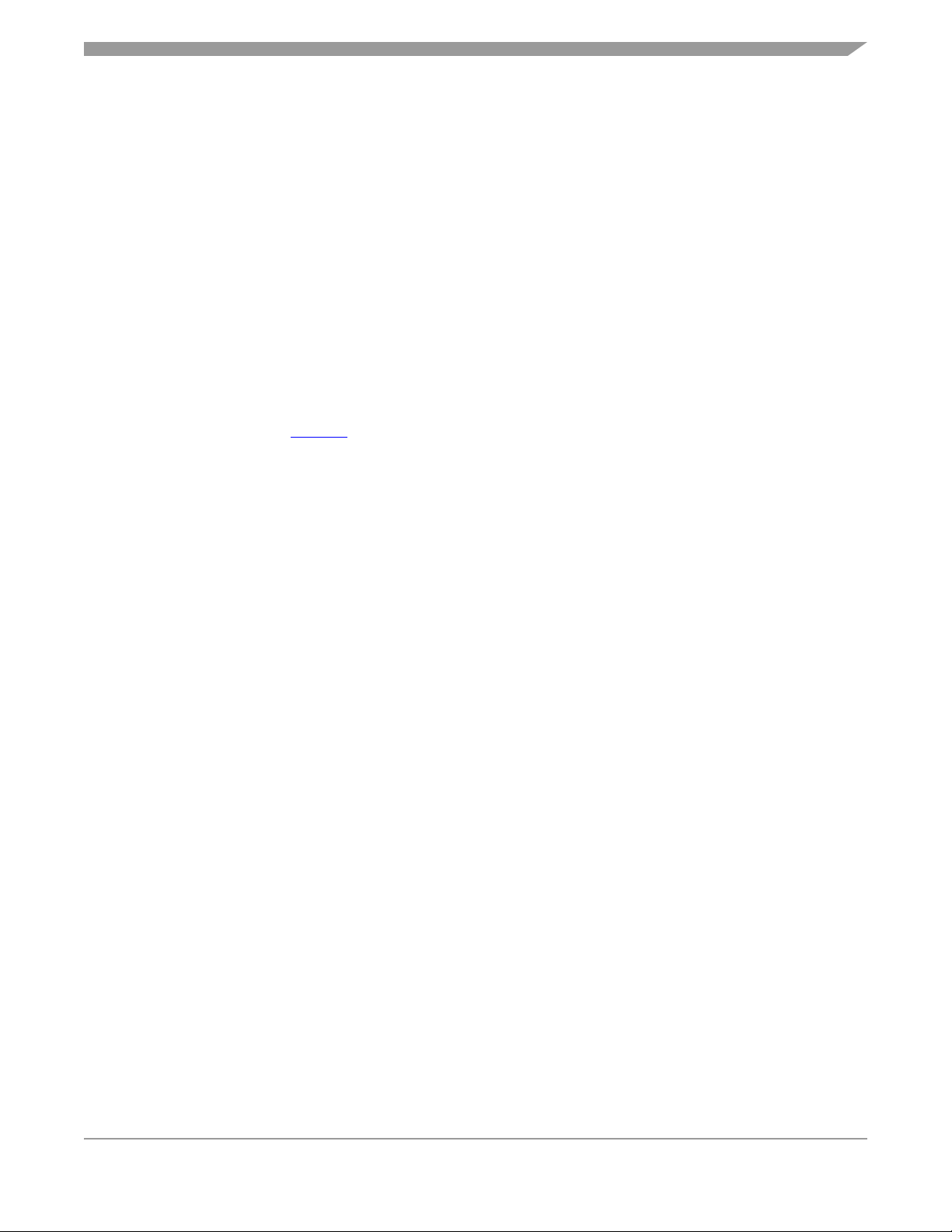

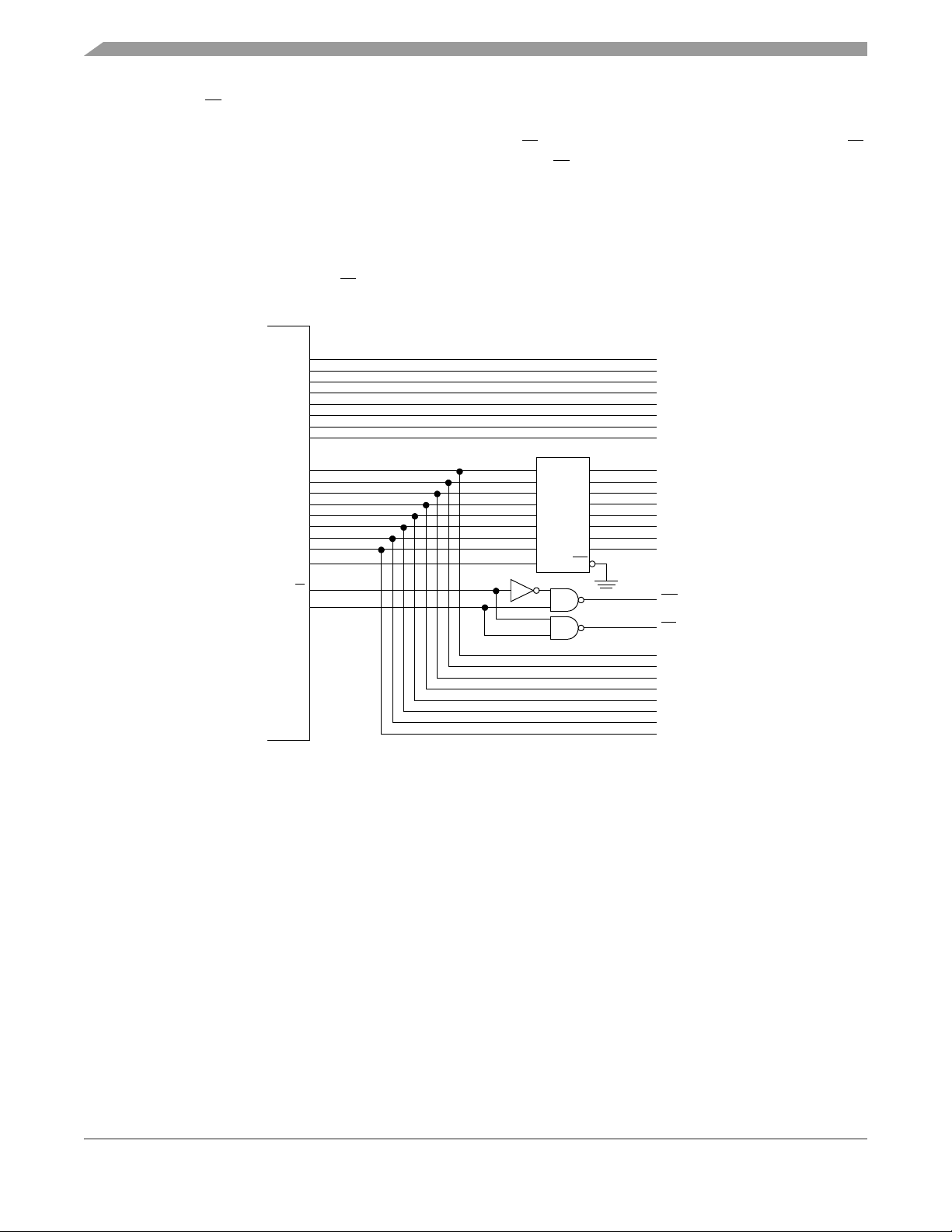

Refer to Figure 2-1.

NOTE

The write enable signal for an external memory is the NAND of the E clock

and the inverted R/W

signal.

2.2.3 Test Mode

MCU

PB7

PB6

PB5

PB4

PB3

PB2

PB1

PB0

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

AS

R/W

E

HC373

D1

D2

D3

D4

D5

D6

D7

D8

LE

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

OE

Figure 2-1. Address/Data Demultiplexing

ADDR15

ADDR14

ADDR13

ADDR12

ADDR11

ADDR10

ADDR9

ADDR8

ADDR7

ADDR6

ADDR5

ADDR4

ADDR3

ADDR2

ADDR1

ADDR0

WE

OE

DATA7

DATA6

DATA5

DATA4

DATA3

DATA2

DATA1

DATA0

Test mode, a variation of the expanded mode, is primarily used during Freescale’s internal production

testing; however, it is accessible for programming the configuration (CONFIG) register, programming

calibration data into electrically erasable, programmable read-only memory (EEPROM), and supporting

emulation and debugging during development.

2.2.4 Bootstrap Mode

When the MCU is reset in special bootstrap mode, a small on-chip read-only memory (ROM) is enabled

at address $BF00–$BFFF. The ROM contains a bootloader program and a special set of interrupt and

reset vectors. The MCU fetches the reset vector, then executes the bootloader.

Bootstrap mode is a special variation of the single-chip mode. Bootstrap mode allows special-purpose

programs to be entered into internal random-access memory (RAM). When bootstrap mode is selected

at reset, a small bootstrap ROM becomes present in the memory map. Reset and interrupt vectors are

M68HC11E Family Data Sheet, Rev. 5.1

30 Freescale Semiconductor

Page 31

Memory Map

located in this ROM at $BFC0–$BFFF. The bootstrap ROM contains a small program which initializes the

serial communications interface (SCI) and allows the user to download a program into on-chip RAM. The

size of the downloaded program can be as large as the size of the on-chip RAM. After a 4-character delay,

or after receiving the character for the highest address in RAM, control passes to the loaded program at

$0000. Refer to Figure 2-2, Figure 2-3, Figure 2-4, Figure 2-5, and Figure 2-6.

Use of an external pullup resistor is required when using the SCI transmitter pin because port D pins are

configured for wired-OR operation by the bootloader. In bootstrap mode, the interrupt vectors are directed

to RAM. This allows the use of interrupts through a jump table. Refer to the application note AN1060

entitled M68HC11 Bootstrap Mode, that is included in this data book.

2.3 Memory Map

The operating mode determines memory mapping and whether external addresses can be accessed.

Refer to Figure 2-2, Figure 2-3, Figure 2-4, Figure 2-5, and Figure 2-6, which illustrate the memory maps

for each of the three families comprising the M68HC11 E series of MCUs.

Memory locations for on-chip resources are the same for both expanded and single-chip modes. Control

bits in the configuration (CONFIG) register allow EPROM and EEPROM (if present) to be disabled from

the memory map. The RAM is mapped to $0000 after reset. It can be placed at any 4-Kbyte boundary

($x000) by writing an appropriate value to the RAM and I/O map register (INIT). The 64-byte register block

is mapped to $1000 after reset and also can be placed at any 4-Kbyte boundary ($x000) by writing an

appropriate value to the INIT register. If RAM and registers are mapped to the same boundary, the first

64 bytes of RAM will be inaccessible.

Refer to Figure 2-7, which details the MCU register and control bit assignments. Reset states shown are

for single-chip mode only.

$0000

$1000

$B600

$D000

$FFFF

EXT

EXT EXT

EXPANDED

BOOTSTRAP SPECIAL

EXT

TEST

0000

512 BYTES RAM

01FF

1000

64-BYTE REGISTER BLOCK

103F

BOOT

BF00

ROM

BFFF

NORMAL

FFC0

MODES

INTERRUPT

FFFF

VECTORS

BFC0

BFFF

SPECIAL MODES

INTERRUPT

VECTORS

Figure 2-2. Memory Map for MC68HC11E0

M68HC11E Family Data Sheet, Rev. 5.1

Freescale Semiconductor 31

Page 32

Operating Modes and On-Chip Memory

$0000

$1000

$B600

$D000

$FFFF

EXT

EXT EXT

EXT

EXPANDED

BOOTSTRAP SPECIAL

Figure 2-3. Memory Map for MC68HC11E1

EXT

EXT

TEST

0000

512 BYTES RAM

01FF

1000

64-BYTE REGISTER BLOCK

103F

B600

512 BYTES EEPROM

B7FF

BOOT

BF00

ROM

BFFF

NORMAL

FFC0

MODES

INTERRUPT

FFFF

VECTORS

BFC0

BFFF

SPECIAL MODES

INTERRUPT

VECTORS

$0000

$1000

$B600

$D000

$FFFF

SINGLE

CHIP