Page 1

Table of Contents Revisions

1 Title

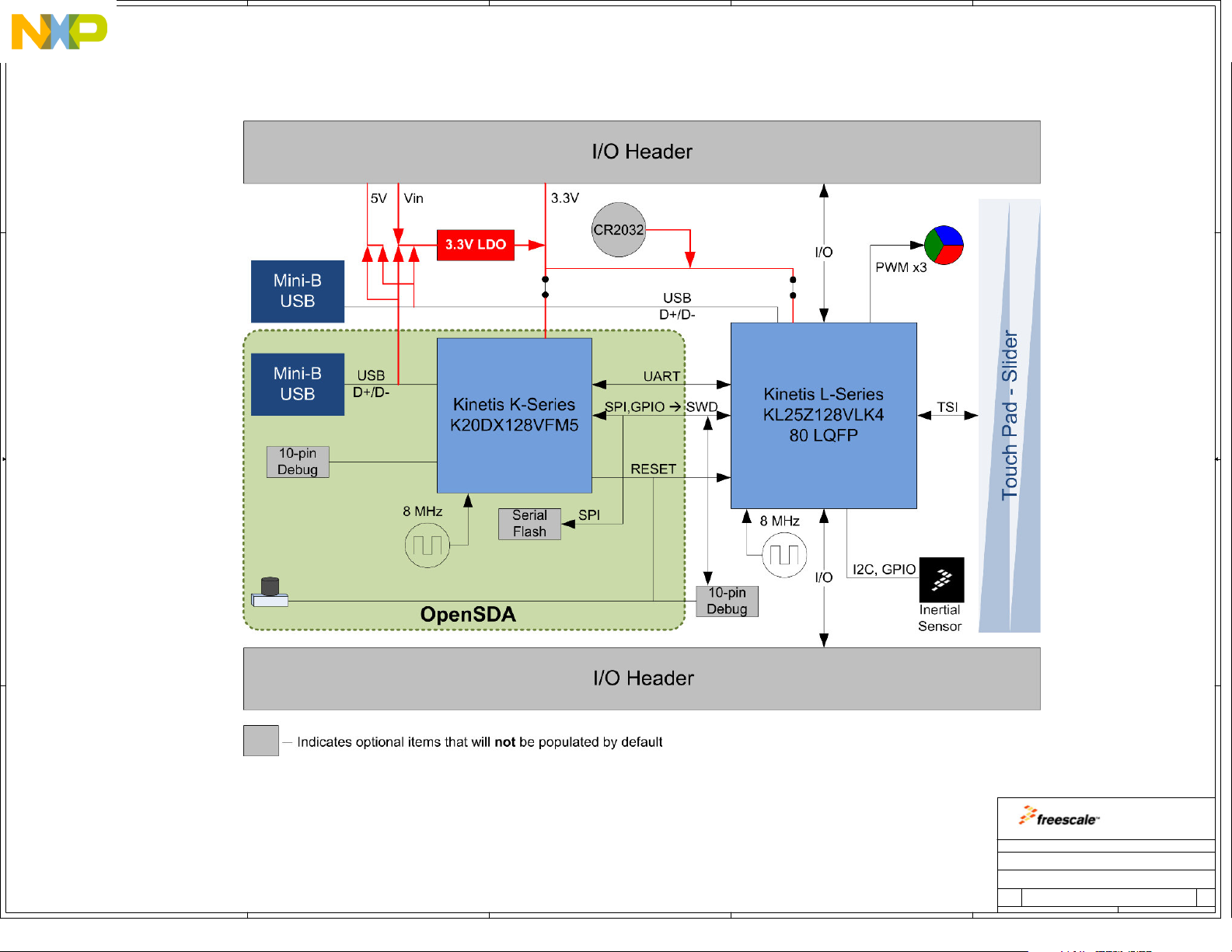

Block Diagram

2

3 KL25Z MCU

OpenSDA INTERFACE

4

5 I/O Headers and Power Supply

D D

C C

5

4

3

2

Rev Description

X1 Initial Draft

A Release to production M. NORMAN05/03/12

B Changes made to KL25Z

XTAL Circuit

CX1

Prototype revision

1

Date

04/10/12

05/09/12

05/21/12

06/29/12

07/10/12

Approved

M. NORMAN

M. NORMAN

M. NORMANFixed J10 orientation.C

M. NORMANInitial Re-spin

M. NORMANRe-spin releaseD

FREEDOM KL25Z

B B

A A

Designer:

Designer:

Designer:

RAFAEL DEL REY

RAFAEL DEL REY

RAFAEL DEL REY

Drawn by:

Drawn by:

Drawn by:

RAFAEL DEL REY

RAFAEL DEL REY

RAFAEL DEL REY

Approved:

Approved:

Approved:

MICHAEL NORMAN

MICHAEL NORMAN

MICHAEL NORMAN

5

4

3

2

Drawing Title:

Drawing Title:

Drawing Title:

Page Title:

Page Title:

Page Title:

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Automotive, Industrial & Multi-

Automotive, Industrial & Multi-

Automotive, Industrial & MultiMarket Solutions Group

Market Solutions Group

Market Solutions Group

6501 William Cannon Drive West Austin, T X 78735-8598

6501 William Cannon Drive West Austin, T X 78735-8598

6501 William Cannon Drive West Austin, T X 78735-8598

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

FRDM-KL25Z

FRDM-KL25Z

FRDM-KL25Z

TITLE PAGE

TITLE PAGE

TITLE PAGE

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

Friday, July 13, 2012

Friday, July 13, 2012

Friday, July 13, 2012

SCH-27556 | PDF: SPF-27556 D

1

1 5

1 5

1 5

____ X____

____ X____

____ X____

Page 2

5

1. Unless Otherwise Specified:

All resistors are in ohms, 5%, 1/8 Watt

All capacitors are in uF, 20%, 50V

All voltages are DC

All polarized capacitors are aluminum electrolytic

2. Interrupted lines coded with the same letter or letter

combinations are electrically connected.

D D

3. Device type number is for reference only. The number

varies with the manufacturer.

4. Special signal usage:

_B Denotes - Active-Low Signal

<> or [] Denotes - Vectored Signals

5. Interpret diagram in accordance with American

National Standards Institute specifications, current

revision, with the exception of logic block symbology.

C C

4

3

2

1

B B

A A

___ X

___ X

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

Drawing Title:

Drawing Title:

Drawing Title:

Page Title:

Page Title:

Page Title:

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Thursday, July 12, 2012

Date: Sheet of

Thursday, July 12, 2012

Date: Sheet of

5

4

3

2

Thursday, July 12, 2012

___ X

FRDM-KL25Z

FRDM-KL25Z

FRDM-KL25Z

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

1

___

___

___

2 5

2 5

2 5

Page 3

5

L1

J5

S1

S3S4

CONN USB MINI-B

1

2

3

4

5

P5V0_USB_CONN_VBUS

USB_CONN_DN

USB_CONN_DP

TC_USB_ID_TP

GND

TP2

2

GND

3

GND

5VD-D+IDG

SHIELD_K20USB

D D

S2

L2

1 2

330 OHM

P5V_KL25Z

1 2

1

C3

330 OHM

1.0UF

GND

U2

GSOT05C-GS08

USB_DN

USB_DP

R2 33

R1 33 C10

KL25Z USB CONNECTOR

1

D14pg(5)

USB_VOUT33

C7

2.2UF

D15pg(5)

PTE20pg(5)

PTE21pg(5)

PTE22pg(5)

PTE23pg(5)

PTE30pg(5)

PTE2pg(5)

PTE3pg(5)

PTE4pg(5)

PTE5pg(5)

C C

B B

I2C0_SCLpg(5)

I2C0_SDApg(5)

PTE31pg(5)

TP3

GND

PTE0/UART1_TX/RTC_CLKOUT/CMP0_OUT/I2C1_SDA

2

PTE1/SPI1_MOSI/UART1_RX/SPI1_MISO/I2C1_SCL

3

PTE2/SPI1_SCK

4

PTE3/SPI1_MISO/SPI1_MOSI

5

PTE4/SPI1_PCS0

6

PTE5

13

PTE20/ADC0_DP0/ADC0_SE0/FTM1_CH0/UART0_TX

14

PTE21/ADC0_DM0/ADC0_SE4A/FTM1_CH1/UART0_RX

15

PTE22/ADC0_DP3/ADC0_SE3/FTM2_CH0/UART2_TX

16

PTE23/ADC0_DM3/ADC0_SE7A/FTM2_CH1/UART2_RX

24

PTE24/FTM0_CH0/I2C0_SCL

25

PTE25/FTM0_CH1/I2C0_SDA

22

PTE30/DAC0_OUT/ADC0_SE23/CMP0_IN4/FTM0_CH3/FTM_CLKIN1

23

PTE31/FTM0_CH4

P5V_KL25Z

12

VREGIN

11

VOUT33

10

USB_DN

USB0_DM

9

USB_DP

USB0_DP

4

3

2

1

KL25Z Decoupling Caps

P3V3_KL25Z

P3V3_KL25Z

C5

1.0UF

P3V3_KL25Z

7

VDD1

C6

1.0UF

SH1

SOLDER SHORT

60

VDD238VDD3

C14

1.0UF

C11

C13

0.1UF

0.1UF

0.1UF

GND

R3

VREFH

C8

C9

0.1UF

0.1UF

GND

GND

18

19

17

20

VDDA

VSSA

VREFL

VREFH

PTC1/LLWU_P6/RTC_CLKIN/ADC0_SE15/TSI0_CH14/I2C1_SCL/FTM0_CH0

AREF pg(5)

0 DNP

CAD NOTE:

Please place these capacitors

near their respective CPU pin

(VREFH to VREFL

and VDDA to VSSA)

PTE29/CMP0_IN5/ADC0_SE4B/FTM0_CH2/FTM_CLKIN0

PTA0/TSI0_CH1/FTM0_CH5/SWD_CLK

PTA1/TSI0_CH2/UART0_RX/FTM2_CH0

PTA2/TSI0_CH3/UART0_TX/FTM2_CH1

PTA3/TSI0_CH4/I2C1_SCL/FTM0_CH0/SWD_DIO

PTA4/TSI0_CH5/I2C1_SDA/FTM0_CH1/NMI

PTA5/USB_CLKIN/FTM0_CH2

PTA12/FTM1_CH0

PTA13/FTM1_CH1

PTA14/SPI0_PCS0/UART0_TX

PTA15/SPI0_SCK/UART0_RX

PTA16/SPI0_MOSI/SPI0_MISO

PTA17/SPI0_MISO/SPI0_MOSI

PTA18/EXTAL0/UART1_RX/FTM_CLKIN0

PTA19/XTAL0/UART1_TX/FTM_CLKIN1/LPTMR0_ALT1

PTB0/LLWU_P5/ADC0_SE8/TSI0_CH0/I2C0_SCL/FTM1_CH0

PTB1/ADC0_SE9/TSI0_CH6/I2C0_SDA/FTM1_CH1

PTB2/ADC0_SE12/TSI0_CH7/I2C0_SCL/FTM2_CH0

PTB3/ADC0_SE13/TSI0_CH8/I2C0_SDA/FTM2_CH1

PTB10/SPI1_PCS0

PTB16/TSI0_CH9/SPI1_MOSI/UART0_RX/FTM_CLKIN0/SPI1_MISO

PTB17/TSI0_CH10/SPI1_MISO/UART0_TX/FTM_CLKIN1/SPI1_MOSI

PTC0/ADC0_SE14/TSI0_CH13/EXTRG_IN/CMP0_OUT

PTC2/ADC0_SE11/TSI0_CH15/I2C1_SDA/FTM0_CH1

PTC3/LLWU_P7/UART1_RX/FTM0_CH2/CLKOUT

PTC4/LLWU_P8/SPI0_PCS0/UART1_TX/FTM0_CH3

PTC5/LLWU_P9/SPI0_SCK/LPTMR0_ALT2/CMP0_OUT

PTC6/LLWU_P10/CMP0_IN0/SPI0_MOSI/EXTRG_IN/SPI0_MISO

PTC7/CMP0_IN1/SPI0_MISO/SPI0_MOSI

PTC8/CMP0_IN2/I2C0_SCL/FTM0_CH4

PTC9/CMP0_IN3/I2C0_SDA/FTM0_CH5

PTB11/SPI1_SCK

PTB18/TSI0_CH11/FTM2_CH0

PTB19/TSI0_CH12/FTM2_CH1

PTC10/I2C1_SCL

PTC11/I2C1_SDA

PTC12/FTM_CLKIN0

PTC13/FTM_CLKIN1

PTA20/RESET

PTB8/EXTRG_IN

PTB9

PTC16

PTC17

U3

21

26

27

28

29

30

31

32

33

34

35

36

37

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

61

62

63

64

65

66

67

68

69

70

71

72

PTE29 pg(5)

KL25_SWD_CLK pg(3)

SWD_DIO_TGTMCU pg(3,4)

D4 pg(5)

D5 pg(5)

D3 pg(5)

D8 pg(5)

INT1_ACCEL pg(5)

INT2_ACCEL pg(5)

EXTAL

XTAL

RST_TGTMCU pg(3,4,5)

A0 pg(5)

A1 pg(5)

A2 pg(5)

A3 pg(5)

TSI0_CH9

TSI0_CH10

PTB18

PTB19

A5 pg(4,5)

A4 pg(5)

D6 pg(5)

D7 pg(5)

PTA16 pg(5)

PTA17 pg(5)

C16

22PF

GND

PTB8 pg(5)

PTB9 pg(5)

PTB10 pg(5)

PTB11 pg(5)

PTC0 pg(5)

PTC3 pg(5)

PTC4 pg(5)

PTC5 pg(5)

PTC6 pg(5)

PTC7 pg(5)

PTC10 pg(5)

PTC11 pg(5)

PTC12 pg(5)

PTC13 pg(5)

PTC16 pg(5)

PTC17 pg(5)

DNP

R25 1.0M

Y1

GND2

1 2

GND1

8MHZ

D0 pg(5)

D1 pg(5)

34

GNDGND

GND

R5 1K

R6 1K

UART1_RX_TGTMCU pg(4)

UART1_TX_TGTMCU pg(4)

TSI CAPACITIVE/TOUCH

C19

22PF

INTERFACE

E1

Slider_4

73

PTD0/SPI0_PCS0/FTM0_CH0

PTD1/ADC0_SE5B/SPI0_SCK/FTM0_CH1

PTD2/SPI0_MOSI/UART2_RX/FTM0_CH2/SPI0_MISO

PTD3/SPI0_MISO/UART2_TX/FTM0_CH3/SPI0_MOSI

PTD4/LLWU_P14/SPI1_PCS0/UART2_RX/FTM0_CH4

PTD5/ADC0_SE6B/SPI1_SCK/UART2_TX/FTM0_CH5

PTD6/LLWU_P15/ADC0_SE7B/SPI1_MOSI/UART0_RX/SPI1_MISO

VSS18VSS239VSS3

59

GND

A A

RGB LED FEATURE

PTB18 PTB19LEDRGB_GREEN

R8

220

TP14

LEDRGB_RED

P3V3

CLV1A-FKB-CJ1M1F1BB7R4S3

5

D3

1

R G

2 3

B

TP13

4

LEDRGB_GREENLEDRGB_RED

LEDRGB_BLUE

LEDRGB_BLUE

R7

220

R11

D13 pg(3,5)

220

TP17

SWD CONNECTOR

P3V3_KL25Z

GND

4

SWD_DIO_TGTMCUpg(3,4)

J6

1 2

3 4

65

7 8

9 10

HDR 2X5

SHORTING HEADER ON BOTTOM LAYER

Jumper is shorted by a cut-trace

on bottom layer. Cutting the trace

will effectively isolate the on-board

MCU from the OpenSDA

debug interface.

1

J11

2

DNP

HDR 1X2 TH

RST_TGTMCU pg(3,4,5)

KL25_SWD_CLK pg(3)

SWD_CLK_TGTMCU pg(4)

3

PTD7/SPI1_MISO/UART0_TX/SPI1_MOSI

KINETIS KL25Z MCU

74

75

76

77

78

79

80

PKL25Z128VLK4

D10 pg(5)

D13 pg(3,5)

D11 pg(5)

D12 pg(5)

D2 pg(5)

D9 pg(5)

PTD6 pg(5)

PTD7 pg(5)

2

___ X

___ X

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

Drawing Title:

Drawing Title:

Drawing Title:

Page Title:

Page Title:

Page Title:

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Thursday, July 12, 2012

Date: Sheet of

Thursday, July 12, 2012

Date: Sheet of

Thursday, July 12, 2012

___ X

FRDM-KL25Z

FRDM-KL25Z

FRDM-KL25Z

KL25Z MCU

KL25Z MCU

KL25Z MCU

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

1

___

___

___

3 5

3 5

3 5

Page 4

5

4

3

2

1

D D

P5V_SDA

L4

1 2

J7

S1

S3S4

CONN USB MINI-B

1

P5V0_SDA_USB_CONN_VBUS

5VD-D+IDG

2

SDA_USB_CONN_DN

3

SDA_USB_CONN_DP

4

TC_SDA_USB_ID_TP

5

C C

B B

S2

SDA_USBSHIELD

L3

1 2

330 OHM

GND

TARGET RESET AND BOOTLOADER

PUSH BUTTON

RST_TGTMCUpg(3,4,5)

P3V3

R4

10K

C12

1.0UF

GND

330 OHM

TP24

GSOT05C-GS08

2

U8

3

GND

P5V_SDA

R17

4.7K

SDA_RST

R21

10K

GND GND

PU/PD LOGIC:

SERIAL INTERFACE

IS ALWAYS RESET

WHEN USB PORT

IS DISCONNECTED

SW1

1 2

EVQ-PE105K

C15

1.0UF

GND

R14 33

R13 33 C25

1

GNDGND

SDA_USB_DN

SDA_USB_DP

TP27

P3V3_SDA

GND

TP5

TP4

SDA_RST

C17

1.0UF

TP25

TC_VBAT_TP

GND

P5V_SDA

SDA_USB_VOUT33

C21

2.2UF

TC_EXTAL_TP

TC_XTAL_TP

U6

1

VDD1

7

VDDA

8

VSSA

GND

11

VBAT

6

VREGIN

5

VOUT33

4

USB0_DM

3

USB0_DP

10

EXTAL32

9

XTAL32

19

RESET

2

VSS1

GND

33

EPAD

GND

PK20DX128VFM5

JTAG_TCLK/SWD_CLK/EZP_CLK/TSI0_CH1/PTA0/UART0_CTS/UART0_COL/FTM0_CH5

ADC0_SE15/TSI0_CH14/PTC1/SPI0_PCS3/UART1_RTS/FTM0_CH0/I2S0_TXD0

ADC0_SE4B/CMP1_IN0/TSI0_CH15/PTC2/SPI0_PCS2/UART1_CTS/FTM0_CH1/I2S0_TX_FS

ADC0_SE6B/PTD5/SPI0_PCS2/UART0_CTS/UART0_COL/FTM0_CH5/EWM_OUT

JTAG_TDI/EZP_DI/TSI0_CH2/PTA1/UART0_RX/FTM0_CH6

JTAG_TDO/TRACE_SWO/EZP_DO/TSI0_CH3/PTA2/UART0_TX/FTM0_CH7

JTAG_TMS/SWD_DIO/TSI0_CH4/PTA3/UART0_RTS/FTM0_CH0

ADC0_SE8/TSI0_CH0/PTB0/I2C0_SCL/FTM1_CH0/FTM1_QD_PHA

ADC0_SE9/TSI0_CH6/PTB1/I2C0_SDA/FTM1_CH1/FTM1_QD_PHB

CMP1_IN1/PTC3/SPI0_PCS1/UART1_RX/FTM0_CH2/CLKOUT/I2S0_TX_BCLK

CMP0_IN0/PTC6/SPI0_SOUT/PDB0_EXTRG/I2S0_RX_BCLK/I2S0_MCLK

ADC0_SE7b/PTD6/SPI0_PCS3/UART0_RX/FTM0_CH6/FTM0_FLT0

NMI/EZP_CS/TSI0_CH5/PTA4/FTM0_CH1

EXTAL/PTA18/FTM0_FLT2/FTM_CLKIN0

XTAL/PTA19/FTM1_FLT0/FTM_CLKIN1/LPTMR0_ALT1

PTC4/SPI0_PCS0/UART1_TX/FTM0_CH3/CMP1_OUT

PTC5/SPI0_SCK/LPTMR0_ALT2/I2S0_RXD0/CMP0_OUT

CMP0_IN1/PTC7/SPI0_SIN/USB_SOF_OUT/I2S0_RX_FS

PTD4/SPI0_PCS1/UART0_RTS/FTM0_CH4/EWM_IN

PTD7/CMT_IRO/UART0_TX/FTM0_CH7/FTM0_FLT1

OpenSDA INTERFACE

12

SDA_JTAG_TCLK

13

SDA_JTAG_TDI

14

SDA_JTAG_TDO

15

SDA_JTAG_TMS

16

SDA_SWD_EN

17

SDA_EXTAL

18

SDA_XTAL

20

21

22

SDA_SPI0_RST_B

23

SDA_SPI0_CS

24

UART1_TX_TGTMCU

25

UART1_RX_TGTMCU

26

SDA_SPI0_SCK

27

SDA_SPI0_SOUT

28

SDA_SPI0_SIN

29

SDA_LED

30

31

32

SDA_USB_P5V_SENSE

22PF

DNP

SDA_SWD_OE_B

AC

TP20

SDA_PTD6

C23

GND

P3V3_SDA

SDA_LED_R

D4LED GREEN

SDA_PTD5 pg(5)

P5V_SDA

GND

1 2

R12

220

R24

0

R10

4.7K

TP19

R9

10K

Y2

GND2

34

GND1

8MHZ

GNDGND

GND

SDA_SPI0_SOUT

SDA_SPI0_SIN

SDA_SPI0_SCK

A5 pg(3,5)

KL25Z Pin

PTC1/LLWU_P6/RTC_CLKIN

22PF

DNP

R15

P3V3_SDA

14

1

VCC

2 3

GND

7

P3V3_SDA

P3V3_SDA

10K

U4A

74LVC125ADB

R23

10K

SDA_SWD_EN

U4C

74LVC125ADB

12 11

10

13

98

U4D

74LVC125ADB

TARGET MCU

INTERFACE

SIGNALS

RST_TGTMCU pg(3,4,5)

UART1_TX_TGTMCU pg(3)

UART1_RX_TGTMCU pg(3)

SWD_DIO_TGTMCU pg(3)

SWD_CLK_TGTMCU pg(3)

SPARE 74HC125 buffer

A A

P3V3_SDA

U4B

TP11

5

4

5 6

TC_74125_SPARE_O_TPTC_74125_SPARE_I_TP

74LVC125ADB

TP15

4

SPI FLASH MEMORY

TP16

SDA_SPI0_SOUT

TP12

SDA_SPI0_SCK

TP22

SDA_SPI0_RST_B

TP18

SDA_SPI0_CS

1

SI

2

SCK

3

RSET_B

4

CS_B

AT45DB161D-S

OR

AT45DB161E-SSHD

U5

VCC

SO

WP_B

GND

SUBASSEMBLY_S08

P3V3_SDA

6

8

5

7

GND

3

SDA_SPI0_SIN

P3V3_SDA

TP10

OpenSDA INTERFACE JTAG CONNECTOR

P3V3_SDA

R19

65

2

10K

SDA_JTAG_TMS

SDA_JTAG_TCLK

SDA_JTAG_TDO

SDA_JTAG_TDI

SDA_RST

P3V3_SDA

GND

J8

1 2

3 4

7 8

9 10

HDR 2X5

___ X

___ X

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

Drawing Title:

Drawing Title:

Drawing Title:

Page Title:

Page Title:

Page Title:

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Thursday, July 12, 2012

Date: Sheet of

Thursday, July 12, 2012

Date: Sheet of

Thursday, July 12, 2012

___ X

FRDM-KL25Z

FRDM-KL25Z

FRDM-KL25Z

OpenSDA interface

OpenSDA interface

OpenSDA interface

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

1

___

___

___

4 5

4 5

4 5

Page 5

5

4

3

2

1

OPTIONAL

COIN CELL

HOLDER

BT1

3 2

P3V3_BATT

1

D D

C C

P5-9V_VIN

P5V_SDA P5V_KL25Z

1

2

3

D2

BAT54C

U1

3

C4

10uF

NCP1117ST33T3G

GND

I2C INERTIAL SENSOR

P3V3

P3V3

P3V3

R16

P3V3

R20

10K

TP26

MMA8451_SERIAL_ADDR0

B B

A A

R22

10K

DNP

GND

4.7K

I2C0_SCLpg(3)

I2C0_SDApg(3)

TP23

MMA8451_BYP

C22

0.1UF

GND

5

R18

4.7K

0.1UF

U7

4

SCL

6

SDA

7

SA0

2

BYP

MMA8451Q

C20

GND

GND15GND210GND3

12

GND

C18

10uF

GND

1

14

VDD

VDDIO

11

INT1_ACCEL pg(3)

INT1

9

INT2_ACCEL pg(3)

INT2

3

NC3

8

NC8

13

NC13

15

NC15

16

NC16

P5V_SDA P5V_KL25Z

1

2

D5

BAT54C

3

4

+

GND

3003

2

VOUT

VIN

TAB

GND

1

GND

P5V_USB

P3V3_VREGP3V3_VREG

4

GND

AREFpg(3)

D14pg(3)

D15pg(3)

PTD7pg(3)

PTD6pg(3)

PTE31pg(3)

PTA17pg(3)

PTA16pg(3)

PTC17pg(3)

PTC16pg(3)

PTC13pg(3)

PTC12pg(3)

PTC11pg(3)

PTC10pg(3)

PTC6pg(3)

PTC5pg(3)

PTC4pg(3)

PTC3pg(3)

PTC0pg(3)

PTC7pg(3)

PTE30pg(3)

PTE29pg(3)

PTE23pg(3)

PTE22pg(3)

PTE21pg(3)

PTE20pg(3)

PTE5pg(3)

PTE4pg(3)

PTE3pg(3)

PTE2pg(3)

PTB11pg(3)

PTB10pg(3)

RST_TGTMCUpg(3,4)

P5-9V_VIN

3

TP8

C1

10uF

GND

C2

10uF

D1

2

TP7

1

BAT54C

20mOhm Resistor in layout

D0pg(3)

D1pg(3)

D2pg(3)

D3pg(3)

D4pg(3)

D5pg(3)

D6pg(3)

D7pg(3)

D8pg(3)

D9pg(3)

D10pg(3)

D11pg(3)

D12pg(3)

D13pg(3)

GND

CON_2X10

PTB9pg(3)

PTB8pg(3)

P3V3

P3V3

GND

SDA_PTD5pg(4)

A0pg(3)

A1pg(3)

A2pg(3)

A3pg(3)

A4pg(3)

A5pg(3,4)

CON 2X8

C24

2.2UF

SHORTING HEADER

ON BOTTOM LAYER

P3V3

3

J4

HDR 1X2 TH

1

2

DNP

SHORTING HEADER

ON BOTTOM LAYER

HDR 1X2 TH

J3

1

2

DNP

P3V3_KL25Z

P3V3_SDA

DEBUG GROUND HOOK

TP6

GND

2468101214

101214

16

CON 2X8

1 2

3 4657 8

111315

15

12

16

GND

J1

13579

34

78

910

1112

CON 2X6 SKT

J10

6 5

2

J2

9 10

11 12

13 14

15 16

17 18

19 20

135791113

J9

246

8

IN CIRCUIT TEST

GND PROBING

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

ICAP Classification: FCP: FIUO: PUBI:

Drawing Title:

Drawing Title:

Drawing Title:

Page Title:

Page Title:

Page Title:

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Thursday, July 12, 2012

Date: Sheet of

Thursday, July 12, 2012

Date: Sheet of

Thursday, July 12, 2012

TP1

TP9

TP28

GND

___ X

___ X

___ X

___

___

___

FRDM-KL25Z

FRDM-KL25Z

FRDM-KL25Z

ARDUINO SHIELDS & PWR SUPPLY

ARDUINO SHIELDS & PWR SUPPLY

ARDUINO SHIELDS & PWR SUPPLY

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

SCH-27556 | PDF: SPF-27556 D

1

5 5

5 5

5 5

Loading...

Loading...