Freescale DSP56309 Technical Data

Freescale Semiconductor

Technical Data Advance Information

DSP56309

24-Bit Digital Signal Processor

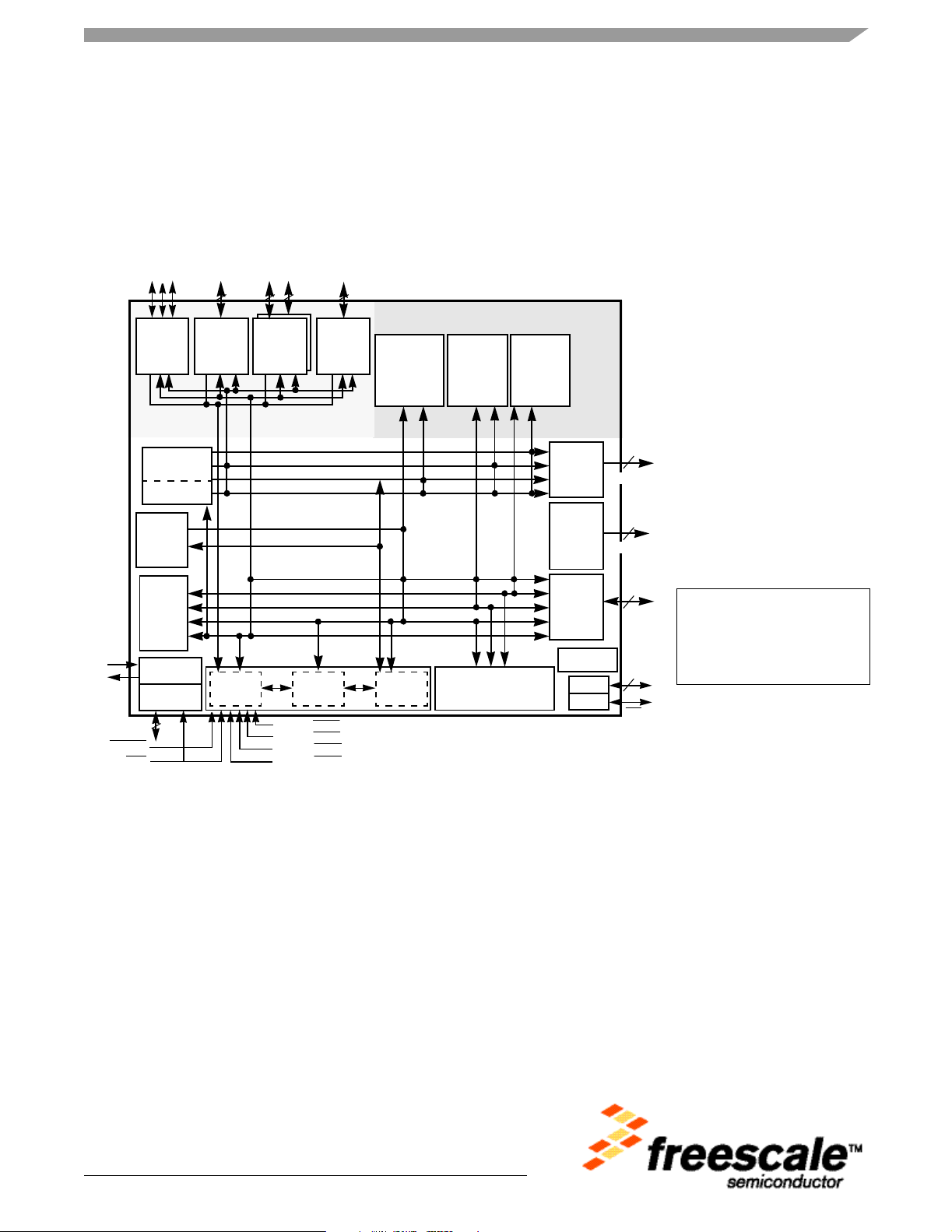

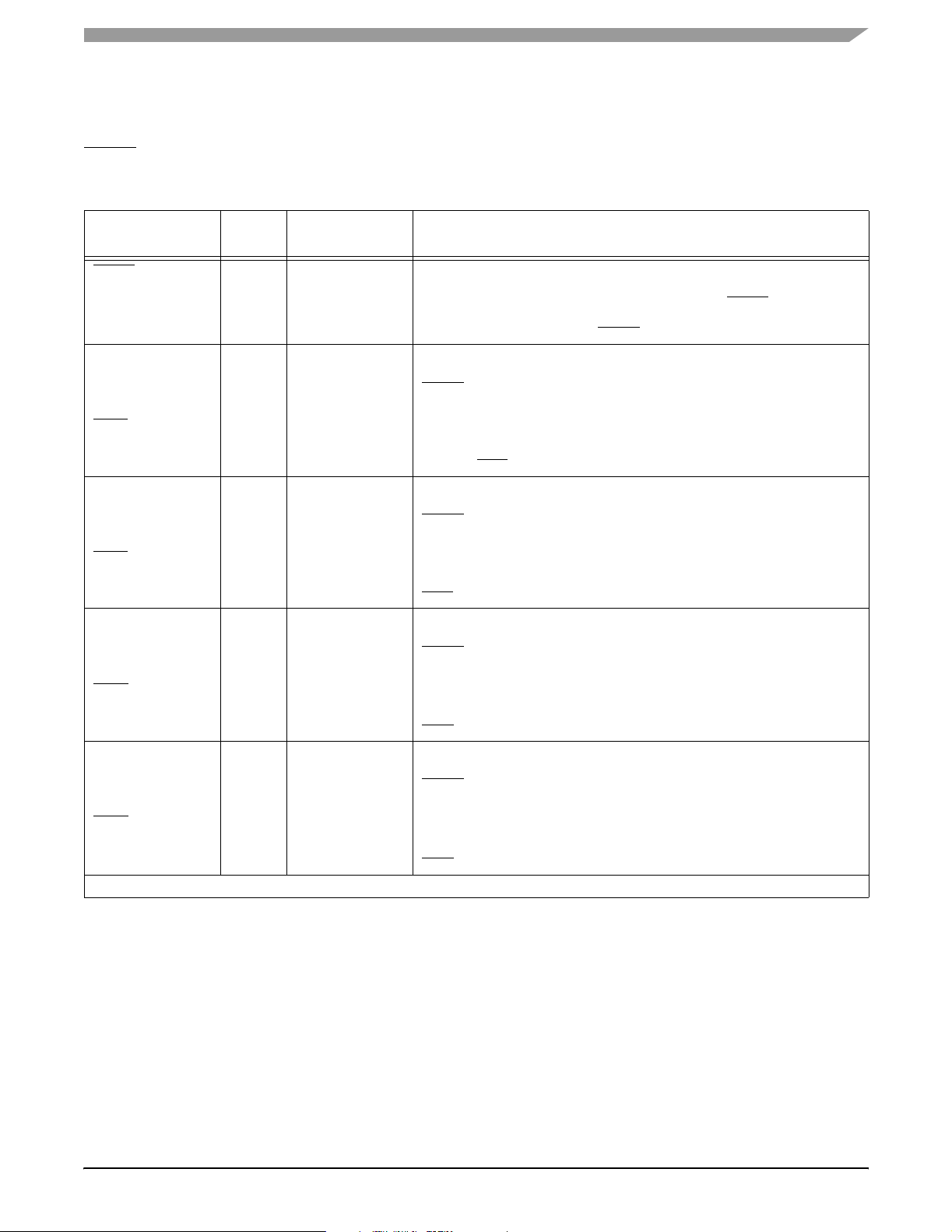

616

EXTAL

XTAL

RESET

PINIT/NMI

Triple

Timer

Address

Generation

Unit

Six-Channel

DMA Unit

Bootstrap

ROM

Internal

Data

Bus

Switch

Clock

Generator

PLL

2

6

HI08 ESSI SCI

Expansion Area

PIO_EB

Program

Interrupt

Controller

MODA/IRQA

MODB/IRQB

MODC/IRQC

MODD/IRQD

Peripheral

Program

Decode

Controller

3

PrograM

RAM

20480 × 24

bits

(default)

PM_EB

DSP56300

Program

Address

Generator

Memory Expansion Area

X Data

RAM

7168 × 24

bits

(default)

YA B

XAB

PA B

DAB

24-Bit

Core

DDB

YDB

XDB

PDB

GDB

24 × 24 + 56 → 56-bit MAC

Two 56-bit Accumulators

56-bit Barrel Shifter

XM_EB

Data ALU

Y Data

RAM

7168 × 24

bits

(default)

YM_EB

External

Address

External

Interface

and Inst.

External

Data Bus

Bus

Switch

Bus

Cache

Control

Switch

Powe r

Management

JTAG

OnCE™

18

Address

13

Control

24

Data

DE

DSP56309

Rev. 7, 2/2005

The DSP56309 is intended

for applications benefiting

from a large amount of

internal memory, such as

wireless infrastructure

applications.

What’s New?

Rev. 7 includes the following

changes:

• Adds lead-free packaging and

5

part numbers.

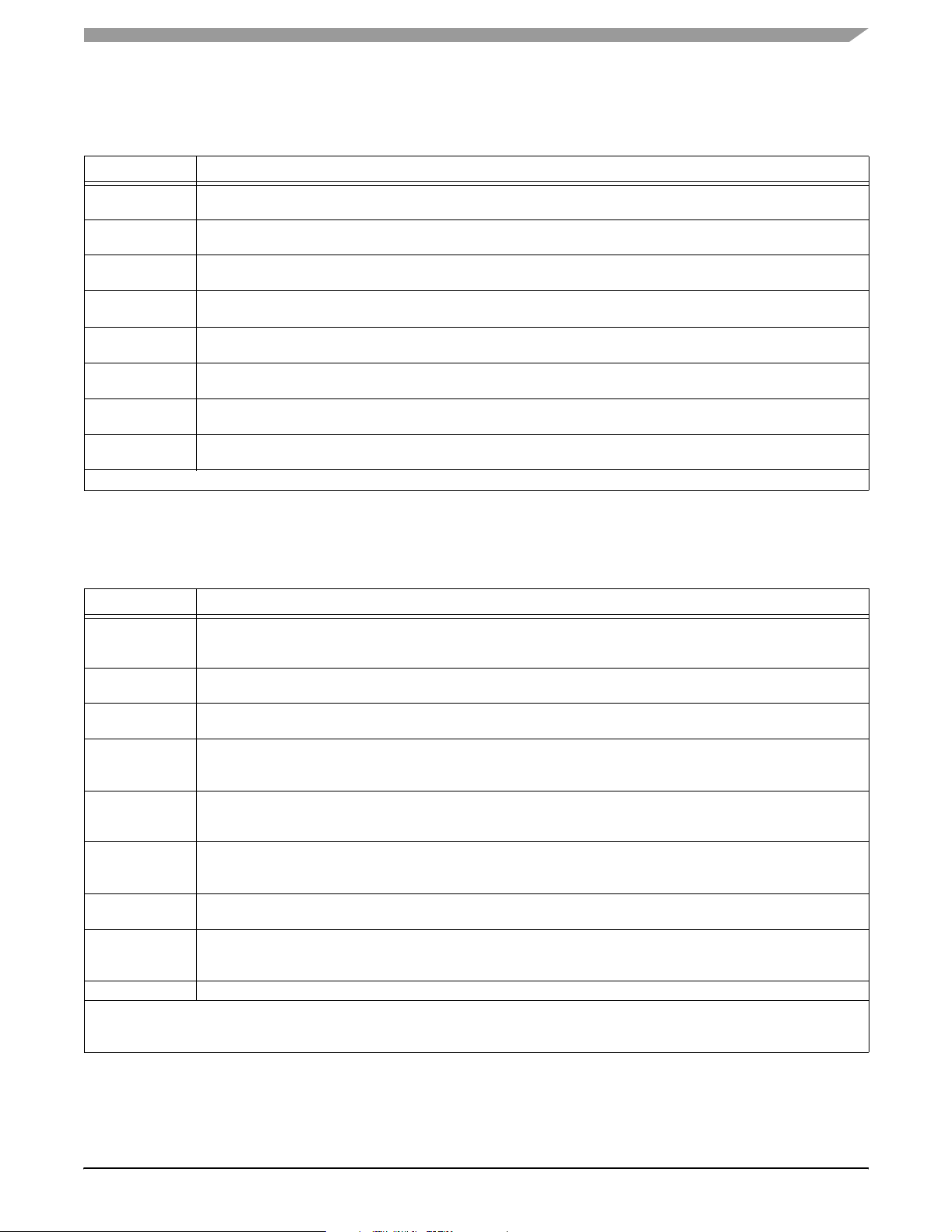

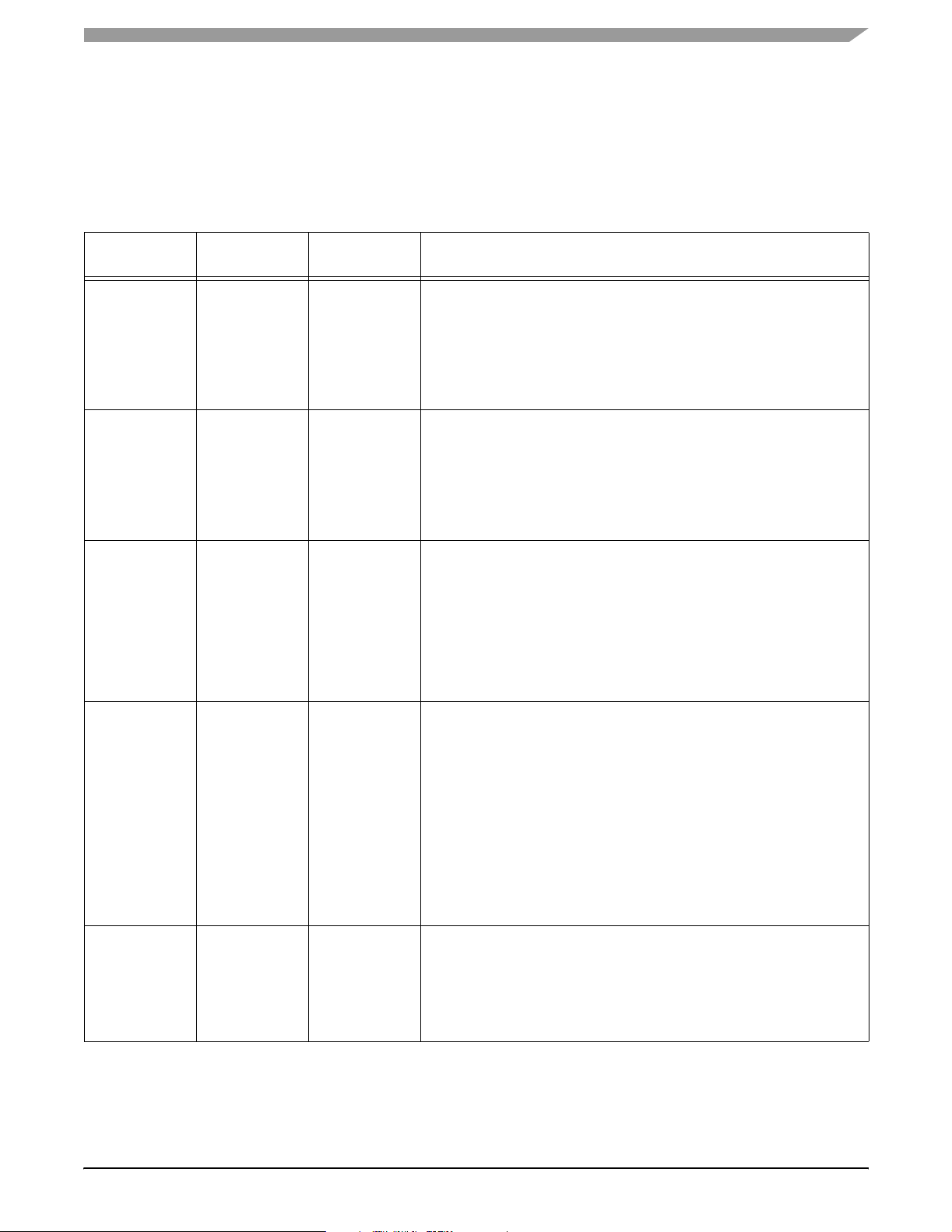

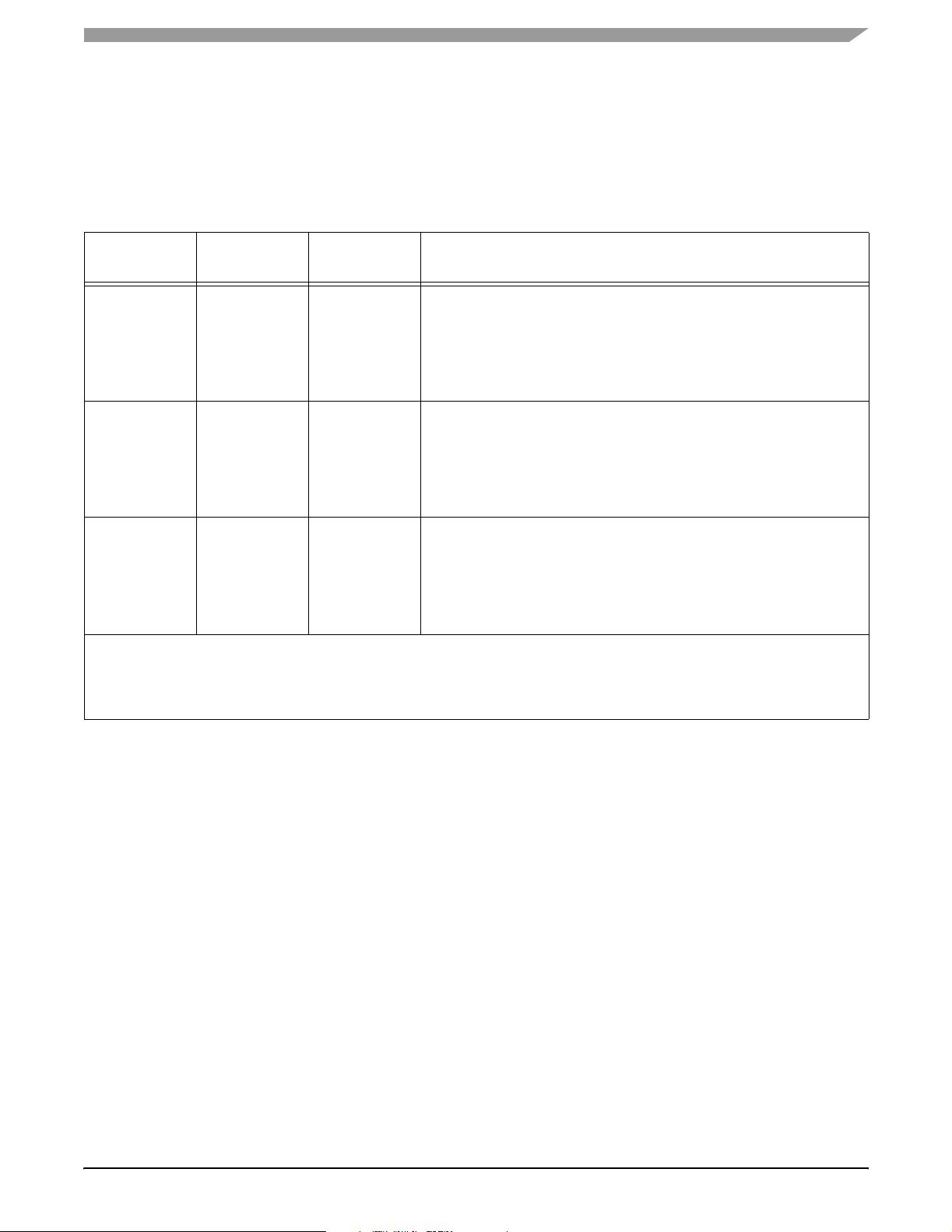

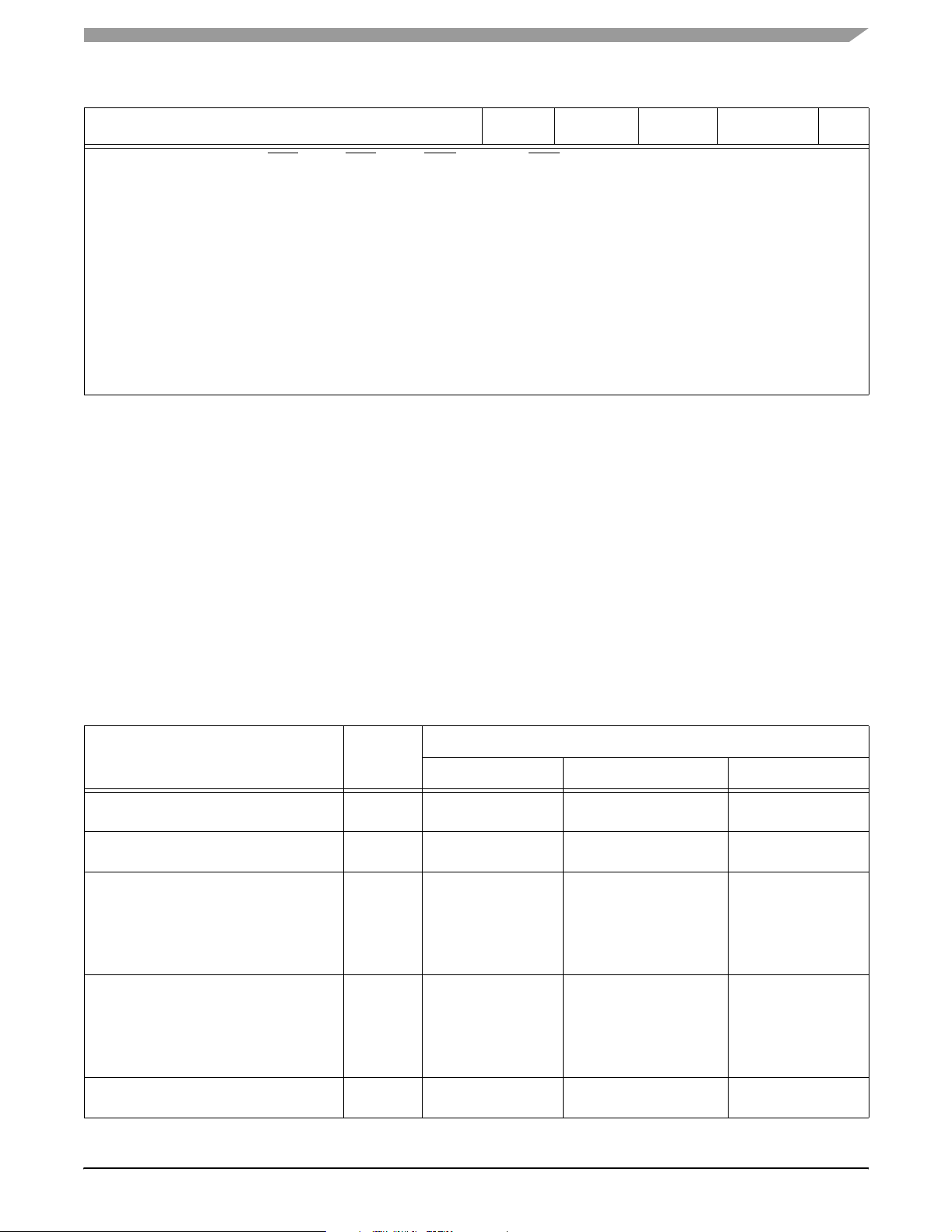

Figure 1. DSP56309 Block Diagram

The DSP56309 is a member of the DSP56300 core family of programmable CMOS DSPs. The DSP56300 core

includes a barrel shifter, 24-bit addressing, an instruction cache, and direct memory access (DMA). The DSP56309

offers 100 MMACS at 3.0–3.6 V using an internal 100 MHz clock. The large internal memory is ideal for wireless

infrastructure and wireless local-loop applications. The DSP56300 core family offers a new level of performance in

speed and power provided by its rich instruction set and low-power dissipation, thus enabling a new generation of

wireless, multimedia, and telecommunications products.

Note: This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 1996, 2005. All rights reserved.

Table of Contents

Data Sheet Conventions .......................................................................................................................................ii

Features...............................................................................................................................................................iii

Target Applications .............................................................................................................................................iv

Product Documentation ......................................................................................................................................iv

Chapter 1 Signals/Connections

1.1 Power ................................................................................................................................................................1-3

1.2 Ground ..............................................................................................................................................................1-3

1.3 Clock .................................................................................................................................................................1-4

1.5 External Memory Expansion Port (Port A) ......................................................................................................1-4

1.6 Interrupt and Mode Control ..............................................................................................................................1-7

1.7 Host Interface (HI08) ........................................................................................................................................1-8

1.8 Enhanced Synchronous Serial Interface 0 (ESSI0) ........................................................................................1-11

1.9 Enhanced Synchronous Serial Interface 1 (ESSI1) ........................................................................................1-12

1.10 Serial Communication Interface (SCI) ...........................................................................................................1-14

1.11 Timers .............................................................................................................................................................1-15

1.12 JTAG and OnCE Interface ..............................................................................................................................1-16

Chapter 2 Specifications

2.1 Maximum Ratings.............................................................................................................................................2-1

2.3 Thermal Characteristics ....................................................................................................................................2-2

2.4 DC Electrical Characteristics ............................................................................................................................2-2

2.5 AC Electrical Characteristics ............................................................................................................................2-3

Chapter 3 Packaging

3.1 TQFP Package Description...............................................................................................................................3-2

3.2 TQFP Package Mechanical Drawing................................................................................................................3-9

3.3 MAP-BGA Package Description ....................................................................................................................3-10

3.4 MAP-BGA Package Mechanical Drawing .....................................................................................................3-18

Chapter 4 Design Considerations

4.1 Thermal Design Considerations........................................................................................................................4-1

4.2 Electrical Design Considerations ......................................................................................................................4-2

4.3 Power Consumption Considerations .................................................................................................................4-3

4.4 PLL Performance Issues ...................................................................................................................................4-4

4.5 Input (EXTAL) Jitter Requirements .................................................................................................................4-5

Appendix A Power Consumption Benchmark

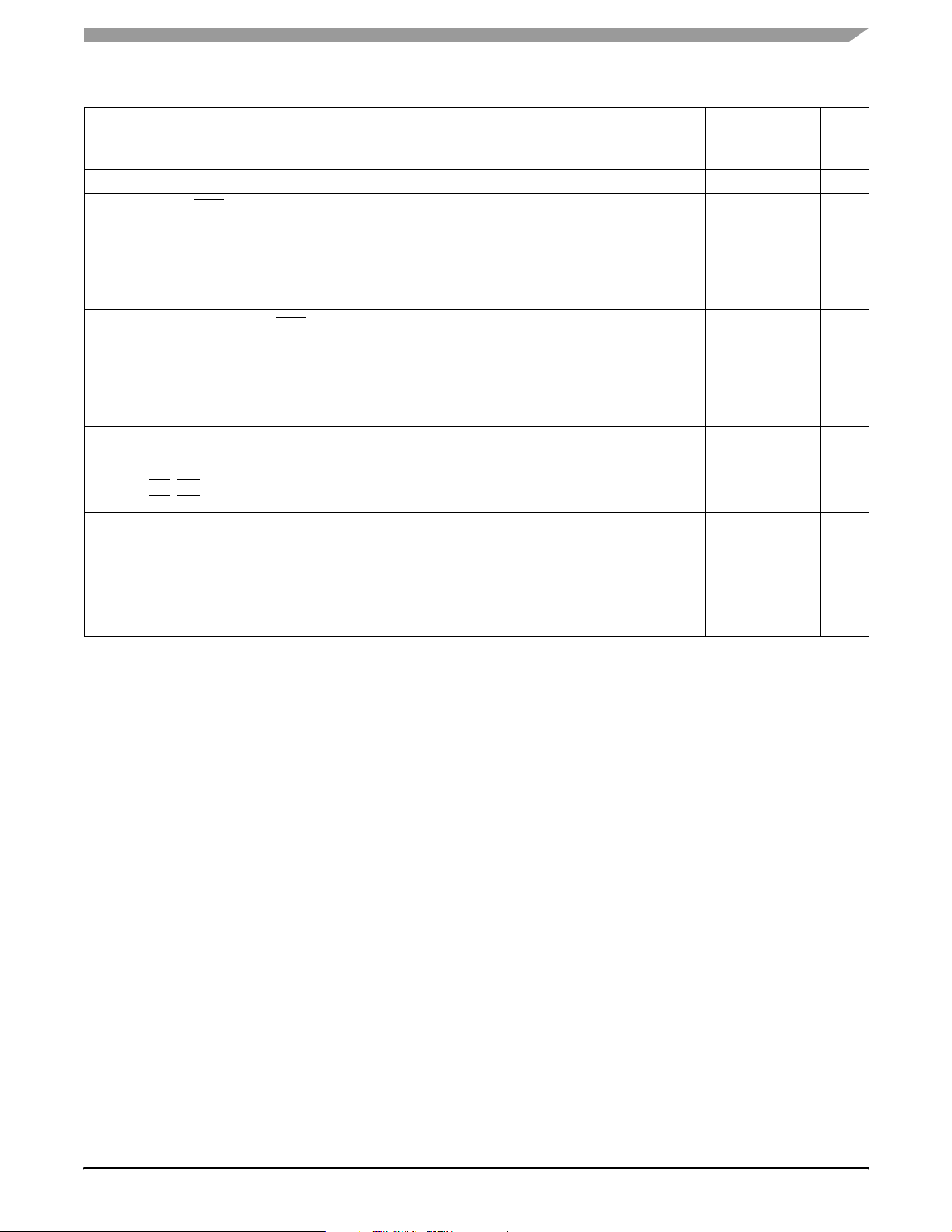

Data Sheet Conventions

OVERBAR

“asserted” Means that a high true (active high) signal is high or that a low true (active low) signal is low

“deasserted” Means that a high true (active high) signal is low or that a low true (active low) signal is high

Examples: Signal/Symbol Logic State Signal State Voltage

Note: Values for VIL, VOL, VIH, and VOH are defined by individual product specifications.

ii Freescale Semiconductor

Indicates a signal that is active when pulled low (For example, the RESET pin is active when

low.)

PIN

PIN

PIN

PIN

True Asserted

False Deasserted

True Asserted

False Deasserted

DSP56309 Technical Data, Rev. 7

VIL/V

VIH/V

VIH/V

VIL/V

OL

OH

OH

OL

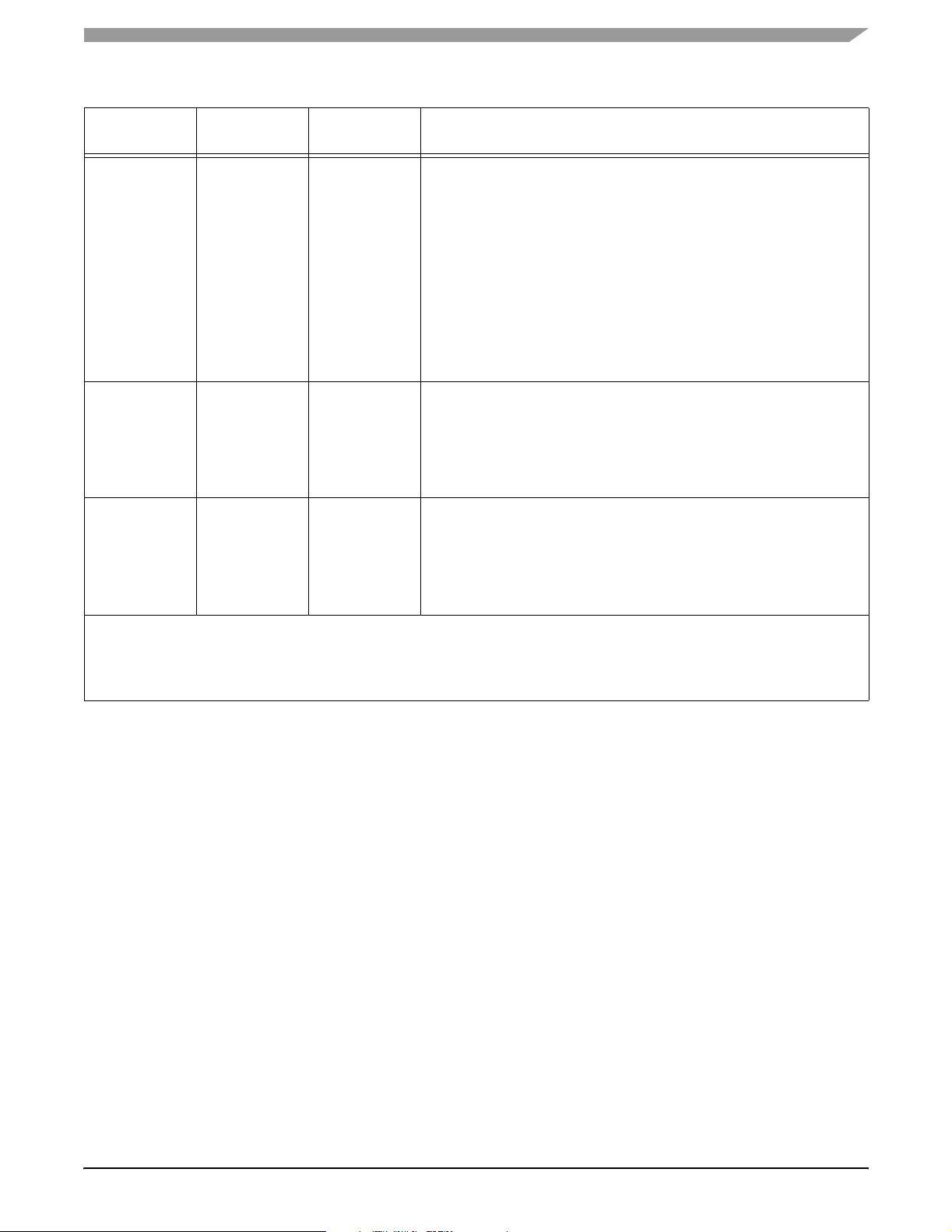

Features

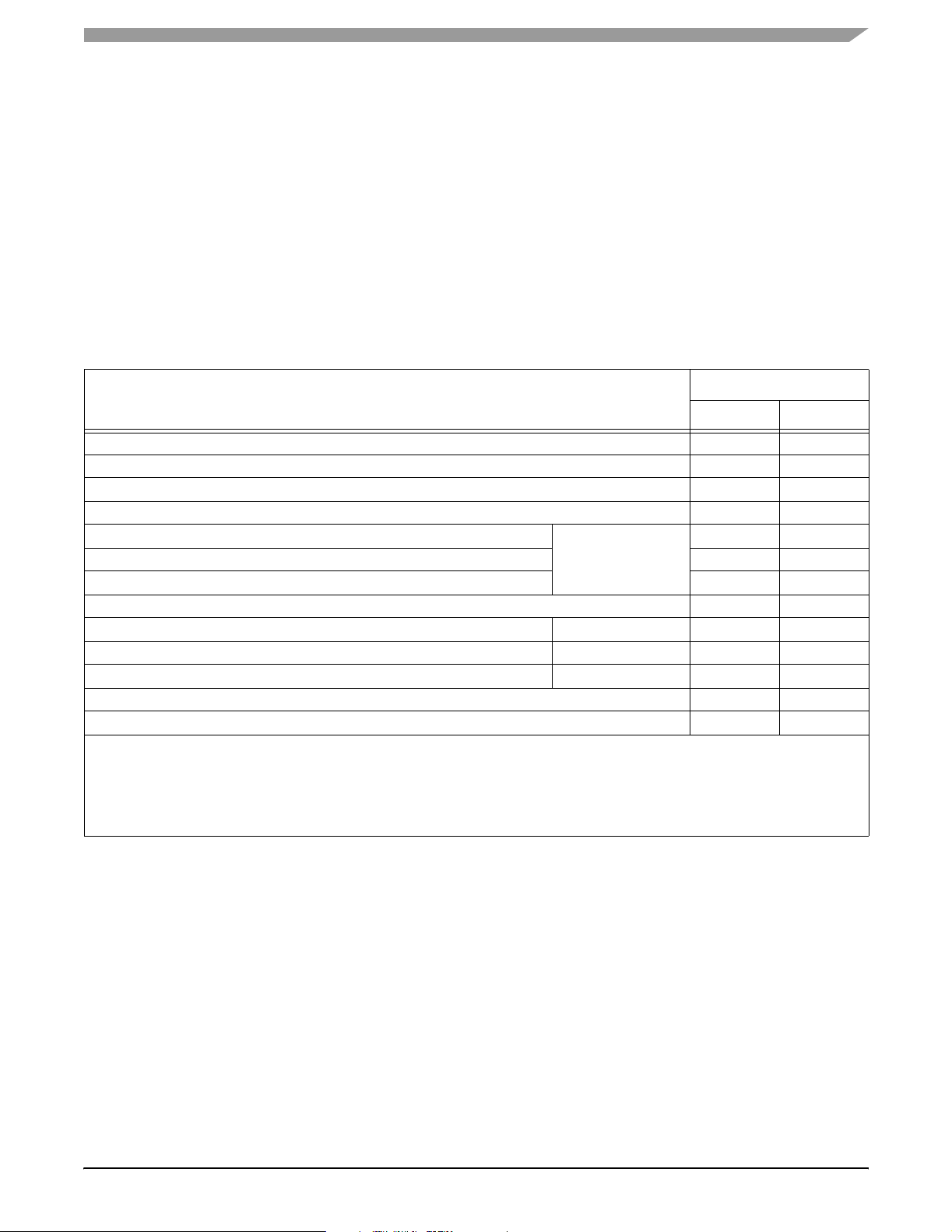

Tabl e 1 lists the features of the DSP56309 device.

Table 1. DSP56309 Features

Feature Description

• 100 million multiply-accumulates per second (MMACS) with a 100 MHz clock at 3.3 V nominal

• Data arithmetic logic unit (Data ALU) with fully pipelined 24 × 24-bit parallel multiplier-accumulator (MAC),

56-bit parallel barrel shifter (fast shift and normalization; bit stream generation and parsing), conditional

ALU instructions, and 24-bit or 16-bit arithmetic support under software control

• Program control unit (PCU) with position-independent code (PIC) support, addressing modes optimized for

High-Performance

DSP56300 Core

Internal Peripherals

DSP applications (including immediate offsets), internal instruction cache controller, internal memoryexpandable hardware stack, nested hardware DO loops, and fast auto-return interrupts

• Direct memory access (DMA) with six DMA channels supporting internal and external accesses; one-, twoand three-dimensional transfers (including circular buffering); end-of-block-transfer interrupts; and

triggering from interrupt lines and all peripherals

• Phase-lock loop (PLL) allows change of low-power divide factor (DF) without loss of lock and output clock

with skew elimination

• Hardware debugging support including On-Chip Emulation (OnCE‘) module, Joint Test Action Group

(JTAG) test access port (TAP)

• Enhanced 8-bit parallel host interface (HI08) supports a variety of buses (for example, ISA) and provides

glueless connection to a number of industry-standard microcomputers, microprocessors, and DSPs

• Two enhanced synchronous serial interfaces (ESSI), each with one receiver and three transmitters (allows

six-channel home theater)

• Serial communications interface (SCI) with baud rate generator

• Triple timer module

• Up to thirty-four programmable general-purpose input/output (GPIO) pins, depending on which peripherals

are enabled

•192 × 24-bit bootstrap ROM

•8 K × 24-bit RAM total

• Program RAM, instruction cache, X data RAM, and Y data RAM sizes are programmable:

Internal Memories

External Memory

Expansion

Power Dissipation

Packaging

Program RAM

Size

20480 × 24 bits 0 7168 × 24 bits 7168 × 24 bits disabled disabled

19456 × 24 bits 1024 × 24-bit 7168 × 24 bits 7168 × 24 bits enabled disabled

24576 × 24 bits 0 5120 × 24 bits 5120 × 24 bits disabled enabled

23552 × 24 bits 1024 × 24-bit 5120 × 24 bits 5120 × 24 bits enabled enabled

• Data memory expansion to two 256 K × 24-bit word memory spaces using the standard external address

lines

• Program memory expansion to one 256 K × 24-bit words memory space using the standard external

address lines

• External memory expansion port

• Chip select logic for glueless interface to static random access memory (SRAMs)

• Internal DRAM Controller for glueless interface to dynamic random access memory (DRAMs)

• Very low-power CMOS design

• Wait and Stop low-power standby modes

• Fully static design specified to oper ate down to 0 Hz (dc)

• Optimized power management circuitry (instruction-dependent, peripheral-dependent, and modedependent)

• 144-pin TQFP package in lead-free or lead-bearing versions

• 196-pin molded array plastic-ball grid array (MAP-BGA) package in lead-free or lead-bearing versions

Instruction

Cache Size

X Data RAM

Size

Y Data RAM

Size

Instruction

Cache

Switch Mode

Freescale Semiconductor

DSP56309 Technical Data, Rev. 7

iii

Target Applications

The DSP56309 is intended for applications benefiting from a large amount of internal memory, such as wireless

infrastructure applications.

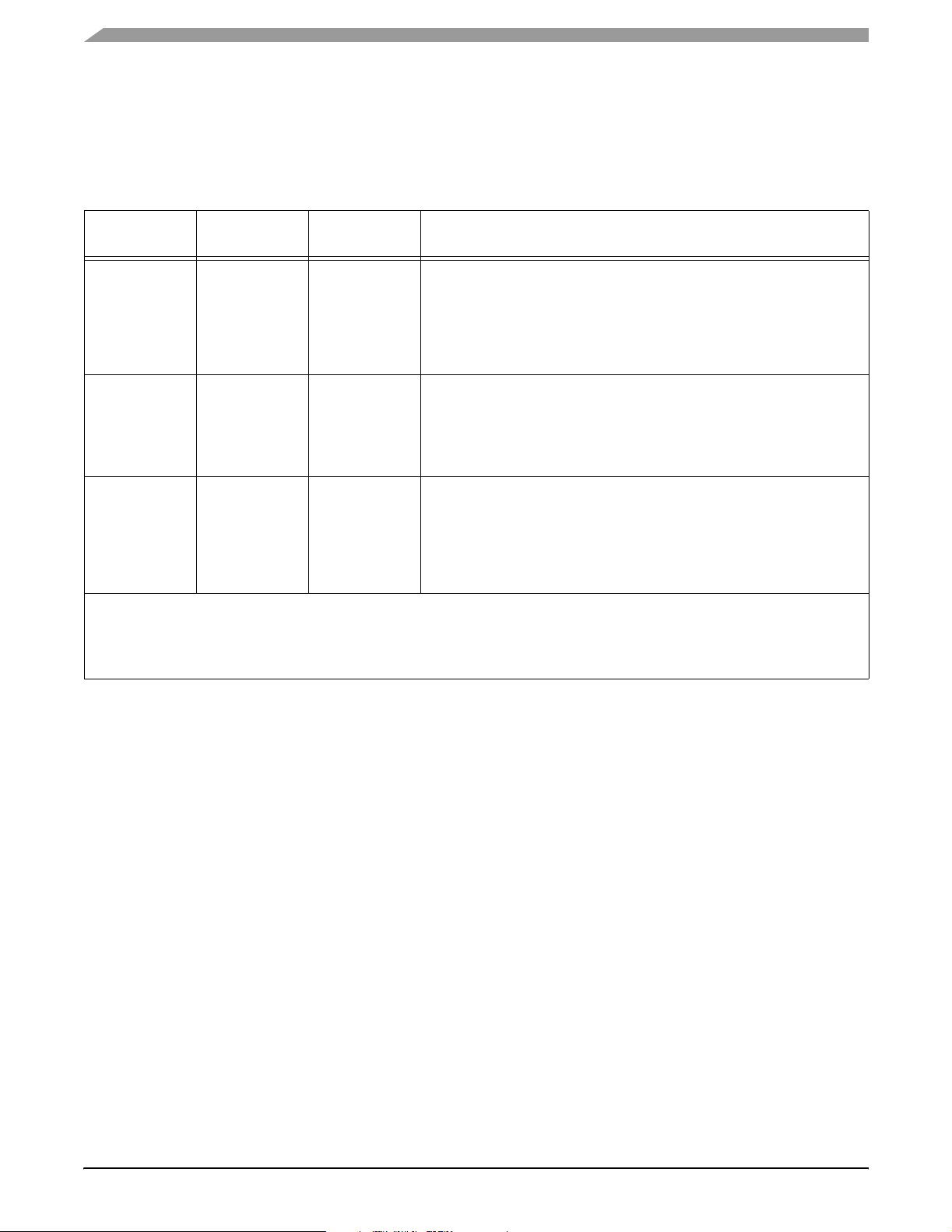

Product Documentation

The documents listed in Tabl e 2 are required for a complete description of the DSP56309 device and are necessary

to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale

semiconductor sales office, or a Freescale Semiconductor Literature Distribution Center. For documentation

updates, visit the Freescale DSP website. See the contact information on the back cover of this document.

Table 2. DSP56309 Documentation

Name Description Order Number

DSP56309

User’s Manual

DSP56300 Family

Manual

Application Notes Documents describing specific applications or optimized device operation

Detailed functional description of the DSP56309 memory configuration,

operation, and register programming

Detailed description of the DSP56300 family processor core and instruction set DSP56300FM

including code examples

DSP56309UM

See the DSP56309 product website

DSP56309 Technical Data, Rev. 7

iv Freescale Semiconductor

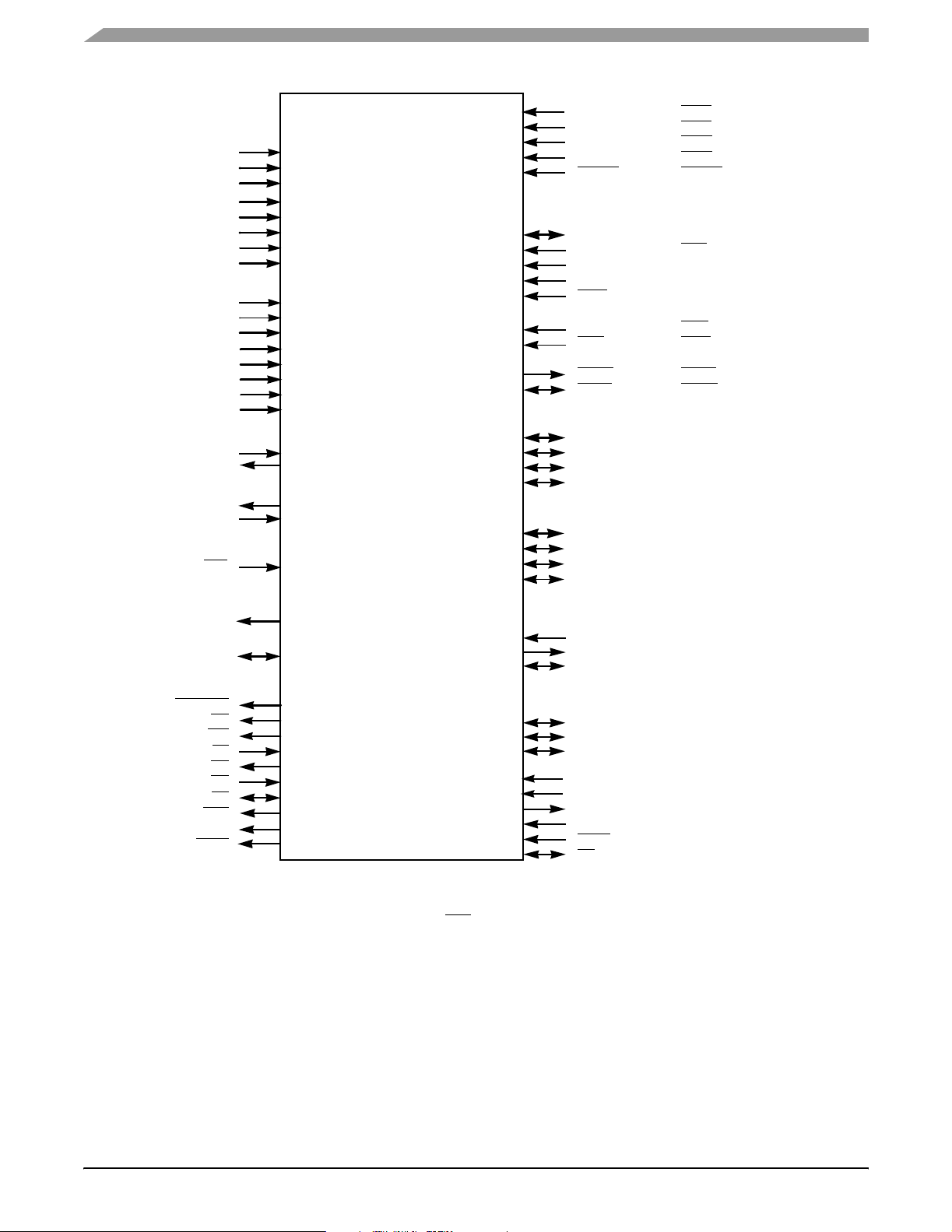

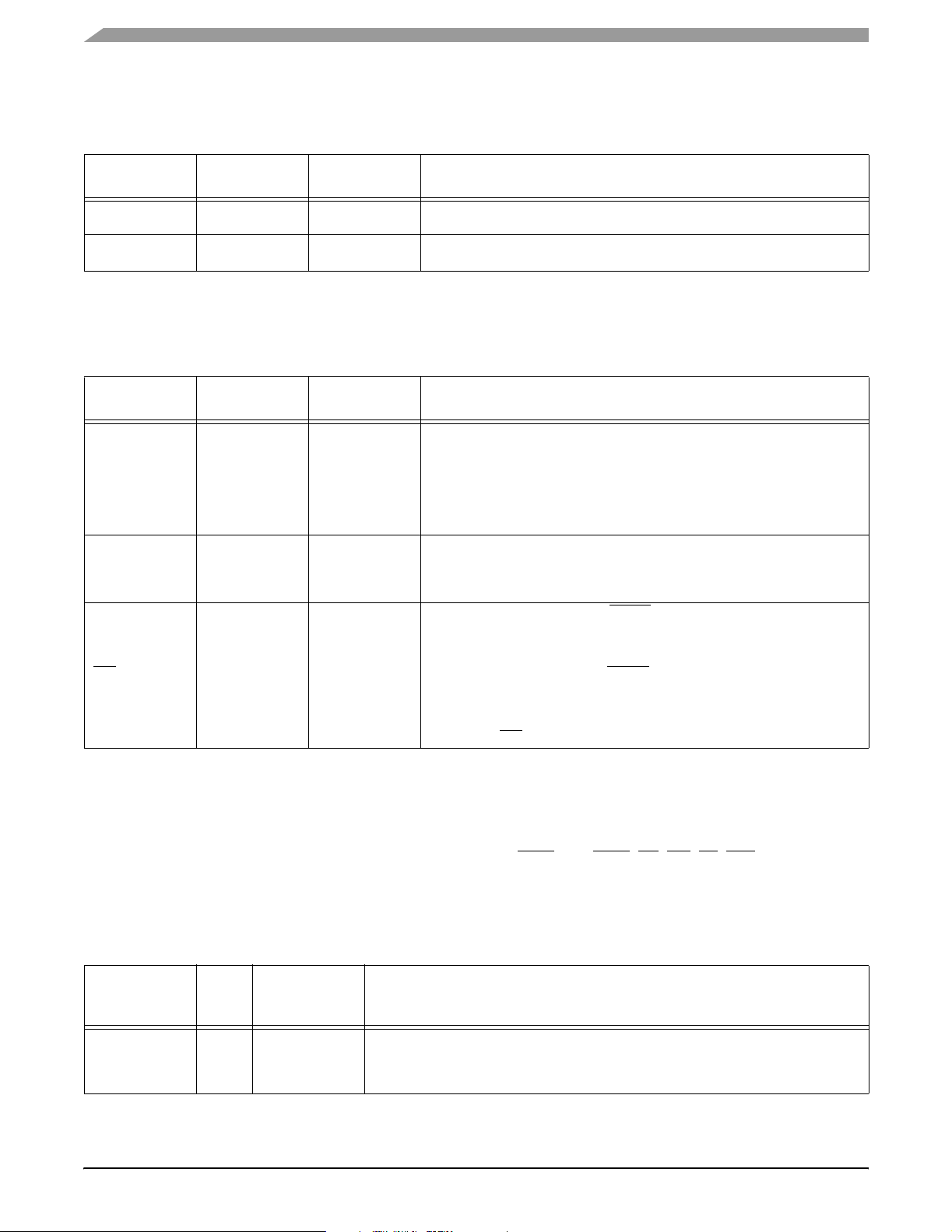

Signals/Connections 1

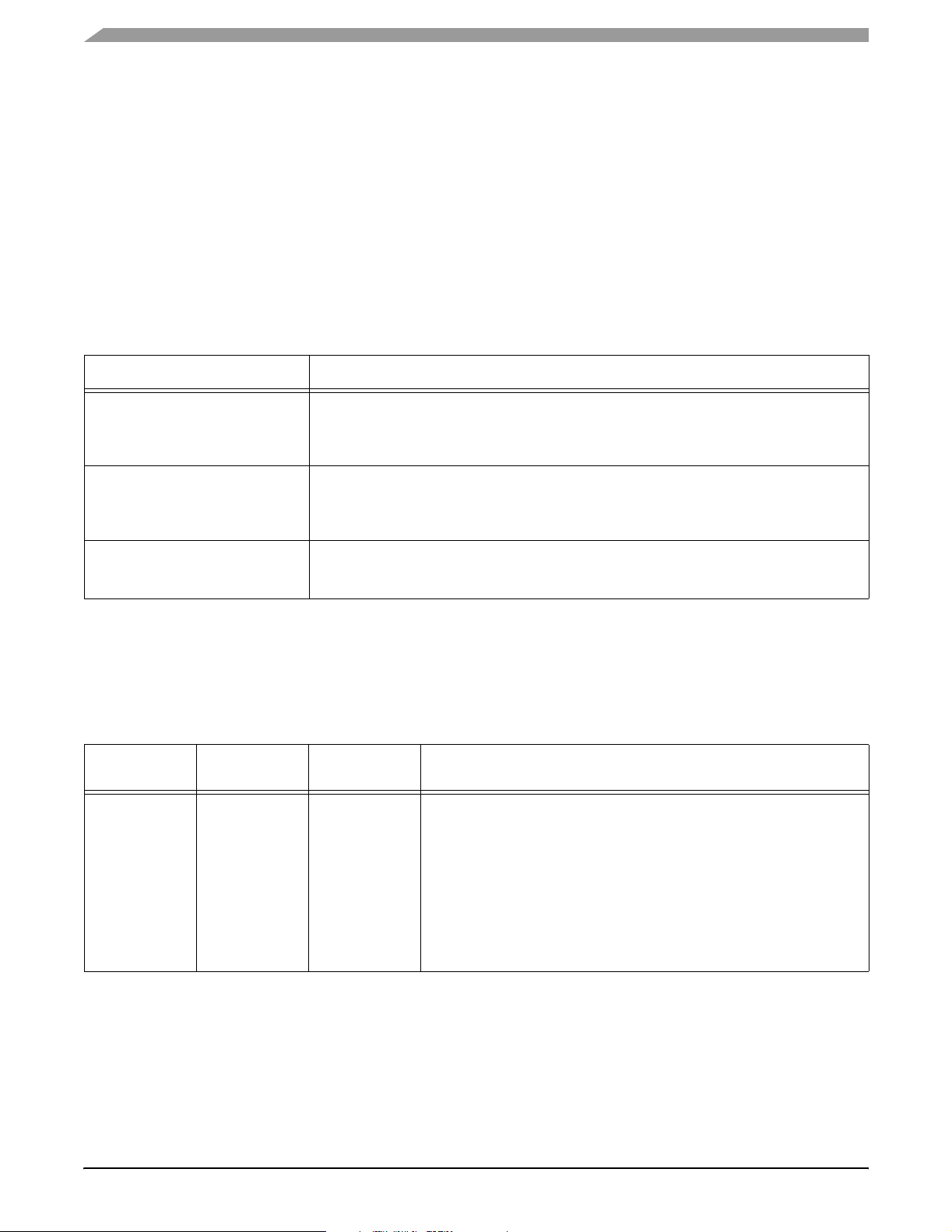

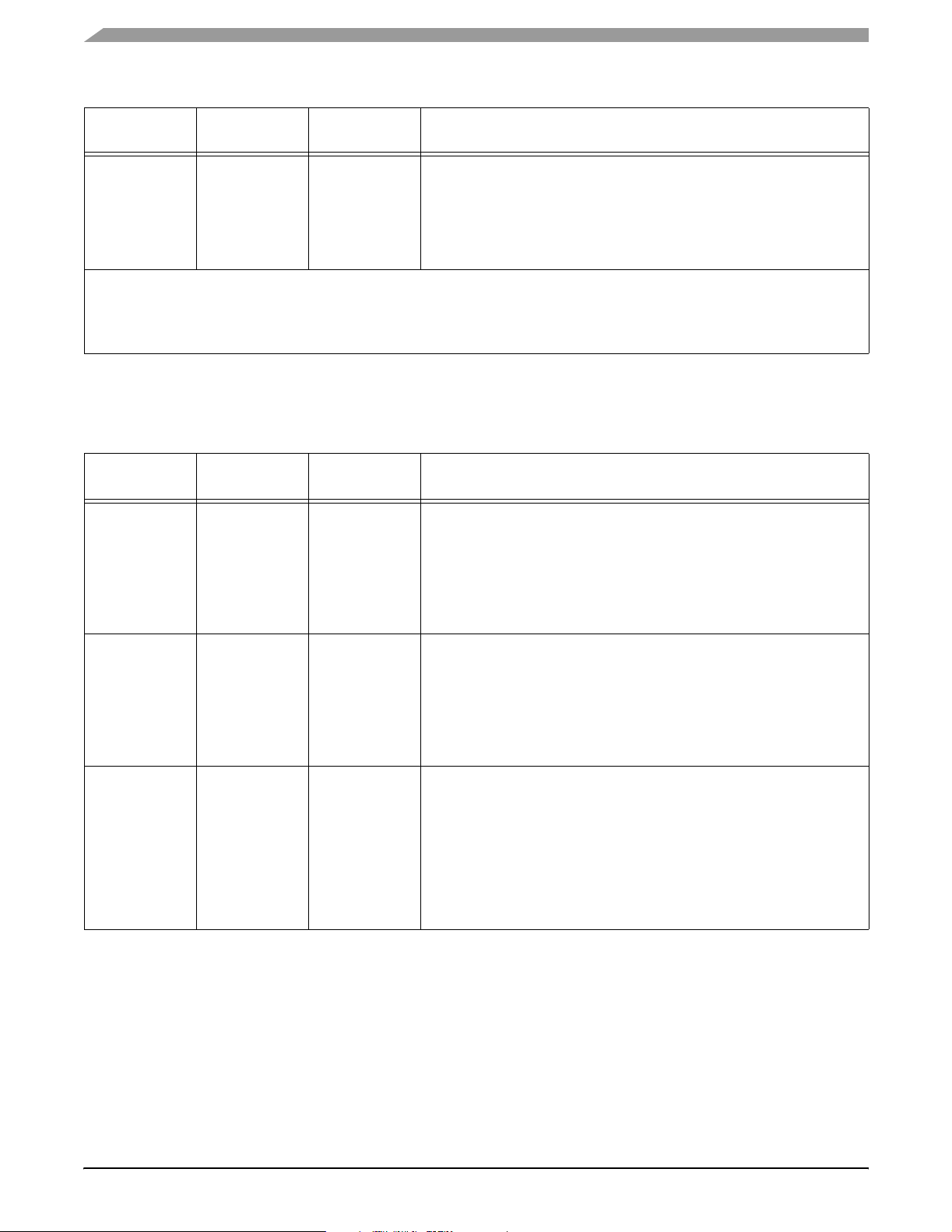

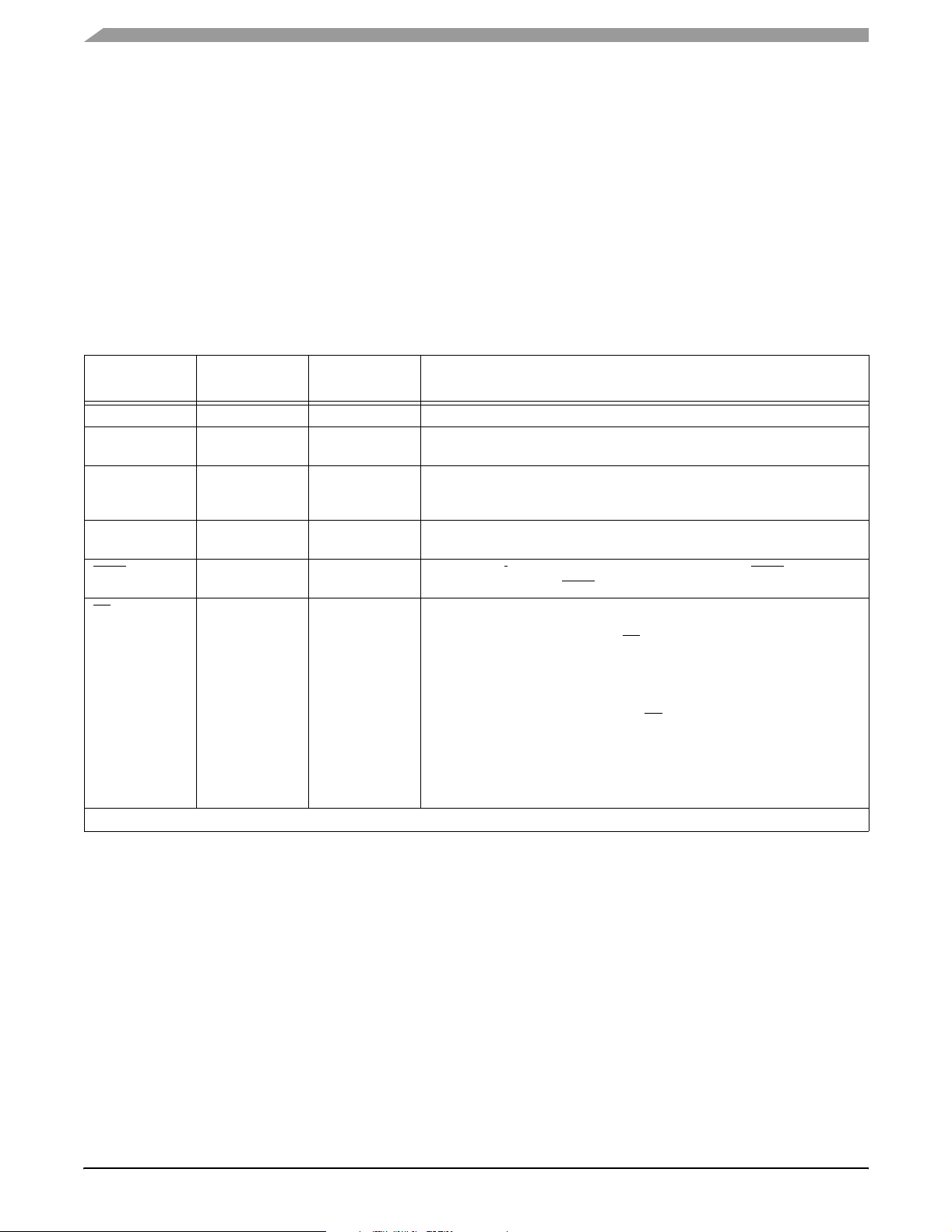

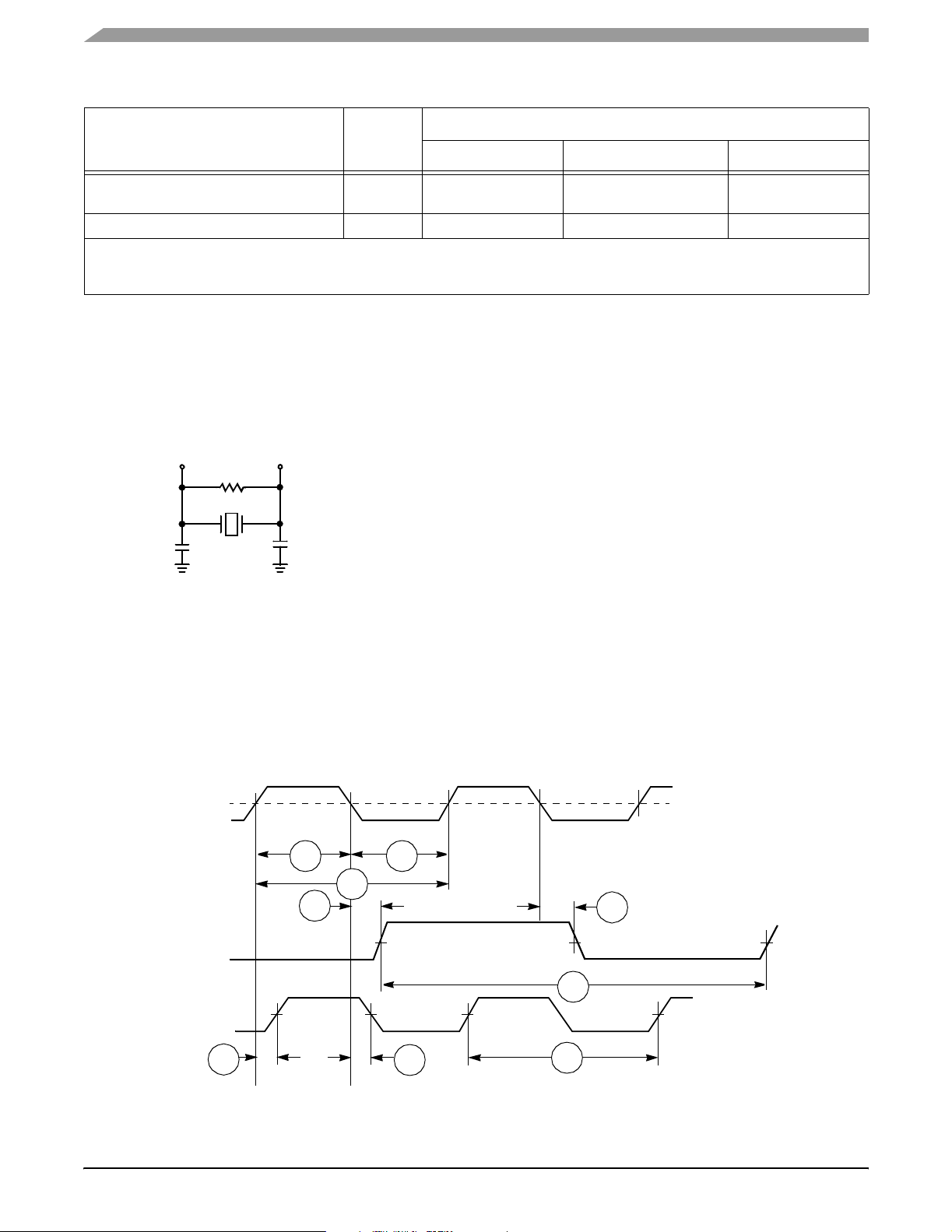

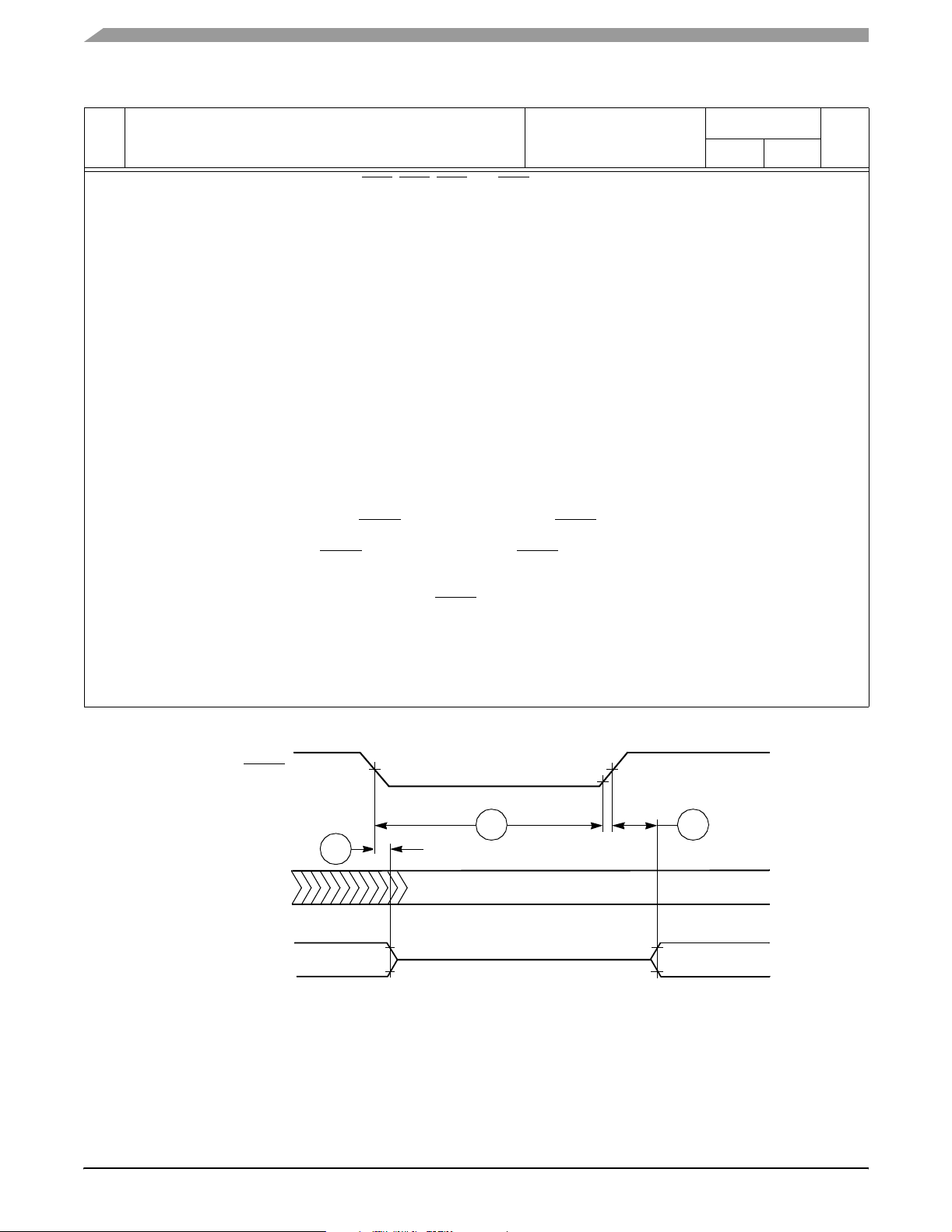

The DSP56309 input and output signals are organized into functional groups as shown in Table 1-1 . Figure 1-1

diagrams the DSP56309 signals by functional group. The remainder of this chapter describes the signal pins in

each functional group.

Table 1-1. DSP56309 Functional Signal Groupings

Functional Group

Number of Signals

TQFP MAP-BGA

Power (VCC) 20 20

Ground (GND) 19 66

Clock 22

PLL 33

Address bus

Data bus 24 24

Bus control 13 13

Interrupt and mode control 55

Host interface (HI08) Port B

Enhanced synchronous serial interface (ESSI) Ports C and D

Serial communication interface (SCI) Port E

Timer 33

OnCE/JTAG Port 66

Notes: 1. Port A signals define the external memory interface port, including the external address bus, data bus, and control signals.

2. Port B signals are the HI08 port signals multiplexed with the GPIO signals.

3. Port C and D signals are the two ESSI port signals multiplexed with the GPIO signals.

4. Port E signals are the SCI port signals multiplexed with the GPIO signals.

5. There are 2 signal connections in the TQFP package and 7 signal connections in the MAP-BGA package that are not used.

These are designated as no connect (NC) in the package description (see Chapter 3).

Port A

1

2

3

4

18 18

16 16

12 12

33

Note: This chapter refers to a number of configuration registers used to select individual multiplexed signal

functionality. Refer to the DSP56309 User’s Manual for details on these configuration registers.

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 1-1

Signals/Connections

During

Reset

PINIT

V

CCP

V

CCQL

V

CCQH

V

CCA

V

CCD

V

CCC

V

CCH

V

CCS

GND

GND

GND

GND

GND

GND

GND

GND

EXTAL

XTAL

CLKOUT

PCAP

After

Reset

NMI

A[0–17]

D[0–23]

DSP56309

Power Inputs:

PLL

4

Internal Logic

3

I/O

3

Address Bus

4

Data Bus

2

Bus Control

HI08

2

ESSI/SCI/Timer

Grounds4:

4

4

2

2

PLL

PLL

Internal Logic

Address Bus

Data Bus

Bus Control

HI08

ESSI/SCI/Timer

Clock

Synchronous Serial

P

P1

Q

A

D

C

H

S

Interrupt/

Mode Control

Host

Interface

(HI08) Port

Enhanced

Interface Port 0

(ESSI0)

1

2

During Reset

MODA

MODB

MODC

MODD

RESET

Non-Multiplexed

Bus

8

H[0–7]

HA0

HA1

HA2

HCS/

Single DS

HRW

HDS

Single HR

HREQ

HACK

3

SC0[0–2]

SCK0

SRD0

STD0

HCS

/HDS

/HREQ

/HACK

PLL

Enhanced

Synchronous Serial

Interface Port 1

(ESSI1)

3

SC1[0–2]

SCK1

2

SRD1

STD1

After Reset

IRQA

IRQB

IRQC

IRQD

RESET

Multiplexed

Bus

HAD[0–7]

HAS

/HAS

HA8

HA9

HA10

Double DS

HRD

/HRD

HWR

/HWR

Double HR

HTRQ

/HTRQ

HRRQ

/HRRQ

Port C GPIO

PC[0–2]

PC3

PC4

PC5

Port D GPIO

PD[0–2]

PD3

PD4

PD5

Port B

GPIO

PB[0–7]

PB8

PB9

PB10

PB13

PB11

PB12

PB14

PB15

Port A

18

24

External

Address Bus

External

Data Bus

Serial

Communications

Interface (SCI) Port

2

TXD

SCLK

RXD

Port E GPIO

PE0

PE1

PE2

AA[0–3]/RAS[

0–3]

RD

WR

TA

BR

BG

BB

CAS

BCLK

BCLK

4

External

Bus

Control

Timers

OnCE/

JTAG Port

3

TIO0

TIO1

TIO2

TCK

TDI

TDO

TMS

TRST

DE

Timer GPIO

TIO0

TIO1

TIO2

Notes: 1. The HI08 port supports a non-multiplexed or a multiplexed bus, single or double Data Strobe (DS), and single or

double Host Request (HR) configurations. Since each of these modes is configured independently, any combination

of these modes is possible. These HI08 signals can also be configured alternatively as GPIO signals (PB[0–15]).

Signals with dual designations (for example, HAS

/HAS) have configurable polarity.

2. The ESSI0, ESSI1, and SCI signals are multiplexed with the Port C GPIO signals (PC[0–5]), Port D GPIO signals

(PD[0–5]), and Port E GPIO signals (PE[0–2]), respectively.

3. TIO[0–2] can be configured as GPIO signals.

4. Ground connections shown in this figure are for the TQFP package. In the MAP-BGA package, in addition to the

GND

and GNDP1 connections, there are 64 GND connections to a common internal package ground plane.

P

Figure 1-1. Signals Identified by Functional Group

DSP56309 Technical Data, Rev. 7

1-2 Freescale Semiconductor

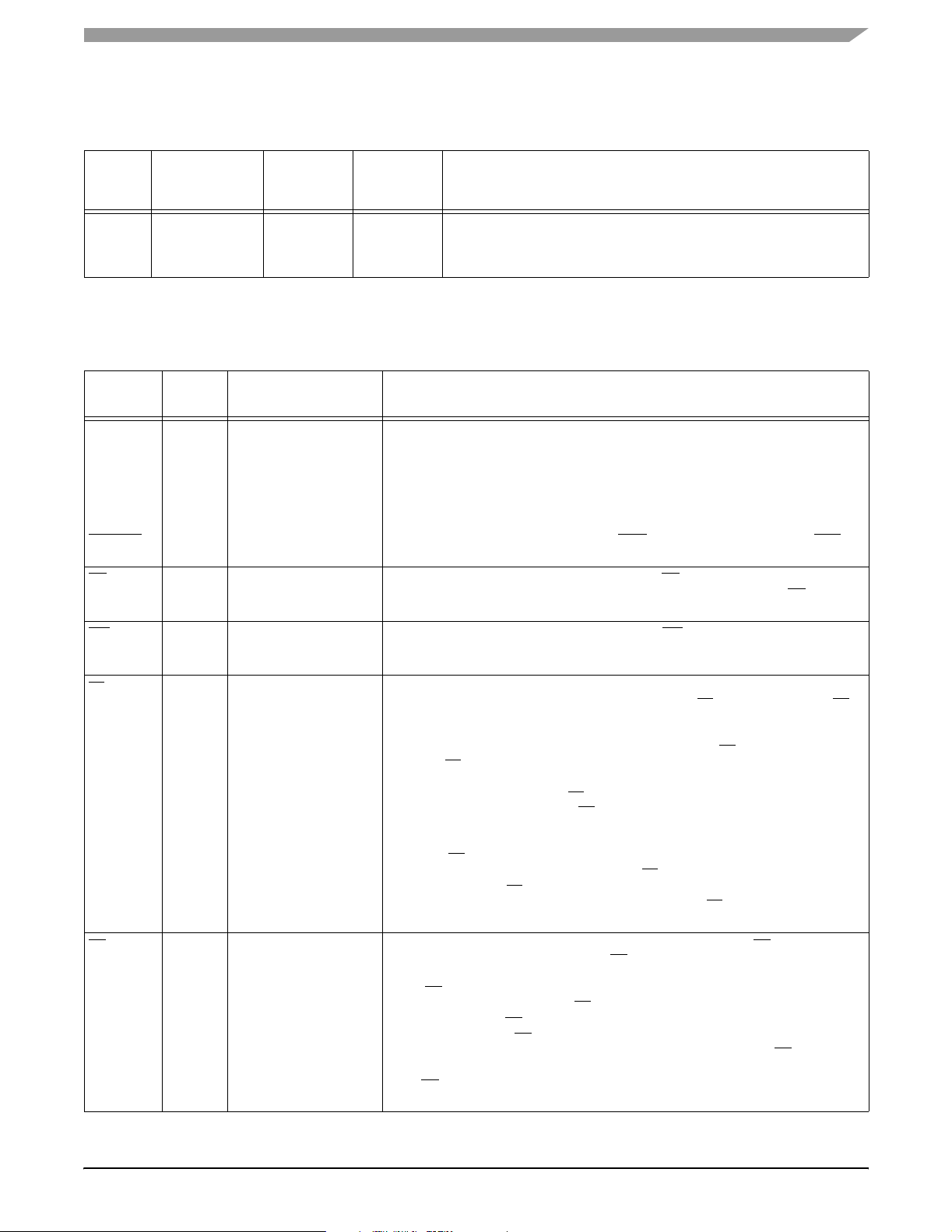

1.1 Power

Table 1-2. Power Inputs

Power Name Description

V

CCP

Quiet Power (core)—An isolated power for the core processing logic. This input must be isolated externally from all

V

CCQL

V

Quiet External (High) Power—A quiet power source for I/O lines. This input must be tied externally to all other chip

CCQH

Address Bus Power—An isolated power for sections of the address bus I/O drivers. This input must be tied externally

V

CCA

Data Bus Power—An isolated power for sections of the data bus I/O drivers. This input must be tied externally to all

V

CCD

Bus Control Power—An isolated power for the bus control I/O drivers. This input must be tied externally to all other

V

CCC

V

CCH

V

CCS

Note: The user must provide adequate external decoupling capacitors for all power connections.

PLL Power—VCC dedicated for PLL use. The voltage should be well-regulated and the input should be provided with

an extremely low impedance path to the V

power rail.

CC

other chip power inputs.

power inputs

to all other chip power inputs,

other chip power inputs,

chip power inputs,

, except

V

CCQL

except

.

except

V

CCQL

except

V

CCQL

.

V

.

CCQL

.

Host Power—An isolated power for the HI08 I/O drivers. This input must be tied externally to all other chip power

inputs,

except

V

.

CCQL

ESSI, SCI, and Timer Power—An isolated power for the ESSI, SCI, and timer I/O drivers. This input must be tied

externally to all other chip power inputs,

except

V

CCQL

.

Power

1.2 Ground

Table 1-3. Grounds

Ground Name Description

GND

P

GND

P1

2

GND

Q

2

GND

A

2

GND

D

2

GND

C

2

GND

H

2

GND

S

3

GND

Notes: 1. The user must provide adequate external decoupling capacitors for all GND connections.

2. These connections are only used on the TQFP package.

3. These connections are common grounds used on the MAP-BGA package.

PLL Ground—Ground-dedicated for PLL use. The connection should be provided with an extremely low-impedance

path to ground. V

package.

should be bypassed to GNDP by a 0.47 µF capacitor located as close as possible to the chip

CCP

PLL Ground 1—Ground-dedicated for PLL use. The connection should be provided with an extremely low-impedance

path to ground.

Quiet Ground—An isolated gr ound for the internal processing logic. This connection must be tied externally to all other

chip ground connections, except GND

and GNDP1. The user must provide adequate external decoupling capacitors.

P

Address Bus Ground—An isolated ground for sections of the address bus I/O drivers. This connection must be tied

externally to all other chip ground connections, except GND

decoupling capacitors.

Data Bus Ground—An isolated ground for sections of the data bus I/O drivers. This connection must be tied externally

to all other chip ground connections, except GND

capacitors.

and GNDP1. The user must provide adequate external decoupling

P

Bus Control Ground—An isolated ground for the bus control I/O drivers. This connection must be tied externally to all

other chip ground connections, except GND

capacitors.

and GNDP1. The user must provide adequate external decoupling

P

Host Ground—An isolated ground for the HI08 I/O drivers. This connection must be tied externally to all other chip

ground connections, except GND

and GNDP1. The user must provide adequate external decoupling capacitors.

P

ESSI, SCI, and Timer Ground—An isolated ground for the ESSI, SCI, and timer I/O drivers. This connection must be

tied externally to all other chip ground connections, except GND

decoupling capacitors.

Ground—Connected to an internal device ground plane.

1

and GNDP1. The user must provide adequate external

P

and GNDP1. The user must provide adequate external

P

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 1-3

Signals/Connections

1.3 Clock

Table 1-4. Clock Signals

Signal Name Type

EXTAL Input Input External Clock/Crystal Input—Interfaces the internal crystal oscillator input

XTAL Output Chip-driven Crystal Output—Connects the internal crystal oscillator output to an external

State During

Reset

Signal Description

to an external crystal or an external clock.

crystal. If an external clock is used, leave XTAL unconnected.

1.4 PLL

Table 1-5. Phase-Locked Loop Signals

Signal Name Type

CLKOUT Output Chip-driven Clock Output—Provides an output clock synchronized to the internal core

PCAP Input Input PLL Capacitor—An input connecting an off-chip capacitor to the PLL filter.

PINIT

Input

State During

Reset

clock phase.

If the PLL is enabled and both the multiplication and division factors equal one,

then CLKOUT is also synchronized to EXTAL.

If the PLL is disabled, the CLKOUT frequency is half the frequency of EXTAL.

Connect one capacitor terminal to PCAP and the other terminal to V

If the PLL is not used, PCAP can be tied to V

Input PLL Initial—During assertion of RESET, the value of PINIT is written into the

PLL enable (PEN) bit of the PLL control (PCTL) register, determining whether

the PLL is enabled or disabled.

Signal Description

, GND, or left floating.

CC

CCP

.

NMI

Input

Nonmaskable Interrupt—After RESET

instruction processing, this Schmitt-trigger input is the negative-edge-triggered

NMI request internally synchronized to CLKOUT.

Note: PINIT/NMI

can tolerate 5 V.

deassertion and during normal

1.5 External Memory Expansion Port (Port A)

Note: When the DSP56309 enters a low-power standby mode (stop or wait), it releases bus mastership and tri-

states the relevant Port A signals:

1.5.1 External Address Bus

State During

Signal Name Type

A[0–17] Output Tri-stated Address Bus—When the DSP is the bus master, A[0–17] are active-high outputs that

Reset, Stop, or

Wait

A[0–17], D[0–23], AA0/RAS0–AA3/RAS3, RD, WR, BB, CAS.

Table 1-6. External Address Bus Signals

Signal Description

specify the address for external program and data memory accesses. Otherwise, the

signals are tri-stated. To minimize power dissipation, A[0–17] do not change state w hen

external memory spaces are not being accessed.

DSP56309 Technical Data, Rev. 7

1-4 Freescale Semiconductor

1.5.2 External Data Bus

Table 1-7. External Data Bus Signals

External Memory Expansion Port (Port A)

Signal

Name

D[0–23] Input/ Output Ignored Input Last state:

Type

State

During

Reset

State

During Stop

or Wait

Input

: Ignored

Output

:

Tri-stated

1.5.3 External Bus Control

Table 1-8. External Bus Control Signals

Signal

Name

AA[0–3]

RAS[0–3]

RD

WR

TA

Type

Output

Output

Output Tri-stated Read Enable—When the DSP is the bus master, RD is an active-low output that is

Output Tri-stated Write Enable—When the DSP is the bus master, WR is an active-low output that is

Input Ignored Input Transfer Acknowledge—If the DSP56309 is the bus master and there is no external

State During Reset,

Stop, or Wait

Tri-stated Address Attribute—When defined as AA, these signals can be used as chip selects or

additional address lines. The default use defines a priority scheme under which only

one AA signal can be asserted at a time. Setting the AA priority disable (APD) bit (Bit

14) of the Operating Mode Register, the priority mechanism is disabled and the lines

can be used together as four external lines that can be decoded externally into 16 chip

select signals.

Row Address Strobe—When defined as RAS

DRAM interface. These signals are tri-statable outputs with programmable polarity.

asserted to read external memory on the data bus (D[0–23]). Otherwise, RD

stated.

asserted to write external memory on the data bus (D[0–23]). Otherwise, the signals

are tri-stated.

bus activity, or the DSP56309 is not the bus master, the TA

input is a data transfer acknowledge (DTACK) function that can extend an external bus

cycle indefinitely. Any number of wait states (1, 2. . .infinity) can be added to the wait

states inserted by the bus control register (BCR) by keeping TA

operation, TA

of the bus cycle, and is deasserted before the next bus cycle. The current bus cycle

completes one clock period after TA

of wait states is determined by the TA

BCR can be used to set the minimum number of wait states in external bus cycles.

Signal Description

Data Bus—When the DSP is the bus master, D[0–23] are active-high,

bidirectional input/outputs that provide the bidirectional data bus for external

program and data memory accesses. Otherwise, D[0–23] are tri-stated.

Signal Description

, these signals can be used as RAS for

is tri-

input is ignored. The TA

deasserted. In typical

is deasserted at the start of a bus cycle, is asserted to enable completion

is asserted synchronous to CLKOUT. The number

input or by the BCR, whichever is longer. The

functionality, the BCR must be programmed to at least one wait state. A

deassertion; otherwise, improper

can operate synchronously or asynchronously depending on

functionality cannot be

is deasserted

may be asserted or deasserted

to be deasserted even though the DSP56309 is the bus master. (See the

signal description.) The bus request hold (BRH)

to be asserted under software control even though the DSP

is typically sent to an external bus arbitrator that controls the

is affected

is deasserted and the arbitration is reset to the bus slave state.

BR

Output Reset: Output

(deasserted)

State during Stop/Wait

depends on BRH bit

setting:

• BRH = 0: Output,

deasserted

• BRH = 1: Maintains last

state (that is, if asserted,

remains asserted)

To use the TA

zero wait state access cannot be extended by TA

operation may result. TA

the setting of the TAS bit in the Operating Mode Register. TA

used during DRAM type accesses; otherwise improper operation may result.

Bus Request—Asserted when the DSP requests bus mastership. BR

when the DSP no longer needs the bus. BR

independently of whether the DSP56309 is a bus master or a bus slave. Bus “parking”

allows BR

description of bus “parking” in the BB

bit in the BCR allows BR

does not need the bus. BR

priority, parking, and tenure of each master on the same external bus. BR

only by DSP requests for the external bus, never for the internal bus. During hardware

reset, BR

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 1-5

Signals/Connections

Table 1-8. External Bus Control Signals (Continued)

Signal

Name

BG Input Ignored Input Bus Grant—Asserted by an external bus arbitration circuit when the DSP56309

BB

CAS

BCLK Output Tri-stated Bus Clock

BCLK

Type

Input/

Output

Output Tri-stated Column Address Strobe—When the DSP is the bus master, CAS is an active-low

Output Tri-stated Bus Clock Not

State During Reset,

Stop, or Wait

becomes the next bus master. When BG

is deasserted before taking bus mastership. When BG

typically given up at the end of the current bus cycle. This may occur in the middle of an

instruction that requires more than one external bus cycle for execution.

The default operation of this bit requires a setup and hold time as specified in Table 2-

14. An alternate mode can be invoked: set the asynchronous bus arbitration enable

(ABE) bit (Bit 13) in the Operating Mode Register. When this bit is set, BG

synchronized internally. This eliminates the respective setup and hold time

requirements but adds a required delay between the deassertion of an initial BG

and the assertion of a subsequent BG

Ignored Input Bus Busy—Indicates that the bus is active. Only after BB is deasserted can the

pending bus master become the bus master (and then assert the signal again). The

bus master may keep BB

is asserted or deasserted. Called “bus parking,” this allows the current bus master to

reuse the bus without rearbitration until another device requires the bus. BB

deasserted by an “active pull-up” method (that is, BB

and held high by an external pull-up resistor).

The default operation of this signal requires a setup and hold time as specified in Ta bl e

2-14. An alternative mode can be invoked by setting the ABE bit (Bit 13) in the

Operating Mode Register. When this bit is set, BG

See BG

for additional information.

Note: BB

output used by DRAM to strobe the column address. Otherwise, if the Bus Mastership

Enable (BME) bit in the DRAM control register is cleared, the signal is tri-stated.

When the DSP is the bus master, BCLK is active when the Operating Mode Register

Address Trace Enable bit is set. When BCLK is active and synchronized to CLKOUT by

the internal PLL, BCLK precedes CLKOUT by one-fourth of a clock cycle.

When the DSP is the bus master, BCLK

the signal is tri-stated.

requires an external pull-up resistor.

Signal Description

is asserted, the DSP56309 must wait until BB

is deasserted, bus mastership is

and BB are

input.

asserted after ceasing bus activity regardless of whether BR

is

is driven high and then released

and BB are synchronized internally.

is the inverse of the BCLK signal. Otherwise,

input

DSP56309 Technical Data, Rev. 7

1-6 Freescale Semiconductor

Interrupt and Mode Control

1.6 Interrupt and Mode Control

The interrupt and mode control signals select the chip operating mode as it comes out of hardware reset. After

RESET

is deasserted, these inputs are hardware interrupt request lines.

Table 1-9. Interrupt and Mode Control

Signal Name Type

RESET Input Schmitt-trigger

MODA

IRQA

MODB

IRQB

MODC

Input

Input

Input

Input

Input

State During

Reset

Input

Schmitt-trigger

Input

Schmitt-trigger

Input

Schmitt-trigger

Input

Signal Description

Reset—Places the chip in the Reset state and resets the internal phase

generator. The Schmitt-trigger input allows a slowly rising input (such as a

capacitor charging) to reset the chip reliably. When the RESET

deasserted, the initial chip operating mode is latched from the MODA, MODB,

MODC, and MODD inputs. The RESET

Mode Select A—MODA, MODB, MODC, and MODD select one of 16 initial

chip operating modes, latched into the Operating Mode Register when the

RESET

signal is deasserted.

External Interrupt Request A—After reset, this input becomes a levelsensitive or negative-edge-triggered, maskable interrupt request input during

normal instruction processing. If the processor is in the STOP or WAIT standby

state and IRQA

Mode Select B—MODA, MODB, MODC, and MODD select one of 16 initial

chip operating modes, latched into the Operating Mode Register when the

RESET

External Interrupt Request B—After reset, this input becomes a levelsensitive or negative-edge-triggered, maskable interrupt request input during

normal instruction processing. If the processor is in the WAIT standby state and

IRQB

is asserted, the processor exits the WAIT state.

Mode Select C—MODA, MODB, MODC, and MODD select one of 16 initial

chip operating modes, latched into the Operating Mode Register when the

RESET

is asserted, the processor exits the STOP or WAIT state.

signal is deasserted.

signal is deasserted.

signal must be asserted after powerup.

signal is

IRQC

MODD

IRQD

Note: These signals are all 5 V tolerant.

Input

Input

Input

Schmitt-trigger

Input

External Interrupt Request C—After reset, this input becomes a levelsensitive or negative-edge-triggered, maskable interrupt request input during

normal instruction processing. If the processor is in the WAIT standby state and

IRQC

is asserted, the processor exits the WAIT state.

Mode Select D—MODA, MODB, MODC, and MODD select one of 16 initial

chip operating modes, latched into the Operating Mode Register when the

RESET

signal is deasserted.

External Interrupt Request D—After reset, this input becomes a levelsensitive or negative-edge-triggered, maskable interrupt request input during

normal instruction processing. If the processor is in the WAIT standby state and

IRQD

is asserted, the processor exits the WAIT state.

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 1-7

Signals/Connections

1.7 Host Interface (HI08)

The HI08 provides a fast, 8-bit, parallel data port that connects directly to the host bus. The HI08 supports a variety

of standard buses and connects directly to a number of industry-standard microcomputers, microprocessors, DSPs,

and DMA hardware.

1.7.1 Host Port Usage Considerations

Careful synchronization is required when the system reads multiple-bit registers that are written by another

asynchronous system. This is a common problem when two asynchronous systems are connected (as they are in the

Host port). The considerations for proper operation are discussed in Table 1-10.

Table 1-10. Host Port Usage Considerations

Action Description

Asynchronous read of receive byte

registers

Asynchronous write to transmit byte

registers

Asynchronous write to host vector The host interface programmer must change the Host Vector (HV) register only when the Host

When reading the receive byte registers, Receive register High (RXH), Receive register Middle

(RXM), or Receive register Low (RXL), the host interface programmer should use interrupts or poll

the Receive register Data Full (RXDF) flag that indicates data is available. This assures that the data

in the receive byte registers is valid.

The host interface programmer should not write to the transmit byte registers, Transmit register High

(TXH), Transmit register Middle (TXM), or Transmit register Low (TXL), unless the Transmit register

Data Empty (TXDE) bit is set indicating that the transmit byte registers are empty. This guarantees

that the transmit byte registers transfer valid data to the Host Receive (HRX) register.

Command bit (HC) is clear. This practice guarantees that the DSP interrupt control logic receives a

stable vector.

1.7.2 Host Port Configuration

HI08 signal functions vary according to the programmed configuration of the interface as determined by the 16 bits

in the HI08 Port Control Register.

Table 1-11. Host Interface

Signal Name Type

H[0–7]

Input/Output

State During

Ignored Input Host Data—When the HI08 is programmed to interface with a non-multiplexed

Reset

1,2

host bus and the HI function is selected, these signals are lines 0–7 of the

bidirectional Data bus.

Signal Description

HAD[0–7]

PB[0–7]

1-8 Freescale Semiconductor

Input/Output

Input or Output

Host Address—When the HI08 is programmed to interface with a multiplexed

host bus and the HI function is selected, these signals are lines 0–7 of the

bidirectional multiplexed Address/Data bus.

Port B 0–7—When the HI08 is configured as GPIO through the HI08 Port

Control Register, these signals are individually programmed as inputs or outputs

through the HI08 Data Direction Register.

DSP56309 Technical Data, Rev. 7

Table 1-11. Host Interface (Continued)

Host Interface (HI08)

Signal Name Type

HA0

HAS

/HAS

PB8

HA1

HA8

PB9

HA2

Input or Output

Input or Output

Input

Input

Input

Input

Input

State During

Ignored Input Host Address Input 0—When the HI08 is programmed to interface with a

Ignored Input Host Address Input 1—When the HI08 is programmed to interface with a

Ignored Input Host Address Input 2—When the HI08 is programmed to interface with a

Reset

1,2

nonmultiplexed host bus and the HI function is selected, this signal is line 0 of

the host address input bus.

Host Address Strobe—When the HI08 is programmed to interface with a

multiplexed host bus and the HI function is selected, this signal is the host

address strobe (HAS) Schmitt-trigger input. The polarity of the address strobe is

programmable but is configured active-low (HAS

Port B 8—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HI08 Data Direction Register.

nonmultiplexed host bus and the HI function is selected, this signal is line 1 of

the host address (HA1) input bus.

Host Address 8—When the HI08 is programmed to interface with a multiplexed

host bus and the HI function is selected, this signal is line 8 of the host address

(HA8) input bus.

Port B 9—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HI08 Data Direction Register.

nonmultiplexed host bus and the HI function is selected, this signal is line 2 of

the host address (HA2) input bus.

Signal Description

) following reset.

HA9

PB10

HCS

HA10

PB13

HRW

HRD

PB11

/HCS

/HRD

Input

Input or Output

Input

Input

Input or Output

Input

Input

Input or Output

Host Address 9—When the HI08 is programmed to interface with a multiplexed

host bus and the HI function is selected, this signal is line 9 of the host address

(HA9) input bus.

Port B 10—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HI08 Data Direction Register.

Ignored Input Host Chip Select—When the HI08 is programmed to interface with a

nonmultiplexed host bus and the HI function is selected, this signal is the host

chip select (HCS) input. The polarity of the chip select is programmable but is

configured active-low (HCS

Host Address 10—When the HI08 is programmed to interface with a

multiplexed host bus and the HI function is selected, this signal is line 10 of the

host address (HA10) input bus.

Port B 13—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HI08 Data Direction Register.

Ignored Input Host Read/Write—When the HI08 is programmed to interface with a single-

data-strobe host bus and the HI function is selected, this signal is the Host

Read/Write

Host Read Data—When the HI08 is programmed to interface with a doubledata-strobe host bus and the HI function is selected, this signal is the HRD

strobe Schmitt-trigger input. The polarity of the data strobe is programmable but

is configured as active-low (HRD

Port B 11—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HI08 Data Direction Register.

(HRW) input.

) after reset.

) after reset.

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 1-9

Signals/Connections

Table 1-11. Host Interface (Continued)

Signal Name Type

HDS/HDS

HWR

/HWR

PB12

HREQ

HTRQ

PB14

HACK

/HREQ

/HTRQ

/HACK

Input or Output

Output

Output

Input or Output

Input

Input

Input

State During

Ignored Input Host Data Strobe—When the HI08 is programmed to interface with a single-

Ignored Input Host Request—When the HI08 is programmed to interface with a single host

Ignored Input Host Acknowledge—When the HI08 is programmed to interface with a single

Reset

1,2

data-strobe host bus and the HI function is selected, this signal is the host data

strobe (HDS) Schmitt-trigger input. The polarity of the data strobe is

programmable but is configured as active-low (HDS

Host Write Data—When the HI08 is programmed to interface with a doubledata-strobe host bus and the HI function is selected, this signal is the host write

data strobe (HWR) Schmitt-trigger input. The polarity of the data strobe is

programmable but is configured as active-low (HWR

Port B 12—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HI08 Data Direction Register.

request host bus and the HI function is selected, this signal is the host request

(HREQ) output. The polarity of the host request is programmable but is

configured as active-low (HREQ

programmed as a driven or open-drain output.

Transmit Host Request—When the HI08 is programmed to interface with a

double host request host bus and the HI function is selected, this signal is the

transmit host request (HTRQ) output. The polarity of the host request is

programmable but is configured as active-low (HTRQ

request may be programmed as a driven or open-drain output.

Port B 14—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HI08 Data Direction Register.

host request host bus and the HI function is selected, this signal is the host

acknowledge (HACK) Schmitt-trigger input. The polarity of the host

acknowledge is programmable but is configured as active-low (HACK

reset.

Signal Description

) following reset.

) following reset.

) following reset. The host request may be

) following reset. The host

) after

/HRRQ

HRRQ

PB15

Notes: 1. In the Stop state, the signal maintains the last state as follows:

• If the last state is input, the signal is an ignored input.

• If the last state is output, the signal is tri-stated.

2. The Wait processing state does not affect the signal state.

3. All inputs are 5 V tolerant.

Output

Input or Output

Receive Host Request—When the HI08 is programmed to interface with a

double host request host bus and the HI function is selected, this signal is the

receive host request (HRRQ) output. The polarity of the host request is

programmable but is configured as active-low (HRRQ

request may be programmed as a driven or open-drain output.

Port B 15—When the HI08 is configured as GPIO through the HI08 Port Control

Register, this signal is individually programmed as an input or output through the

HI08 Data Direction Register.

DSP56309 Technical Data, Rev. 7

) after reset. The host

1-10 Freescale Semiconductor

Enhanced Synchronous Serial Interface 0 (ESSI0)

1.8 Enhanced Synchronous Serial Interface 0 (ESSI0)

Two synchronous serial interfaces (ESSI0 and ESSI1) provide a full-duplex serial port for serial communication

with a variety of serial devices, including one or more industry-standard codecs, other DSPs, microprocessors, and

peripherals that implement the serial peripheral interface (SPI).

Table 1-12. Enhanced Synchronous Serial Interface 0

Signal Name Type

SC00

PC0

SC01

PC1

SC02

PC2

SCK0

Input or Output

Input or Output

Input/Output

Input or Output

Input/Output

Input or Output

Input/Output

State During

Ignored Input Serial Control 0—For asynchronous mode, this signal is used for the receive

Ignored Input Serial Control 1—For asynchronous mode, this signal is the receiver frame

Ignored Input Serial Control Signal 2—The frame sync for both the transmitter and receiver

Ignored Input Serial Clock—Provides the serial bit rate clock for the ESSI. The SCK0 is a

Reset

1,2

clock I/O (Schmitt-trigger input). For synchronous mode, this signal is used

either for transmitter 1 output or for serial I/O flag 0.

Port C 0—The default configuration following reset is GPIO input PC0. When

configured as PC0, signal direction is controlled through the Port C Direction

Register. The signal can be configured as ESSI signal SC00 through the Port C

Control Register.

sync I/O. For synchronous mode, this signal is used either for transmitter 2

output or for serial I/O flag 1.

Port C 1—The default configuration following reset is GPIO input PC1. When

configured as PC1, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal SC01 through the Port

C Control Register.

in synchronous mode, and for the transmitter only in asynchronous mode. When

configured as an output, this signal is the internally generated frame sync signal.

When configured as an input, this signal receives an external frame sync signal

for the transmitter (and the receiver in synchronous operation).

Port C 2—The default configuration following reset is GPIO input PC2. When

configured as PC2, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal SC02 through the Port

C Control Register.

clock input or output, used by both the transmitter and receiver in synchronous

modes or by the transmitter in asynchronous modes.

Signal Description

Although an external serial clock can be independent of and asynchronous to

the DSP system clock, it must exceed the minimum clock cycle time of 6T (that

is, the system clock frequency must be at least three times the external ESSI

clock frequency). The ESSI needs at least three DSP phases inside each half of

the serial clock.

PC3

SRD0

PC4

Input or Output

Input

Input or Output

Ignored Input Serial Receive Data—Receives serial data and transfers the data to the ESSI

Port C 3—The default configuration following reset is GPIO input PC3. When

configured as PC3, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal SCK0 through the Port

C Control Register.

Receive Shift Register. SRD0 is an input when data is received.

Port C 4—The default configuration following reset is GPIO input PC4. When

configured as PC4, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal SRD0 through the

Port C Control Register.

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 1-11

Signals/Connections

Table 1-12. Enhanced Synchronous Serial Interface 0 (Continued)

Signal Name Type

STD0

PC5

Notes: 1. In the Stop state, the signal maintains the last state as follows:

• If the last state is input, the signal is an ignored input.

• If the last state is output, the signal is tri-stated.

2. The Wait processing state does not affect the signal state.

3. All inputs are 5 V tolerant.

Output

Input or Output

State During

Ignored Input Serial Transmit Data—Transmits data from the Serial Transmit Shift Register.

Reset

1,2

STD0 is an output when data is transmitted.

Port C 5—The default configuration following reset is GPIO input PC5. When

configured as PC5, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal STD0 through the Port

C Control Register.

Signal Description

1.9 Enhanced Synchronous Serial Interface 1 (ESSI1)

Table 1-13. Enhanced Serial Synchronous Interface 1

Signal Name Type

SC10

Input or Output

State During

Ignored Input Serial Control 0—For asynchronous mode, this signal is used for the receive

Reset

1,2

clock I/O (Schmitt-trigger input). For synchronous mode, this signal is used

either for transmitter 1 output or for serial I/O flag 0.

Signal Description

PD0

SC11

PD1

SC12

PD2

Input or Output

Input/Output

Input or Output

Input/Output

Input or Output

Port D 0—The default configuration following reset is GPIO input PD0. When

configured as PD0, signal direction is controlled through the Port D Direction

Register. The signal can be configured as an ESSI signal SC10 through the Port

D Control Register.

Ignored Input Serial Control 1—For asynchronous mode, this signal is the receiver frame

sync I/O. For synchronous mode, this signal is used either for Transmitter 2

output or for Serial I/O Flag 1.

Port D 1—The default configuration following reset is GPIO input PD1. When

configured as PD1, signal direction is controlled through the Port D Direction

Register. The signal can be configured as an ESSI signal SC11 through the Port

D Control Register.

Ignored Input Serial Control Signal 2—The frame sync for both the transmitter and receiver

in synchronous mode and for the transmitter only in asynchronous mode. When

configured as an output, this signal is the internally generated frame sync signal.

When configured as an input, this signal receives an external frame sync signal

for the transmitter (and the receiver in synchronous operation).

Port D 2—The default configuration following reset is GPIO input PD2. When

configured as PD2, signal direction is controlled through the Port D Direction

Register. The signal can be configured as an ESSI signal SC12 through the Port

D Control Register.

DSP56309 Technical Data, Rev. 7

1-12 Freescale Semiconductor

Enhanced Synchronous Serial Interface 1 (ESSI1)

Table 1-13. Enhanced Serial Synchronous Interface 1 (Continued)

Signal Name Type

SCK1

PD3

SRD1

PD4

STD1

PD5

Notes: 1. In the Stop state, the signal maintains the last state as follows:

• If the last state is input, the signal is an ignored input.

• If the last state is output, the signal is tri-stated.

2. The Wait processing state does not affect the signal state.

3. All inputs are 5 V tolerant.

Input/Output

Input or Output

Input

Input or Output

Output

Input or Output

State During

Ignored Input Serial Clock—Provides the serial bit rate clock for the ESSI. The SCK1 is a

Ignored Input Serial Receive Data—Receives serial data and transfers the data to the ESSI

Ignored Input Serial Transmit Data—Transmits data from the Serial Transmit Shift Register.

Reset

1,2

clock input or output used by both the transmitter and receiver in synchronous

modes or by the transmitter in asynchronous modes.

Although an external serial clock can be independent of and asynchronous to

the DSP system clock, it must exceed the minimum clock cycle time of 6T (that

is, the system clock frequency must be at least three times the external ESSI

clock frequency). The ESSI needs at least three DSP phases inside each half of

the serial clock.

Port D 3—The default configuration following reset is GPIO input PD3. When

configured as PD3, signal direction is controlled through the Port D Direction

Register. The signal can be configured as an ESSI signal SCK1 through the Port

D Control Register.

Receive Shift Register. SRD1 is an input when data is being received.

Port D 4—The default configuration following reset is GPIO input PD4. When

configured as PD4, signal direction is controlled through the Port D Direction

Register. The signal can be configured as an ESSI signal SRD1 through the

Port D Control Register.

STD1 is an output when data is being transmitted.

Port D 5—The default configuration following reset is GPIO input PD5. When

configured as PD5, signal direction is controlled through the Port D Direction

Register. The signal can be configured as an ESSI signal STD1 through the Port

D Control Register.

Signal Description

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 1-13

Signals/Connections

1.10 Serial Communication Interface (SCI)

The SCI provides a full duplex port for serial communication with other DSPs, microprocessors, or peripherals

such as modems.

Table 1-14. Serial Communication Interface

Signal Name Type

RXD

PE0

TXD

PE1

SCLK

PE2

Notes: 1. In the Stop state, the signal maintains the last state as follows:

• If the last state is input, the signal is an ignored input.

• If the last state is output, the signal is tri-stated.

2. The Wait processing state does not affect the signal state.

3. All inputs are 5 V tolerant.

Input

Input or Output

Output

Input or Output

Input/Output

Input or Output

State During

Ignored Input Serial Receive Data—Receives byte-oriented serial data and transfers it to the

Ignored Input Serial Transmit Data—Transmits data from the SCI Transmit Data Register.

Ignored Input Serial Clock—Provides the input or output clock used by the transmitter and/or

Reset

1,2

SCI Receive Shift Register.

Port E 0—The default configuration following reset is GPIO input PE0. When

configured as PE0, signal direction is controlled through the Port E Direction

Register. The signal can be configured as an SCI signal RXD through the Port E

Control Register.

Port E 1—The default configuration following reset is GPIO input PE1. When

configured as PE1, signal direction is controlled through the Port E Direction

Register. The signal can be configured as an SCI signal TXD through the Port E

Control Register.

the receiver.

Port E 2—The default configuration following reset is GPIO input PE2. When

configured as PE2, signal direction is controlled through the Port E Direction

Register. The signal can be configured as an SCI signal SCLK through the Port

E Control Register.

Signal Description

DSP56309 Technical Data, Rev. 7

1-14 Freescale Semiconductor

Timers

1.11 Timers

The DSP56309 has three identical and independent timers. Each timer can use internal or external clocking and can

either interrupt the DSP56309 after a specified number of events (clocks) or signal an external device after

counting a specific number of internal events.

Table 1-15. Triple Timer Signals

Signal Name Type

TIO0 Input or Output Ignored Input Timer 0 Schmitt-Trigger Input/Output— When Timer 0 functions as an

TIO1 Input or Output Ignored Input Timer 1 Schmitt-Trigger Input/Output— When Timer 1 functions as an

TIO2 Input or Output Ignored Input Timer 2 Schmitt-Trigger Input/Output— When Timer 2 functions as an

Notes: 1. In the Stop state, the signal maintains the last state as follows:

• If the last state is input, the signal is an ignored input.

• If the last state is output, the signal is tri-stated.

2. The Wait processing state does not affect the signal state.

3. All inputs are 5 V tolerant.

State During

1,2

Reset

Signal Description

external event counter or in measurement mode, TIO0 is used as input. When

Timer 0 functions in watchdog, timer, or pulse modulation mode, TIO0 is used

as output.

The default mode after reset is GPIO input. TIO0 can be changed to output or

configured as a timer I/O through the Timer 0 Control/Status Register (TCSR0).

external event counter or in measurement mode, TIO1 is used as input. When

Timer 1 functions in watchdog, timer, or pulse modulation mode, TIO1 is used

as output.

The default mode after reset is GPIO input. TIO1 can be changed to output or

configured as a timer I/O through the Timer 1 Control/Status Register (TCSR1).

external event counter or in measurement mode, TIO2 is used as input. When

Timer 2 functions in watchdog, timer, or pulse modulation mode, TIO2 is used

as output.

The default mode after reset is GPIO input. TIO2 can be changed to output or

configured as a timer I/O through the Timer 2 Control/Status Register (TCSR2).

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 1-15

Signals/Connections

1.12 JTAG and OnCE Interface

The DSP56300 family and in particular the DSP56309 support circuit-board test strategies based on the IEEE®

Std. 1149.1™ test access port and boundary scan architecture, the industry standard developed under the

sponsorship of the Test Technology Committee of IEEE and the JTAG.

The OnCE module provides a means to interface nonintrusively with the DSP56300 core and its peripherals so that

you can examine registers, memory, or on-chip peripherals. Functions of the OnCE module are provided through

the JTAG TAP signals.

For programming models, see the chapter on debugging support in the DSP56300 Family Manual.

Table 1-16. JTAG/OnCE Interface

Signal

Name

TCK Input Input Test Cl oc k—A test clock input signal to synchronize the JTAG test logic.

TDI Input Input Test Data Input—A test data serial input signal for test instructions and data.

TDO Output Tri-stated Test Data Output—A test data serial output signal for test instructions and

TMS Input Input Test Mode Select—Sequences the test controller’s state machine. TMS is

TRST

DE

Note: All inputs are 5 V tolerant.

Type

Input Input Test Reset—Initializes the test controller asynchronously. TRST has an

Input/ Output

(open-drain)

State During

Reset

TDI is sampled on the rising edge of TCK and has an internal pull-up resistor.

data. TDO is actively driven in the shift-IR and shift-DR controller states. TDO

changes on the falling edge of TCK.

sampled on the rising edge of TCK and has an internal pull-up resistor.

internal pull-up resistor. TRST

Input Debug Event—As an input, initiates Debug mode from an external command

controller, and, as an open-drain output, acknowledges that the chip has

entered Debug mode. As an input, DE

executing the current instruction, save the instruction pipeline information,

enter Debug mode, and wait for commands to be entered from the debug

serial input line. This signal is asserted as an output for three clock cycles

when the chip enters Debug mode as a result of a debug request or as a result

of meeting a breakpoint condition. The DE

This signal is not a standard part of the JTAG TAP controller. The signal

connects directly to the OnCE module to initiate debug mode directly or to

provide a direct external indication that the chip has entered Debug mode. All

other interface with the OnCE module must occur through the JTAG port.

Signal Description

must be asserted after powerup.

causes the DSP56300 core to finish

has an internal pull-up resistor.

DSP56309 Technical Data, Rev. 7

1-16 Freescale Semiconductor

Specifications 2

Note: The DSP56309 is fabricated in high-density CMOS with Transistor-Transistor Logic (TTL) compatible

inputs and outputs. The DSP56309 specifications are preliminary and are from design simulations, and

may not be fully tested or guaranteed. Finalized specifications will be published after full characterization

and device qualifications are complete.

2.1 Maximum Ratings

CAUTION

This device contains circuitry protecting

against damage due to high static voltage or

electrical fields; however, normal precautions

should be taken to avoid exceeding maximum

voltage ratings. Reliability is enhanced if

unused inputs are tied to an appropriate logic

voltage level (for example, either GND or V

CC

).

In the calculation of timing requirements, adding a maximum value of one specification to a minimum value of

another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case

variation of process parameter values in one direction. The minimum specification is calculated using the worst

case for the same parameters in the opposite direction. Therefore, a “maximum” value for a specification never

occurs in the same device that has a “minimum” value for another specification; adding a maximum to a minimum

represents a condition that can never exist.

2.2 Absolute Maximum Ratings

Table 2-1. Absolute Maximum Ratings

Rating Symbol Value Unit

Supply Voltage V

All input voltages excluding “5 V tolerant” inputs V

All “5 V tolerant” input voltages

Current drain per pin excluding V

Operating temperature range T

Storage temperature T

Notes: 1. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond

the maximum rating may affect device reliability or cause permanent damage to the device.

2. At power-up, ensure that the voltage difference between the 5 V tolerant pins and the chip V

2

and GND I 10 mA

CC

DSP56309 Technical Data, Rev. 7

V

CC

IN

IN5

J

STG

1

−0.3 to +4.0 V

GND − 0.3 to VCC + 0.3 V

GND − 0.3 to 5.5 V

−40 to +100 °C

−55 to +150 °C

never exceeds 3.5 V.

CC

Freescale Semiconductor 2-1

Specifications

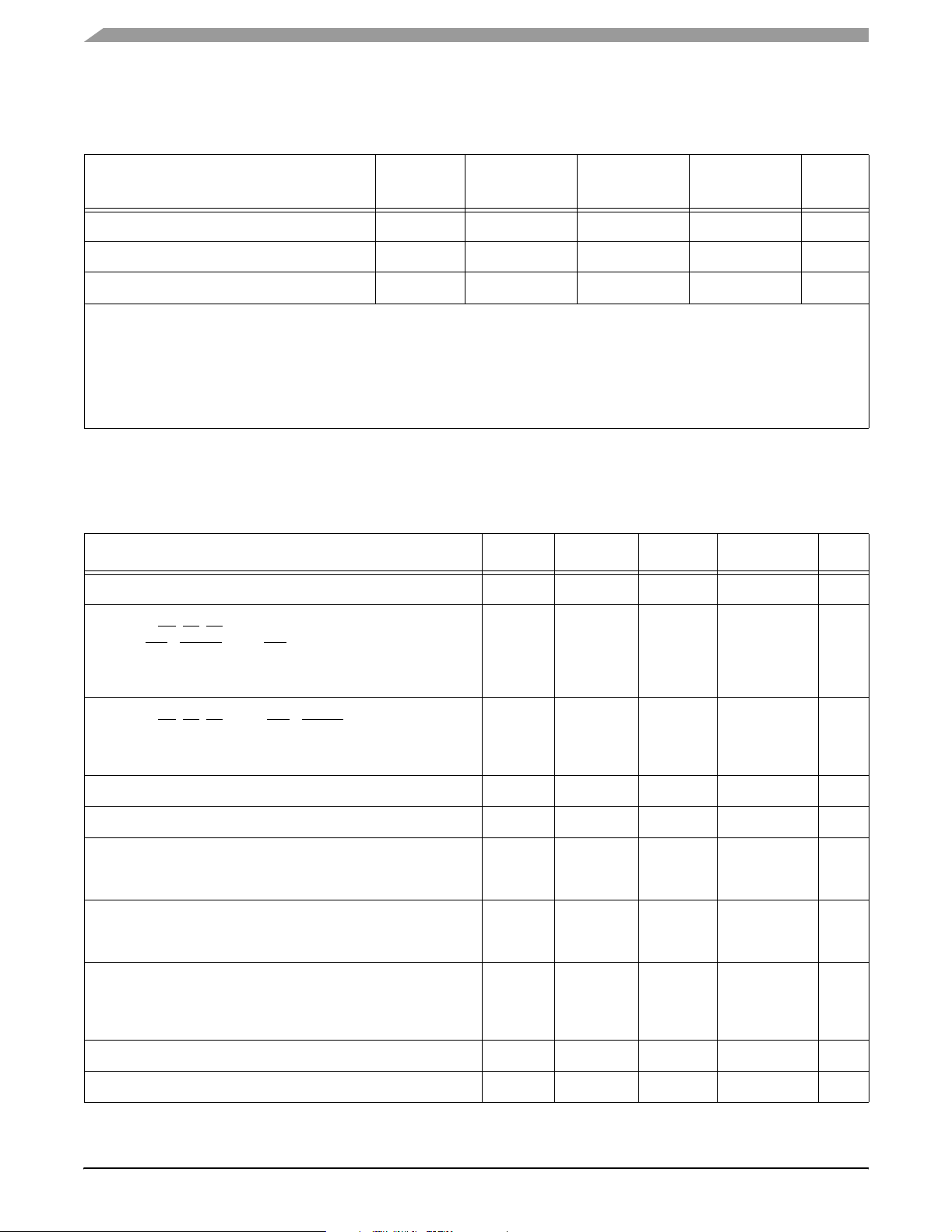

2.3 Thermal Characteristics

Table 2-2. Thermal Characteristics

Characteristic Symbol TQFP Value

MAP-BGA

Value

3

MAP-BGA4

Value

Unit

Junction-to-ambient thermal resistance

Junction-to-case thermal resistance

Thermal characterization parameter Ψ

1

2

R

θJA or θJA

R

θJC or θJC

JT

49.3 49.4 28.5 °C/W

8.2 12.0 — °C/W

5.5 2.0 — °C/W

Notes: 1. Junction-to-ambient thermal resistance is based on measurements on a horizontal single-sided printed circuit board per

JEDEC Specification JESD51-3.

2. Junction-to-case thermal resistance is based on measurements using a cold plate per SEMI G30-88, with the exception that

the cold plate temperature is used for the case temperature.

3. These are simulated values. See note 1 for test board conditions.

4. These are simulated values. The test board has two 2-ounce signal layers and two 1-ounce solid ground planes internal to the

test board.

2.4 DC Electrical Characteristics

Table 2-3. DC Electrical Characteristics6

Characteristics Symbol Min Typ Max Unit

Supply voltage V

Input high voltage

• D[0–23], BG

, BB, TA

•MOD1/IRQ1, RESET, PINIT/NMI and all

JTAG/ESSI/SCI/Timer/HI08 pins

•EXTAL

8

CC

V

IH

V

IHP

V

IHX

3.0 3.3 3.6 V

2.0

2.0

0.8 × V

CC

—

—

—

V

CC

5.25

V

CC

V

V

V

Input low voltage

• D[0–23], BG

• All JTAG/ESSI/SCI/Timer/HI08 pins

•EXTAL

, BB, TA, MOD1/IRQ1, RESET, PINIT

8

Input leakage current I

High impedance (off-state) input current (@ 2.4 V / 0.4 V) I

Output high voltage

•TTL (I

•CMOS (IOH = –10 µA)

= –0.4 mA)

OH

Output low voltage

•TTL (I

•CMOS (IOL = 10 µA)

= 1.6 mA, open-drain pins IOL = 6.7 mA)

OL

Internal supply current

• In Normal mode

•In Wait mode

• In Stop mode

5,7

5

5,7

5

2

:

3

4

V

V

V

TSI

V

V

I

CCI

I

CCW

I

CCS

ILP

ILX

IN

OH

OL

IL

–0.3

–0.3

–0.3

—

—

—

–10 — 10 µA

–10 — 10 µA

V

CC

2.4

– 0.01

—

—

—

—

—

—

—

—

—

127

7.5

100

0.8

0.8

0.2 × V

—

—

0.4

0.01

—

—

—

CC

V

V

V

V

V

V

V

mA

mA

µA

PLL supply current —1 2.5mA

Input capacitance

5

C

IN

— — 10 pF

DSP56309 Technical Data, Rev. 7

2-2 Freescale Semiconductor

AC Electrical Characteristics

Table 2-3. DC Electrical Characteristics6 (Continued)

Characteristics Symbol Min Typ Max Unit

Notes: 1. Refers to MODA/IRQA, MODB/IRQB, MODC/IRQC, and MODD/IRQD pins.

2. Section 4.3 provides a formula to compute the estimated current requirements in Normal mode. In order to obtain these

results, all inputs must be terminated (that is, not allowed to float). Measurements are based on synthetic intensive DSP

benchmarks (see Appendix A). The power consumption numbers in this specification are 90 percent of the measured results

of this benchmark. This reflects typical DSP applications. Typical internal supply current is measured with V

100°C.

3. In order to obtain these results, all inputs must be terminated (that is, not allowed to float).

4. In order to obtain these results, all inputs that are not disconnected at Stop mode must be terminated (that is, not allowed to

float). PLL and XTAL signals are disabled during Stop state.

5. Periodically sampled and not 100 percent tested.

6. V

7. This characteristic does not apply to XTAL and PCAP.

8. Driving EXTAL to the low V

= 3.3 V ± 0.3 V; TJ = –40°C to +100 °C, CL = 50 pF

CC

or the high V

power consumption, the minimum V

0.9 × V

and the maximum V

CC

IHX

should be no lower than

IHX

should be no higher than 0.1 × VCC.

ILX

value may cause additional power consumption (DC current). To minimize

ILX

= 3.3 V at TJ =

CC

2.5 AC Electrical Characteristics

The timing waveforms shown in the AC electrical characteristics section are tested with a VIL maximum of 0.3 V

and a V

the previous table. AC timing specifications, which are referenced to a device input signal, are measured in

production with respect to the 50 percent point of the respective input signal transition. DSP56309 output levels are

measured with the production test machine V

minimum of 2.4 V for all pins except EXTAL, which is tested using the input levels shown in Note 6 of

IH

and VOH reference levels set at 0.4 V and 2.4 V, respectively.

OL

Note: Although the minimum value for the frequency of EXTAL is 0 MHz, the device AC test conditions are 15

MHz and rated speed.

2.5.1 Internal Clocks

Table 2-4. Internal Clocks, CLKOUT

1, 2

ET

C

—

—

ET

C

—

—

× PDF ×

—

—

0.51 × ETC ×

PDF × DF/MF

0.53 × ET

PDF × DF/MF

0.51 × ETC ×

PDF × DF/MF

0.53 × ET

PDF × DF/MF

×

C

—

×

C

—

Characteristics Symbol

Internal operation frequency and CLKOUT

with PLL enabled

Internal operation frequency and CLKOUT

with PLL disabled

Internal clock and CLKOUT high period

• With PLL disabled

• With PLL enabled and MF ≤ 4

• With PLL enabled and MF > 4

Internal clock and CLKOUT low period

• With PLL disabled

• With PLL enabled and MF ≤ 4

• With PLL enabled and MF > 4

Internal clock and CLKOUT cycle time with

PLL enabled

Expression

Min Typ Max

f— (Ef × MF)/

f— Ef/2 —

T

H

T

L

T

—ET

C

—

0.49 × ET

PDF × DF/MF

0.47 × ET

PDF × DF/MF

0.49 × ET

PDF × DF/MF

0.47 × ET

PDF × DF/MF

×

C

×

C

—

×

C

×

C

(PDF × DF)

C

DF/MF

DSP56309 Technical Data, Rev. 7

Freescale Semiconductor 2-3

Specifications

Table 2-4. Internal Clocks, CLKOUT (Continued)

Expression

1, 2

Characteristics Symbol

Min Typ Max

Internal clock and CLKOUT cycle time with

PLL disabled

Instruction cycle time I

Notes: 1. DF = Division Factor; Ef = External frequency; ET

PDF = Predivision Factor; T

2. See the PLL and Clock Generation section in the

C

TC —2 × ET

CYC

= internal clock cycle

—TC—

= External clock cycle; MF = Multiplication Factor;

C

DSP56300 Family Manual

C

for a detailed discussion of the PLL.

—

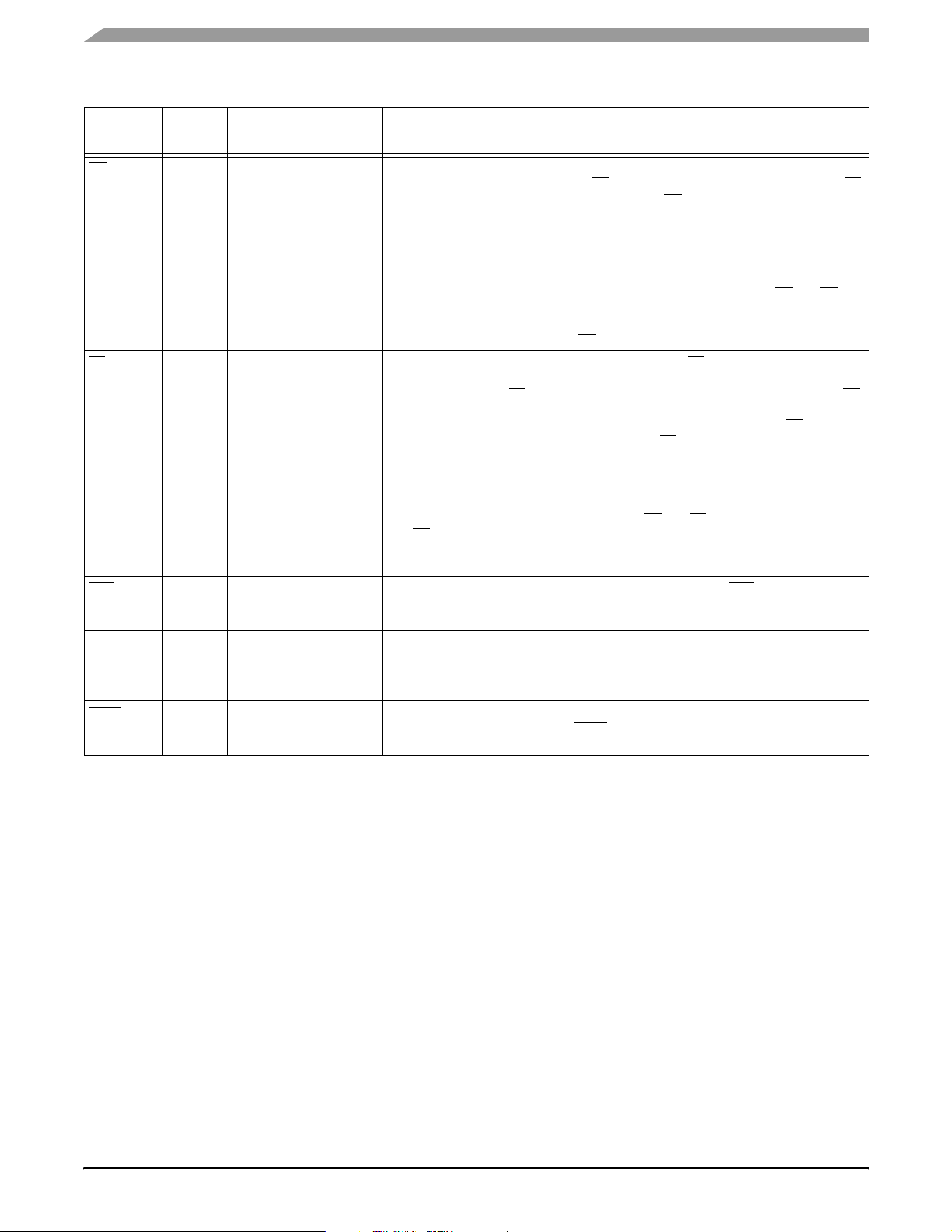

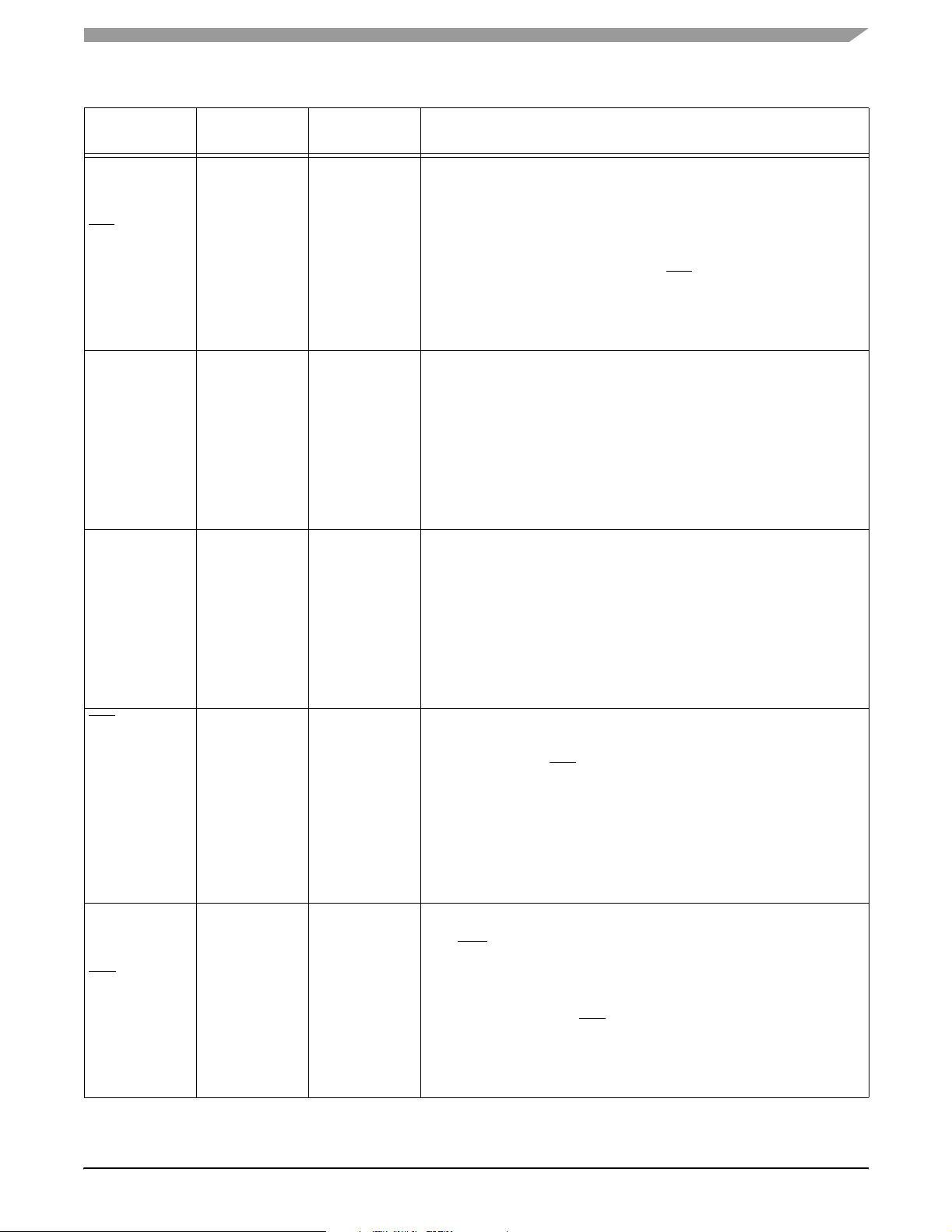

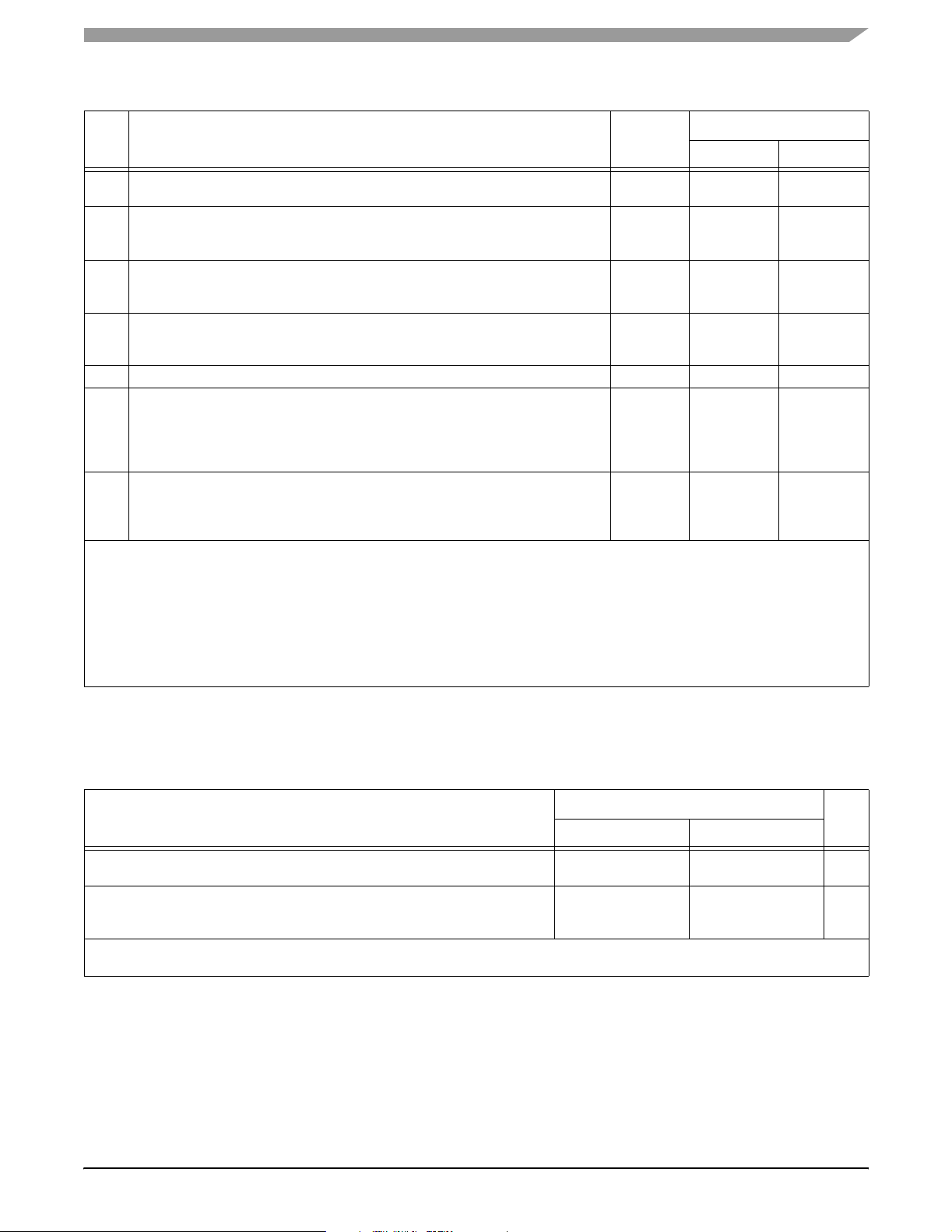

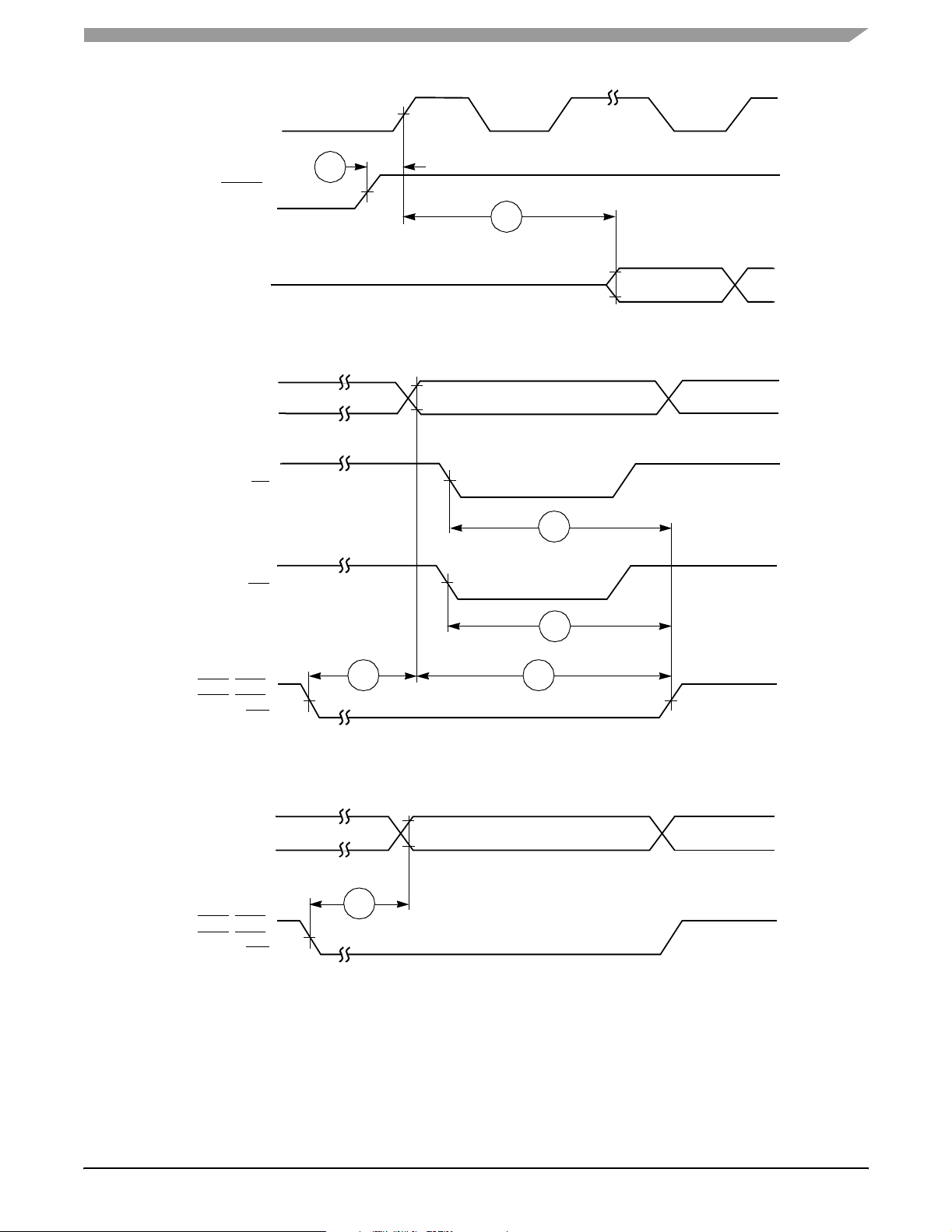

2.5.2 External Clock Operation

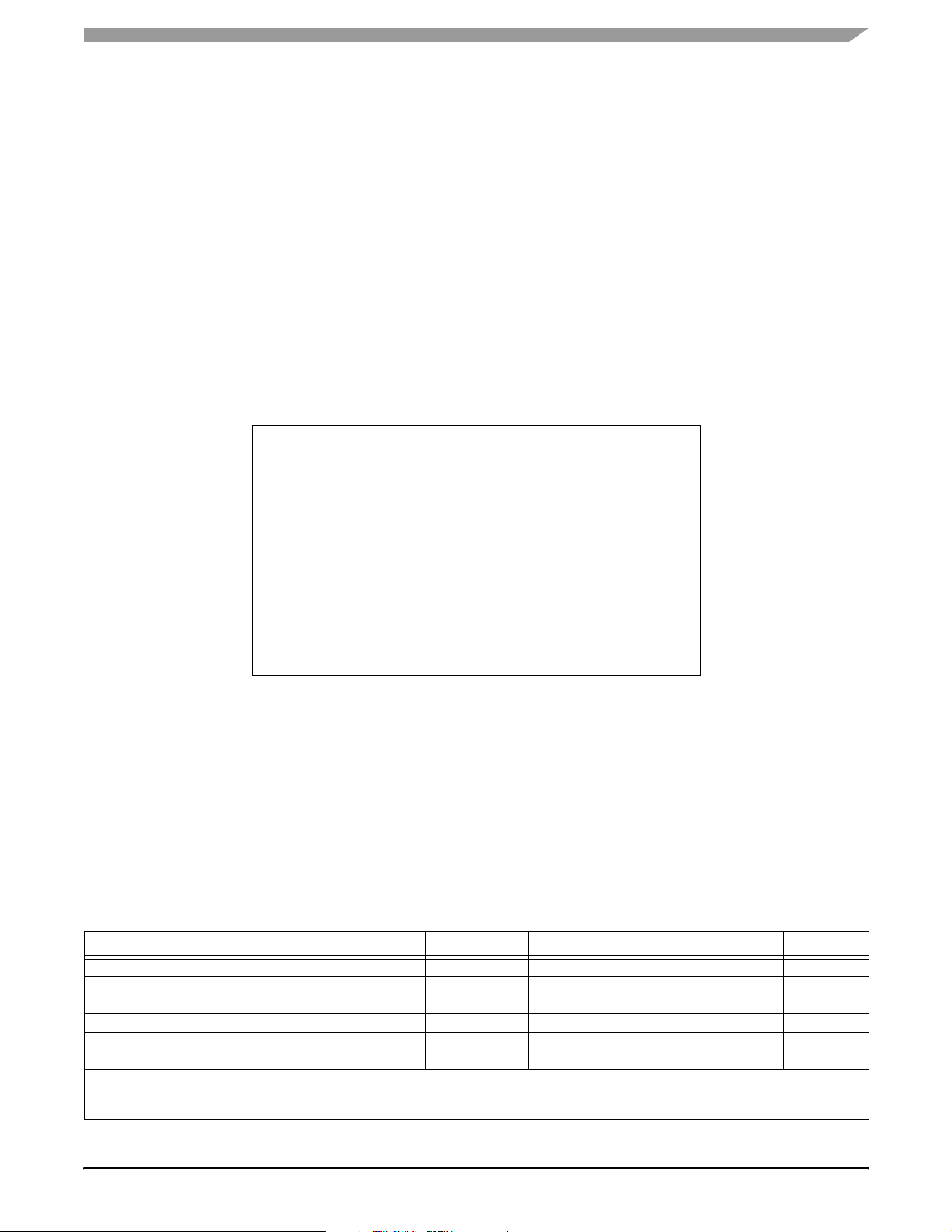

The DSP56309 system clock is derived from the on-chip oscillator or is externally supplied. To use the on-chip

oscillator, connect a crystal and associated resistor/capacitor components to EXTAL and XTAL; examples are

shown in

Figure 2-1.

R

C

XTAL1

Fundamental Frequency

Crystal Oscillator

XTALEXTAL

Note: Make su re t hat i n

the PCTL Register:

• XTLD (bit 16) = 0

• If f

C

> 200 kHz,

OSC

XTLR (bit 15) = 0

Suggested Component Values:

f

= 4 MHz

OSC

R = 680 kΩ ± 10%

C = 56 pF ± 20%

Calculations were done for a 4/20 MHz crystal

with the following parameters:

•C

of 30/20 pF,

L

•C

of 7/6 pF,

0

• series resistance of 100/20 Ω, and

• drive level of 2 mW.

f

= 20 MHz

OSC

R = 680 kΩ ± 10%

C = 22 pF ± 20%

Figure 2-1. Crystal Oscillator Circuits

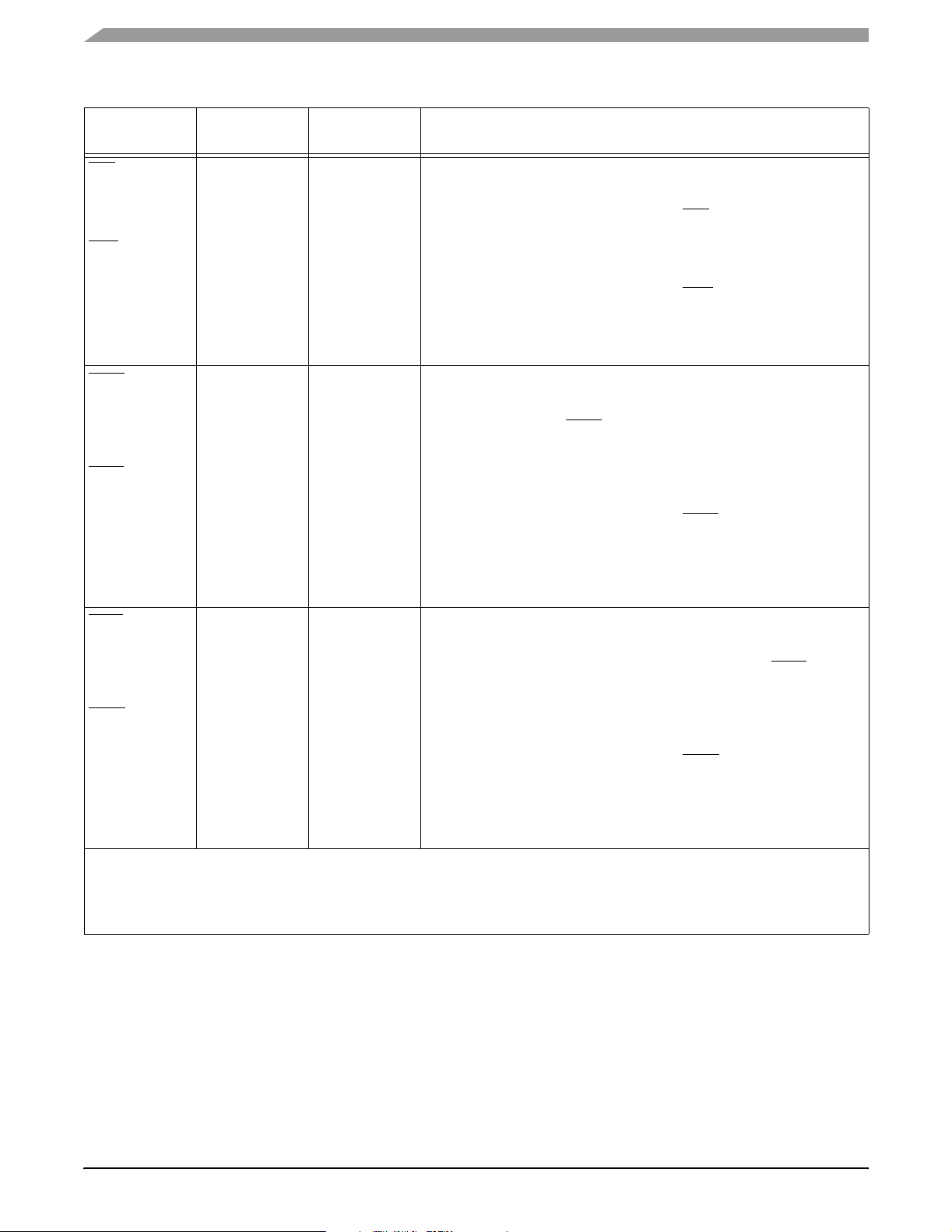

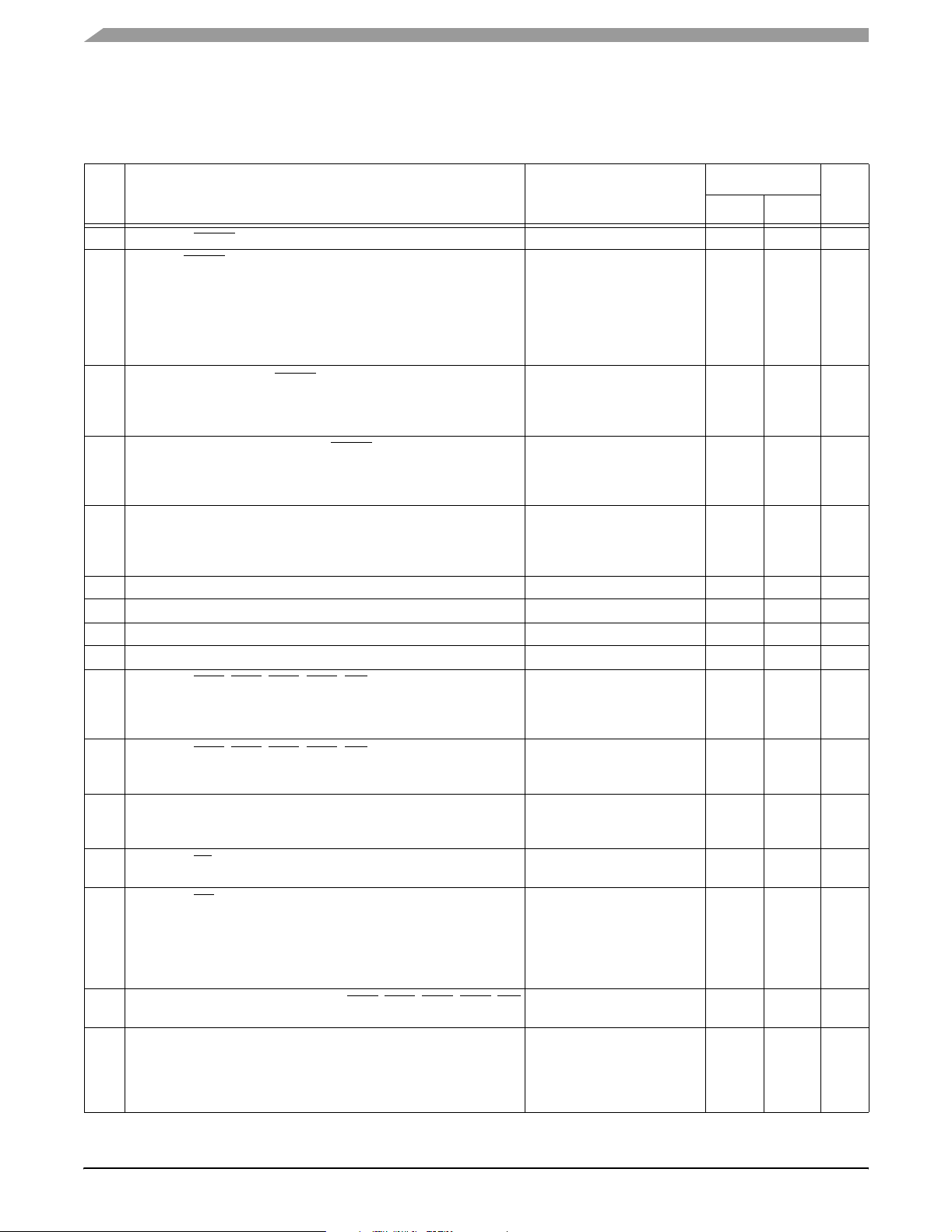

If an externally-supplied square wave voltage source is used, disable the internal oscillator circuit during bootup by

setting XTLD (PCTL Register bit 16 = 1—see the DSP56309 User’s Manual). The external square wave source

connects to EXTAL; XTAL is not physically connected to the board or socket. Figure 2-2 shows the relationship

between the

EXTAL input and the internal clock and CLKOUT.

EXTAL

CLKOUT with

PLL disabled

CLKOUT with

PLL enabled

6a

ET

ILX

H

2

5

V

ET

L

3

4

ET

C

6b

Midpoint

Note: The midpoint is

0.5 (V

5

7

7

IHX

V

+ V

IHX

ILX

).

Figure 2-2. External Clock Timing

DSP56309 Technical Data, Rev. 7

2-4 Freescale Semiconductor

Table 2-5. Clock Operation

AC Electrical Characteristics

No. Characteristics Symbol

100 MHz

Min Max

1 Frequency of EXTAL (EXTAL Pin Frequency)

The rise and fall time of this external clock should be 3 ns maximum.

1, 2

1, 2

2

6

)

6

)

2 EXTAL input high

• With PLL disabled (46.7%–53.3% duty cycle6)

• With PLL enabled (42.5%–57.5% duty cycle

3 EXTAL input low

• With PLL disabled (46.7%–53.3% duty cycle6)

• With PLL enabled (42.5%–57.5% duty cycle

4 EXTAL cycle time

• With PLL disabled

• With PLL enabled

5 Internal clock change from EXTAL fall with PLL disabled 4.3 ns 11.0 ns

6 a.Internal clock rising edge from EXTAL rising edge with PLL enabled (MF = 1 or 2 or

4, PDF = 1, Ef > 15 MHz)

b. Internal clock falling edge from EXTAL falling edge with PLL enabled (MF ≤ 4, PDF ≠

1, Ef / PDF > 15 MHz)

7 Instruction cycle time = I

(see Table 2-4) (46.7%–53.3% duty cycle)

3,5

3,5

CYC

= T

4

C

• With PLL disabled

• With PLL enabled

Notes: 1. Measured at 50 percent of the input transition.

2. The maximum value for PLL enabled is given for minimum VCO frequency (see Table 2-4) and maximum MF.

3. Periodically sampled and not 100 percent tested.

4. The maximum value for PLL enabled is given for minimum VCO frequency and maximum DF.

5. The skew is not guaranteed for any other MF value.

6. The indicated duty cycle is for the specified maximum frequency for which a part is rated. The minimum clock high or low time

required for correction operation, however, remains the same at lower operating frequencies; therefore, when a lower clock

frequency is used, the signal symmetry may vary from the specified duty cycle as long as the minimum high time and low time

requirements are met.

Ef 0 100.0

ET

ET

ET

H

L

C

4.67 ns

4.25 ns

4.67 ns

4.25 ns

10.00 ns

10.00 ns

157.0 µs

157.0 µs

273.1 µs

0.0 ns

0.0 ns

I

CYC

20.0 ns

10.00 ns

∞

∞

∞

1.8 ns

1.8 ns

∞

8.53 µs

2.5.3 Phase Lock Loop (PLL) Characteristics

Table 2-6. PLL Characteristics

Characteristics

Voltage Controlled Oscillator (VCO) frequency when PLL enabled

(MF × E

PLL external capacitor (PCAP pin to V

•@ MF ≤ 4

× 2/PDF)

f

CCP

) (C

PCAP

1

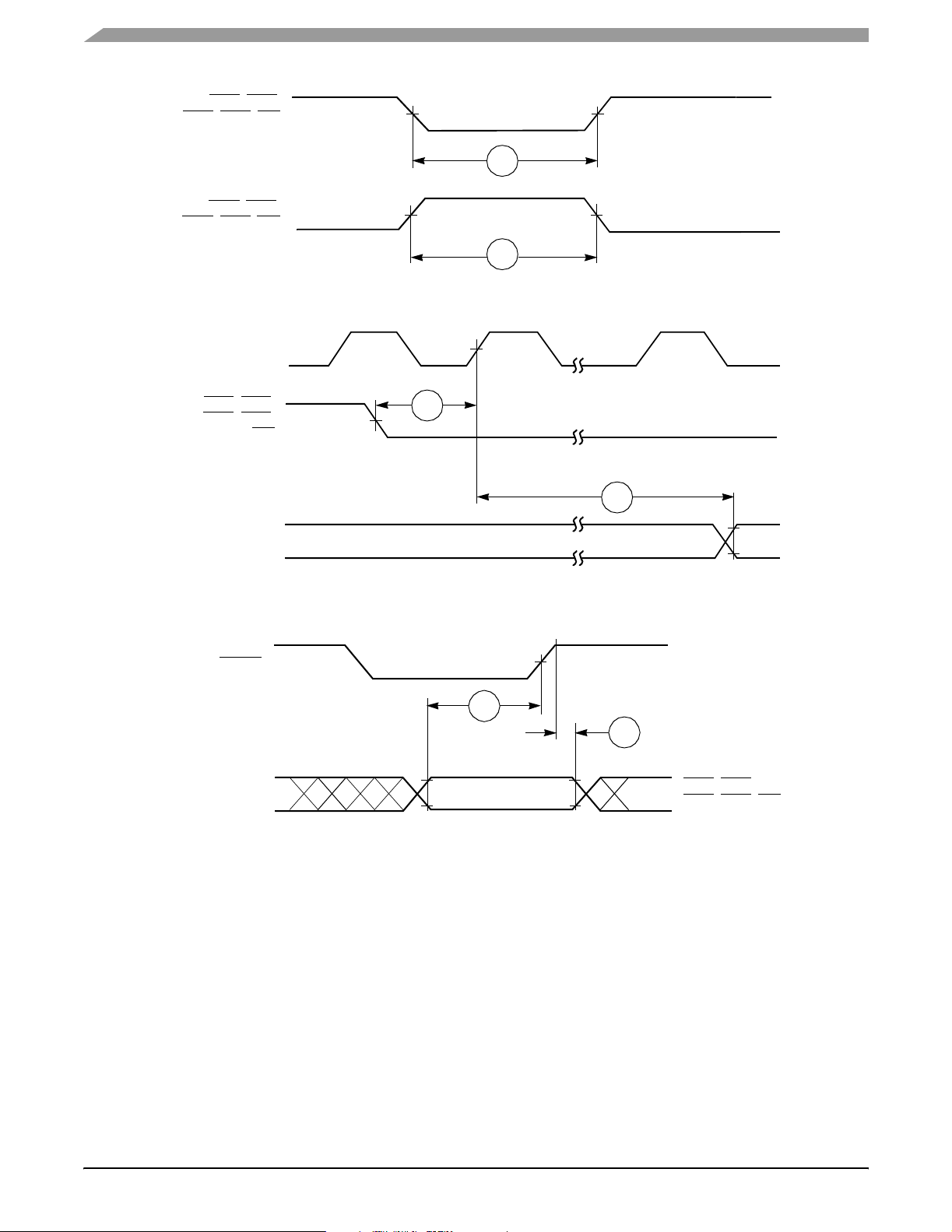

)