Freescale 33999 Advance Information

Freescale Semiconductor

Advance Information

16-Output Switch with SPI

Document Number: MC33999

Rev. 4.0, 4/2007

and PWM Control

The 33999 is a 16-output low-side switch with a 24-bit serial input

control. It is designed for a variety of applications including inductive,

incandescent, and LED loads. The Serial Peripheral Interface (SPI)

provides both input control and diagnostic readout. Eight parallel inputs

are also provided for direct Pulse Width Modulation (PWM) control of

eight dedicated outputs. Additionally, an output-programmable PWM

input provides PWM of any combination of outputs. A dedicated reset

input provides the ability to clear all internal registers and turn all

outputs off.

The 33999 directly interfaces with microcontrollers and is

compatible with both 3.3

in effect, serves as a bus expander and buffer with fault management

features that reduces the MCU’s fault management burden.

Features

• Designed to Operate 5.0 V < V

• 24-Bit SPI for Control and Fault reporting, 3.3 V/5.0 V Compatible

• Outputs Are Current Limited (0.9 A to 2.5 A) to Drive

Incandescent Lamps

• Output Voltage Clamp of +50 V During Inductive Switching

• On/Off Control of Open Load Detect Current (LED Application)

•V

•R

Standby Current < 10 µA

PWR

of 0.55 Ω at 25°C Typical

DS(ON)

• Independent Overtemperature Protection

• Output Selectable for PWM Control

• Output ON Short-to-V

• 54-Pin Exposed Pad Package for Thermal Performance

• Pb-Free Packaging Designated by Suffix Code EK

V and 5.0 V CMOS logic levels. The 33999,

< 27 V

PWR

and OFF Short-to-Ground /Open Detection

BAT

3.3 V/5.0 V

33999

33999

POWER DUAL OCTAL SERIAL SWITCH WITH

SERIAL PERIPHERAL INTERFACE I/O

EK SUFFIX (PB-FREE)

98ASA10506D

Temperature

Range (T

-40°C to 125°C 54 SOICW-EP

V

BAT

)

A

Package

ORDERING INFORMATION

Device

MC33999EK/R2

MCZ33999EK/R2

V

PWR

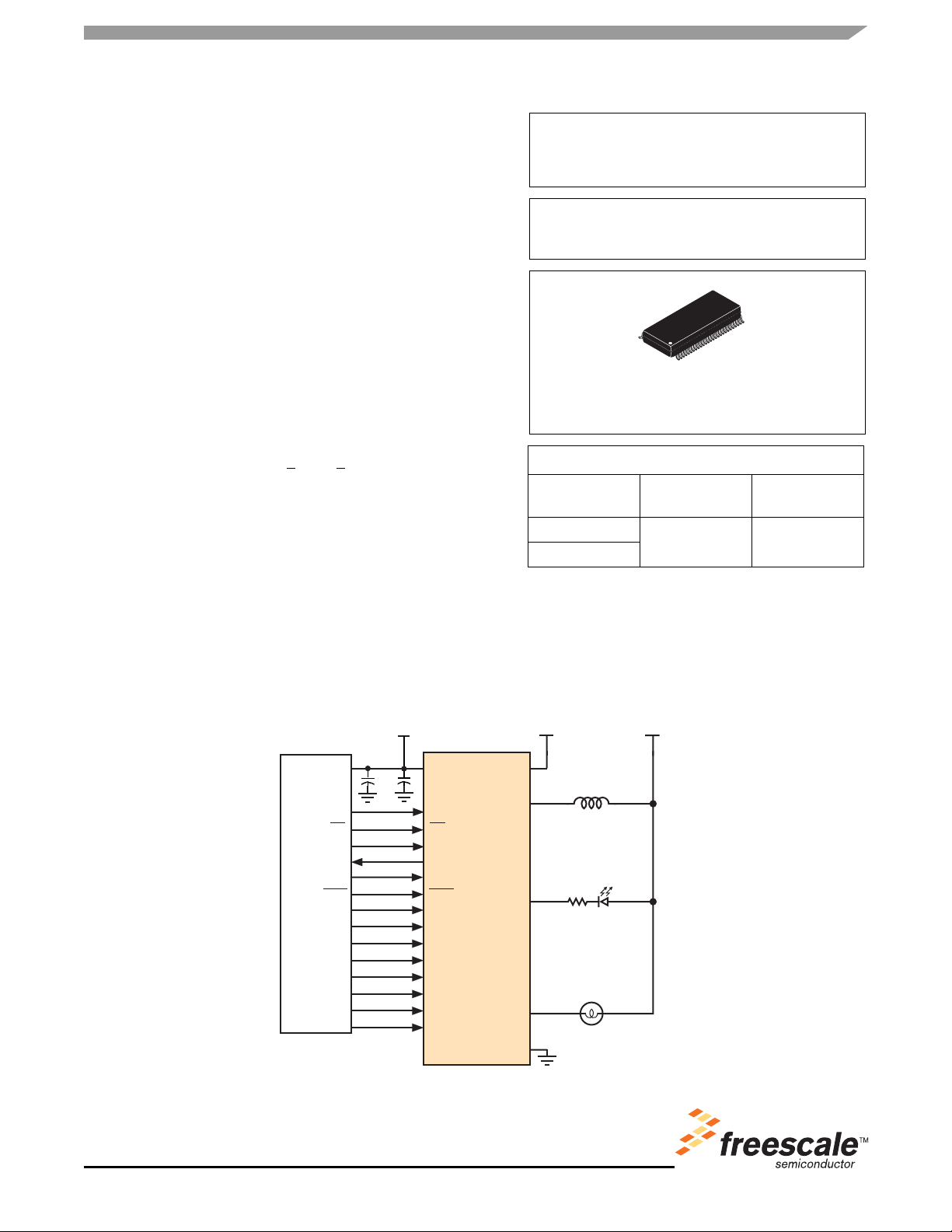

54-PIN SOICW EXPOSED PAD

VDD

MCU

SCLK

CS

MISO

MOSI

PWM

RST

SOPWR

SCLK

CS

SI

SO

PWM

RST

PWM0

PWM1

PWM6

PWM7

PWM8

PWM9

PWM14

PWM15

Figure 1. 33999 Simplified Application Diagram

* This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2007. All rights reserved.

VPWR

OUT0

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

OUT8

OUT9

OUT10

OUT11

OUT12

OUT13

OUT14

OUT15

GND

Solenoid/Relay

LED

Lamp

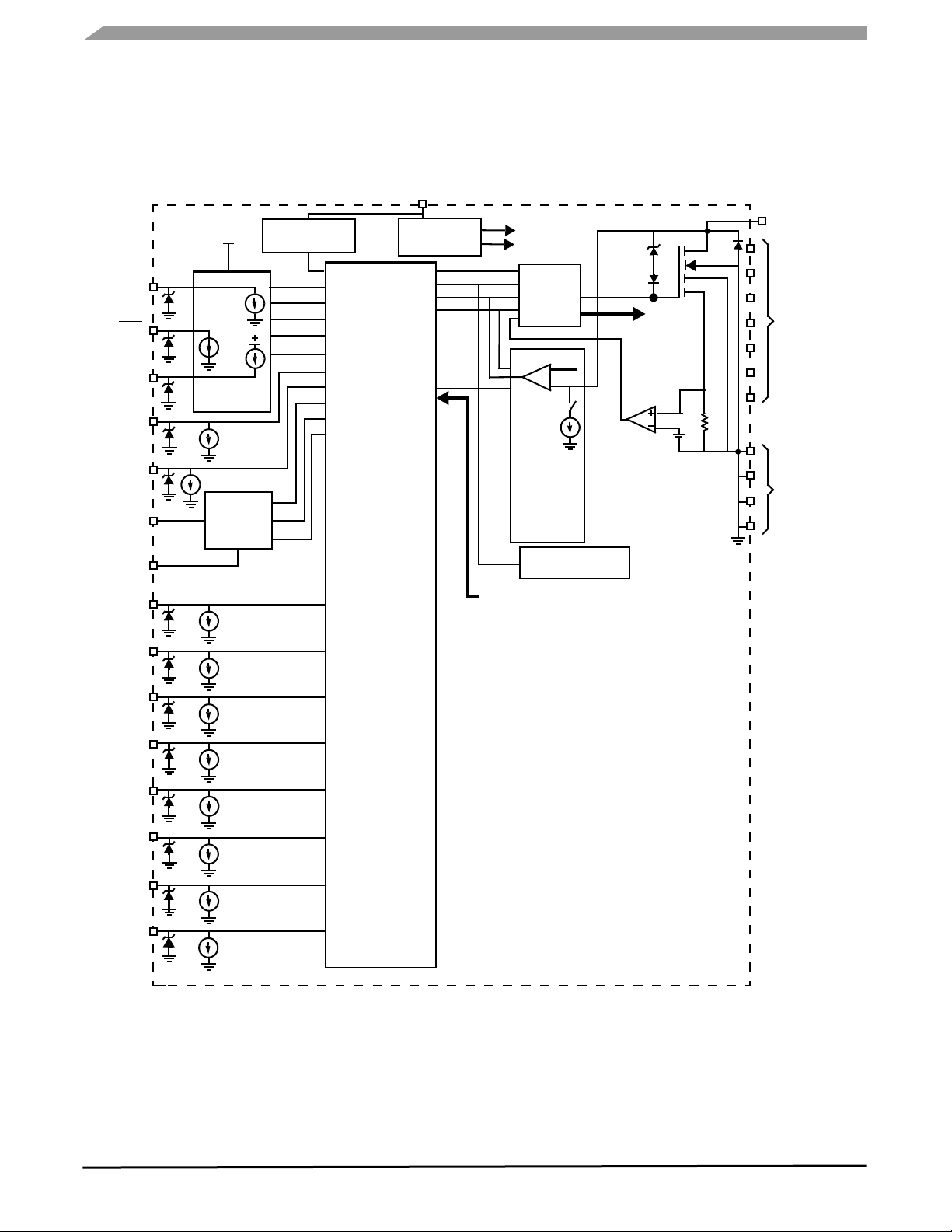

INTERNAL BLOCK DIAGRAM

INTERNAL BLOCK DIAGRAM

V

8

PWR

PWM

50

RST

47

CS

23

SCLK

20

SI

32

SO

35

SO

PWR

PWM0

PWM1

PWM6

24

PWM7

27

PWM8

28

PWM9

31

PWM14

51

PWM15

54

V

DD

10 µA

25 µA

10 µA

Input

Buffers

10 µA

10 µA

Serial D/O

Overvoltage

Detect

OVD

VDD

RB

SFPDB

SFL

CS

SCLK

SI

SO

CSI

CSBI

Open

Load

Detect

Enable

SPI

Interface

Logic

Voltage

Regulator

GE

OT

SF

OF

V

DD

Bias

Gate

Control

V

50 µA

Short and

Open

Circuit

Detect

Ref

50 V

I

To Gates

1 to 15

LIMIT

R

S

2

OUT1– OUT 15:

3, 6, 7, 21, 22,

25, 26, 29, 30,

33, 34, 48, 49,

52, 53

GND Pins:

10 – 18

37 – 40

42 – 45

Line Driver

Overtemperature

OUT0

5

1

4

10 µA

10 µA

PWM0

PWM1

From Detectors 1 to 15

Detect

PWM6

10 µA

PWM7

10 µA

PWM8

10 µA

PWM9

10 µA

PWM14

10 µA

PWM15

10 µA

Figure 2. 33999 Simplified Internal Block Diagram

33999

Analog Integrated Circuit Device Data

2 Freescale Semiconductor

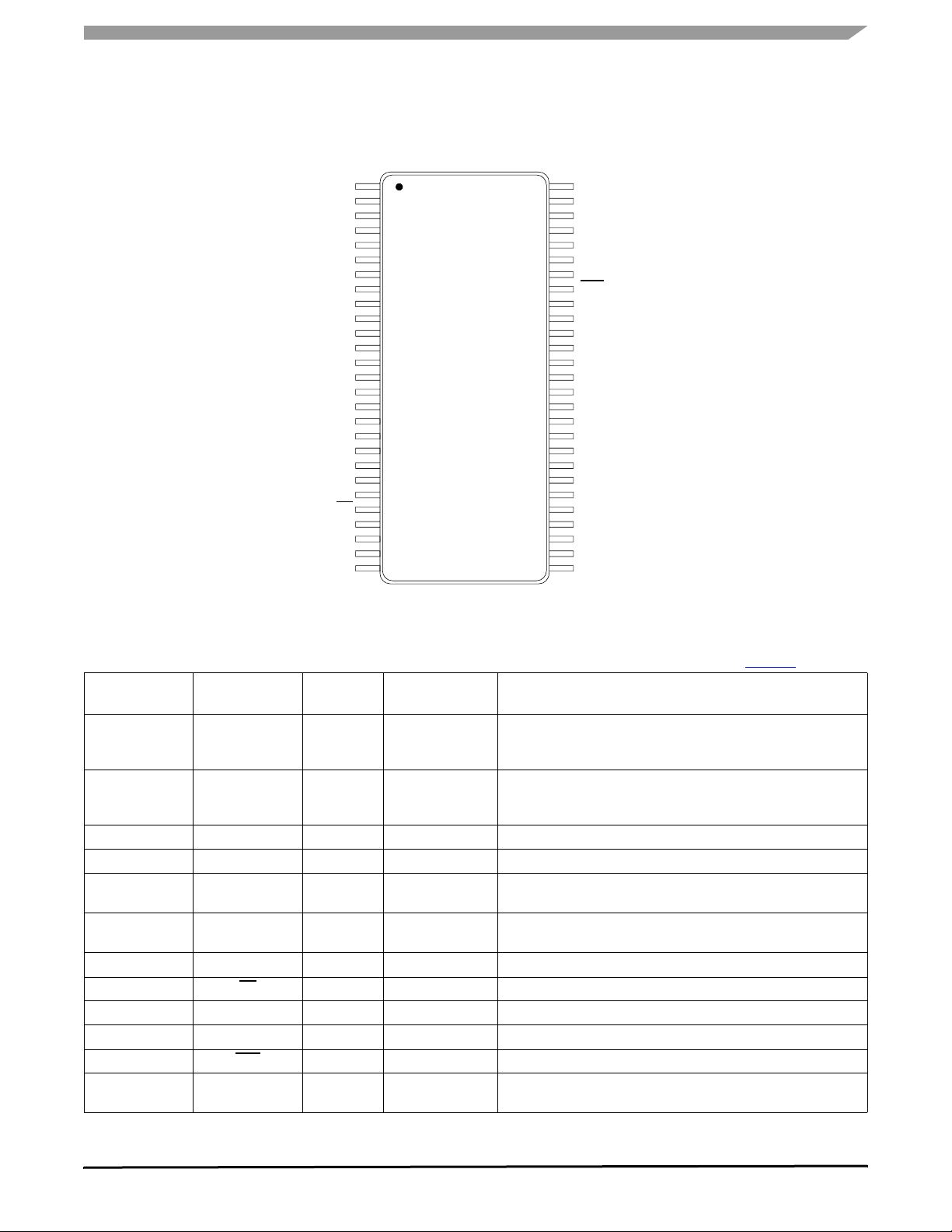

PIN CONNECTIONS

PIN CONNECTIONS

PWM0

OUT0

OUT1

PWM1

SOPWR

OUT2

OUT3

VPWR

NC

NC

GND

GND

GND

GND

GND

GND

GND

NC

NC

SCLK

OUT4

OUT5

CS

PWM6

OUT6

OUT7

PWM7

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

PWM15

OUT15

OUT14

PWM14

PWM

OUT13

OUT12

RST

NC

NC

GND

GND

GND

NC

GND

GND

GND

NC

NC

SO

OUT11

OUT10

SI

PWM9

OUT9

OUT8

PWM8

Figure 3. 33999 Pin Connections

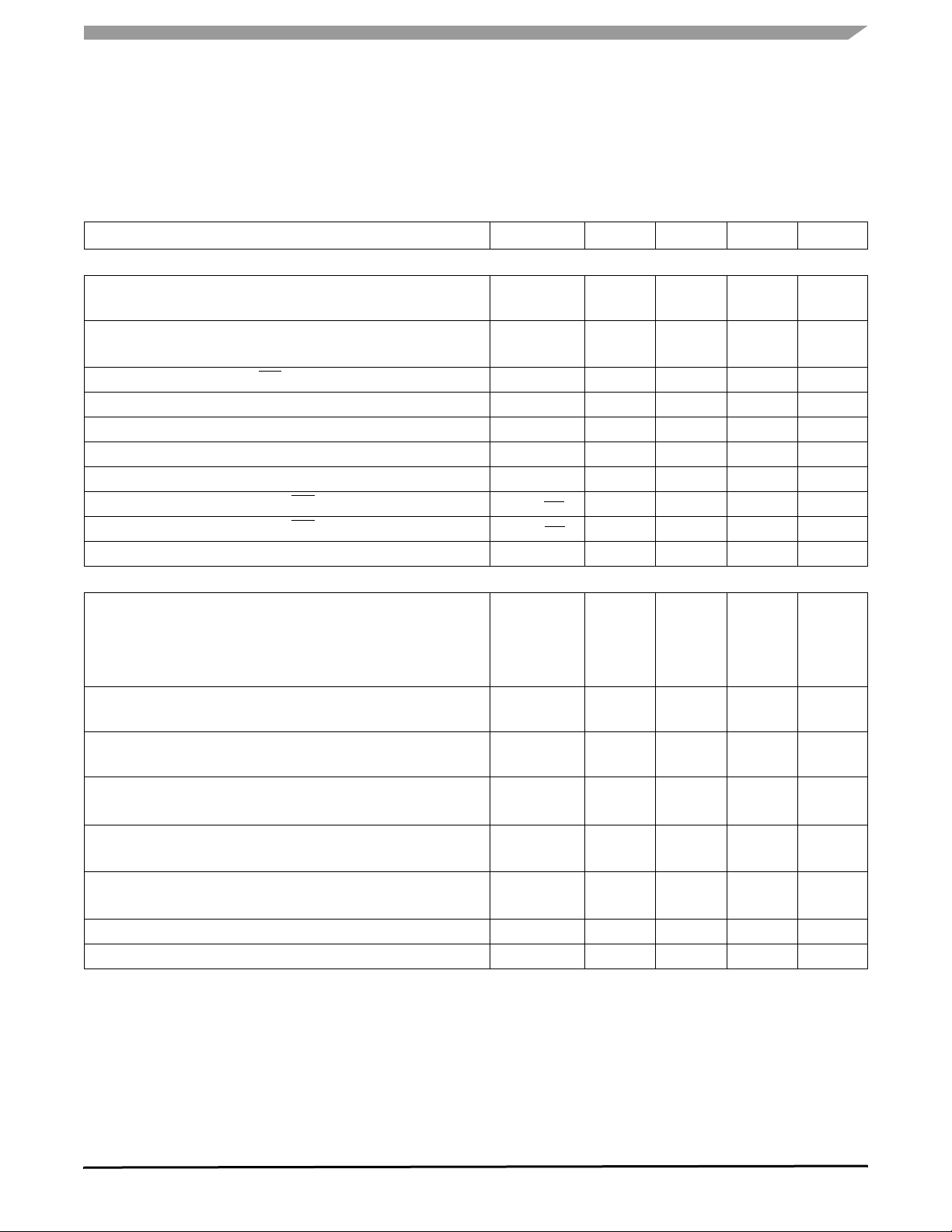

Table 1. 33999 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 10.

Pin Number

1, 4, 24, 27, 28,

31, 51, 54

2, 3, 6, 7, 21, 22,

Pin

Name

PWM0, PWM1,

PWM6

– PWM9,

PWM14,

PWM15

OUT0 – OUT15 Output Output 0 –

25, 26, 29, 30, 33,

34, 48, 49, 52, 53

5 SOPWR Power SO 8 VPWR Input Battery Input

9, 10, 18, 19, 36,

NC N/C No Connect

37, 41, 45, 46

11 –17, 38 – 40,

42

– 44

GND Ground Ground

20 SCLK Input System Clock 23 CS Input Chip Select 32 SI Input Serial Input 35 SO Output Serial Output 47 RST Input Reset 50 PWM Input PWM Control Pin

Pin

Function

Formal Name Definition

Input PWMn Input

Output 15

PWR

Supply

Parallel PWM control Input pins. Allows direct PWM control of

eight outputs.

Low-side driver outputs.

Power supply pin to the SO output driver.

Battery supply input pin.

These pins have no connection.

Ground for logic, analog, and power output devices.

System Clock for internal shift registers of the 33999.

SPI control chip select input pin from MCU to 33999.

Serial data input pin to the 33999.

Serial data output pin.

Active low reset input pin.

PWM control input pin. Supports PWM on any combination of

outputs.

33999

Analog Integrated Circuit Device Data

Freescale Semiconductor 3

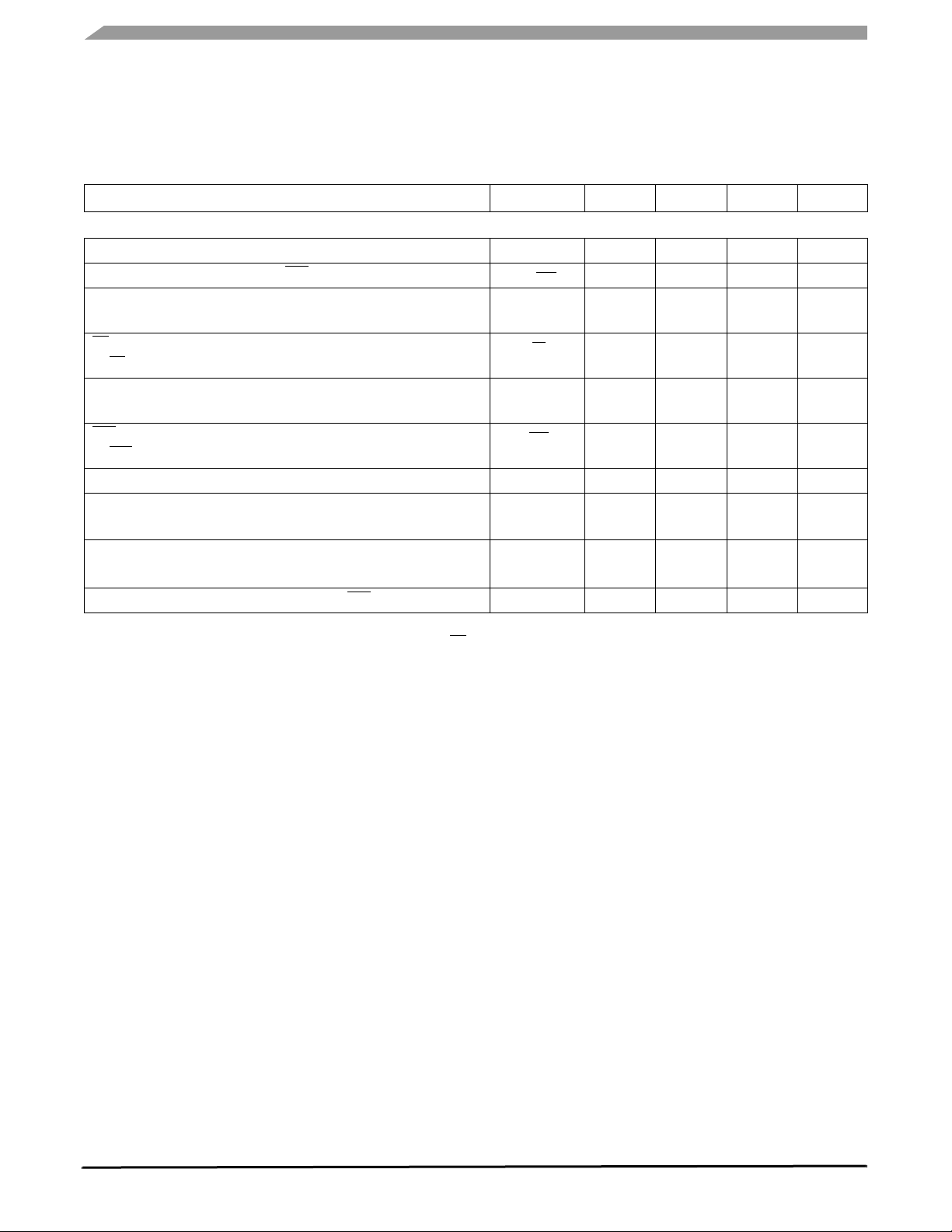

ELECTRICAL CHARACTERISTICS

MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

MAXIMUM RATINGS

Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or

permanent damage to the device.

Ratings Symbol Value Unit

ELECTRICAL RATINGS

VPWR Supply Voltage

SPI Interface Logic Supply Voltage

SPI Interface Logic Input Voltage (CS, PWM, SI, SO, SCLK, RST, PWMn)

Output Drain Voltage

Frequency of SPI Operation

Output Clamp Energy

ESD Voltage

(4)

Human Body Model

Machine Model

THERMAL RATINGS

Operating Temperature

Ambient

Junction

Case

Storage Temperature

Power Dissipation (TA = 25°C)

Peak Package Reflow Temperature During Reflow

Thermal Resistance

Junction-to-Ambient

Junction- to-Lead

Junction-to-Flag

Notes

1. Exceeding these limits may cause malfunction or permanent damage to the device.

2. This parameter is guaranteed by design but not production tested.

3. Maximum output clamp energy capability at 150°C junction temperature using single non-repetitive pulse method.

4. ESD data is available upon request. ESD testing is performed in accordance with the Human Body Model (C

Ω) and the Machine Model (C

5. Maximum power dissipation with no heat sink used.

6. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may

cause malfunction or permanent damage to the device.

7. Freescale’s Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow

Temperature and Moisture Sensitivity Levels (MSL),

Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e.

MC33xxxD enter 33xxx), and review parametrics.

8. Tested per JEDEC test JESD52-2 (single-layer PWB).

9. Tested per JEDEC test JESD51-8 (two-layer PWB).

(1)

(1)

(1)

(2)

(3)

(5)

(6), (7)

V

SO

V

V

f

E

CLAMP

V

ESD1

V

ESD2

T

T

PPRT

PWR

PWR

IN

DS

SPI

T

A

T

J

T

C

STG

P

D

-1.5 to 50 V

-0.3 to 7.0 V

-0.3 to 7.0 V

-0.3 to 45

6.0

MHz

50 mJ

±2000

±200

-40 to 125

-40 to 150

-40 to 125

-55 to 150 °C

1.7 W

Note 7

°C/W

(8)

(9)

= 200 pF, R

ZAP

ZAP

= 0 Ω).

R

JA

θ

R

JL

θ

R

JC

θ

75

8.0

1.2

= 100 pF, R

ZAP

ZAP

V

V

°C

°C

= 1500

33999

Analog Integrated Circuit Device Data

4 Freescale Semiconductor

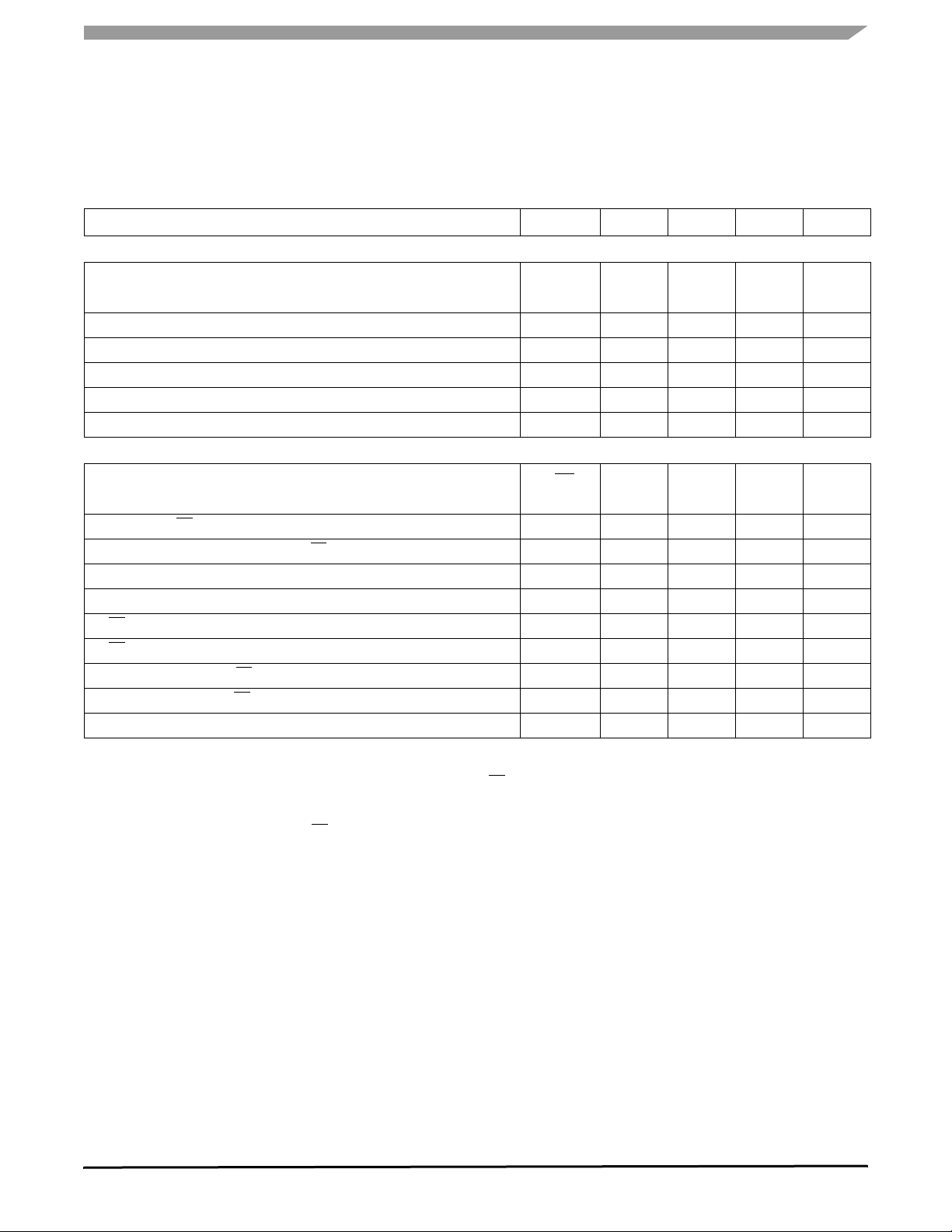

STATIC ELECTRICAL CHARACTERISTICS

Table 3. Static Electrical Characteristics

Characteristics noted under conditions 3.1 V ≤ SO

noted. Typical values noted reflect the approximate parameter means at V

unless otherwise noted.

Characteristic Symbol Min Typ Max Unit

POWER INPUT

Supply Voltage Range

Fully Operational

Supply Current

All Outputs ON, I

Sleep State Supply Current at RST ≤ 0.2 SO

Overvoltage Shutdown

Overvoltage Shutdown Hysteresis

VPWR Undervoltage Shutdown

SPI Interface Logic Supply Voltage

SPI Interface Logic Supply Current (RST Pin High)

SPI Interface Logic Supply Current (RST Pin Low)

SPI Interface Logic Supply Undervoltage Lockout Threshold

POWER OUTPUT

Drain-to-Source ON Resistance (I

TJ = 125°C

TJ = 25°C

TJ = -40°C

OUT

= 0.3 A

= 0.35 A, V

OUT

and / or SO

PWR

PWR

= 13 V)

≤ 5.5 V, 5.0 V ≤ V

PWR

≤ 0.5 V

PWR

V

PWR(FO)

I

PWR(ON)

I

PWR(SS)

V

V

OV (

V

PWR(UV)

SO

I

SOPWR(RSTH)

I

SOPWR(RSTL)

SO

PWR (

R

DS(ON)

STATIC ELECTRICAL CHARACTERISTICS

≤ 18 V, -40°C ≤ TC ≤ 125°C unless otherwise

PWR

= 13 V, TA = 25°C under nominal conditions

PWR

ELECTRICAL CHARACTERISTICS

5.0 – 27

– 4.0 8.0

– 1.0 10 µA

OV

HYS

)

27.5 31.5 35 V

0.6 1.4 2.3 V

– 3.2 4.0 V

PWR

3.1 – 5.5 V

100 – 500 µA

-10 – 10 µA

1.5 2.5 3.0 V

)

UNVOL

–

–

–

0.75

0.55

0.45

1.1

–

–

V

mA

Ω

Output Self-Limiting Current

Outputs Programmed ON

Output Fault Detect Threshold

(10)

Outputs Programmed OFF

Output Off Open Load Detect Current

Outputs Programmed OFF (V

(11)

= 5.0 V, 13 V, 18 V)

PWR

Output Clamp Voltage

2.0 mA ≤ I

OUT

≤ 200 mA

Output Leakage Current

SO

≤ 2.0 V

PWR

Overtemperature Shutdown (Outputs OFF)

Overtemperature Shutdown Hysteresis

(12)

(12)

I

OUT (

V

OUTTH(F)

I

OCO

V

CL

I

OUT (

T

LIM

T

LIM (

LIM

LKG

HYS

)

A

0.9 1.2 2.5

V

2.5 3.0 3.5

µA

25 50 100

V

45 50 55

)

µA

-10 2.0 10

155 165 180 °C

)

5.0 10 20 °C

Notes

10. Output Fault Detect Thresholds with outputs programmed OFF. Output Fault Detect Thresholds are the same for output open and shorts.

11. Output OFF Open Load Detect Current is the current required to flow through the load for the purpose of detecting the existence of an

open load condition when the specific output is commanded to be OFF.

12. This parameter is guaranteed by design but is not production tested.

33999

Analog Integrated Circuit Device Data

Freescale Semiconductor 5

ELECTRICAL CHARACTERISTICS

STATIC ELECTRICAL CHARACTERISTICS

Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions 3.1 V ≤ SO

noted. Typical values noted reflect the approximate parameter means at V

≤ 5.5 V, 5.0 V ≤ V

PWR

≤ 18 V, -40°C ≤ TC ≤ 125°C unless otherwise

PWR

= 13 V, TA = 25°C under nominal conditions

PWR

unless otherwise noted.

Characteristic Symbol Min Typ Max Unit

DIGITAL INTERFACE

Input Logic Voltage Thresholds

Input Logic Voltage Thresholds for RST

SI Pulldown Current

SI = 5.0 V

CS Pullup Current

CS = 0 V

SCLK Pulldown Current

SCLK = 5.0 V

RST Pulldown Current

RST = 5.0 V

PWM and PWMn Pulldown Current

SO High-State Output Voltage

I

= -1.6 mA

SO-high

SO Low-State Output Voltage

I

= 1.6 mA

SO-

low

Input Capacitance on SCLK, SI, Tri-State SO, RST

Notes

13. Upper and lower logic threshold voltage levels apply to SI, CS, SCLK, PWM, and PWMn.

14. This parameter is guaranteed by design but is not production tested.

(13)

(14)

V

INLOGIC

V

INRST

I

I

I

SCLK

I

RST

I

PWM

V

SOH

V

C

SI

CS

SOL

IN

0.8 – 2.2 V

0.8 – 2.2 V

2.0 10 30

-30 -10 -2.0

2.0 10 30

5.0 25 50

2.0 10 30 µA

SO

-

SO

PWR

0.4

PWR

0.2

-

– V

– – 0.4

– – 20 pF

µA

µA

µA

µA

V

33999

Analog Integrated Circuit Device Data

6 Freescale Semiconductor

DYNAMIC ELECTRICAL CHARACTERISTICS

ELECTRICAL CHARACTERISTICS

DYNAMIC ELECTRICAL CHARACTERISTICS

Table 4. Dynamic Electrical Characteristics

Characteristics noted under conditions 3.1 V ≤ SO

noted. Typical values noted reflect the approximate parameter means at V

unless otherwise noted.

Characteristic Symbol Min Typ Max Unit

POWER OUTPUT TIMING

Output Slew Rate

RL = 60 Ω

Output Turn ON Delay Time

Output Turn OFF Delay Time

Output ON Short Fault Disable Report Delay

Output OFF Open Fault Delay Time

Output PWM Frequency

DIGITAL INTERFACE TIMING

Required Low State Duration on V

V

PWR

Falling Edge of CS to Rising Edge of SCLK (Required Setup Time)

Falling Edge of SCLK to Rising Edge of CS (Required Setup Time)

SI to Falling Edge of SCLK (Required Setup Time)

Falling Edge of SCLK to SI (Required Setup Time)

SI, CS, SCLK Signal Rise Time

SI, CS, SCLK Signal Fall Time

Time from Falling Edge of CS to SO Low Impedance

Time from Rising Edge of CS to SO High Impedance

Time from Rising Edge of SCLK to SO Data Valid

Notes

15. Output slew rate measured across a 60 Ω resistive load.

16. Output turn ON and OFF delay time measured from 50% rising edge of CS to 80% and 20% of initial voltage.

17. Duration of fault before fault bit is set. Duration between access times must be greater than 450 µs to read faults.

18. This parameter is guaranteed by design but is not production tested.

19. Rise and Fall time of incoming SI, CS, and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

20. Time required for valid output status data to be available on SO pin.

21. Time required for output status data to be terminated at SO pin.

22. Time required to obtain valid data out from SO following the rise of SCLK with 200 pF load.

23. This parameter is guaranteed by design. Production test equipment used 4.16 MHz, 5.5 V/3.1 V SPI Interface.

(15)

≤ 0.2 V

(18)

(16)

(16)

(23)

(19)

(19)

(17)

PWR

(17)

for Reset

(20)

(21)

(22)

≤ 5.25 V, 9.0 V ≤ V

PWR

≤ 16 V, -40°C ≤ TC ≤ 125°C unless otherwise

PWR

= 13 V, TA = 25°C under nominal conditions

PWR

SR

1.0 2.0 10

T

(ON)

DLY

T

DLY(OFF

T

DLY(SHORT)

T

(

DLY

OPEN

T

FREQ

T

RST

1.0 2.0 10 µs

1.0 4.0 10 µs

)

100 – 450 µs

100 – 450 µs

)

– – 2.0 kHz

– – 10

T

T SI

T SI

T R

T SO

T SO

T

LEAD

T

LAG

(SU)

(

HOLD

(SI)

T F

(SI)

(EN)

(

VALID

DIS

100 – – ns

50 – – ns

16 – – ns

20 – – ns

)

– 5.0 – ns

– 5.0 – ns

– – 50 ns

)

– – 50 ns

– 25 80 ns

V/µs

µs

33999

Analog Integrated Circuit Device Data

Freescale Semiconductor 7

Loading...

Loading...