Force-Mos ME2306D, ME2306D-G Schematics

N-Channel 30V (D-S) MOSFET , ESD Protected

GENERAL DESCRIPTION

The ME2306D is the N-Channel logic enhancement mode power

field effect transistors are produced using high cell density , DMOS

trench technology. This high density process is especially tailored to

minimize on-state resistance. These devices are particularly suited

for low voltage application such as cellular phone and notebook

computer power management and other battery powered circuits

where high-side switching , and low in-line power loss are needed in

a very small outline surface mount package.

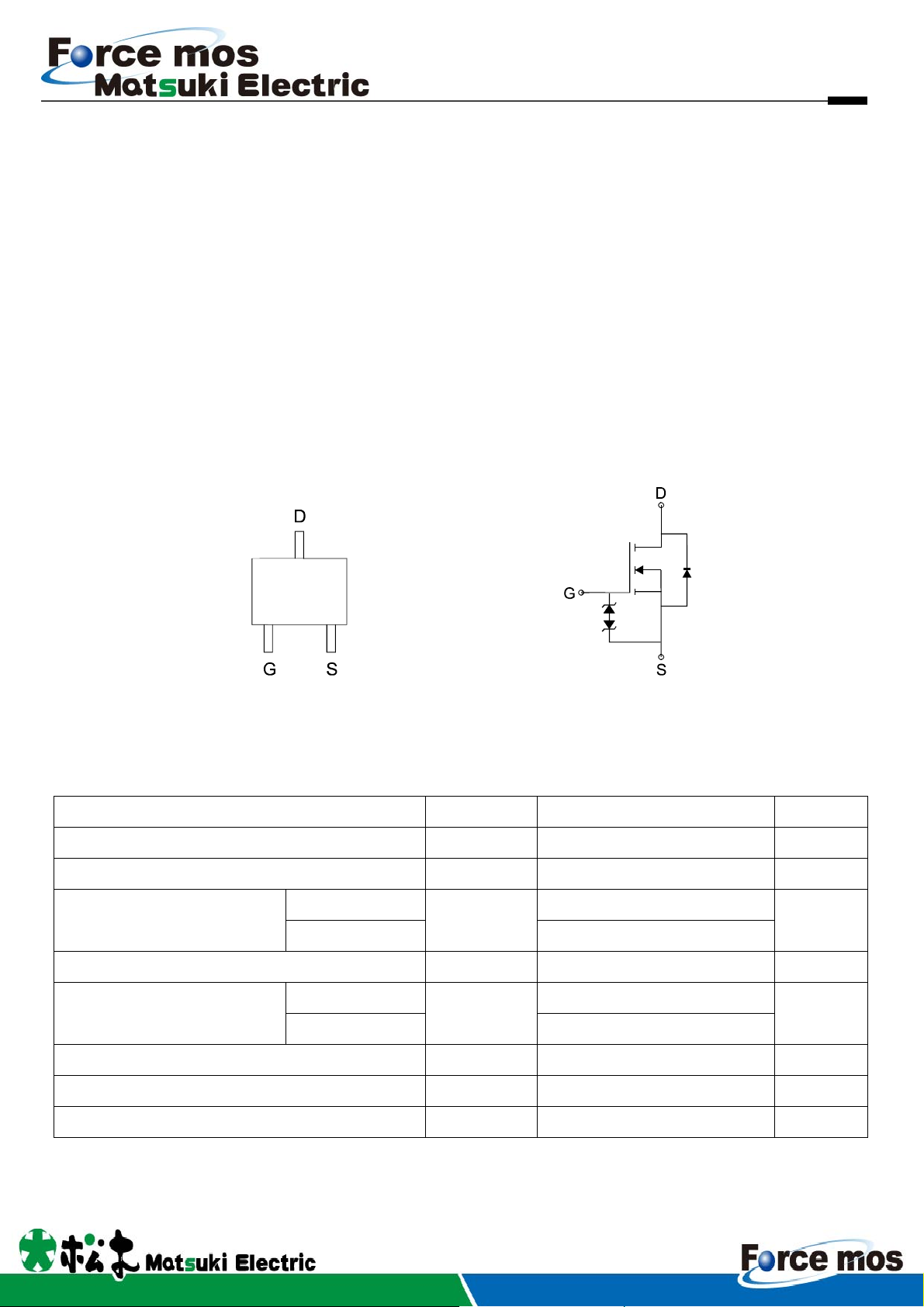

PIN CONFIGURATION

ME2306D/ME2306D-G

FEATURES

● RDS(ON)≦31mΩ@VGS=10V

● RDS(ON)≦52mΩ@VGS=4.5V

● ESD Protected

● Super high density cell design for extremely low RDS(ON)

● Exceptional on-resistance and maximum DC current

capability

APPLICATIONS

● Power Management in Note book

● Portable Equipment

● Load Switch

(SOT-23)

Top View

Ordering Information: ME2306D(Pb-free)

ME2306D-G (Green product-Halogen free)

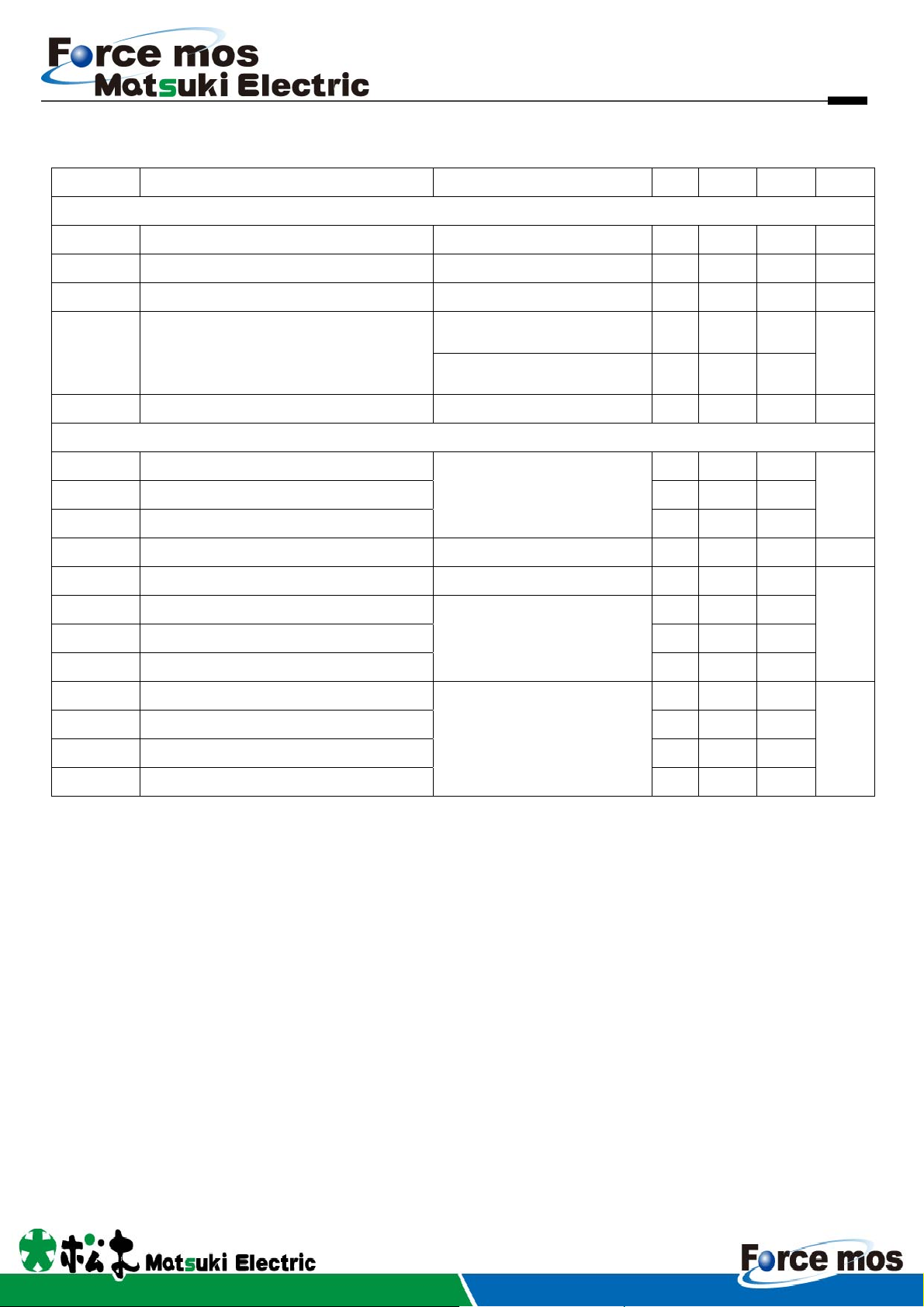

Absolute Maximum Ratings (TA=25℃ Unless Otherwise Noted)

Drain-Source Voltage VDS 30 V

Gate-Source Voltage VGSS ±20 V

Continuous Drain*

Parameter Symbol

TA=25℃

T

A=70℃

Maximum Ratings

I

D

5.3

4.2

Unit

A

Pulsed Drain Current IDM 21.2 A

Maximum Power Dissipation*

Operating Junction Temperature TJ -55 to 150

Storage Temperature Range Tstg -55 to 150

Thermal Resistance-Junction to Ambient*

*The device mounted on 1in

Sep, 2012-Ver1.2

TA=25℃

T

A=70℃

2

FR4 board with 2 oz copper

P

D

θJA 90

R

1.39

0.89

W

℃

℃

℃/W

01

N-Channel 30V (D-S) MOSFET , ESD Protected

Electrical Characteristics (TA =25℃ Unless Otherwise Specified)

ME2306D/ME2306D-G

Symbol Parameter Limit Min Typ Max Unit

STATIC

DS=VGS, ID=250μA

VGS(th) Gate Threshold Voltage

V

1 1.5 3 V

IGSS Gate Leakage Current VDS=0V, VGS=±16V ±10

IDSS Zero Gate Voltage Drain Current VDS=30V, VGS=0V 1

RDS(ON) Drain-Source On-Resistance

VSD Diode Forward Voltage IS=1.7A, VGS=0V 0.8 1.2 V

DYNAMIC

Ciss

COSS

Crss

Rg Gate Resistance f=1MHz

Qg Total Gate Charge VDS=15V, VGS=10V, ID=6.7A

Qg Total Gate Charge

Qgs Gate-Source Charge

Qgd Gate-Drain Charge

td(on)

tr

td(off)

tf

Notes: a. Pulse test: pulse width≦ 300us, duty cycle≦ 2%, Guaranteed by design, not subject to production testing.

Input Capacitance

Output Capacitance

Reverse Transfer Capacitance

Turn-On Delay Time

Turn-On Rise Time

Turn-Off Delay Time

Turn-Off Fall Time

a

VGS=10V, ID= 6.7A 26 31

VGS=4.5V, ID= 5.0A 40 52

370

68

21

1.9

12

5.7

3.0

2.1

9.2

13

33

3.7

V

DS=15V, VGS=0V, f=1MHZ

V

DS=15V, VGS=4.5V, ID=6.7A

V

DD=15V, RL =15Ω

I

D=1.0A, VGEN=10V

R

G=6Ω

μA

μA

mΩ

pF

Ω

nC

ns

b. Matsuki Electric/ Force mos reserves the right to improve product design, functions and reliability without notice.

Sep, 2012-Ver1.2

02

Loading...

Loading...