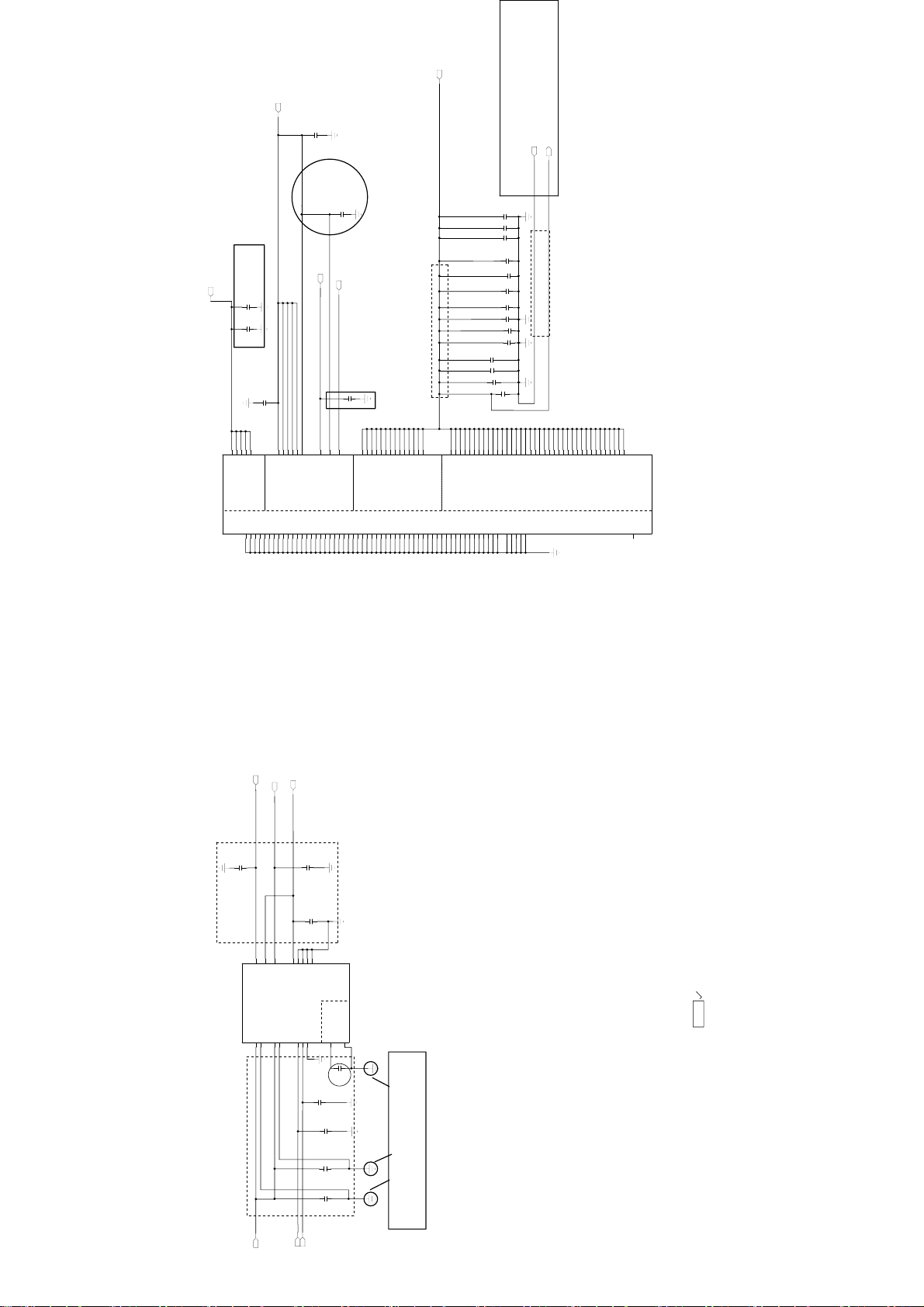

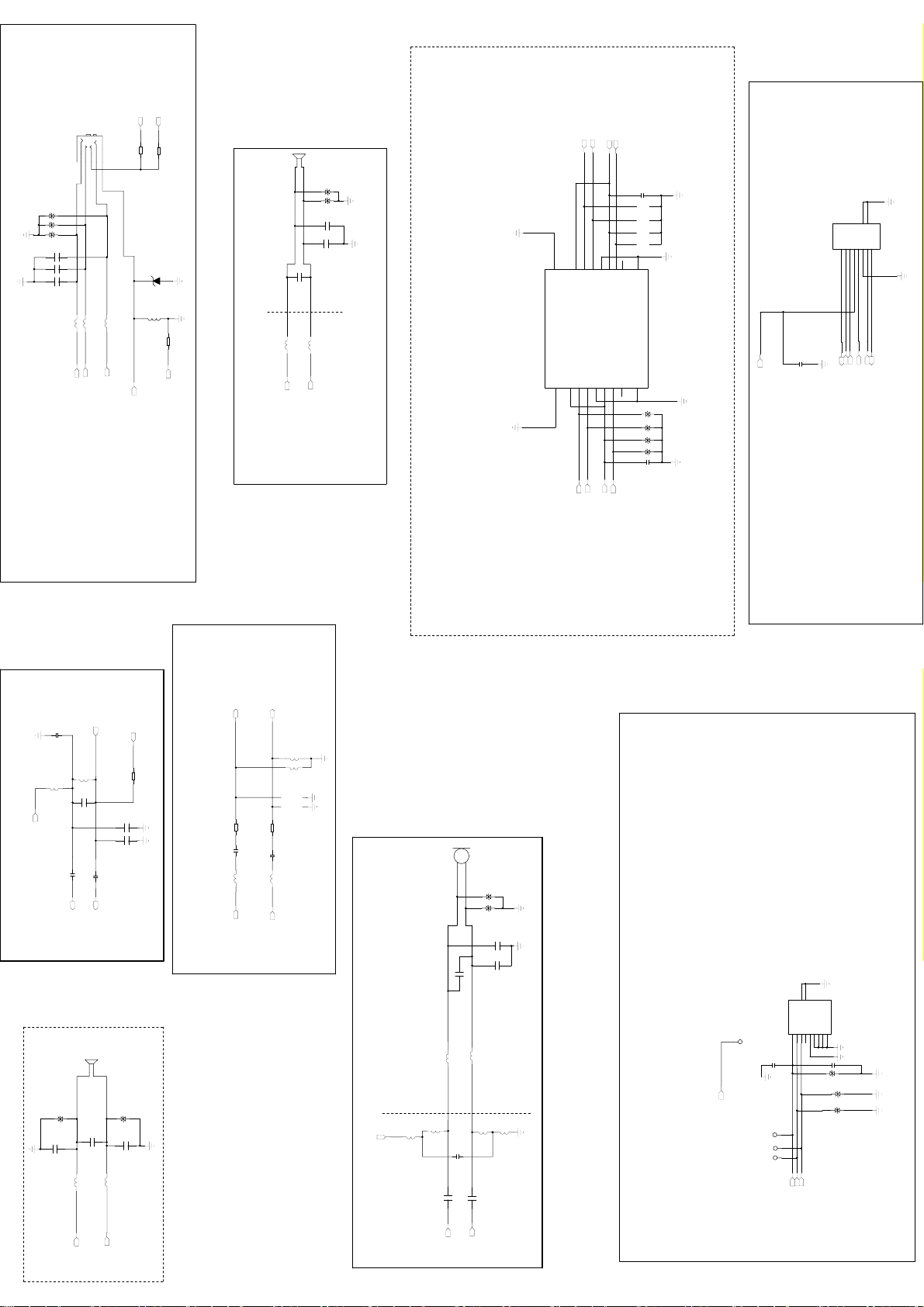

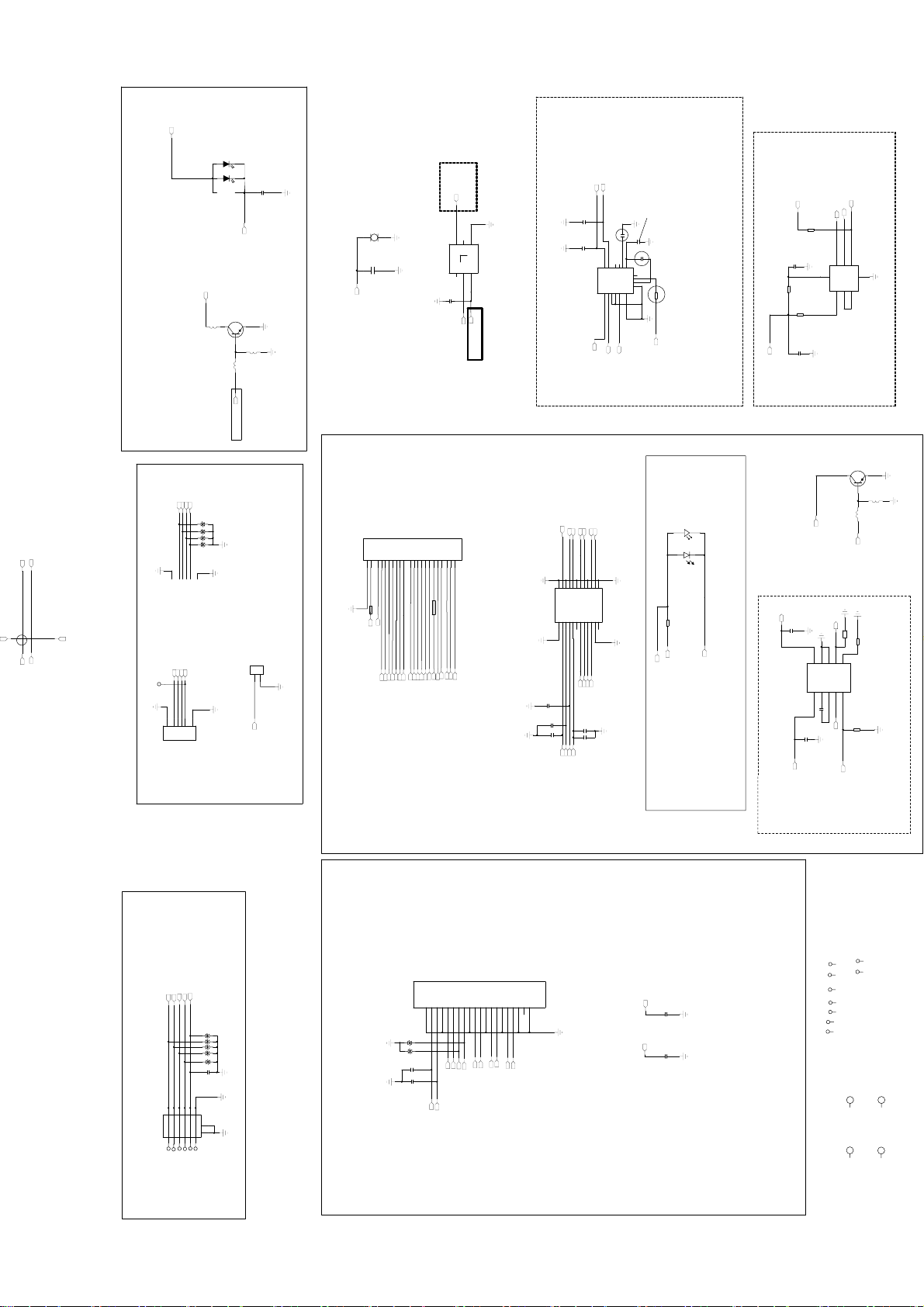

Page 1

[1,2,3,4,5,8]

VIO18_PMU

1uF

C126

If double-sided SMT, put C405 & C406 below BB.

If single-sided SMT, put C405 & C406 around memory.

[4]

VIO_EMI

1.8V IO for DDR1

1.2V IO for DDR2

C131

100nF

C130

100nF

C124

100nF

VMC_PMU

[3]

Based on your system level

design , if better FM performance

is needed on your system ,

please refer to FM desense

performance enhance proposal

C121

100nF

VIO28_PMU

[3,5,7,8]

Close to BB IC, recommand < 150mil

1uF

C117

[1,3]

VPROC_PMU

120mil

TO:MT6323_B12

TO:MT6323_C12

GND

VPROC_PMU

Vproc remote sense :

differential 4mil with good shielding, from the BB to PMIC

[1,3]

[2,3,4,5,6,7,8]

C10310uF

C10210uF

C10610uF

C111

4.7uF

2.2uF(0402)

C137

2.2uF(0402)

C136

1uF

C119

1uF

C134

4mil - defferential - GND shielding

1uF

C120

1uF

C135

RLC0201

100NF

C116

RLC0201

100NF

C118

RLC0201

100NF

C115

RLC0201

100NF

C114

W9

W12

W14

VCCIO_EMI

VCCIO_EMI

VCC

U100-B

100nF

W16

W19

VCCIO_EMI

VCCIO_EMI

Memory

GND

AC21

AB11

C108

VCCIO_EMI

GND

GND

AF13

[3,5]

VTCXO_PMU

GND

AD11

GND

AC8

AB5

AA1

DVDD18_MC0

Peripheral

DVDD

GND

GND

GND

W26

AB14

[1,2,3,4,5,8]

VIO18_PMU

L3

K20

DVDD18_CAM

DVDD18_VIO_1

GND

GND

T15

W23

H13

AB24

J19

DVDD18_LCD

DVDD18_VIO_3

DVDD18_VIO_2

GND

GNDG3GND

GND

T14

K21

AF26

[1,2,3,4,5,8]

VIO18_PMU

100nF

K24

P6

W24

P7

C10

T7

VCCK_CPU

VCCK_CPUP8VCCK_CPUP9VCCK_CPUR6VCCK_CPUR7VCCK_CPUR8VCCK_CPUR9VCCK_CPUT6VCCK_CPU

GND

L15

DVDD3_LCD

GNDM5GND

L16

DVDD28_BPI

GND

GND

M11

M12

VCCK_CPU

CPU

VCC

GND

GND

GND

GND

GNDN8GNDN9GND

GND

GND

GND

M13

GND

M14

M15

M16

N10

N11

N12

N13

N14

Based on your system level design

GND

N15

1. use RTP

DVDD3_MC1

GND

GND

GND

L11

L12

L14

C128

J9

J15

K11

K14

K15

M9

T8

VCCK

VCCKK6VCCKK7VCCKK8VCCKK9VCCK

VCCK

VCCK

VCCK

VCCK

VCCK_CPUT9VCCK_CPUU6VCCK_CPUU7VCCK_CPU

Core

VCC

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

N16

N22

P10

P11

P12

P13

P14

P15

P16

R10

AVDD18_AP = ext. 1.8V LDO

cap = 0.1uF

2. use AUXADC, no RTP

AVDD18_AP = VIO18

cap = 0.1uF (NC)

3. no use AUXADC, no RTP

GND

R11

R12

R13

R14

R15

R16

T10

T11

T12

T13

AVDD18_AP = VIO18

cap = none (share with C112)

K16

K17

M10

VCCK

VCCK

VCCKJ8VCCK

GND

GND

AF1

U10

K12

GND

L17

VCCKM6VCCKM7VCCKM8VCCK

L6

J10

J11

J14

T16

T17

J16

J17

U12

U13

U14

U15

U16

M17

R17

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

DUMMY

MT6572/TFBGA428/P0.4/B0.25/10.6X10.6

A26

L7

U17

VCCKL8VCCKL9VCCK

VCCK

GND

GND

GND

U11

V13

W11

Y21

cap Close to BB IC

E5

F1

AVDD28_DAC

U100-H

DVDD18_MIPIRX

DVSS18_MIPIRX

T25

U25

cap Close to BB IC

VIO18_PMU

[1,2,3,4,5,8]

U9

AVDD18_AP

R25

DVDD18_PLLGP

DVDD18_MIPITX

DVSS18_MIPITX

P25

100nF

A1

D3

AVSS18_MDA4AVSS18_MDC3AVSS18_MDE2AVSS18_MD

AVDD18_MD

AVDD18_USB

AVDD33_USB

H23

G24

G23

VUSB_PMU

VIO18_PMU

[3]

[1,2,3,4,5,8]

C112

AVSS33_USB

1uF

BG

REFPG6REFN

F6

0.1uF

C113

C104

100nF

C101

100nF

C107

100nF

MT6572/TFBGA428/P0.4/B0.25/10.6X10.6

C109

dedicate VSS ball, must return to cap then to main GND:

1. REFN(G6) => C109

2. DVSS18_MIPIRX(U25) => C107

3. DVSS18_MIPITX(P25) => C101

6572M

6572A/X

WCDMA: 6572A/W

6572A/F

GSM: 6572A/E

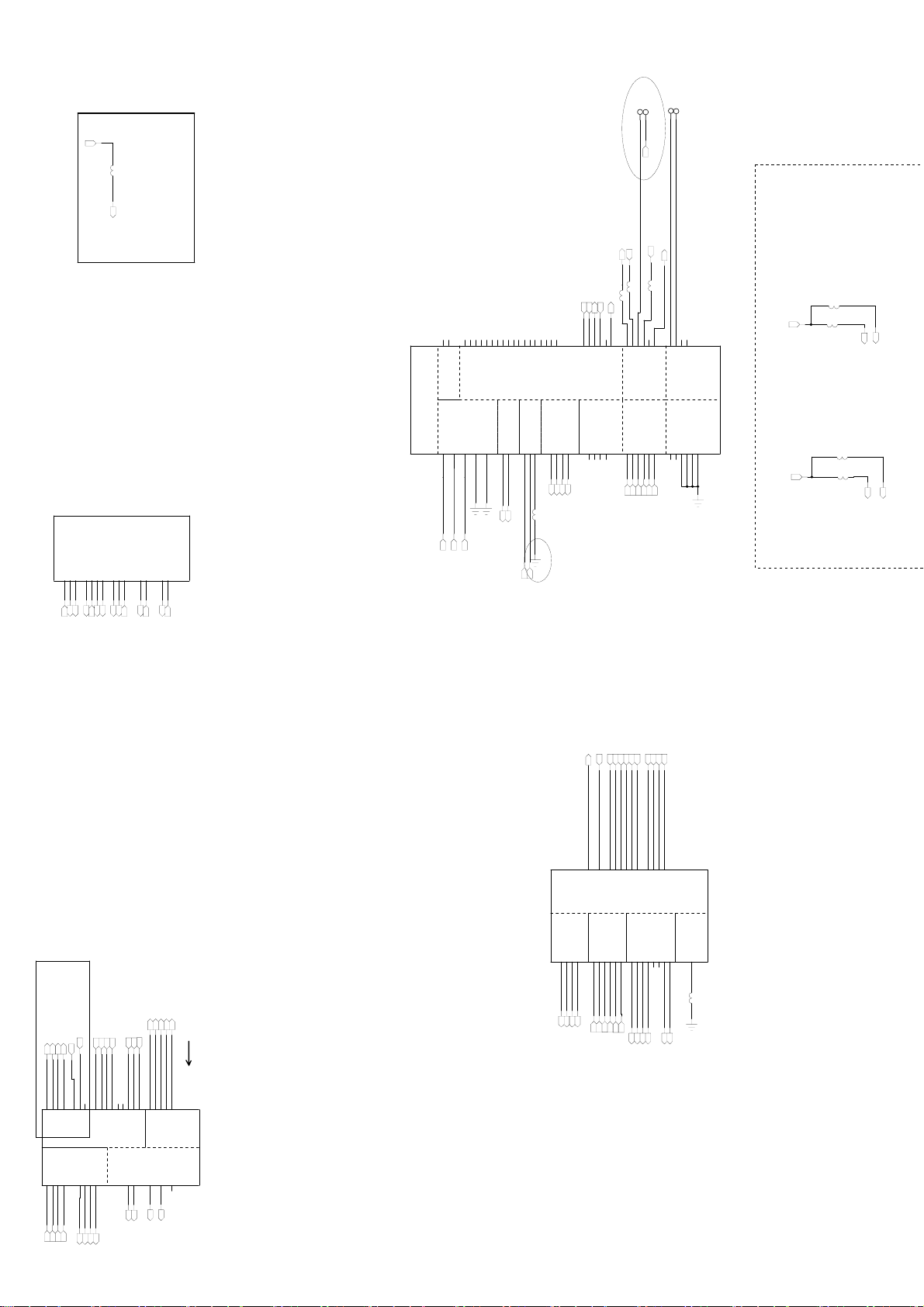

Page 2

~

~

TPLED5

TPLED1

TPLED2

TPLED3

VIO18_PMU

[1,2,3,4,5,8]

R213 NC

reserve for JTAG debug

U100-D

AUD_DAT_MISOK5AUD_CLK_MOSIK1AUD_DAT_MOSIH4SRCLKENA

J1

AUD_MISO

[3]

SIM1_SCLK

[2,3]

PMIC_SPI_CSN

PMIC_SPI_MOSIL5PMIC_SPI_MISOL4PMIC_SPI_SCKG2WATCHDOGJ2EINTXH5SIM1_SCLKM3SIM1_SIOJ5SIM2_SCLKM1SIM2_SIO

K2

L2

SRCLKENA

WATCHDOG

PMIC_SPI_CS

PMIC_SPI_SCK

PMIC_SPI_MISO

[3]

[3]

[3] PMIC_SPI_MOSI

[3,4]

[3,4]

EINT_PMIC

[3,5]

[3]

AUD_MOSI

[3]

[3] AUD_CLK

JTAG : 20K

Normal : NC

Reserve R footprint

SIM1_SIO

SIM2_SIO

SIM2_SCLK

[3]

[2,3]SIM1_SCLK

[3]

[3]

for JTAG debugging

MT6572/TFBGA428/P0.4/B0.25/10.6X10.6

U100-E

D12

E12

PWM_A

PWM_B

PWM

SYSTEM

CLK32K_ING4TESTMODE

CLK26M

H2

E1

CLK1_BB

CLK32K_BB

[3]

[5]

N2

N3

LPD16N1LPD17

LPD15P2LPD14N4LPD13R2LPD12N5LPD11R1LPD10

Parallel

LCD

SYSRSTB

M2

RESETB

[3]

FSOURCE

AC24

BC 1.1

CHD_DP

J26

CHD_DP

[3]

P5

T2

LPD6T5LPD5U2LPD4T3LPD3U5LPD2T4LPD1V2LPD0

LPD9T1LPD8R5LPD7

i2C

USB 2.0

USB_DM

USB_DP

CHD_DM

USB_VRT

G26

G25

J25

H25

USB_VRT

5.1K 1%

R2

CHD_DM

[3]

90-ohm differential

USB_DP

USB_DM

close to BB

[7]

[7]

KCOL2

MT6572 support JTAG from below :

1. KP (recommand)

2. MC1

3. CAM

[8]

[8]

[8]GPIO59_LRSTB

LPTE

G_SENSOR_INT

AC26

AB26

AD25

AA22

LPTE

LRSTB

LPCE0B

SPI

SCL_0

SDA_0

SCL_1

SDA_1

SPI_MOSI

SPI_MISO

C25

C26

B24

B23

F25

F23

F24

SDA_0

SCL_1

SCL_0

SDA_1

[2,8]

[2,8]

[2,8]

[2,8]

[2]

for JTAG pin out from MC1/CAM, refer

to HW design notice

[7,8]

[2]

[8]

[8]

KCOL0

KROW0

KCOL2

KROW1

[8]

[8]

R77

R79

R75

GPIO57_CTP_RSTB

GPIO58_FLASH_SEL

LPRDB

SPI_SCK

AB23

E23

LPA0

SPI_CS

1K

1K

1K

AC25

B25

A24

B26

A25

D24

C24

E25

LPWRB

KROW0

KROW1

KROW2

KCOL2

KCOL1

KCOL0

UTXD1

KP

UART

ADC

T-flash

AUX_IN0B6AUX_IN1B5AUX_IN3_YPC4AUX_IN4_XMA5AUX_IN5_YM

MC1_CMD

MC1_CK

MC1_DAT0

MC1_DAT3

MC1_DAT2

MC1_DAT1

B7

K23

L21

K22

L26

M25

M22

MC1CK

MC1CMD

MC1DAT0

MC1DAT1

MC1DAT3

MC1DAT2

[7]

[7]

[7]

[7]

[7]

[7]

E26

D25

URXD1

C5

F26

UTXD2

URXD2

AUX_IN2_XP

VIO18_PMU

[1,2,3,4,5,8]

MT6572/TFBGA428/P0.4/B0.25/10.6X10.6

VCAMD_IO_PMU

[3,8]

Power by CTP, MEMS sensor

R207 2.2K

R206 2.2K

SDA_1

SCL_1

[2,8]

[2,8]

Power by CAM_IO

R205 2.2K

R204 2.2K

SDA_0

SCL_0

[2,8]

[2,8]

2.8V

[5]

[5]

[5]

[5]

[5]

[5]

[8]

[5]

[7]

EINT0_HP

WG_GGE_PA_ENABLE

W_HB_V2

W_PA_H_EN

W_PA_L_EN

ASM_VCTRL_B

ASM_VCTRL_A

ASM_VCTRL_C

11 are 2G+3G mode both

GPIO134

4 and 10

BPI0

BPI5~9 and 12~14 are 3G mode only

(suggest BPI5~9 = 1.8V)

B12

B11

C12

A11

D11

C11

A13

A10

B10

D10

BPI_BUS0

BPI_BUS1

BPI_BUS2

BPI_BUS3

BPI_BUS4

BPI_BUS5

BPI_BUS6

BPI_BUS7

BPI_BUS8

4

U100-A

DL_I_NC1DL_Q_NB1DL_Q_PD2DL_I_PA2UL_I_PB2UL_I_NB3UL_Q_NB4UL_Q_P

C2

1.8V

[8]GPIO144_FLASH_EN

[8]

[8]

[5]

[5]

[5]

BSI-A_DAT2

BSI-A_DAT1

EINT8_CTP

EINT4_ALPXS

W_HB_V1

D7

E9

D6

E7

E8

BPI_BUS9

BPI_BUS15

BPI_BUS10C7BSI_DATA1

BSI_DATA2

BPI_BUS14

BPI_BUS11B9BPI_BUS12B8BPI_BUS13

VM0A7VM1D5TXBPIF2APCF3VBIAS

A8

[5]

[5]

[5]

BSI-A_EN

BSI-A_CK

BSI-A_DAT0

Must be sure BPI_BUS4 & 5 is under

0.2*VDD28_BPI during booting

(please refer to HW design notice V0.4)

F11

F9

G11

BSI_EN

BSI_CLK

BSI_DATA0

MT6572/TFBGA428/P0.4/B0.25/10.6X10.6

[8]

[8]

[8]

[8]

[8]

[8]

CMHSYNC

CMDAT6

CMDAT7

CMVSYNC

CMPCLK

CMMCLK

V23

V24

W25

V25

Y22

Y23

RCP_A

RCN_A

RDP1_A

RDN1_A

CMMCLK

CMPCLK

Parallel 8-bit

U100-G

MIPI_2nd_CAM

CMPDN2

CMRST2

CMPDN

L25

K25

H22

CMRST2

CMPDN2

GPIO_CMPDN

[8]

[8]

[8]

CMRST

J22

GPIO_CMRST

[8]

MIPI_CAM

RDN0

R24

R23

MIPI_RDN0

MIPI_RDP0

[8]

RDN1

RDP0

R22

MIPI_RDN1

[8]

[8]

RCN

RDP1

R26

R21

MIPI_RCN

MIPI_RDP1

[8]

[8]

RCP

T26

MIPI_RCP

[8]

Based on your system level design , if better

desense performance is needed on your

system , please refer to desense

performance enhance proposal

[8]

[8]

[8]

[8]

[8]

[8]CMDAT1

CMDAT4

CMDAT5

CMDAT0

CMDAT2

CMDAT3

U21

U22

Y26

Y25

AA25

AB25

RDP0_A

RDN0_A

CMDAT3

CMDAT2

CMDAT1

CMDAT0

MIPI_LCD

TDP0

TDN1

TDN0

TDP1

TCN

TCP

TDP2

TDN2

P20

N25

P19

N26

N20

N19

P24

P23

MIPI_TDP0

MIPI_TDN0

MIPI_TCN

MIPI_TCP

MIPI_TDN1

MIPI_TDP1

[8]

[8]

[8]

[8]

[8]

[8]

100-ohm differential

VRT

MT6572/TFBGA428/P0.4/B0.25/10.6X10.6

P26

R202 1.5K 1%

close to BB

100-ohm differential

1. All MIPI port can NOT as Output function

2. MIPI group function is mutually exclusive with Input function

(please refer to HW design notice V0.5)

VM1

VM0

TXBPI

[5]

[5]

RX_I_P

[5]

RX_I_N

[5]

RX_Q_P

[5]

RX_Q_N

[5]

TX_I_P

[5]

TX_I_N

[5]

TX_Q_P

[5]

TX_Q_N

[5]

[5]

WG_GGE_PA_VRAMP

[5]

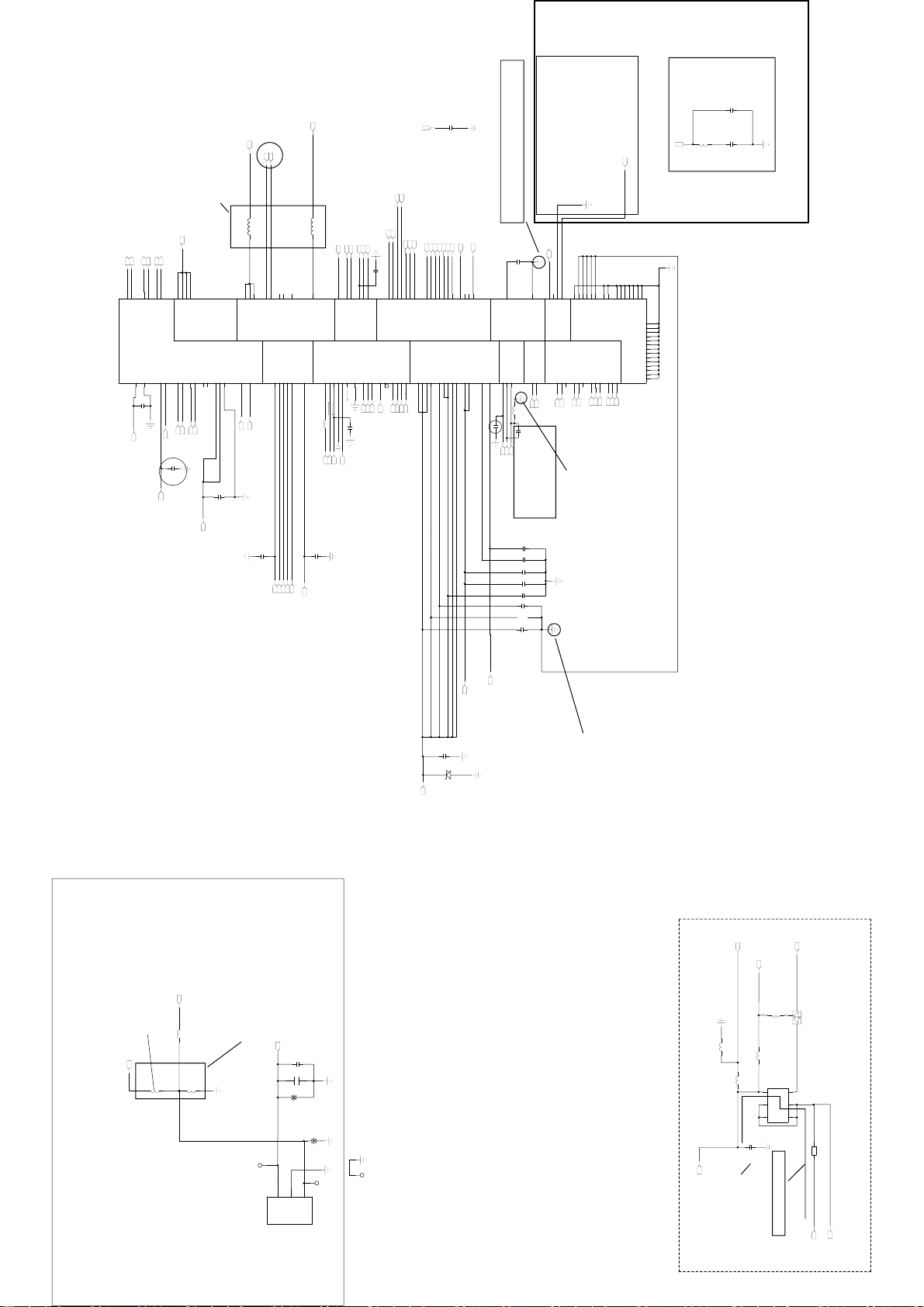

Page 3

[7]

[7]

[7]

[7]

AU_HSN

AU_SPKN

AU_SPKP

AU_HSP

H1

K1

G1

SPK_PL1SPK_N

AU_HSP

AU_HSNH4AU_HPLJ4AU_HPR

U301

MT6323/VFBGA145/P0.4/B0.25/5.8X5.8

VBAT_SPKE4AU_VIN0_PF4AU_VIN0_NG3AU_VIN1_PG4AU_VIN1_ND2AU_VIN2_PD1AU_VIN2_N

GND_SPK

P1

L2

C313

2.2uF(0402)

VBAT

[3,5,8]

if you use digital MIC,

please change cap (C312)

to 1.0uF

[7]

[7]

AU_HPR

AU_HPL

AU_MICBIAS0G2AU_MICBIAS1

F2

[7]

MICBIAS1

MICBIAS0

[7]

[8]

Please use inductor recommand by MTK

Refer to MT6323 design notice

LED-

E9

E10

C10

ISINK0C9ISINK1

ISINK2

ISINK3

DRIVER

AUDIO

AVDD28_ABB

J2

[7]

[7]

[7]

[7]

AU_VIN1_N

AU_VIN0_P

AU_VIN1_P

AU_VIN0_N

C312

100nF

1uF

VA_PMU

[3]

AVDD28_AUXADCH2GND_ABB

D3

C314

L301 0.68uH

C14

BUCK OUTPUT

ACCDET

E2

ACCDET

[7]

VPROC_PMU

D14

VPROC

VPROC

CLK26M

E1

[1,3]

E14

CLK4_AUDIO

[5]

VPROC

ISENSE/BSTSNS 4mil

TO:C114-

TO:C114+

[1,3]

VPROC_PMU

[1,2,4,5,6,7,8]

GND

B14

B12

A14

D12

C12

VPA

VPA

VPA_FB

VPROC_FB

GND_VPROC_FB

CHARGER

VCDT

VDRV

ISENSE

BATSNSK3BATON

A12

M13

P12

P13

VBAT

VCDT

ISENSE

BAT_ON

VDRV

1uF

C302

VCDT

ISENSE

VBAT

BAT_ON

[3]

[3]

[3]

[3] VDRV

[3,5,8]

differential to Rsense

CHRLDO

N13

CHR_LDO

CHR_LDO

[3]

[3]

VSYS_PMU

L303 0.68uH

H14

VSYS

1uF

[3]

VA_PMU

6mil

8mil

M3

VA

ALDO OUTPUT

CONTROL SIGNAL

RESETBM2PWRKEYN2PMU_TESTMODEB6AUD_MISO

FSOURCEE7AUD_MOSIE8AUD_CLK

INT

SYSRSTB

K4

A9

A7

A1

1K

R316

RESETB

PWRKEY

WATCHDOG

EINT_PMIC

[8]

[2]

[2]

[2,4]

C316

[6]

[1,5]

VTCXO_PMU

VCN_2V8_PMU

6mil

L4

N3

VTCXO

VCN28

EXT_PMIC_EN

N12

10nF

C351

[8]

[6]

VCAMA_PMU

VCN_3V3_PMU

12mil

P3

VCAMAM6VCN33

AUD_MOSI

[2]

[3]

VRTC

6mil

12mil

C3

AVDD33_RTC

AUD_CLK

[2]

AUD_MISO

[2]

[4]

C355

1uF

J13VMH11

DLDO OUTPUT

SRCLKEN

FCHR_ENBD9SPI_CLK

A2

M1

SRCLKENA

[2,5]

[5]

VM_PMU

VRF18_PMU

15mil

35mil

L12

VRF18

B7

PMIC_SPI_SCK

PMIC_SPI_CS

[2]

[1,5,7,8]

[1,2,3,4,5,8]

VIO18_PMU

VIO28_PMU

[8]

[6]

VCN_1V8_PMU

VCAMD_PMU

8mil

15mil

12mil

12mil

M4

K14

J12

VIO18

VIO28

VCAMD

VCN18

SPI_CSND8SPI_MOSIB8SPI_MISO

PMIC_SPI_MOSI

PMIC_SPI_MISO

[2]

[2]

[2,4]

VEMC_3V3_PMU

[3,4]

[2,8]

[3,4]

[7]

[1]

VCAMD_IO_PMU

VEMC_3V3_PMU

VMC_PMU

VMCH_PMU

12mil

15mil

6mil

8mil

L6

P4

L13

P7

VMC

VMCHL8VGP1N6VUSB

VCAM_IO

VEMC_3V3

VBAT INPUT

VBAT_VPROC

VBAT_VPAP5VBAT_LDOS2

VBAT_VPROCP2VBAT_LDOS1

VBAT_VPROC

F14

A13

G13

F13

30mil

30mil

15mil

100nF

C354

[8]

[8]

[7]

[1]

[7]

VIBR_PMU

VSIM2_PMU

VGP1_TP_2.8

VSIM1_PMU

VUSB_PMU

6mil

8mil

6mil

8mil

N8

L14

P9

M7

VGP2

VGP3

VIBR

VSIM1N9VSIM2

VBAT_VSYS

AVDD22_BUCK

VBAT_LDOS3A5DVDD18_IOA8DVDD18_DIG

VBAT_LDOS3

AVDD22_BUCK

VBAT

P6

P8

H13

J14

M14

20mil

20mil

20mil

20mil

RTC

RTC 32K : X301+C324+C319=> mount, R333=> NC

[8]

VCAM_AF_PMU

8mil

N7

VCAM_AF

C323

有问题

100nF

C323 must to be close to PMIC

32K-less: X301+C324=> remove, C319+R333=> 0R

dedicate VSS ball, must return to cap then to main GND:

1. GND_VREF(N14) => C320

[2]

CLK32K_BB

C320

100nF

VREF

P14

VREF

AUXADC

AUXADC_VREF18B1AUXADC_AUXIN_GPSB2AVSS28_AUXADC

C2

R350 0

GND_AUXADC

AUXADC_REF

AUXADC_TSX

[5]

[5]

[3,5]

DCXO_32K

B10

A3

A4

D5

C4

N14

XIN

XOUT

GND_VREF

RTC_32K1V8

RTC_32K2V8

RTC

SIM LVS

BC 1.1

CHG_DP

CHG_DM

SIM1_AP_SCLK

SIMLS1_AP_SIOE6SIM1_AP_SRSTC5SIM2_AP_SCLK

B5

A11

A10

M11

CHD_DM

CHD_DP

SIM1_SIO

SIM1_SCLK

[2]

[2]

[2] SIM2_SCLK

[2]

[2]

C322 100nF

Connect TSX/XTAL GND

to AUXADC_GND first

than connect to main GND

C322 must to be close

to PMIC AUXADC_AUXIN_GPS pin

1uF

C308

1uF

C307

10uF

C309

10uF

C306

1uF

C304

C303

10uF

C301

Refer to GPS co-clock layout rule

10uF

G11

GND_VSYS

GND_ISINK

SIMLS2_AP_SIOD6SIM2_AP_SRSTM9SIMLS1_SCLK

K11

SIM2_SIO

[2]

E13

E11

GND_VPA

F11

GND_VPROC

GND_VPROC

SCLK

[7]

F10

GND_VPROC

SIMLS1_SIO

M10

N11

SIO

SRST

[7]

[7]

SIMLS1_SRST

K6

GND_LDOK8GND_LDO

L11

SCLK2

[7]

F5

GND_LDOG5GND_LDO

SIMLS2_SRST

SIMLS2_SIOK9SIMLS2_SCLK

K10

SIO2

SRST2

[7]

[7]

DCXO_32K

[5]

Close to chip

F6

F7

G6

GND_LDO

GND_LDOF8GND_LDOF9GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

C318

100nF

R312

1K

10uF

VRTC

C325

[3]

please refer to RTC design notice

==> for longer RTC time sustain after battery remove,

G7

G8

G9

H5

H6

H7

H8

H9

H10

J6

J7

J8

J9

J10

MT6323

[3,5]

AUXADC_REF

BATTERY

CONNECTOR

靠近PMU

R334 16.9K 1%

[3]

BAT_ON

R3171K

R334,R335 must to be close to

PMIC AUXADC_REF pin

R335 27K 1%

[3,5,8]

VBAT

if battery NTC is 10kohm, R334=39K, R335=90K

if battery NTC is 47kohm, R334=190K, R335=390K

Refer to MT6323 HW design notice

10uF

C382

C377

33pF

T300

40mils

T301

TPLED4

2ID3

TPLED6

GND

J1

WKBAH009-A31

1

VBAT

VIO18_PMU

VSYS_PMU

[3]

[1,2,3,4,5,8]

10uF

C310

D302

5V1 SOD123

80mil

VBAT

[3,5,8]

TPLED7

Refer to MT6323 design notice

for Buck GND layout rule

39K

R324

VBUS

[7]

Pulse Charger

VCDT

CHR_LDO

[3]

[3]

3.3K

R331

330K

R329

40mils

C329

1uF

瑻溃+16V

CHRIN max. 8.0V when U290 NC

[3]

VDRV

Q301

NTA4153NT1G

R301

1

10K

32

BC

E

34

C

52

16

C

C

U303

STT818B

40mils

R328

and others are 40mils

connector, and SNS trace should be 4mil~6mil,

Place this resister close to battery

VBAT

[3,5,8]

0.2R

ISENSE

[3]

Page 4

[4]

[4]

NAND_D15_EMMC_VCCQ

NAND_VCC_EMMC_VCC

Micron

Sandisk KSI Toshiba

Hynix

Sumsung

Recommand

Cap Value

1+0.1uF

0.1uF

1uF

0.1uF

1+0.1uF

0.1uF

VDDi

4.7+0.22uF

2.2+0.1uF

1+0.1uF

2.2+0.1uF

4.7+0.22uF

4.7+0.2uF

VCC

2+0.2uF

2+0.2uF

2+0.2uF

2+0.2uF

2+0.1uF

2+0.2uF

VCCQ

V1.0

RevDocument NumberSize

49ofSheetDate:

MT6572 REF PHONE

Wednesday, January 02, 2013

Memory

1234

A1

Title

C453

[1,4]

VIO_EMI

100nF

R453

8.2K

R452

8.2K

[1,2,3,4,5,8]VIO18_PMU

eMMC MCP/DDR2

C421

C422

4.7uF

100nF

F1

E6

U401

VDD1M7VDD2G5VDDQ

VDD1

CA1

CA0

T3

U3

EA1

EA0

[4]

[4]

close to MCP

VIO_EMI

[1,4]

V1

G2

W6

E5

K1

VDD1

VDD2

VDD1W5VDD2

VDD2

VDD2

CA6J3CA7

CA5

CA4R2CA3R3CA2

J2

K2

R1

EA5

EA7

EA2

EA4

EA3

[4]

[4]

[4]

[4]

[4] EA6

[4]

C401

4.7uF

U2

VDD2

CA9H3CA8

DQ0

H2

T8

EA9

[4] ED0

[4]

[4] EA8

1uF

C402

C403

C411

C412

4.7uF

100nF

100nF

close to MCP

Put C402 & C403 between BB & memory.

F10

VDDQ

VDDQ

VDDQL6VDDQ

VDDQ

A8

VDDQ

VCCB2VCC

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDCAT2VDDCA

VDDCA

L1

M6

N6

U5

H9

R10

F7

V7

J10

V10

J1

T9

Power

DQ15

DQ11J7DQ13J8DQ14J9DQ12

DQ8K8DQ9K7DQ10

DQ5P8DQ6P9DQ7

DQ4R7DQ2R8DQ1R9DQ3

P7

R6

ED3

ED2

ED1

ED5

ED6

ED7

[4]ED4

[4]

[4]

[4]

[4]

[4]

[4]

DQ19T6DQ23

DQ17U7DQ20

DQ16W8DQ18W9DQ21

H8

J6

K9

T5

U6

W7

ED9

ED8

ED18

ED17

ED16

ED12

ED14

ED13

ED11

ED10

[4]

[4]

[4]

[4]

[4]

[4]ED15

[4]

[4]

[4]

[4]

[4]

[4] ED19

[4]

NAND_VCC_EMMC_VDDI

NAND_VCC_EMMC_VDDI

B5

B8

VCCQA5VDDI

DQ22

V8

ED20

ED23

ED22

ED21

[4]

[4]

[4]

[4]

[4]

[4]NREB

NLD10

C1

RSTC5CMD

CLKM

DQ25

F8

ED25

ED24

[4]

[4]

1uF

C410

[4]

[4]

[4]

NRNB

NCLE

NLD4

NALE

B4

DAT7A4DAT6A6DAT5B6DAT4A7DAT3B7DAT2B3DAT1A3DAT0

eMMC

DQ28H6DQ24

H5

ED26

ED29

ED28

ED30

ED27

[4]

[4]

[4]

[4]

[4]

[4]

[4]

NLD5

DQ31E8DQ29E9DQ26F3ZQ1F6VSSQ

E7

ED31

[4]

Must Check the eMMC data sheet

for VDDI capacitor value

[4]

NAND_WPB_EMMC_DAT0

[4]

[4]

[4]

NLD7

NLD14

NLD11

240

240

R464

R465

[4]

[4]

ECS0_B

ECS1_B

P1

CS0#P2CS1#N1CKE0N2CKE1

VSSQG3ZQ0G6DQ30G7DQ27

F9

G10

[4]

[4]

[4]

[4]

[4]

EDCLK

EDCLK_B

EDQS0

ECKE

EDQS0_B

M3

L3

P5

K6

CLK

CLK#P6DQS0

DQS0#

VSSQ

VSSQ

VSSQ

VSSQM5VSSQ

VSSQ

VSSQ

VSSQ

VSSQV6VSSQ

J5

R5

H10

K10

P10

T10

U10

[4]

[4]

[4]

[4]

[4]

[4]

[4]EDQM0

[4]

EDQS1

EDQS2

EDQM1

EDQS2_B

EDQS1_B

EDQS3_B

EDQS3

K5

U8

U9

G8

G9

N5

DM0L5DM1T7DM2H7DM3

DQS1

DQS2

DQS3

DQS1#

DQS2#

DQS3#

VSSCAM1VSSCAH1VSSCAB9VSSME1VSSMF2VSSF5VSSG1VSSL2VSSM8VSSU1VSSV2VSSV5VSS

VSSQ

T1

V9

[4]

[4]

EDQM3

EDQM2

LP-DDR2

[4]

EVREF

K3

VREFCAM9VREFDQ

[4]

[4]

[4]

[4]NLD0

[4]

NLD1

NWRB

NLD6

NLD8

R18

R3

R44

R42

R43

NC(0) 0201

NC(0) 0201

NC(0) 0201

NC(0) 0201

NC(0) 0201

C2NCC4NCC6NCD1NCD2NCD3NCD4

VSSQMA1DNUA2DNUA9DNU

C3

NAND_D3_EMMC_VSS

[4]

[4] EVREF

[4]

[4]

[4]

[4]

[4]

NLD12

NCEB

NLD13

NLD9

NLD2

R48

R4NC(0) 0201

R46

R47

R45

NC(0) 0201

NC(0) 0201

NC(0) 0201

NC(0) 0201

NCD5NCD6NCE2NCE3NCM2NCN3NCP3NCV3NCW2NCW3NC

DNUB1DNU

DNU

DNUW1DNU

A10

B10

E10

DNUY1DNUY2DNUY9DNU

W10

DNU

Y10

eMMC

R62=0

R65=0

R50=0

R67=0

R402=NC

NAND

HW trapping PIN

20K: VM=1.8V DDR1

NC : VM=1.2V DDR2

4 3 2 1

[2,3]

PMIC_SPI_CS

[1,4]

VIO_EMI

0

R401

VM_PMU

[3]

[4]

[4]

[4]

ECKE

ECS1_B

ECS0_B

AD12

AB18

AC18

AB19

AD18

AF25

AF19

ECKE

EWR_B

ERAS_B

ECAS_B

ECS1_B

ECS0_B

Ctrl

DRAM

Data

DRAM

ED23

ED26

ED25

ED24

ED31

ED27

ED29

ED28

ED30

U100-F

AF5

AE5

AB6

AF2

AF3

AE4

AD5

AC5

AB16

AE13

ED30

ED23

ED24

ED25

ED26

ED27

ED28

ED29

[4]

[4]

[4]

[4]

[4]

[4]

[4]ED31

[4]

[4]

[4]

[4]

EDQM0

EDQM1

AE12

EDQM0

EDQM1

ED21

ED22

AE14

ED21

ED22

[4]

[4]

[4]

[4]

EDQM2

EDQM3

AB13

Y13

AD8

EDQM2

EDQM3Y8EDQS3

ED19

ED20

ED18

AF16

AC15

AE15

AE16

ED18

ED20

[4]ED19

[4]

[4]

[4]EDQS0

[4]

EDQS1

AA9

EDQS0

EDQS1

ED16

ED17

AF15

ED16

ED17

[4]

[4]

162 Ball, 0.5mm pitch

VDD1=1.8V

VDD2=1.20V

for DDR1 : AA19+Y19 must NC

for DDR2 : AA18+Y18 must NC

[4]

[4]

[4]

[4]EDQS1_B

[4]

[4]

[4]

[4]

EDCLK

EDQS3_B

EDQS0_B

EDQS2_B

EDCLK_B

EDQS3

EDQS2

AA19

AA14

EDQS2

ED15

AC7

ED15

[4]

Y19

Y14

AA13

Y18

AA18

Y9

AA8

EDCLK1

EDCLK0

EDQS2_B

EDQS0_B

EDQS1_B

EDQS3_B

EDCLK1_B

EDCLK0_B

ED3

ED7

ED6

ED5

ED4

ED8

ED13

ED10

ED11

ED14

ED12

ED9

AE9

AF9

AE6

AC9

AF8

AB9

AE7

AF6

AE8

AF11

AE11

AC13

ED9

ED10

ED12

ED13

ED8

ED11

ED14

ED7

ED3

ED4

ED5

ED6

[4]

[4]

[4]

[4]

[4]

[4]

[4]

[4]

[4]

[4]

[4]

[4]

VDDCA=1.20V

VDDQ= 1.20V

[4]

[4]

[4]

[4]

[4]

NLD6

NLD3

NLD2

NLD1

NLD0

Y4

AA2

ND0

ND1V5ND2W1ND3Y3ND6Y2ND8W2ND9

VREF0

ED1

ED0

ED2

VREF1

AC11

AE10

AD15

AF12

AB17

ED2

ED0

ED1

[4]

[4]

[4]

EVREF

[4]

[4]

NLD8

[4]

NLD9

DRAM

EA18

AE19

[4]

[4]

[4]

NLD15

NLD13

NLD12

W4

ND12W3ND13V1ND15W5NCEBY5NWRB

Address

EA15

EA17

EA16

AC23

AE18

AE17

[4]

[4]

EA10

AE26

AE24

EA9

(LPDDR1)

EMMC_DAT0

[4]

[4]

NRNB

NREB

[4]

[4]

[4]

[4]NLD10

[4]

[4]

[4]NALE

[4]

NLD7

NLD4

NLD5

NCLE

NLD11

NLD14

AB3

AD3

AE3

AE2

AB2

AC1

AE1

AD2

AC3

AB1

AC2

ND7

ND5

ND4

ND11

NALE

NRNB

NREB

ND14

NCLE

ND10

GPIO46

ERESET

EA0

EA2

EA1

EA3

EA4

EA6

EA5

EA9

EA7

EA8

AE22

AD22

AB20

AD21

AE25

EA6

EA4

EA7

EA8

EA5

[4]

[4]

[4]

[4]

[4]

[4]

AE20

AE23

AF18

AF21

EA1

EA3

EA2

[4]

[4]

[4]

AF24

EA0

[4]

MT6572/TFBGA428/P0.4/B0.25/10.6X10.6

Please make sure the ball map is

match to the MCP type you selected

[4]

[4]

NWRB

NCEB

NAND I/F

EA12

EA11

EA13

EA14

AD24

AC22

AE21

AF22

BA[1:0] =

EA[15:14]

NAND_D3_EMMC_VSS

R53

NAND

NLD3

[4]

0

R50

NC(0) 0201

eMMC

[4]

NAND_D15_EMMC_VCCQ

R63

NAND

[4] NLD15

0

R62

eMMC

NC(0) 0201

VIO18_PMU

[1,2,3,4,5,8]

[4]

NAND_VCC_EMMC_VDDI

NC

R64

C414

2.2uF(0402)

R66

NAND

NAND

[4]NAND_WPB_EMMC_DAT0

R65

0

NC(0) 0201

eMMC

WATCHDOG

EMMC_DAT0

[2,3]

[4]

R402=47k

[4]

NAND_VCC_EMMC_VCC

NC

R68

NAND

[1,2,3,4,5,8] VIO18_PMU

eMMC

0

R67

220nF

VEMC_3V3_PMU

[3]

If use Nand MCP, R402: 47K ohm.

[1,2,3,4,5,8]

VIO18_PMU

NC

C431

C430

4.7uF

If use eMMC MCP, R402: NC.

[4]

NRNB

R402

R68=0

R66=0

R53=0

R63=0

R64=0

Page 5

ANT2

ANT8

ANT1

RF-CON-KEYPAD

[5]

[5]

TRXB5

L11

nc

C9

2NH

L10

8.2nH

6

2

ANT

4

5

7

9

RX

TX

RX

B39881B7923P810

1

3

8

L13

33nH

1.5nH

L9

L14

共用

WCDMA_Band5_Rx

[5]PDET

50Ω阻抗

26R

R26

35R

26R

R22

50Ω阻抗

8

CPOUT

77758PART

GND

15

NC

C14

W_PA_H_EN

[2]

[5]

[5]

[5]

2G_LB

TRXB1

2G_HB

19

GND

TRX_4

TRX_120TRX_221TRX_3

GND

GND

GND

GND

GND

GND

U6

SKY77590

GND

GND

GND

GND

GND

GND

TX_HB_IN10TX_LB_IN

9

[5]

RFOUT_LB

18pF

L7

U2

B39881B7923P810

RX

1

1.5nH

C4

3.9pF

L12

nc

WCDMA_Band8_Rx

R19

SKY77590 control logic table

Enable VctC VctB VctA

SKY77590 control logic table

Enable VctC VctB VctA

29

28

27

25

15

8

7

6

5

4

3

2

1

C47

NC

RLC0201

R10

0R

R9

C46

NC

RLC0201

GGE_PA_LB_IN

GGE_PA_HB_IN

[5]

[5]

[5]

TRXB2

6

ANT

RX

8

W_PA_OUT_B2

C7

2NH

3GL5_TX TX_LOW_BAND1

3GH2_TX TX_HIGH_BAND3

C5

3.9pF

3GH1_TX TX_HIGH_BAND2

3GB5_RX LNA_2

3GB8_RX LNA_4

3GB1_RX LNA_3

3GB2_RX LNA_1

L8

NC

2

4

5

7

9

TX

3

L6

4.3nH

nc

L4

WCDMA_Band2_Rx

[5]

W_PA_OUT_B2

WCDMA_TX_BAND2

C20

NM

0

C21

C129

LB_GMSK_TX H L L H

HB_GMSK_TX H L H H

LB_EDGE_TX H H L H

HB_EDGE_TX H H H H

LB_GMSK_TX H L L H

HB_GMSK_TX H L H H

LB_EDGE_TX H H L H

HB_EDGE_TX H H H H

C54

NC

RLC0201

0R

C49

NC

RLC0201

[2]

[1,3,7,8]

[2]

W_HB_V1

VIO28_PMU

W_HB_V2

C182

100pF

C181

SKY13472-460LF

GND

VDD

7

GND

8

J2

9

GND11RFC12GND

10

100pF

C18

1uF

4V15V26

U504

N/C

3

GND

2

J1

1

R16

13

R6

RLC0201

50Ω阻抗

NC

R54

NC

R5

50Ω阻抗

RFOUT_HB

[5]

TRX1 L H L L

TRX2 L H H L

TRX3 L H L H

TRX4 L H H H

TRX5 L L H L

TRX6 L L L H

TRX1 L H L L

TRX2 L H H L

TRX3 L H L H

TRX4 L H H H

TRX5 L L H L

TRX6 L L L H

[5]

W_PA_OUT_B1

WCDMA_TX_BAND1

C16

NM

C17

3.3nH

C91

RLC0201

50Ω阻抗

NC

NC

[5]

LB_RX_P

L0400

L0404

12nH

L0021

2.2nH

C0411

22pF

2G_LB

[5]

2G_Rx

2G_Rx

[5]

GGE_PA_LB_IN

[5]

[5]

[5]GGE_PA_HB_IN

[5]

LB_RX_N

39nH

L0406

L040512nH

1.5nH

8

GND

LBOUT9LBOUT

12

GND

10

GND1LBIN

GND4HBIN

SF602

2

3

[5]

HB_RX_P

6

L0022

2.2nH

C041022pF

W_PA_H_IN

L0401

GND

HBOUT7HBOUT

GND

2G_HB

[5]

W_PA_L_IN

BD2012-20L0820T

11

5

VRF18_PMU

[3,5]

L628

[5]

HB_RX_N

5.1nH

L04071.5nH

470nF

C563

PDET

C9

J8

C8

J7

[5]

C7

C10

B10

D11

B11

A11

A10

A9

A8

2nH

B8

B6

A6

B5

A5

B4

B3

3GB1_RXN

A3

A2

3GB1_RXP

C2

J2

C3

D3

E3

U509

WCDMA_PA_TX

VTCXO_PMU

[1,3,5]

DETGND(MT6166 Pin D10) connect to L2 solid ground plane, it can't connect to other RF GND in L1.

E10

D10

C11

D9

GND

GND

GND

GND

GND

GND

GND

DET

GND

GND

GND

GND

GND

V28

GNDE9GNDF9GNDG9GNDJ9GNDH9GND

TMEAS

DETGND

VTXHF

2GLB_TX

3GL5_TX

3GH2_TX

3GH1_TX

TXOFDD RX

2GHB_TX

3GB8_RXN

3GB8_RXP

3GB2_RXN

3GB2_RXP

3GB5_RXN

3GB5_RXP

3GB1_RXN

3GB1_RXP

LB_RXPD1LB_RXN

GNDH3GNDJ3GNDD4GND

B40_RXPB1B40_RXN

GND

GND

C1

G3

A1

F3

C4

[5] LB_RX_P

2.XTAL Circuit :X501=Mobile XTAL, R527=R529=0ohm, R526=R525=R658=NC

1.TSX Circuit : X501=TSX, R527=R529=NC, R526=100K+-1%, R525=R528=0ohm

Two Application Circuit Conditions,

Two Application Circuit Conditions,

BPI0~4 and 10~11 are 2G+3G mode both

BPI5~9 and 12~14 are 3G mode only

(suggest BPI5~9 = 1.8V)

[3,5]

VRF18_PMU

C565

470nF

C564

470nF

TX_Q_N

TX_Q_P

TX_I_N

TX_I_P

[2]

G10

3GTX_IP

TXBPI

[2]

[2]

[2]

[2]

VRF18_PMU

J11

H10

G11

F10

F11

L11

VTXLF

TXBPI

3GTX_IN

3GTX_QP

3GTX_QN

TXVCO_MON

TX(I/Q)

MT6166

MT6166/VFBGA104/P0.4/B0.25/4.6X4.6

TDD RX

LB_RX_N

[5]

connect to main GND

connect to main GND

XO

VRXHF

HB_RXPF1HB_RXN

XTAL2J1XTAL1

RFVCO_MON

F2

E1

H2

G2

VRF18_PMU

C59

470nF

[3,5]

HB_RX_P

HB_RX_N

[5]

[5]

XTAL1

XTAL2

VRF18_PMU

X600

MT6166 QVL 26M

GND

4

远离射频PA10mm

R527

NC(0) 0201

R526

100k 1%

R525

0 0201

1uF

C570

[3]

[3]

AUXADC_REF

AUXADC_TSX

Route AUXADC_TSX with 4mil trace width

Route AUXADC_TSX with 4mil trace width

Route AUXADC_REF with 4mil trace width

Route AUXADC_REF with 4mil trace width

Route AUXADC_GND with 24mil trace width

Route AUXADC_GND with 24mil trace width

Route AUXADC_REF/AUXADC_TSX as differential trace with well GND shielding

and route AUXADC_GND with 24mil trace width under

AUXADC_TSX/AUXADC_REF trace to provide return current path.

Route AUXADC_REF/AUXADC_TSX as differential trace with well GND shielding

and route AUXADC_GND with 24mil trace width under

AUXADC_TSX/AUXADC_REF trace to provide return current path.

R538

2k

BSI-A_DAT2

BSI-A_DAT1

[2]

[2]

G8

L10

K11

J10

B7

D8

GND

GND

GND

GNDE8GNDJ6GND

TST1

TST2

RCAL

Test pin

VTCXO28K2CLK_SEL

32K_EN

K1

G1

VTCXO_PMU

2

GND3HOT

BSI

EN_BB

L1

SRCLKENA

BSI_DATA2H8BSI_DATA1

26M output

XO3

L2

SRCLKENA

C568

470nF

GNDF4GNDG4GND

E4

RX(I/Q)

GND

GND

GND

GND

BSI_DATA0

BSI_CLK

BSI_EN

RX_QN

RX_QP

RX_IN

RX_IP

VRXLF

VXODIG

AVDD_VIO18

XMODE

OUT32K

XO1

XO2

XO4

GND

GND

GND

GND

GND

GND

GND

H4

DCXO_32K_EN

[1,3,5]

HOT

1

under AUXADC_REF/AUXADC_TSX trace

under AUXADC_REF/AUXADC_TSX trace

SRCLKENA

SRCLKENA

VTCXO_PMU

VTCXO_PMU

[2,3,5]

[2,3,5]

[1,3,5]

R529

NC(0) 0201

R528

0 0201

connect to main GND

connect to main GND

[3]

GND_AUXADC

Close to each other and nearby X501

Connect TSX/XTAL GND

to GND_AUXADC first

than connect to main GND

Connect TSX/XTAL GND

to GND_AUXADC first

than connect to main GND

[2]

F6

BSI-A_DAT0

E6

D6

C6

J5

E7

F8

H6

G6

K9

K10

K8

L8

L7

K7

K6

L5

K5

L4

K3

K4

D7

F5

E5

D5

C5

J4

CLK1_BB

SYSCLK_WCN

CLK4_AUDIO

[2]

[3]

[6]

VTCXO_PMU

[1,3,5]

DCXO_32K_EN

VTCXO_PMU

[1,3,5]

VXODIG

VXODIG

XMODE

XMODE

DCXO_

32K_EN

DCXO_

32K_EN

Logic

Logic

MODE

MODE

[2]

[2]

BSI-A_EN

BSI-A_CK

[2]

[2]

[2]

[2]

L5330

VIO18_PMU

[1,2,3,4,5,8]

DCXO_32K

XMODE

[3]

VTCXO_PMU

[1,3,5]

VTCXO_PMU

[1,3,5]

XMODE

VTCXO_PMU

VIO18_PMU

[1,3,5]

[1,2,3,4,5,8]

1(VIO18)

1(VIO18)

1(VTXCO28)

1(VTXCO28)

1(VIO18)

1(VIO18)

1(VTXCO28)

1(VTXCO28)

0(GND)

0(GND)

1(VTXCO28)

1(VTXCO28)

DCXO + 32K XO

DCXO + 32K-Less

DCXO + 32K XO

DCXO + 32K-Less

[3,5]

VRF18_PMU

RX_Q_N

RX_Q_P

C589

RX_I_N

RX_I_P

470nF

100nF

C567

VXODIG

[1,3,5]

VTCXO_PMU

Reserved LC filter

VTCXO_PMU

VXODIG

[1,3,5]

VTCXO_PMU

VIO18_PMU

[1,3,5]

[1,2,3,4,5,8]

[5]

W_PA_OUT_B1

NC

C556

L514

2nH

2

4

5

7

9

TX

3

L3

4.3nH

nc

U3

C2

4.3pF

L1

U505

RX

SAYRF1G95HQ0F0A

1

C1

4.3pF

[17]

[5]

TRXB1

15NH

L515

6

ANT

RX

8

WCDMA_Band1_Rx

[5]

[5]

RFOUT_LB

RFOUT_HB

C33

NM

10nh

0

W_PA_L_IN

[5]

R14

2nh

C28

C10

56pF

1K 0201

ASM_VCTRL_B

[2]

C34

C29

0.5pf

50Ω阻抗

14

OUTLB

U5

VENLB2RFLB3VBAT4RFHB5NC6MODE7VENHB

1

0R

R23

NC

C35

18pF

W_PA_H_IN

[5]

77584(使用pin19,20,21,23)

C3

22PF

RLC0201

C38

22PF

RLC0201

R15

1K 0201

ASM_VCTRL_A

[2]

C30

2.2pf

C26

12nh

VBAT

[3,5,8]

51

R25

50Ω阻抗

400ma

9

10

11

12

GND

VCC13GND

CPIN

OUTHB

NC

R24

50Ω阻抗

VBAT

[3,5,8]

NC

C13

VM1

VM0

[2]

[2]

[5]

[5]

TRXB5

TRXB2

改动PA 逻辑,使用21,23做高低频兼容。

22

23

TRX_524TRX_6

ANT

26

MODE

16

TXEN

17

VRAMP

18

BS1

12

BS2

11

VBATT14VCC

13

C86

22uF

C84

100nF

C85

47pF

VBAT

[3,5,8]

WCDMA_TX_BAND5

WCDMA_TX_BAND8

C50

C31

2.2uF

C27

100nF

C179

1

1

C8

nc

1

L2 0

C6

nc

J2

MM8430-2600RAI

1

35

4

6

12

2

1

SIG

J8

GND

2

nc

C652

L25

2nh

NC

C653

47pF

VBAT

[3,5,8]

50Ω阻抗

C51

W_PA_L_EN

[2]

RF-PAD

R12

R716

22pf 0201

C81

24k 0201

R715

1K 0201

R713

[2] ASM_VCTRL_C

22pf 0201

1K 0201

WG_GGE_PA_ENABLE

[2]

C24

220pf 0201

C25

R11

10K 0201

WG_GGE_PA_VRAMP

[2]

Page 6

[3,6]

[3,6]

VCN_1V8_PMU

VCN_1V8_PMU

[6]

[6]

[6]

[6]

[6]

[6]

[6]

[6]

[6]

[6]

[6]

[6]

[6]

WB_CTRL0

WB_CTRL3

WB_CTRL5

WB_CTRL1

WB_CTRL2

WB_CTRL4

B22

C16

C17

C18

C19

C20

C21

A14

D18

C15

D16

D17

GND_WBG

GND_WBG

GND_WBG

GND_WBG

GND_WBG

GND_WBG

GND_WBG

GND_WBG

GND_WBG

GND_WBG

GND_WBG

U100-C

GPS_RXIN

GPS_RXIP

GPS_RXQN

GPS_RXQP

WB_TXIN

A16

GPS_RX_IP

[6]

B14

B15

GPS_RX_QP

GPS_RX_QN

[6]

[6]

A19

WB_TXIN

[6]

WB_TXIP

B19

WB_TXIP

[6]

B18

WB_TXQN

[6]

B16

GPS_RX_IN

[6]

D19

GND_WBG

WB_TXQN

A18

WB_TXQP

[6]

D20

GND_WBG

GND_WBG

WB_TXQP

WB_RXIN

A21

WB_RXIN

[6]

WB_RXIP

A22

WB_RXIP

[6]

E20

D22

F20

E22

CONN_WB_CTRL0

CONN_WB_CTRL2

CONN_WB_CTRL1

CONN_WB_CTRL3

WB_RXQP

WB_RXQN

B21

B20

WB_RXQN

WB_RXQP

[6]

[6]

C22

C23

CONN_WB_CTRL4

CONN_WB_CTRL5

Close to MT6572

CONN_SEN

CONN_SDATA

CONN_RSTB

C14

E15

E14

CONN_SEN

CONN_RSTB

CONN_SDATA

AVDD18_WBG

F18

VCN_1V8_PMU

[3,6]

FM_DATA

CONN_SCLK

E13

G12

CONN_SCLK

[3,6]

VCN_1V8_PMU

CONN_XO_IN

FM_CLK

F12

F14

CONN_XO_IN

CONN_F2W_DAT

CONN_F2W_CLK

MT6572/TFBGA428/P0.4/B0.25/10.6X10.6

C37

100nF

[6]

WB_CTRL3

VCN_1V8_PMU

[6]

WB_CTRL2

[3,6]

[6]

WB_CTRL1

VCN_1V8_PMU

[3,6]

[6]

WB_CTRL0

1uF

Star Conn

for WB/GPS/WBG 1V8

C44

C42

100pF

C41

100nF

[6]

[6]

WB_RXIN

WB_RXIP

4.7nF

C43

[6]

[6]

WB_RXQP

WB_RXQN

20

19

WB_RX_QP

WB_RX_QN

WB_RX_IN

21

WB_RX_IP

22

WB_CTRL0

23

WB_CTRL1

24

WB_CTRL2

25

WB_CTRL3

26

WB_CTRL4

27

WB_CTRL5

28

AVDD18_WBT

29

W_LNA_EXT

30

[6]

WB_TXIP

18

WB_TX_IP

[6]

WB_TXIN

17

WB_TX_IN

[6]

WB_TXQP

16

WB_TX_QP

[3]

VCN_2V8_PMU

bead 75

R30

10nF

refer to FM desense performance

enhance proposal

C45

Close to MT6627

AVDD28_FM

[6]

[6]

[6]

[6]

[6]

[6]

GPS_RX_IN

13

GPS_RX_IN

GPS_RX_QP

12

GPS_RX_QP

GPS_RX_QN

11

GPS_RX_QN

GPS_RX_IP

WB_TXQN

14

15

WB_TX_QN

GPS_RX_IP

MT6627-NS/MQFN40/SMD/P0.4/5X5

MT6627 SMD QFN40

XO_IN

10

CEXT

9

SEN

8

SDATA

7

SCLK

6

F2W_CLK

5

F2W_DATA

4

FM_DBG

3

HRST_B

2

AVDD28_FSOURCE

1

[6]

CONN_XO_IN

[3,6]

VCN_3V3_PMU

C15

VCN_3V3_PMU

[3,6]

C40

100pF

C39

1uF

100pF

C48

4.7uF

[5]

SYSCLK_WCN

0

R27

CONN_XO_IN

[6]

AVDD33_WBT

GPS_DPX_RFOUT

WB_GPS_RF_IN

33

32

WB_CTRL4

WB_CTRL5

[6]

[6]

[3,6] VCN_1V8_PMU

Reserved 4.8GHz notch filter for WiFi FCC test tuning

1.2PF

C55

NC

50 Ohm

50 Ohm

C52

0

L29

NC

C53

WIFI/BT/GPS Single ANT Ref.

1

ANT4

TPLED10

31

U601

50 Ohm

50 Ohm

WBG_ANT

VCN_3V3_PMU

[3,6]

L50

1NH

Based on your system level design , if

better WiFi TX performance is needed on

your system, please refer to WiFi

performance enhance proposal

AVDD18_GPS

NC

NC

34

35

50 Ohm

AVDD28_FM37FM_LANT_N

36

AVDD28_FM

[6]

FM_RX_N_6572

FM_RX_N_6572

[7]

FM_LANT_P

38

FM_LANT_P

L2782nH

FM_ANT

[7]

GPS_RFIN

39

DVSS

40

41

[3,6]

VCN_1V8_PMU

CONN_RSTB

[6]

FM_DATA

[6]

[6] FM_CLK

CONN_SCLK

[6]

CONN_SDATA

[6]

CONN_SEN

[6]

FM

1

ANT3

Page 7

苹果接口

T12

T10

T5

33pF

33pF

33pF

C73

C72

C71

G

2M4L5

1

BLM15BB750SN1

BLM15BB750SN1

L43

L44

HP_MIC

[7]

HP_MP3L

[7]

D

R6G

3

U4

AUDIOJACK_PH10_2B05F35A

BLM15BB750SN1

L42

HP_MP3R

[7]

[1,3,5,8]

[2]

[3]

VIO28_PMU

EINT0_HP

47K

470K

R39

R40

ESD7001

L41 100nH

0

R37

FM_RX_N_6572

FM_ANT

[6]

[6]

close to

connector

BLM15BB750SN1

close to IC

L45

AU_SPKP

[3]

SP1

T26

T25

C88

33pF

C36

33pF

C57

100pF

SPKP

SPKN

BLM15BB750SN1

L46

AU_SPKN

[3]

SIM CARD 1

17

GND

GND

15

Speaker

[3]

[3]

SRST

SCLK

VSIM1_PMU

8

P1-B-VCC9P2-B-RST10P3-B-CLK11P5-B-GND12P6-B-VPP

RIGHT-BLIFT-A

P1-A-VCC2P2-A-RST3P3-A-CLK4P5-A-GND5P6-A-VPP6P7-A-I/O

1

SCLK2

VSIM2_PMU

[3]

[3] SRST2

[3]

[3]

SIO

1uF

C23

9

GND410GND3

J7

DAT17DAT06GND5CLK4VDD3CMD2CD/DAT31DAT2

8

13

14

18

GND

P7-B-I/O

G1-B-SWTICH

J15

DUAL_SIM_T887

C612.2uF

GND7G1-A-SWTICH

16

T35

T19

T16

T15

1uF

C22

SIO2

[3]

VMCH_PMU

[3]

MC1DAT2

[2]

MC1DAT3

[2]

MC1CMD

[2]

T_FLASH_T08-BB08F320

MC1CK

MC1DAT1

MC1DAT0

[2]

[2]

[2]

Earphone Audio

[7]HP_MIC

C66

4.7uF

1.5K

R330

R364

1K

C373

100pF

[3] MICBIAS1

100nF

C67

C68 100nF

AU_VIN1_P

AU_VIN1_N

[3]

Earphone MICPHONE

[3]

T-FLASH

SIM CARD2

SIM0 & SIM1

[7]

[7]

HP_MP3R

[3]

ACCDET

1K

R35

C372

33pF

C371

33pF

HP_MP3L

R34

470

R33

470

100

100

R32

R36

C6910uF

C7010uF

BLM15BB750SN1

L329

L328

BLM15BB750SN1

AU_HPL

Earphone RECEIVER

AU_HPR

[3]

[3]

MIC2

1

2

MIC-FPC

T28

T27

33pF

C75

100pF

C74

C58

33pF

USB interface

10

11

T30

C62

33pF

Receiver

L38BLM15BB750SN1

AU_HSP

[3]

L40

L39

1

2

RCV200

BLM15BB750SN1

BLM15BB750SN1

T29

C63

100pF

C60

33pF

L302BLM15BB750SN1

AU_HSN

[3]

MICBIAS0

[3]

Handset Microphone 1

1k

R86

Close to BB Close to MIC

R891.5k

4.7uF

C64100nF

[3]

AU_VIN0_P

R881k

R901.5k

C65

C110

100nF

[3]

AU_VIN0_N

TPLED8

C78NC

C11

10uF

KCOL0

[2,8]

TPLED9

TPLED11

TPLED12

T23

T22

T21

VBUS

USB_DP

USB_DM

[3]

[2]

[2]

USB2

UAF08-05396-1500

VUSB(5V)2D-/TXD3D+/RXD4PWRKEY5DATA_GND6SHIELDING_GND7SHIELDING_GND8SHIELDING_GND9SHIELDING_GND

1

Page 8

[3,5,8]

VBAT

21

D6

21

LED BACKLIGHT

[2,7,8]

KCOL0

[2,8]

[2,8]

KROW1

KROW0

D5

NC

C19

MOT400

MOTOR

VIBR_PMU

[3]

J17

GND

RESET(BACK)

1

2

3

+

1uF

C32

D4

PWD(FRONT)10D511D612MCLK9PLCK13D717PWD(BACK)14IOVDD16HREF15DVDD21AVDD20SCL22SDA

D2

5D17D06D38

4

KPLED

[8]

[8]

KPLED

2SC4617

Q2

R69

100

R71

100k

R70

2.2k

GPIO134

[2]

[2,8]

[2,8]

[3,8]

KROW1

PWRKEY

KROW0

T4

T1

T2

T7

后

KCOL0

Volume Down

KROW1

[2,8]

[2,7,8]

KCOL0

download

Volume Up

[2,7,8]

KROW0

[2,8]

[3,8]

[2,8]

[2,8]

[2,7,8]

KROW1

KROW0

KCOL0

PWRKEY

TPLED19

12345

SIDE KEY 1 右 侧键

6

J9

SIDEKEY-6PIN

J3

PWK_KEY

1

2

[3,8]

PWRKEY

GPIO_CMRST

[2,8]

CMPDN2

[2]

CMDAT6

CMDAT4

CMDAT5

CMDAT0

CMPCLK

CMDAT1

CMDAT2

[2]

[2] CMDAT3

[2]

[2]

[2]

[2]

[2]

[2,8]

SCL_1

PIN1 右上角

1

2NC3

SCL

GND

+X

U305A1

+Y

MXC6225XC

VDD5SDA4INT

6

C12

100nF

SDA_1

VIO28_PMU

[2,8]

[1,3,5,7,8]

VREF

RESET(FRONT)

19

18

CAMERA_818_22_FRONT

nc

后

13

Main CAM

Sub CAM

SDA_0

SCL_0

CMRST2

CMMCLK

CMDAT7

CMHSYNC

CMVSYNC

VCAMA_PMU

GPIO_CMPDN

VCAMD_PMU

[2]

[2]

[2]

[2,8]

VCAMD_IO_PMU

[2,8]

[2]

[2]

[2,8]

[2,8]

[3,8]

[3,8]

[2,3,8]

1uF

C141

C140

1uF

C83

1uF

Power Key

Camera

Camera

G-Sensor

100nF

C143

C305

100nF

[2]

[2]

[2]

[2]

[2,8]

CMMCLK

MIPI_RDN1

MIPI_RDP1

MIPI_RCN

MIPI_RCP

21

20

18

17

15

14

GND

GND

GND

GND

MCLK

MIPI_RCN19MIPI_RCP

MIPI_RDN116MIPI_RDP1

SCL_0

GPIO_CMRST

GPIO_CMPDN

[2,8]

[2,8]

[2,8]

2.2uF

C77

2V8

2V8

1V2

1V8

100nF

VCAMD_PMU

VCAMA_PMU

VCAM_AF_PMU

VCAMD_IO_PMU

[3,8]

[3,8]

[3]

[2,3,8]

C175

[1,3,5,7,8]

VIO28_PMU

MMA8452Q

U305

G_SENSOR_INT

[2]

[2]

[2]

MIPI_RDN0

MIPI_RDP0

24

23

MIPI_RDP022MIPI_RDN0

AGND3SIO_D4SIO_C5PDN6RESET7NC8AVDD289VAF10DVDD1811DOVDD1812GND

1NC2

SDA_0

[2,8]

[1,2,3,4,5,8]

VIO18_PMU

14

VDD

GND

R95

4.7k

FLASH_N

10

VOUT9PGND8SGND

U8004

VIN2C13C24FLASH5EN

1

C162

[2]

[2,8]

[2,8]

EINT4_ALPXS

SCL_1

SDA_1

1

7

SDA2INT

SCL

U1609

GND

VDD

6

8

LDR4LEDK5LEDA

3

ASIC-SENSOR-STK3310

2SC4617

Q1

R13

100k

R8

2.2k

pu

[8]

GPIO58_FLASH_SEL

[2,8]

[8]

FLASH_N

R59

R60

0.36R

47k

7FB6

RSET

OCP8110

pu

1uF

C166

10k

GPIO58_FLASH_SEL

[2,8]

GPIO144_FLASH_EN

[2]

R56

CAMERA FLASH LED

[1,2,3,4,5,8]

VIO18_PMU

KXCJK-1013:NC

C145

NC

nc

C142

NC

16NC15NC2

9

1

C144

NC

BYP

13

INT2

NC

VDDIO

8

NC

3

GND

12

SA010GND11INT14SCL6SDA5GND

nc

7

R52

SCL_1

[2,8]

VIO18_PMU

SDA_1

[1,2,3,4,5,8]

[2,8]

FLASH_LED_3528

25MA350MA

-

1+2

D7

12

D8

NC

R1

VBAT

FLASH_P

[8]

FLASH_N

[8]

[3,5,8]

FLASH_LED

ALS & PS Sensor

100nF

C146

0

R51

R97

5.1

2.2uF

C147

VIO28_PMU

[1,3,5,7,8]

[8]

FLASH_P

C167

4.7uF

4.7uF

[3,5,8] VBAT

Flash 505mA Troch 185mA

Flash 100mA for backup

CTP

J4

[2]

[2]EINT8_CTP

GPIO57_CTP_RSTB

1

RST2INT3SDA4SCL

TPLED13

TPLED14

[3]

[2,8]

[2,8]

SCL_1

VGP1_TP_2.8

SDA_1

T11

T9

T8

T6

T3

C82

1uF

5

6

GND

7

FH34SRJ-06S-05SH_887

GND

8

GND

VDDIO(2.8V)

TPLED17

TPLED15

TPLED18

TPLED16

J12

GND2LED-3LED+4GND5VDD6VDDIO187LPTE8RESET9GND10DATA_0_N11DATA_0_P12GND13DATA_1_N14DATA_1_P15GND16CLK_N17CLK_P18GND19ADC(1.2V)20GND

1

T24

T20

C90

1uF

1uF

LPTE

MIPI_TDP0

C56

MIPI_TDN0

VIO18_PMU

VIO28_PMU

[2]

GPIO59_LRSTB

[2]

[2]

[2]

[1,3,5,7,8]

[1,2,3,4,5,8]

LED-

VBAT

[3]

[3,5,8]

MIPI_TDN1

[2]

[2] MIPI_TDP1

MIPI_TCN

[2]

MIPI_TCP

[2]

TFT_T818_20PIN

VIO18_PMU

[1,2,3,4,5,8]

VIO28_PMU

[1,3,5,7,8]

C95

1uF

C94

1uF

H9

H4

H8

H3

H2

H1

H7

H6

H5

F1

F3

1

FIDUCIAL

1

FIDUCIAL

FIDUCIAL

1

FIDUCIAL_1MM_SINGLESIDE

F4

FIDUCIAL

FIDUCIAL_1MM_SINGLESIDE

F2

1

FIDUCIAL_1MM_SINGLESIDE

FIDUCIAL_1MM_SINGLESIDE

LCD

Loading...

Loading...