5 4 3 2 1

JUMPER

3.9nH

R801

[1]GGE_PA_VRAMP

[1]GGE_PA_ENABLE

[1]ASM_VCTRL_A

[1]ASM_VCTRL_B

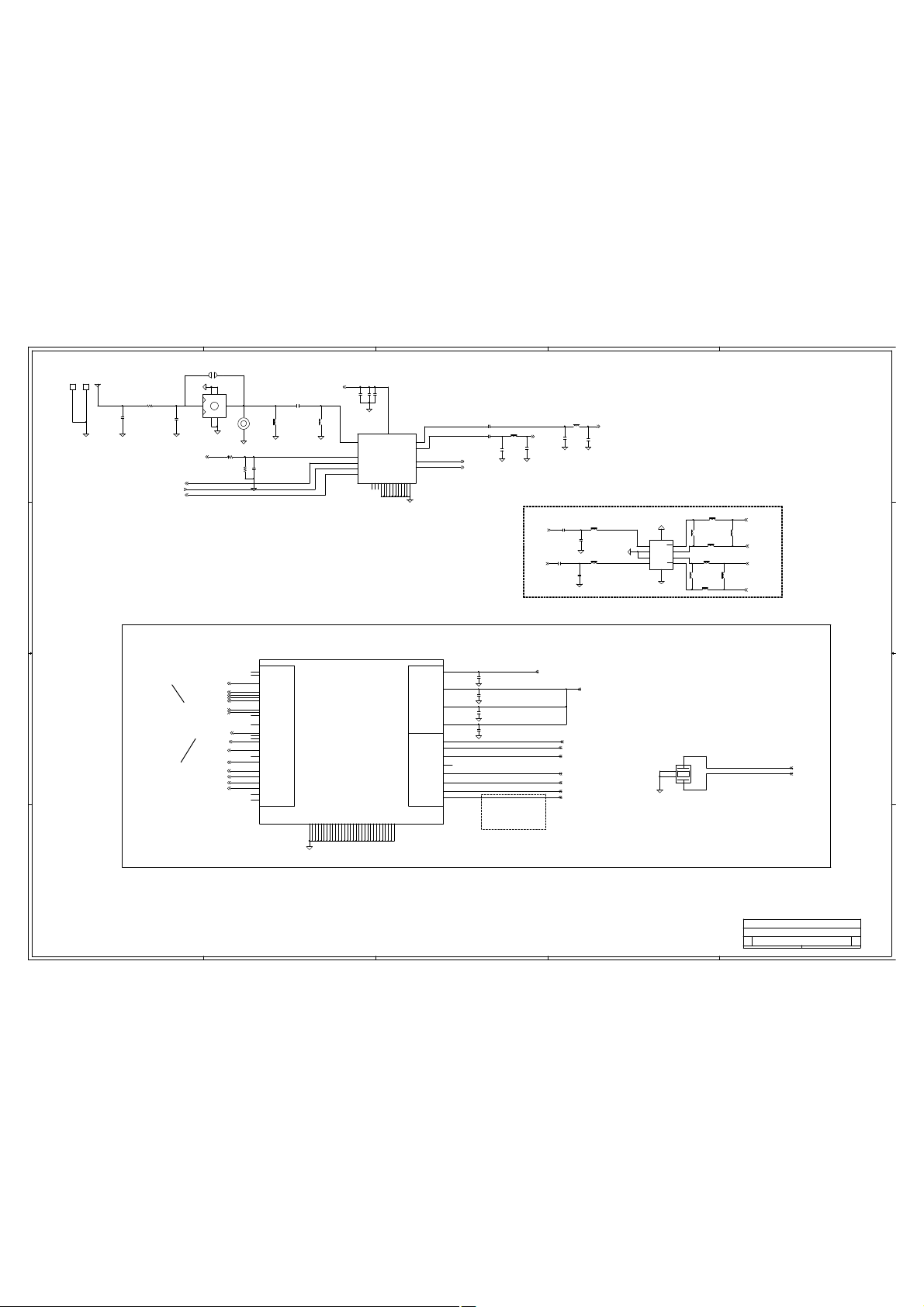

AP300

ECT818000001

1

ANT2RF

AU115

3

GND4GND

GND6GND

5

R814

NC

RFGND

AU114

PAD-RF

L700

10K 1%

C839220pF

R824 24K 1%

[5,8,9]

VBAT

C840

C847100nF

C825

22uF

C8640R

NC

L701

6pF

GND

R213

4.7nH

GGE_PA_HB_IN

C606 56pF

[1]

C8262.7pF

C8282.7pF

GND

L127

4.3nH

[1]LB_RX_N

NC

L118 2.2nH

C165NC

GND

L129

C448NC

GND

GND

3nH

ACX BALUN

18nH

GND

10

U606

L130

G

1

9

LBIN

LBOUT

2

8

GND

LBOUT

3

7

GND

HBOUT

4

6

HBIN

HBOUT

G

5

GND

L616

L128

4.3nH

2.7nH

L132

NC

L134

2.7nH

L133

[1]LB_RX_P

[1]HB_RX_N

L131

4.3nH

[1]HB_RX_P

8.2nH

GGE_PA_LB_IN

[1]

C890

2.2pF

2G_Rx

[1]RX_2G_LB

[1]RX_2G_HB

C707 22pF

D

C

RX_2G_HB

RX_2G_LB

C80722pF

R113

C829

56pF

C817

2.2pF

GND

[1]

[1]

18

U100

VBATT

14

ANTENNA

22

VRAMP

21

TX_EN

20

GPCTRL0

19

GPCTRL1

VC5278

3

TX_HB

5

TX_LB

11

RX0

12

RX1

NC

GND2GND1GND4GND

GND7GND8GND9GND10NC

NC

GND

GND24GND

6

17

16

13

15

23

GND

AU182

PAD

PAD

PAD

AU181

AU180

0R

R721

D

C

C760 NC

GND

[8]CTP_RST

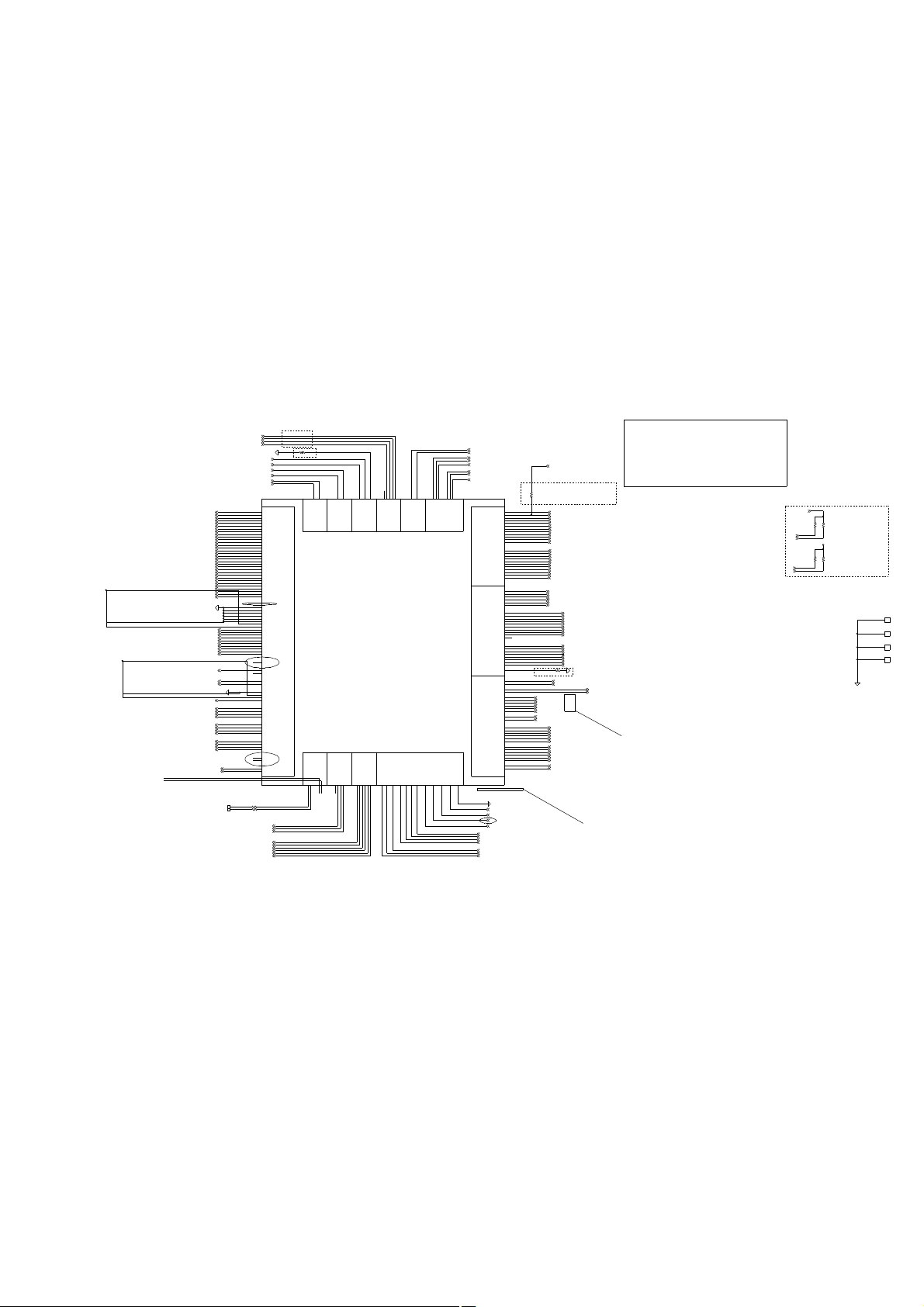

U101-D

B9

VM0

A9

VM1

G9

APC

B11

BPI_BUS0

C12

BPI_BUS1

C10

BPI_BUS2

A11

BPI_BUS3

C13

BPI_BUS4

C9

BPI_BUS5

E11

BPI_BUS6

F9

BPI_BUS7

E10

BPI_BUS8

F10

BPI_BUS9

F8

BPI_BUS10

E8

BPI_BUS11

B6

TXO_HB

A7

TXO_B40

B7

TXO_LB

A4

RX_LBINN

A3

RX_LBINP

B3

RX_HBINN

B2

RX_HBINP

B5

RX_B40INN

B4

RX_B40INP

MT6571_LPDDR2_V12_20131219

GSM & TD

MT6571_Cell RF

GND_CELLB8GND_CELLC1GND_CELLC2GND_CELLC3GND_CELLC4GND_CELLC5GND_CELLC6GND_CELLC7GND_CELLC8GND_CELLD2GND_CELLD3GND_CELLD4GND_CELLD5GND_CELLD6GND_CELLD7GND_CELLE2GND_CELLE3GND_CELLE4GND_CELLE5GND_CELLE6GND_CELLE7GND_CELLF2GND_CELLF3GND_CELLF4GND_CELLF5GND_CELLF6GND_CELLF7GND_CELLG3GND_CELLG7GND_CELL

A1

AVDD28_VTCXO

Power

AVDD18_LF

AVDD18_HF_TRX

AVDD18_HF_DCO

26M & CLK Buffer

XTAL1

XTAL2

CLK2

CLK3_TP3

CLK4_TP4

OUT_32K

XMODE_TP2

DCXO_32KEN_TP1

D1

H1

A8

B1

E1

F1

G6

H2

G4

G5

G2

G1

籔 R632 co-lay

470nF

C642

470nF

C644

100nF

C645

470nF

C646

Put away from RF

[1,3,5]VTCXO_PMU

[5]VRF18_PMU

[1]XTAL1

[1]XTAL2

[6]CONN_XO_IN

[5]CLK4_AUDIO

DCXO_32K

[5]DCXO_32K

[1,3,5]VTCXO_PMU

[1,3,5]VTCXO_PMU

3

X2

4

G

2

G

X1

X100

1

26MHz NC

GND

[1]XTAL1

[1]XTAL2

B

HW trapping PIN BPI_BUS4

Must be sure BPI_BUS4 is under

0.2*VDD28_BPI during booting

(please refer to HW design notice)

HW trapping PIN BPI_BUS5 and 6

Must be sure BPI_BUS5 and 6 are under

B

0.2*VDD28_BPI during booting

(please refer to HW design notice)

HW trapping PIN BPI_BUS9 and BUS10

Must be sure BPI_BUS9 and BUS10 is under

0.2*VDD18_BPI during booting

(please refer to HW design notice)

[1]GGE_PA_VRAMP

[1]ASM_VCTRL_A

[1]ASM_VCTRL_B

ASM_VCTRL_C

[1]GGE_PA_ENABLE

BPI_BUS4

BPI_BUS5

ANT_SEL0

BPI_BUS6

[8] CM_FLASH_EN

BPI_BUS9

BPI_BUS10

[8]EINT_CTP

[1]GGE_PA_HB_IN

[1]GGE_PA_LB_IN

[1]LB_RX_N

[1]LB_RX_P

[1]HB_RX_N

[1]HB_RX_P

Refer to page "03_MT6323_PMIC Core" for 32K setting

A

No. 1, Dusing Rd. 1, Hsinchu Science Park

Hsin-Chu City, Taiwan 300. R.O.C.

RF-EDGE/TD

MT6571 REF PHONE

Thursday, December 26, 2013

TEL: +886-3-567-0766 FAX:+886-3-578-7610

4 99

12345

ofSheetDate:

Title

A2

A

RevDocument NumberSize

1.0

AP-PTH-2.2DRILL-3.4D-V525

AP-PTH-2.2DRILL-3.4D-V525

EINT_MAG

[4]ED31

[4]ED30

[4] ED29

[4]ED28

[4]ED27

[4]ED26

[4] ED25

[4]ED24

[4] ED23

[4] ED22

[4]ED21

[4] ED20

[4]ED19

[4]ED18

[4]ED17

[4]ED16

[4]ED15

[4]ED14

[4]ED13

[4]ED12

[4]ED11

[4] ED10

[4]ED9

[4] ED8

[4] ED7

[4] ED6

[4] ED5

[4] ED4

[4]ED3

[4]ED2

[4] ED1

[4]ED0

for DDR2 : AG25 must NC

[4] EA9

[4] EA8

[4] EA7

[4] EA6

[4] EA5

[4]EA4

[4] EA3

[4] EA2

[4]EA1

[4] EA0

for DDR2 : AF26 must NC

[4]

EVREF

[4]

ECS0_B

[4]

ECS1_B

[4]ECKE

[4]EDQM0

[4]EDQM1

[4]EDQM2

[4]EDQM3

[4]EDQS0

[4]EDQS1

[4]EDQS2

[4]EDQS3

[4]EDQS0_B

EDQS1_B

[4]

[4]EDQS2_B

[4]EDQS3_B

for DDR2 : AA18+AB18 must NC

EDCLK_B

[4]EDCLK

[4]

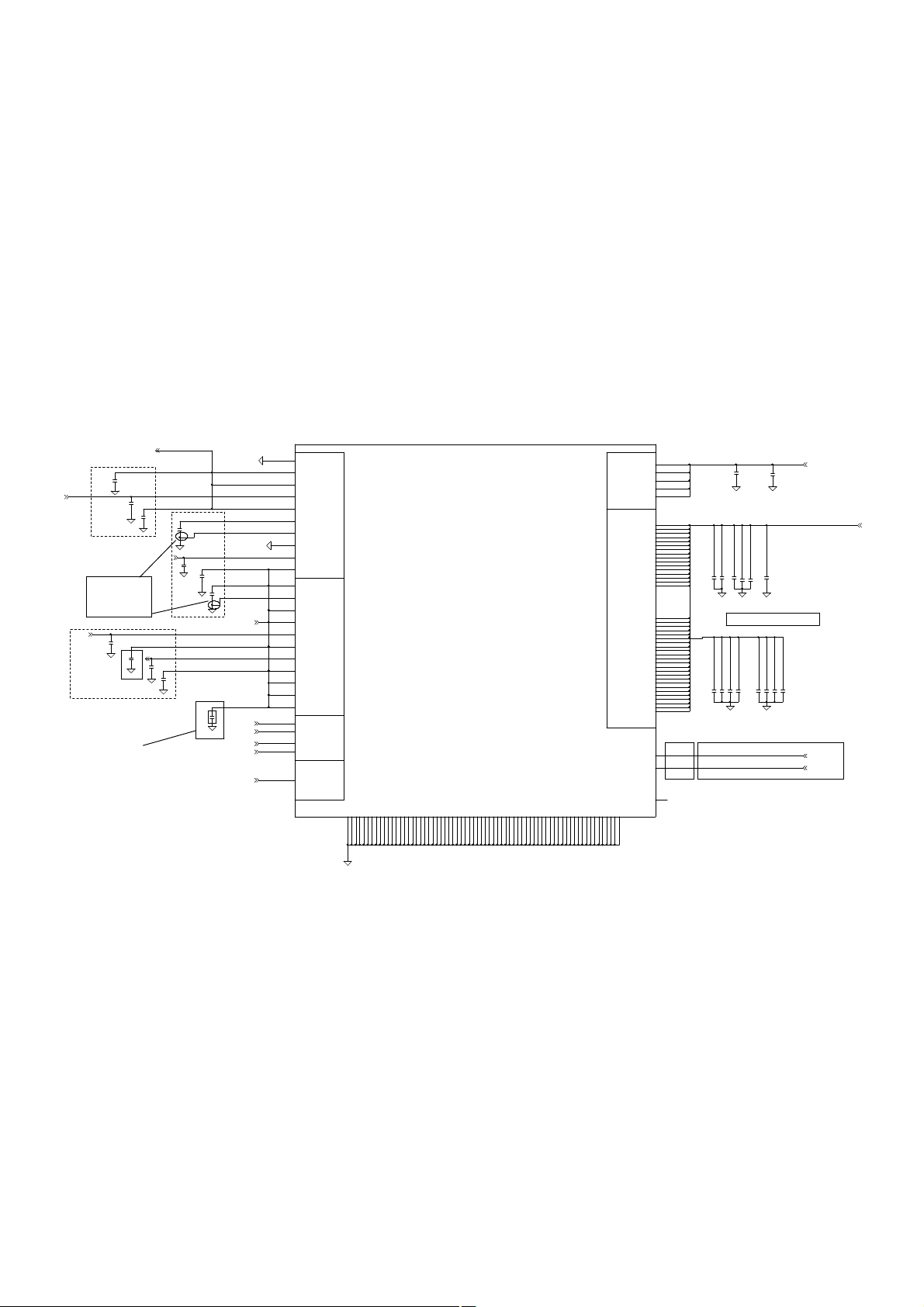

UART1 : AP UART

AU30

AU31

[8] EINT_ACC

[8] EINT_ALPXS

EINT_GY

MC1_INS

[9] USB_DP

[9] USB_DM

[8] CM_FLASH_ON

[7] EINT_EAR

[5] CHD_DP

[5] CHD_DM

AD15

AG16

AD10

AG12

AD13

AG13

AG25

AG24

AD23

AG22

AD22

AD11

AG21

AD18

AG19

AG18

AD12

AA13

AA14

AA18

AA19

R521 1K

R530

MC1CMD

MC1CK

MC1DAT2

MC1DAT3

[2,8]

SCL1

[2,8]SDA1

LED_GPIO100

SDI

SCLK

SDA

NAND & eMMC

LCD

Camera

MT6571_LPDDR2_V12_20131219

[9]KCOL0

[9]KCOL1

MC0_RSTB__DDR2_

MC0_DAT7__DDR2_

MC0_DAT6__DDR2_

MC0_DAT5__DDR2_

MC0_DAT4__DDR2_

MC0_DAT3__DDR2_

MC0_DAT2__DDR2_

MC0_DAT1__DDR2_

MC0_DAT0__DDR2_

MC0_CK__DDR2_

MC0_CMD__DDR2_

PMIC_SPI_SCK

ND0__DDR2_

ND1__DDR2_

ND2__DDR2_

ND3__DDR2_

ND6__DDR2_

ND8__DDR2_

ND9__DDR2_

ND12__DDR2_

ND13__DDR2_

ND15__DDR2_

NCEB__DDR2_

NWRB__DDR2_

WATCHDOG

EINT_PMIC

AA4

AB2

W5

Y1

AA3

AA2

Y2

Y4

Y3

W1

Y5

AA5

AC1

AE3

AD3

AD2

AE2

AF2

AF1

AC3

AC2

AD1

AF3

AE25

LPCEB

AC24

LPTE

AD24

LRSTB

AC25

LPRDB

AD26

LPA0

AD25

LPWRB

AC23

LPD9

AB23

LPD8

AB22

LPD7

AA22

LPD6

Y22

LPD5

W22

LPD4

W23

LPD3

V23

LPD2

V24

LPD1

AB24

LPD0

AA25

TDN2

Y25

TDP2

Y26

TDN0

W26

TDP0

U25

TDN1

U26

TDP1

W25

TCN

V25

TCP

U24

MIPI_VRT

N21

SCL_0

M21

SDA_0

L23

CMPCLK

K24

CMMCLK

R21

RDN0

P21

RDP0

P20

RDN1

P19

RDP1

U22

RCN

V22

RCP

K25

CMRST

K23

CMPDN

P25

CMDAT0

N25

CMDAT1

N26

CMDAT2

M26

CMDAT3

M25

CMDAT4

P24

CMDAT5

R26

RDN0_A

R25

RDP0_A

P22

RDN1_A

P23

RDP1_A

T22

RCN_A

R22

RCP_A

N22

CMRST2

M22

CMPDN2

[4,5]

[5]RESETB

[5]

[5]

[5]PMIC_SPI_CS

[5]PMIC_SPI_MISO

[5]PMIC_SPI_MOSI

[5]AUD_CLK

[5]AUD_MISO

[5]AUD_MOSI

MT6571 support JTAG from below :

1. KP (recommand)

2. MC1

3. CAM

for JTAG pin out from MC1/CAM, refer

to HW design notice

[2,3,4,5,8]VIO18_PMU

1K/NC

HW trapping PIN R211

&

eMMC ON

1K: eMMC

NC: NAND

R211

[4]NLD0

[4]

NLD1

[4]NLD2

[4]NLD3

[4]NLD6

[4]NLD8

[4]NLD9

[4]NLD12

[4]NLD13

[4]NLD15

NCEB

[4]

[4]

NWRB

[4]

NLD10

[4]

NALE

[4]NCLE

[4]NLD4

[4]

NLD5

[4]NLD7

[4]

NLD14

[4]NLD11

[4]

GPIO74

[4]NREB

[4]NRNB

CS

[8]

LPTE

LRSTB

[8]

HS

DE

VS

LCM_G5

LCM_G4

LCM_G3

LCM_G2

LCM_B7

LCM_B6

LCM_B5

LCM_B4

LCM_B3

LCM_G7

LCM_G6

TDN0

TDN1

TCN

TCP

R2211.5K

[2,8]SCL0

[2,8]SDA0

100-ohm differential

MIPI_RDN0

MIPI_RDP0

MIPI_RDN1

MIPI_RDP1

MIPI_RCN

MIPI_RCP

[8]CMRST

[8]CMPDN

CMDAT0

CMDAT1

[8]CMDAT2

[8]CMDAT3

[8]CMDAT4

[8]CMDAT5

[8]CMHSYNC

[8]CMVSYNC

[8]CMDAT6

[8]CMDAT7

[8]CMDAT8

[8]CMDAT9

CMRST2

[8]

[8]CMPDN2

[5]PMIC_SRCLKENA

72 C⊿

Please make sure the ball map is

match to the MCP type you selected

For other memory pin mux, please refer

to Design Notice "DDR1/DDR2 Pin Mux"

and "NAND/eMMC Pin Mux"

[8]

[8]TDP0

[8]

[8]TDP1

[8]

[8]

Close to BB IC

reserve for de-sense

HW trapping PIN for JTAG debug from KP(serial)

Reserve R footprint for JTAG

debugging

(please refer to HW design notice)

[8]CMPCLK

[8]CMMCLK

Based on your system level design , if better

desense performance is needed on your

system , please refer to desense

performance enhance proposal

Normal : NC

JTAG : 4.7K

[2,8]

[2,8]

[2,8]

[2,8]

[2,3,4,5,8] VIO18_PMU

SDA1

SCL1

SDA0

SCL0

R223 2.2K

R222 4.7K

VCAMD_IO_PMU

R224 2.2K

R215 4.7K

Power by CTP, MEMS sensor

Power by CAM_IO

1

AP26

NC

1

AP20

1

AP21

1

AP22

NC

GND

Only GPI

Close to BB

R220 5.1K

90-ohm differential

C11

D11

E25

E26

F25

K5

K6

PWM_A

SPI_MOSI

G24

PWM_B

SPI_SCK

SPI_CS

E23

F23

USB_DP

USB_DM

USB_VRT

MC1_CMD

MC1_DAT0

MC1_DAT1

MC1_DAT2K4AUD_DAT_MOSI

MC1_CKL4AUD_CLK_MOSI

MC1_DAT3

J25

G22

H22

H25

K22

L25

L5

M5

M6

AUX_XP

AUX_YP

AUX_YM

AUX_IN0

L21

EMI - LPDDR2

URXD2

L22

CHG_DP

CHG_DM

URXD1

UTXD2

UTXD1

URXD2

A25

B25

B26

C25

MT6571_BB

SPI_MISO

G23

U101-C

AG2

ED31__DDR2_

AC5

ED30__DDR2_

AE5

ED29__DDR2_

AD5

ED28__DDR2_

AG3

ED27__DDR2_

AF5

ED26__DDR2_

AC6

ED25__DDR2_

AG5

ED24__DDR2_

AC16

ED23__DDR2_

AE15

ED22__DDR2_

ED21__DDR2_

AC14

ED20__DDR2_

ED19__DDR2_

AF14

ED18__DDR2_

AF16

ED17__DDR2_

AF15

ED16__DDR2_

AE8

ED15__DDR2_

AC9

ED14__DDR2_

AD8

ED13__DDR2_

AD7

ED12__DDR2_

AG8

ED11__DDR2_

AF7

ED10__DDR2_

AF6

ED9__DDR2_

AC8

ED8__DDR2_

AF11

ED7__DDR2_

AG9

ED6__DDR2_

ED5__DDR2_

AE13

ED4__DDR2_

ED3__DDR2_

ED2__DDR2_

AF10

ED1__DDR2_

ED0__DDR2_

EA18__DDR2_

AF23

EA17__DDR2_

AF21

EA16__DDR2_

AF17

EA15__DDR2_

AF24

EA14__DDR2_

AF22

EA13__DDR2_

AE22

EA12__DDR2_

EA11__DDR2_

AC19

EA10__DDR2_

EA9__DDR2_

EA8__DDR2_

AE21

EA7__DDR2_

EA6__DDR2_

AC20

EA5__DDR2_

AF20

EA4__DDR2_

AF19

EA3__DDR2_

AC18

EA2__DDR2_

AF18

EA1__DDR2_

AE18

EA0__DDR2_

AF26

ERESET

VREF0

AC17

VREF1

ECS0_B__DDR2_

AE24

ECS1_B__DDR2_

EWR_B__DDR2_

ERAS_B__DDR2_

ECAS_B__DDR2_

AF25

ECKE__DDR2_

AE12

EDQM0__DDR2_

EDQM1__DDR2_

AC13

EDQM2__DDR2_

AE7

EDQM3__DDR2_

EDQS0__DDR2_

AB9

EDQS1__DDR2_

AB14

EDQS2__DDR2_

AA8

EDQS3__DDR2_

AB13

EDQS0_B

AA9

EDQS1_B

EDQS2_B

AB8

EDQS3_B

AB18

EDCLK0

EDCLK0_B

EDCLK1

AB19

EDCLK1_B

1K

SPI_MOSI

SPI_SCK

SPI_CSB

[9]

[9]

[9]MC1DAT0

[9]MC1DAT1

[9]

[9]

GPIO100

GPIO101

A24

B24

C24

D23

D24

D25

K17

K18

KCOL1

KCOL0

KCOL2

SDA_1

SCL_1

KROW2

KROW0

KROW1

AUX_XM

Double KeyI2CADCUSBPWMBC 1.1

SYS CtrlMSDCSPIUART

PMIC_SPI_MOSI

M4

TESTMODE

WATCHDOGP1SRCLKENAP2SYSRSTBP3PMIC_SPI_MISOP4PMIC_SPI_SCKT1PMIC_SPI_CSNT2AUD_DAT_MISO

EINTX

N2

U1

M2

A

[1,5]

VTCXO_PMU

Close to BB

GND ball return to

cap :

REFN

1.REFN(F11)

2.DVSS18_MIPI(U23)

[5,7,8]VIO28_PMU

Reserve for eMMC

Close to BB

Based on your system level design , if better

desense performance is needed on your

system , please refer to desense

performance enhance proposal

[2,3,4,5,8]VIO18_PMU

C102 100nF

100nF

C100

C101 100nF

100nF

C104

reserve for de-sense

U101-A

V7

DVDD18_FSRC

V8

DVDD18_PLLGP

K1

AVDD18_AP

Power In

L1

AVDD28_DAC

J1

AVDD18_MD

G11

[5]SIM1_SCLK

REFP

F11

REFN

D26

AVSS33_USB

G25

AVDD33_USB

G26

AVDD18_USB

T26

DVDD18_MIPI

U23

DVSS18_MIPI

K26

DVDD18_CM

G10

DVDD18_BPI

A13

DVDD28_BPI

AB1

DVDDIO_MC0

J26

DVDDIO_MC1

V2

DVDD18_VIO

A23

DVDD18_VIO2

V5

DVDDIO_NF

AB26

DVDD18_LP

R2

SIM1_SCLK

U2

SIM1_SIO

K3

SIM2_SCLK

U3

SIM2_SIO

N1

CLK32K_IN

MT6571_LPDDR2_V12_20131219

IO Power

SIM

32K

MT6571_ABB

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN9VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSP9VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR9VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSST9VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J22

C23

L11

L12

L13

L24

A26

M10

M11

M12

M13

M14

M15

GND

P10

P11

P12

P13

P14

P15

P16

P17

N10

N11

N12

N13

N14

N15

N16

M16

M23

T10

R10

R11

R12

R13

R14

R15

R16

R17

VSS

T11

T12

T13

T14

T15

T16

U10

U11

U12

U13

U14

U15

C103 100nF

C109 1uF

[5]VUSB_PMU

C113

1uF

C115

100nF

C108

100nF

Close to BB

[5]VMC_PMU

C131

1uF

100nF

C118

[2,3,4,5,8]VIO18_PMU

150mil

150mil

C199

100nF

SIM1_SIO

[5]

[5]SIM2_SCLK

[5]SIM2_SIO

[5]

CLK32K_BB

EMI Power

Y9

VCCIO_EMI

Y12

VCCIO_EMI

Y14

VCCIO_EMI

Y16

VCCIO_EMI

Y19

VCCIO_EMI

VPROC_PMU

P5

VCCK_CPU

P6

VCCK_CPU

P7

VCCK_CPU

P8

VCCK_CPU

R5

VCCK_CPU

R6

VCCK_CPU

R7

VCCK_CPU

R8

VCCK_CPU

T5

VCCK_CPU

T6

VCCK_CPU

T7

VCCK_CPU

T8

VCCK_CPU

U5

VCCK_CPU

U6

VCCK_CPU

U7

Vcore Power

VCCK_CPU

U8

VCCK_CPU

L7

VCCK

L8

VCCK

L9

VCCK

L10

VCCK

L14

VCCK

L15

VCCK

L16

VCCK

L17

VCCK

M7

VCCK

M8

VCCK

M9

VCCK

M17

VCCK

N17

VCCK

T17

VCCK

U9

VCCK

U17

VCCK

V10

VCCK

V11

VCCK

V12

VCCK

V13

VCCK

V14

VCCK

V15

VCCK

V16

VCCK

V17

VCCK

Close to BB

R3

RS_VDD

T3

RS_VSS

AG26

VSSW2VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y11

AF4

AF8

U16

AA21

AA24

AC11

AD21

NC

VSS

VSS

VSS

VSS

VSS

AG6

AG1

AF12

AG15

&&

C136

2.2uF

VPROC_PMU

&&&& &&&&

C111

100nF 0201

100nF 0201

MT6571.RS_VDD connect to MT6323.VPROC_FB

MT6571.RS_VSS connect to MT6323.GND_VPROC_FB

4mil - defferential - GND shielding

Vproc remote sense :

differential 4mil with good shielding, from the BB to PMIC

& &

C117 1uF

&

&

& &

C137

C123

C135

C116

10uF

2.2uF

10uF

10uF

Star-connection from big cap

C124

C112

C110

C107

100nF 0201

100nF 0201

1uF

1.2V IO for DDR2

C138

4.7uF

C119

C125

1uF

1uF

C139 4.7uF

VIO_EMI

120mil

double sided SMT

Bottom cap: 0.1uF*4+1uF*2

1st priority cap: 1uF

1st group cap: 1uF*1+2.2uF*2

+4.7uF*1+10uF*3

single sided SMT

1st priority cap: 0.1uF

1st group cap: 0.1uF*3+1uF*4

+2.2uF*2+4.7uF*1+10uF*3

C127

1uF

VPROC_FB

GND_VPROC_FB

[4,5]

[5]

VPROC_PMU

[5]

[5]

Loading...

Loading...