5

www.bufanxiu.com

4

3

2

1

First International Computer,Inc

D D

Portable Computer Group HW Department

Board name : Mother Board Schematic

Project : VA250W_250D

C C

Version : 0.2

1. Schematic Page Description :

2. PCI & IRQ & DMA Description :

3. Block Diagram :

4. Net name Description :

Current Date : Oct 20, 2006

5. Board Stack up Description :

6. Schematic modify Item and History :

7. power on & off & S3 Sequence :

8. Layout Guideline :

9. switch setting

B B

Manager Sign by: Avery Lee, Adam

Drawing by : Richard Wang

Total confirm by:

A A

LAN Circuit check by:

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Audio Circuit check by:

5

4

Title

Size Document Number Rev

C

3

2

Date: Sheet of

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<>

1

1 56Friday, October 20, 2006

0.2

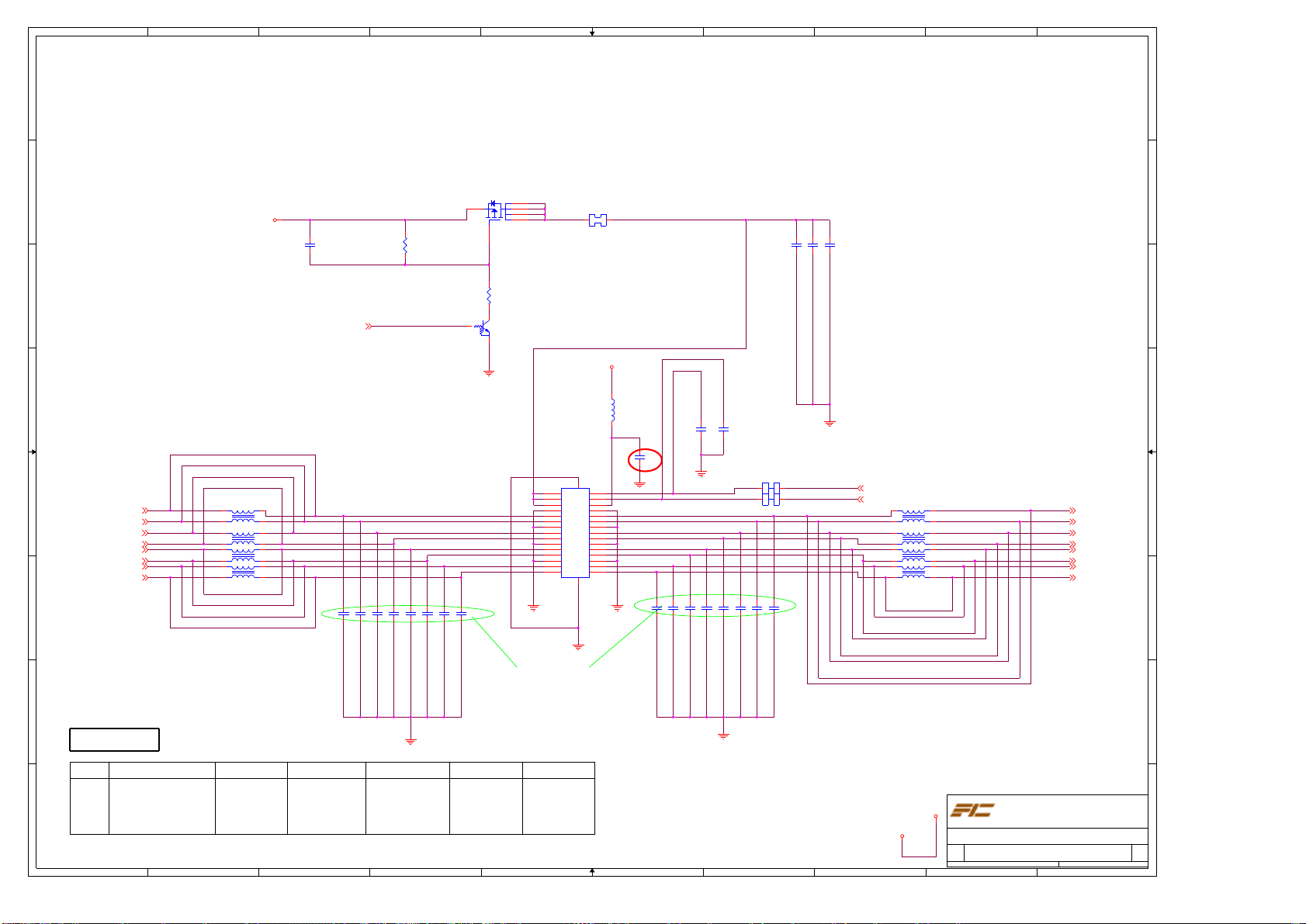

37. DIP/Lid/Power

www.bufanxiu.com

Switch & LED

8

7

6

5

4

1. Schematic Page Description :

VA250W/D Schematic Ver : 0.2

3

2

1

D D

1. Title

2. Schematic Page Description

3. Block Diagram

4. ANNOTATIONS

5. Schematic Modify

6. Timing Diagram

7. DDR Layout Guideline 51. Charge Circuit

8. Yonah processor (1/2)

9. Yonah processor (2/2)

10. POWER (CPU CORE)

11. Thermal

12. Clock Generator

C C

13. Clock Buffer

14. VN896 (1/4)

15. VN896 (2/4)

16. VN896 (3/4)

17. VN896 (4/4)

18. DDR SO-DIMM1

19. DDR SO-DIMM0

20. VT1637 LVDS Transmitter

21. LCD Connector

22. CRT Connector

2. PCI & IRQ & DMA Description :

B B

IDSEL

AD17

PCIINT

IRQA

IRQB

IRQC

IRQD

A A

BUSMASTER

REQ

REQ0 / GNT0

REQ1 / GNT1

REQ2 / GNT2

REQ3 / GNT3

REQ4 / GNT4

8

CHIP

Mini PCI(Wireless LAN)

CHIP

NB

MiniPCI

MiniPCI

IRQH

CHIP

Mini PCI(Wireless LAN)

7

PCI-E

23. VT8237A (1/3)

24. VT8237A (2/3)

25. VT8237A (3/3)

26. Power Good & Fan Controller

27. Blank

28. RTC and MODEM Conn.

29. MINI PCI Conn.

30. VT6103L PHY

31. USB CNN

32. HDD / CD-ROM CNN

33. LPC PMU08

34. LPC KBC M38827

35. INT KBC / GP Connector

36. ENI component

37. DIP/Lid/Power Switch & LED

38. Firm Ware Hub

39. Reset Circuit

40. SCREW

41. VT1708A Audio Codec

42. G1432+1410 Audio Amplifier

43. H.P. Out / Audio CNN

44. PWR Block

IRQ0

IRQ1

IRQ2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8

IRQ9

IRQ10

IRQ11

IRQ12

IRQ13

IRQ14

IRQ15

6

System timer

Keyboard

(Casacde)

LAN / MODEM

Serial Port

AUDIO / VGA / USB

FLOPPY DISK

LPT

RTC

ACPI

FIR

Cardbus

PS/2 mouse

FPU

HDD

CDROM

5

(Disable by default)

(MODEM/LAN)

4

45. 1.5VDDA/S , 1.8/2.5VDDM/A

46. VCCP/1.5VDDM

47. DDR II Power

48. 3VDDA / 5VDDA

49. POW-ON Controller

50. ADIN / Battery CNN

52. Inverter Controller

53. On board Audio

54. Unused Switch transfer board

55. Update List

56. Unused Audio Board

DMA Channel

DMA0 FIR

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

3

DeviceIRQ Channel Desciption

(disable by default)

ECP

FLOPPY DISK

AUDIO

(Cascade)

Unused

Unused

Unused

(MODEM / LAN)

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet of

2

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<>

2 56Friday, October 20, 2006

1

0.2

8

www.bufanxiu.com

7

6

5

4

3

2

1

3. Block Diagram :

D D

Thermal

Sensor

GMT G796

P11

Intel

Yonah Celeron

or C7 via

400/533/667MHz

Processor

Host Bus

P8,9

VIA

CPU

CORE

P10

CPU

VCCP

P46

DDR2 400/533

INTERFACE

P18,P19

CLK ICS953009AFLF

P12

CLK Buffer

P13

Power Good

P26

LED and LID/DIP/Power SW

P37

Power Block

P44

MAIN SW

P49

VN896

CRT

C C

LCD

RJ-45

ACIN

P50

3VDDA/5VDDA

B B

P48

A A

8

PMU3V/5V

3VDDS/5VDDS

3VDDM/5VDDM

1.8VDDS/DDM

DDR 0.9VDDM

VCCP/1.5VDDM

Over Voltage

Protect

Battery

charger

Battery Select

BAT CON

Battery Voltage

sense

P22

VT1637

P21

P30

P48

P48

P48

P47

P47

P46

P?

P51

P51

P50

P33

7

LVDS Tx

LAN Phy

VT6103L

USB 2.0

USB(2),3

P31

6

P20

MII BUS

P30

USB0,1

Mini PCI

P31

32Bit PCI BUS

P29

952 HSBGA

P14~P17

Hub Interface

VT8237A

539 BGA

P23~P25

LPC M3885X

INT K/B

5

Mem Bus

IDE BUS

S-ATA

LPC BUS

K/B CTRL

P35

CDROM

HDA-Link

P34

GP

P35

4

HDD

P32

P32

FLASH ROM

( F/W Hub)

4M

FAN CNN

RTC

RESET

P38

P11

P28

P39

3

Azalia

CODEC

VT1708A

MDC CNN

P28

P41

LPC

PMU08

P33

Audio

AMP

HEADPHONE

Mic IN

2

P42

P43

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet of

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<>

3 56Friday, October 20, 2006

1

0.2

8

www.bufanxiu.com

7

6

4. Net name Description :

5

4

3

2

1

5.Board Stack up Description

Voltage Rails

DCIN

PMU5V 5.0V always on power rail by LATCH or ACIN

D D

PMU3V 3.3V always on power rail by LATCH or ACIN

3VDDA 3.3V always on power rail by DCON or PSUSC0

3VDDS 3.3V power rail

5VDDS 5.0V power rail

3VDDM

Vcore_CPU

VCCP 1.05V for AGTL+ Termination Voltage

DDR_0.9VDDM 0.9V DDR Termination Voltage

1.5VDDM 1.5V switched power rail

1.5VDDS 1.5V power rail

1.5VDDA 1.5V always on power rail

2.5VDDS 2.5V power rail for DDR

C C

Primary DC system power supply

5.0V always on power rail by DCON or PSUSC05VDDA

3.3V switched power rail

5.0V switched power rail5VDDM

Core Voltage for CPU

1.8V for CPU PLL Voltage1.8VDDM

PCB Layers

Layer 1

Layer 2

Layer 3

Layer 4

Layer 5

Layer 6

Component Side, Microstrip signal Layer

Ground Plane

Stripline Layer(AGTL,CLOCK,DDR)

Stripline Layer(Analog,LVDS,other)

Power Plane

Solder Side,Microstrip signal Layer

Part Naming Conventions

C

=

Capacitor

CN

D

F

L

Q

R

B B

RP

U

Y

Connector

=

Diode

=

Fuse

=

Inductor

=

Transistor

=

Resistor

=

Resistor Pack

=

Arbitrary Logic Device

=

Crystal and Osc

=

Net Name Suffix

0 =

Active Low signal

Signal Conditioning

_D_

_Q_

_L_

A A

Damped (by a resistor)

=

Isolated (by a Q-switch)

=

Filtered (by an inductor or bead)

=

8

7

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

6

5

4

3

Date: Sheet of

2

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<>

1

4 56Friday, October 20, 2006

0.2

5

www.bufanxiu.com

4

3

2

1

6.Schematic modify Item and History :

D D

C C

B B

A A

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<>

1

5 56Friday, October 20, 2006

0.2

5

www.bufanxiu.com

4

3

7. power on & off & S3 Sequence :

2

1

D D

Power On Sequencing Timing Diagram

VID

VR_ON

Vcc-core

CPU_UP

Tboot

Tsft_star_vcc

Tcpu_up

Vboot

Tboot-vid-tr

Vid

Vccp

Vccp_UP

Tvccp_up

Vccgmch

GMCHPWRGD

Tgmch_pwrgd

CLK_ENABLE#

IMVP4_PWRGD

C C

BATTERY ONLY POWER ON TIMING

POWSW0

PMU5V/PMU3V

DCON

VDDA

MAINSW0_ICH

PM_RSTRST0

PM_SLP_S30/S40/S50

PSUSC0

B B

A A

SUSTAT_B0

VDDM,VDDS

PM_PWROK

SYS_PWROK

VRON_VCCP

VCCP/1.2VDDM

VCORE_ON

VR_ON

VCORE_CPU

CK408_PWRGD0

PM_VGATE

CPU_PWRGD

PCI_RST0

AGTL+_CPURST0

Tcpu_pwrgd

To ICH4

To ICH4

From ICH4

From ASIC_B0

From ASIC_B0

To clock generator

To ODEM and ICH4

From ICH4 to CPU

To ODEM/other PCI device

From ODEM to CPU

S3 SUSPEND AND RESUME TIMING

POWSW0

PMU5V/PMU3V

PM_RSMRST0

PM_SLP_S30

PM_SLP_S40/S50

SUSTAT_B0

PM_PWROK

SYS_PWROK

VRON_VCCP

VCCP,1.2VDDM

VCORE_ON

VCORE_CPU

CK408_PWRGD0

PM_VGATE

CPU_PWRGOOD

PCI_RST0

AGTL+_CPURST0

DCON

VDDA

PSUSC0

VDDS

VDDM

VR_ON

H

H

H

H

H

H

H

To ICH4_M

From ICH4_M

From ICH4_M

From ASIC_B0

From ASIC_B0

1.5VDDS AND

DDR_PWRGD

Generator

To clock

ToICH4 and ODEM

From ICH4 to CPU

To ODEM/other

PCI device

From ODEM to CPU

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<>

1

6 56Friday, October 20, 2006

0.2

5

www.bufanxiu.com

4

3

2

1

8. Layout Guideline :

Montara-GM DDR Layout Guidelines

Note that all length matching formulas are based on GMCH die-pad to SO-DIMM pin total length

D D

DDR Signal Groups

Group Signal Name

Clocks

SCK[5:0]

SCK#[5:0]

Data

SDQ[71:0]

SDQS[8:0]

SDM[8:0]

Control

SCKE[3:0]

SCS#[3:0]

Command

SMA[12:6,3:0]

SBA[1:0]

SRAS#

SCAS#

SWE#

CPC

SMA[5,4,2,1]

SMAB[5,4,2,1]

Feedback

RCVENOUT#

RCVENIN#

Length Matching Formulas

Signal Group Minimum Length Maximum Length

Control to Clock

Command to Clock

CPC to Clock

Strobe to Clock

Data to Strobe

Clock - 1.0"

Clock - 1.0"

Clock - 1.0"

Clock - 1.0"

Strobe - 25 mils Strobe + 25 mils

Clock + 0.5"

Clock + 2.0"

Clock + 0.5"

Clock + 0.5"

Clock Signals Topologies and Routing Guidelines

SO-DIMM PADS

C C

GMCH

Pin

P1 L1

Package Length

Range

Min:0.5"

Max:5.0"

7 mil trace, 4 mil pair space

Clock length tolerenve within the pair : +/- 10 mil

Clock to Clock Length Matching : +/- 25 mils

Minimum Pair to Pair Spacing : 20 mils

Minimum Spacing to other Signals : 20 mils

CLOCKS LENGTH

HCLKCPU[1..0]

HCLKNB[1..0]

HCLKITP[1..0]

66MCLK_ICH

66MCLK_GMCH

AGPCLK_ATI

PCLKICH

PCLKCB

PCLK1394

PCLKUSB20

PCLKOP

PCLKFWH

PCLKSIO

PCLKLAN

14MCLK_SIO

14MCLK_ICH

14MCLK_AC97

48MCLK_ICH

48MCLK_CB

2" ~ 8 "

4.5" ~ 9.0 "

MAX : 8.5"

4.5"~9.0"

4.5"~9.0"

3.5" ~ 12.5"

TRACE / SPACE NOTES

5 / 20 mils

(5 mil space

between + & - )

5 / 20 mils

Differentials pairs with1.

the same length

(within 10 mil)

2.CPU & NB trace

mismatch within

450 mil

* 66MCLK_ICH &

AGPCLK_GMCH

AGPCLK_ATI

Length mismatch

within 100 mils

1.Making PCI length with

minimum various

2.Max skew = 1ns

5 / 20 mils

5 / 10 mils

5 / 20 mils

Data Signals Topologies and Routing Guidelines

GMCH

Pin

Package Length

Range

B B

Control Signals Topologies and Routing Guidelines

GMCH

Pin

Package Length

Range

L1

P1

P1

L1

L2 L3 L4

SO-DIMM0

SO-DIMM1

PADS

PADS

L2

56 ohm 5%

56 ohm 5%

Minimun Spacing to Trace Width Ratio, SDQ/SDM : 2 to 1

Minimum Spacing to other Signals : 20 mils

Trace Length L1 : Min 0.5" , Max 3.75"

Length Matching : SDQS to SCK/SCK#

Trace spacing to trace width ratio : 2 to 1

Minimum Spacing to other Signals : 20 mils

Trace Length L1 : Min 0.5" , Max 5.5"

Length Matching : CTRL(P1+L1) to SCK/SCK#

L2 : Max 0.75"

L3 : Min 0.25" , Max 1.0"

L4 : Max 1.0 "

SDQS , SODIMM0 P1+L1+L2

SDQS , SODIMM1 P1+L1+L2+L3

Min : Clock - 1.0" , Max : Clock + 0.5"

SDQ/SDM to SDQS : +/- 25 mils

L2 : Max 2.0"

Min : Clock - 1.0" , Max : Clock + 0.5"

SO-DIMM0,1 PADS

Command Signals Topologies and Routing Guidelines

GMCH

Pin

A A

Package Length

Range

L1

P1

SO-DIMM0

PADS

5

10 ohm 5%

L2

L3 L4

SO-DIMM1

PADS

56 ohm 5%

Trace spacing to trace width ratio : 2 to 1

Minimum Spacing to other Signals : 20 mils

Trace Length L1 : Min 0.5" , Max 4.0"

Length Matching : CMD to SCK/SCK#

L2 : Max 1.0"

L3 : Max 2.0"

L2+L3 : Max 3.0"

L4 : Max 1.0"

4

CMD , SODIMM0 P1+L1+L2

CMD , SODIMM1 P1+L1+L3

Min : Clock - 1.0" , Max : Clock + 2.0"

SDQS : 3 to1

CPC Signals Topologies and Routing Guidelines

GMCH

Pin

P1

Package Length

Range

3

L1

SO-DIMM0,1 PADS

SDQ/SDM to SDQS Mapping

Signal Mask

SDQ[7..0]

SDQ[15..8]

SDQ[23..16]

SDQ[31..24]

SDQ[39..32]

SDQ[56..40]

SDQ[55..48]

SDQ[63..56]

SDQ[71..64]

SDM[0]

SDM[1]

SDM[2]

SDM[3]

SDM[4]

SDM[5]

SDM[6]

SDM[7]

SDM[8]

L2

56 ohm 5%

2

Relative To

SDQS[0]

SDQS[1]

SDQS[2]

SDQS[3]

SDQS[4]

SDQS[5]

SDQS[6]

SDQS[7]

SDQS[8]

Mismatching

+/- 25 mil

+/- 25 mil

+/- 25 mil

+/- 25 mil

+/- 25 mil

+/- 25 mil

+/- 25 mil

+/- 25 mil

+/- 25 mil

Trace spacing to trace width ratio : 2 to 1

Minimum Spacing to other Signals : 20 mils

Trace Length L1 : Min 0.5" , Max 5.5"

Length Matching : CPC(P1+L1) to SCK/SCK#

L2 : Max 2.0"

Min : Clock - 1.0" , Max : Clock + 0.5"

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet of

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<>

1

7 56Friday, October 20, 2006

0.2

A

www.bufanxiu.com

B

C

D

E

AGTL+_HA03

AGTL+_HA04

AGTL+_HA05

AGTL+_HA06

AGTL+_HA07

AGTL+_HA08

AGTL+_HA09

AGTL+_HA010

AGTL+_HA011

AGTL+_HA012

AGTL+_HA013

AGTL+_HA014 H_INIT0

4 4

3 3

AGTL+_HA0[31..3]<14>

AGTL+_ADSTB00<14>

AGTL+_HREQ0[4..0]<14>

AGTL+_HA0[31..3]<14>

AGTL+_ADSTB10<14>

H_A20M0<25>

H_IGNNE0<25>

H_STPCLK0<25>

H_INTR<25>

H_NMI<25>

H_SMI0<25>

AGTL+_HA0[31..3]

AGTL+_HREQ0[4..0]

AGTL+_HA0[31..3]

H_A20M0

H_FERR0

H_IGNNE0

H_STPCLK0

H_INTR

H_NMI

H_SMI0

AGTL+_HA015

AGTL+_HA016

AGTL+_HREQ00

AGTL+_HREQ01

AGTL+_HREQ02

AGTL+_HREQ03

AGTL+_HREQ04

AGTL+_HA017

AGTL+_HA018

AGTL+_HA019

AGTL+_HA020

AGTL+_HA021

AGTL+_HA022

AGTL+_HA023

AGTL+_HA024

AGTL+_HA025

AGTL+_HA026

AGTL+_HA027

AGTL+_HA028

AGTL+_HA029

AGTL+_HA030

AGTL+_HA031

No stub on H_STPCLK test point

VCCP<9,12,14,17,25,26,38,46>

H_A20M0

CPU_DPSLP0

H_IGNNE0

H_INIT0

H_INTR

H_STPCLK0

H_NMI

H_CPUSLP0

H_SMI0

PSI0

H_FERR0

AGTL+_BR00

AGTL+_CPURST0

CPU_PWRGOOD

2 2

1KΩ 1% 1/10W SMT0603 LR

2KΩ 1% 1/10W SMT0603 LR

1 1

R888 150Ω 1% 1/10W SMT0603 LR

R890 150Ω 1% 1/10W SMT0603 LR

R892 150Ω 1% 1/10W SMT0603 LR

R894 150Ω 1% 1/10W SMT0603 LR

R895 150Ω 1% 1/10W SMT0603 LR

R896 150Ω 1% 1/10W SMT0603 LR

R897 150Ω 1% 1/10W SMT0603 LR

R898 150Ω 1% 1/10W SMT0603 LR

R899 150Ω 1% 1/10W SMT0603 LR

R900 150Ω 1% 1/10W SMT0603 LR(NU)

R901 51Ω 1% 1/10W SMT0603 LR

R902 220Ω 5% 1/10W SMT0603 LR

R903 51Ω 1% 1/10W SMT0603 LR

R970 470Ω 5% 1/10W SMT0603 LR

AGTL+_HD0[63..0]<14>

VCCP<9,12,14,17,25,26,38,46>

R821

R825

AGTL+_HD0[63..0]<14>

GTLREF

1uF 6.3V 10% SMT0402 X5R LR

1uF 6. 3V 1 0% S MT0 402 X5R LR

C938

C93 7

C93 9

220 pF 50V 10% SMT 0402 X7 R LR

A

A#[32-39], APM#[0-1]:Leave escape routing on for future functionality

AGTL+_HD0[63..0]

AGTL+_DSTBN00<14>

AGTL+_DSTBP00<14>

AGTL+_DINV00<14>

AGTL+_DSTBN10<14>

AGTL+_DSTBP10<14>

AGTL+_DINV10<14>

C940

220p F 50V 10% SM T0402 X7R LR

AGTL+_HD0[63..0]

10mils

VCCP<9,12,14,17,25,26,38,46>

Zo=55ohm, 0.5" max for GTLREF, Space any other switch

signals away from GTLREF with a minimum of 25mils.

Don't allow the GTLREF routing to create splits or

discontinuities in the reference planes of the FSB signals

R826

1KΩ 5% 1/16W SMT0402 LR(NU)

R828

51Ω 5% 1/16W SMT0402 LR

H_BSEL0<12>

H_BSEL1<12>

H_BSEL2<12>

R972 10KΩ 5% 1/16W SMT0402 LR

R974 10KΩ 5% 1/16W SMT0402 LR

R1396 10KΩ 5% 1/16W SMT0402 LR

U59A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

A[6]#

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

ADDR GROUP 0 ADDR GROUP 1

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

RSVD[11]

SCKT Molex ZIF BGA SMT micro-FCPGA478 47170-4787 Yonah CPU 478Pin LR

Micro-FCPGA 478

CONTROLXDP/ITP SIGNALSHCLK THERM

RESERVED

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

DBR#

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

BCLK[0]

BCLK[1]

RSVD[12]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RSVD[18]

RSVD[19]

RSVD[20]

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

HIT#

E4

XDP_BPM0

AD4

XDP_BPM1

AD3

XDP_BPM2

AD1

XDP_BPM3

AC4

XDP_PRDY

AC2

XDP_PREQ

AC1

XDP_TCK

AC5

TCK

XDP_TDI

AA6

TDI

XDP_TDO

AB3

TDO

XDP_TMS

AB5

TMS

XDP_TRST0

AB6

XDP_DBRESET0

C20

D21

A24

A25

C7

510Ω 5% 1/16W SMT0402 LR

A22

A21

T22

R1388220Ω 5% 1/16W SMT0402 LR (NU)

D2

F6

R1389220Ω 5% 1/16W SMT0402 LR (NU)

D3

C1

AF1

R1390220Ω 5% 1/16W SMT0402 LR (NU)

D22

R1395220Ω 5% 1/16W SMT0402 LR (NU)

C23

C24

AGTL+_BR00

R811 51Ω 1% 1/10W SMT0603 LR

AGTL+_CPURST0

H_ADSTB0N <14>

Rout to TP via and place gnd via w/in 100mils

AGTL+_HD00

AGTL+_HD01

AGTL+_HD02

AGTL+_HD03

AGTL+_HD04

AGTL+_HD05

AGTL+_HD06

AGTL+_HD07

AGTL+_HD08

AGTL+_HD09

AGTL+_HD010

AGTL+_HD011

AGTL+_HD012

AGTL+_HD013

AGTL+_HD014

AGTL+_HD015

AGTL+_HD016

AGTL+_HD017

AGTL+_HD018

AGTL+_HD019

AGTL+_HD020

AGTL+_HD021

AGTL+_HD022

AGTL+_HD023

AGTL+_HD024

AGTL+_HD025

AGTL+_HD026

AGTL+_HD027

AGTL+_HD028

AGTL+_HD029

AGTL+_HD030

AGTL+_HD031

GTLREF

H_TEST1

H_TEST2

H_BSEL1

H_BSEL2

U59B

E22

D[0]#

F24

D[1]#

E26

D[2]#

H22

D[3]#

F23

DATA GRP 0 DATA GRP 1

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

H26

F26

K22

H25

H23

G22

J26

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

AD26

C26

D25

B22

B23

C21

SCKT Molex ZIF BGA SMT micro-FCPGA478 47170-4787 Yonah CPU 478Pin LR

Micro-FCPGA 478

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

MISC

B

DATA GRP 2DATA GRP 3

DSTBN[2]#

DSTBP[2]#

DSTBN[3]#

DSTBP[3]#

DPRSTP#

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPSLP#

DPWR#

AGTL+_HD032

AA23

AGTL+_HD033

AB24

AGTL+_HD034

V24

AGTL+_HD035

V26

AGTL+_HD036

W25

AGTL+_HD037

U23

AGTL+_HD038

U25

AGTL+_HD039

U22

AGTL+_HD040

AB25

AGTL+_HD041

W22

AGTL+_HD042

Y23

AGTL+_HD043

AA26

AGTL+_HD044

Y26

AGTL+_HD045

Y22

AGTL+_HD046

AC26

AGTL+_HD047

AA24

W24

Y25

V23

AGTL+_HD048

AC22

AGTL+_HD049

AC23

AGTL+_HD050

AB22

AGTL+_HD051

AA21

AGTL+_HD052

AB21

AGTL+_HD053

AC25

AGTL+_HD054

AD20

AGTL+_HD055

AE22

AGTL+_HD056

AF23

AGTL+_HD057

AD24

AGTL+_HD058

AE21

AGTL+_HD059

AD21

AGTL+_HD060

AE25

AGTL+_HD061

AF25

AGTL+_HD062

AF22

AGTL+_HD063

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

SLP#

AE6

PSI#

AGTL+_ADS0 <14>

AGTL+_BNR0 <14>

AGTL+_BPRI0 <14>

AGTL+_DEFER0 <14>

AGTL+_DRDY0 <14>

AGTL+_DBSY0 <14>

AGTL+_BR00 <14>

H_INIT0 <25,38>

AGTL+_LOCK0 <14>

AGTL+_CPURST0 <14>

AGTL+_RS00 <14>

AGTL+_RS01 <14>

AGTL+_RS02 <14>

AGTL+_TRDY0 <14>

AGTL+_HIT0 <14>

AGTL+_HITM0 <14>

VCCP<9,12,14,17,25,26,38,46>

R813

VCCP<9,12,14,17,25,26,38,46>

Should be connect to ICH7 and Calistoga without T-ing(no stub)

XDP_TDO

XDP_TMS

XDP_TDI

XDP_PREQ

XDP_PRDY

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

XDP_DBRESET0

XDP_TRST0

XDP_TCK

AGTL+_HD0[63..0]

AGTL+_HD0[63..0]

H_PWRGD rise time :

Max : 15ns

COMP0

R822 27.4Ω 1% 1/10W SMT0603 LR

COMP1

R823 54.9Ω 1% 1/10W SMT0603 LR

COMP2

R824 27.4Ω 1% 1/10W SMT0603 LR

COMP3

R827 54.9Ω 1% 1/10W SMT0603 LR

H_DPRSTP0

CPU_DPSLP0

CPU_PWRGOOD

H_CPUSLP0

PSI0

H_DPRSTP0 <10>

CPU_DPSLP0 <25>

AGTL+_DPWR0 <14>

CPU_PWRGOOD <26>

H_CPUSLP0 <17,25>

PSI0 <10>

Modify Q79 Library 2006.0608

VCCP <9,12,14,17,25,26,38,46>

R812

75Ω 5% 1/16W SMT0402 LR

PROCHOT#

THERMDA <11>

THERMDC <11>

VCCP <9,12,14,17,25,26,38,46>

2/6 Change

to VCCP

CPU_BCLK <12>

CPU_BCLK0 <12>

XDP P/U & P/D

R815 75Ω 1% 1/10W SMT0603 LR

R816 54.9Ω 1% 1/10W SMT0603 LR

R817 54.9Ω 1% 1/10W SMT0603 LR

R818 54.9Ω 1% 1/10W SMT0603 LR(NU)

R886 54.9Ω 1% 1/10W SMT0603 LR(NU)

R887 220Ω 5% 1/10W SMT0603 LR(NU)

R889 220Ω 5% 1/10W SMT0603 LR(NU)

R891 220Ω 5% 1/10W SMT0603 LR(NU)

R893 220Ω 5% 1/10W SMT0603 LR(NU)

R814 150Ω 1% 1/10W SMT0603 LR(NU)

R819 680Ω 5% 1/10W SMT0603 LR

R820 27Ω 5% 1/10W SMT0603 LR

AGTL+_HD0[63..0] <14>

Modify Q73 Library 2006.0608

H_FERR0

E C

TRANS NPN MMBT2222A 40V 600mA SOT-23 3PIN PSI LR

AGTL+_DSTBN20 <14>

AGTL+_DSTBP20 <14>

AGTL+_DINV20 <14>

AGTL+_HD0[63..0] <14>

AGTL+_DSTBN30 <14>

AGTL+_DSTBP30 <14>

AGTL+_DINV30 <14>

DPRSLPVR<10,25>

R976

470Ω 5% 1/16W SMT0402 LR

TRANS NPN MMBT3904 40V 200mA SOT-23 3PIN PSI LR

2.5VDDM<13,20,23,24,25,26,36,45>

Q73

B

R904

10KΩ 5% 1/16W SMT0402 LR

VCCP<9,12,14,17,25,26,38,46>

R973 470Ω 5% 1/16W SMT0402 LR

Q79

B

E C

C

R971

10KΩ 5% 1/16W SMT0402 LR

FERR0 <25>

VCCP <9,12,14,17,25,26,38,46>

R975

Topology : FERR#

ICH7mCPU

VCCP L1

L2

VCCP

CPU IMVP6

Rtt

L4

L2+L1 L3 Strip-line

Topology : PWRGOOD

CPU

L1

ICH7m

L1

0.5" - 12"

0.5" - 12" Strip-line

Topology : INTR , NMI , A20M# , DPSLP# , IGNNE# , INIT# , SMI# , STPCLK#

L1CPU ICH7m

L1

0.5" - 12" Micro-strip

0.5" - 12"

Topology : THERMTRIP#

GMCHL2CPU ICH7m

VCCP<9,12,14,17,25,26,38,46>

FSB Common Clock Signal Layout Guide :

ADS# , BNR# , BPRI# , BR0# , DBSY# , DEFER# , DPWR# , DRDY# , HIT# , HITM# , LOCK# ,

RS[2..0]# , TRDY# , RESET#.

Transmission Line Type Total Trace Length

Strip-line(Int. Layer)

Micro-strip(Ext. Layer)

FSB Source Synchronous Data Length Variation and Strobe Matching Requirements :

Signals Name

DATA#[15..0] , DINV0#

DATA#[31..16] , DINV1#

DATA#[47..32] , DINV2#

FSB Source Synchronous Data Signal Routing Topology#1 :

Signal Name

DATA#[63..0]

DSTBN#[3..0]

DSTBP#[3..0]

FSB Source Synchronous Address Length Variation and Strobe Matching Requirements :

Signals Name Strobes associated with the group

A#[16..3] , REQ#[4..0]

A#[31..17]

*** No length matching requirements exist between ADSTB0# and ADSTB1#

FSB Source Synchronous Address Signal Routing :

Signal Name

Address#[31..3]

REQ#[4..0]

ADSTB#[1..0]

Layout Note:

Address [16~3 and 30] ,REQ[4..0],H_ADSTB0[1..0],

need routing on same plan.

Address [29~17 and 31] ,AGTL+_ADSTB10 are not used.

L3

1.0 ~ 6.5 inch

Signals Matching

+/- 100 mils

+/- 100 mils

+/- 100 mils

+/- 100 mils

Transmission Line Type

Strip-line

Strip-line

Strip-line

Strip-line

Signals Matching

+/- 200 mils

+/- 200 mils

Transmission Line Type

Strip-line

Strip-line

Strip-line

For C7M-V4

C7 Changing

H_DPRSTP0

SHW 0 5% 1/16W 0402

Comp0,2 connect with Zo=27.4ohm, make trace

length shorter than 0.5" and width is 18mils.

Comp1,3 connect with Zo=55ohm, make trace

length shorter than 0.5" and width is 5mils

Rtt

VCCP

Rtt

Transmission Line

Micro-strip

Transmission Line

Strip-line

RttL1 L4

D

L2

Rtt Transmission Line

0" - 3.0" Micro-strip0.5" - 12"

56 +/-5%

0" - 3.0"

0.5" - 6.5"

0.5" - 6.5"

56 +/-5%

L3 L4

0" - 3.0"

0" - 3.0"

0.5" - 12"L1

Topology : CPUSLP#

Topology : RESET#

VCCP

Rtt

L1 L2

1" - 12"

1" - 12" 1" - 6"

L1+L3

1" - 6" 0" - 3.0"

1" - 12"

1" - 12"

Normal Impedance

55+/-15%

Strobes associated with the group

DSTBP0#,DSTBN0#

DSTBP1#,DSTBN1#

DSTBP2#,DSTBN2#

DSTBP3#,DSTBN3#

Total Trace Length Normal Impedance

0.5 ~ 5.5 inchDINV#[3..0]

0.5 ~ 5.5 inch

0.5 ~ 5.5 inch

0.5 ~ 5.5 inch

ADSTB0#

ADSTB1#

Total Trace Length

0.5 ~ 6.5 inch

0.5 ~ 6.5 inch

0.5 ~ 6.5 inch

Source Synchronous ADDRESS :

Address#[31..3] , REQ#[4..0] , ADSTB#[1..0]

Transmission Line Type

Strip-line

55+/-15%

55+/-15%

55+/-15% 4 & 12 mils

Normal Impedance Width & Spacing (mils)

55+/-15%

55+/-15%

55+/-15%

Signals Name

Strip-line

Rtt Transmission LineL2L1

0" - 3.0"

0" - 3.0"

Spacing (mils)

4 & 8 mils

5 & 10 mils

Total Trace Length

1.0 ~ 5.5 inch

Signals Matching

+/- 100 milsA#[31..3] , REQ#[4..0]

Micro-strip70 +/-5%0.5" - 6.5"

70 +/-5%0.5" - 6.5"

Transmission Line

L1CPU

GMCH

0.5" - 12"

L1

GMCH

L1

L3

0" - 3.0"

0" - 3.0"

Title

Size Document Number Rev

Date: Sheet of

Rss

24 +/-5%

24 +/-5% 56 +/-5%

Strobe-to-Strobe Complement Matching

+/- 25 mils

+/- 25 mils

+/- 25 mils

+/- 25 milsDATA#[63..48] , DINV3#

Width & Spacing (mils)

Data-to-Data,Strobe-to-strobe

4 & 8 mils

4 & 8 mils

4 & 12 mils

4 & 12 mils

Strobe to Assoc. Address Signal Matching

+/- 200 mils

+/- 200 mils

4 & 8 mils

4 & 8 mils

4 & 8 mils

Normal Impedance

55+/-10%

Strobes associated

with the group

ADSTB00/01,

VA250W/D < VIA C7 + VN896 + VT8237A >

C

Yonah Processor (1/2)

Micro-strip

Strip-line

0.5" - 12"

Transmission LineCPU

L1

Micro-strip

1" - 6"

Strip-line

1" - 6"

Rtt

56 +/-5%

ADSTB01

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

E

Transmission LineL4

Micro-strip

Strip-line0" - 3.0"

Strobe-to-Data

N/A55+/-15%

N/A

4 & 12 mils

Spacing (mils)

4 & 12

Strobe Matching

+/- 20 mils

8 56Friday, October 20, 2006

0.2

A

www.bufanxiu.com

B

C

D

E

Place these inside socket cavity on L8

(North side secondary)

4 4

3 3

2 2

VCORE_CPU<10,33,36>

C85 6 22 uF 6 .3V ± 2 0% S MT0 805 X5R C20 12X5 R0J 226M TD K L R(NU)

C853 22uF 6.3V ± 20% SM T0805 X5R C 2012X5R0J226M TDK LR(NU)

C857 22uF 6.3V ± 20% SM T0805 X5R C 2012X5R0J226M TDK LR(NU)

C854 22uF 6.3V ± 20% SM T0805 X5R C2012X5R0J226M TDK LR(NU)

C855 22uF 6.3V ± 20% SM T0805 X5R C 2012X5R0J226M TDK LR(NU)

12

12

12

12

12

Place these inside socket cavity on L1

(North side Primary)

C88 0 22 uF 6 .3V ± 2 0% S MT0 805 X5R C20 12X5 R0J 226M TD K L R(NU)

12

C88 5 22 uF 6 .3V ± 2 0% S MT0 805 X5R C20 12X5 R0J 226M TD K L R(NU)

C884 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

C88 2 10 uF 6 .3V 10% SM T080 5 X5 R C 2012 X5R 0J10 6K TDK L R

C883 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

C881 10uF 6.3V 10% SM T0805 X5R C2012X5R0J106K TDK LR

12

C862 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

C859 10uF 6.3V 10% SM T0805 X5R C2012X5R0J106K TDK LR

North side secondary

Place these inside socket cavity on

L8 (South side secondary)

C86 5 10 uF 6 .3V 10% SM T080 5 X5 R C 2012 X5R 0J10 6K TDK L R

C86 7 22 uF 6 .3V ± 2 0% S MT0 805 X5R C20 12X5 R0J 226M TD K L R(NU)

C864 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

C866 22uF 6.3V ± 20% SM T0805 X5R C 2012X5R0J226M TDK LR(NU)

12

12

Place these inside socket cavity on L1

(South side Primary)

C888 22uF 6. 3V ± 2 0% SM T0805 X5 R C2012X5R0J2 26M TDK LR(N U)

C88 6 22 uF 6 .3V ± 2 0% S MT0 805 X5R C20 12X5 R0J 226M TD K L R(NU)

C887 22uF 6.3V ± 20% SM T0805 X5R C 2012X5R0J226M TDK LR(NU)

C889 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

12

12

12

C871 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

C870 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

C86 8 22 uF 6 .3V ± 2 0% S MT0 805 X5R C20 12X5 R0J 226M TD K L R(NU)

C86 9 22 uF 6 .3V ± 2 0% S MT0 805 X5R C20 12X5 R0J 226M TD K L R(NU)

12

C891 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

C872 22uF 6.3V ± 20% SM T0805 X5R C 2012X5R0J226M TDK LR(NU)

12

12

South side secondary

U59C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

SCKT Molex ZIF BGA SMT micro-FCPGA478 47170-4787 Yonah CPU 478Pin LR

Micro-FCPGA 478

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

H_VID0 <10>

H_VID1 <10>

H_VID2 <10>

H_VID3 <10>

H_VID4 <10>

H_VID5 <10>

H_VID6 <10>

C877 0.1uF 16V ± 1 0% SM D0603 X7R LR

C874 10uF 6.3V 10% SM T0805 X5R C2 012X5R0J106K TDK LR

C87 5 0. 1uF 16V ± 1 0% S MD0 603 X7R LR12C87 8 0. 1uF 16V ± 10 % SMD 0603 X7 R LR

C876 0.1u F 16V ± 10% SM D0603 X7R LR

12

12

Close to CPU

pin B26

C892

0.01uF 16V 10% SMT0402 X7R LR

Via:2.5A

>100mils

VCCP <8,12,14,17,25,26,38,46>

C873

T100uF 2V ±20% ESR=18mΩ SMT7343 EEFCD0D101ER PANASONIC LR

Place these inside socket cavity on L8

(North side secondary)

1.5VDDM<17,20,46>

C893

10uF 6.3V 10% 0805 X5R TDK LR

VCCSENSE <10>

VSSSENSE <10>

18mil

7mil space

12

C87 9 0. 1uF 16V ± 1 0% S MD0 603 X7R LR

12

20mils

+

U59D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

P3 AF24

VSS[081] VSS[162]

SCKT Molex ZIF BGA SMT micro-FCPGA478 47170-4787 Yonah CPU 478Pin LR

Micro-FCPGA 478

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

Route VCCSENSE and VSSSENSE traces

at 27.4 ohms with 50mil spacing.

Place PU and PD within 1 inch of CPU

1 1

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

A

B

C

D

Date: Sheet of

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

Yonah Processor (2/2)

E

9 56Friday, October 20, 2006

0.2

Close L1

www.bufanxiu.com

Rn

=[Rparallel*(Rntc+Rserial)/(Rparallel+Rntc+Rserial)

=[R813*(R815+R811)]/(R813+R815+R811)

=3.4K

Gain factor G=Rn/[RS(eqv)+Rn]=0.57 ----Recommend

RS(eqv)=2.56K

Rfb=[N*Rdroop/(DCR*G)-1]*Rin N:no.

of phase

D D

C C

B B

A A

R357=[2*2.1mV/(1.1m*0.57)-1]*1K=3.96K

Rdroop:Intel spec. -2.1m Ohms

3VDDM

,42,45,46,48,52>

CPUAGND

2 VIA

5

R1302 10Ω 5% 1/16W SMT0402 LR

3VDDM<11,12,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

DCIN_CPU<36,46,47,48,49,50,52>

1uF 10V 10% SMT0603 X5R C1608X5R1A105KT TDK LR

PSI0<8>

VCORE_ON<46>

R1309

499Ω 1% 0402 LR (NU)

THERMO-RES 470KΩ 5% B25/50=4700K± 2% B25/85=4750K SMT0402 NTC ERTJ0EV474J PANASONIC LR(NU)

CPUAGND

R1161

SPWR 0 5% 1/16W 0603

R1110 SHW 0 5% 1/16W 0402

R1305 SHW 0 5% 1/16W 0402

4.02KΩ 1% 1/10W SMT0603 LR(NU)

R1311

H_VID0<9>

H_VID1<9>

H_VID2<9>

H_VID3<9>

H_VID4<9>

H_VID5<9>

H_VID6<9>

VRON_VCCP<26,46>

DPRSLPVR<8,25>

H_DPRSTP0<8>

CLK_ENB<12>

R1317

1.4KΩ 1% 1/10W SMT0603 LR

R1115

61.9KΩ 1% 1/16W SMT0402 LR

R1307 147KΩ 1% 1/10W SMT0603 LR

C1412 0.015uF 16V 10% SMT0402 X7R LR

C1413 0.01uF 16V 10% SMT0402 X7R LR(NU)

R1096 SHW 0 5% 1/16W 0402

R1097 SHW 0 5% 1/16W 0402

R1099 SHW 0 5% 1/16W 0402

R1100 SHW 0 5% 1/16W 0402

R1101 SHW 0 5% 1/16W 0402

R1102 SHW 0 5% 1/16W 0402

R1103 SHW 0 5% 1/16W 0402

R1136 SHW 0 5% 1/16W 0402

R1105 SHW 0 5% 1/16W 0402

R1118 SHW 0 5% 1/16W 0402

R1109 SHW 0 5% 1/16W 0402

R1339 1.82KΩ 0.5% 1/10W SMT0603 LR

470pF 50V 10% SMT0402 X7R LR

2KΩ 1% 1/16W SMT0402 LR(NU)

0.033uF 16V ±10% SMT0402 X7R LR

C1218

390pF 50V 10% SMT0402 X7R LR

4.42KΩ 1% 1/16W SMT0402 LR

C1419

2 VIA

VCCSENSE<9>

VSSSENSE<9>

18mil

7mil space

5

R1303 10Ω 5% 1/16W SMT0402 LR

R1088 10Ω 5% 1/16W SMT0402 LR

5VDDA<31,36,37,45,46,47,48>

CPUAGND

Close L126

R1312

C1415

R1318

1 2

C1220

R1322

47pF 50V 5% SMT0402 NPO LR

0.01uF 16V 10% SMT0402 X7R LR

0.01uF 16V 10% SMT0402 X7R LR

R1119

SHW 0 5% 1/16W 0402

R1120

SHW 0 5% 1/16W 0402

IMVP IV

VCORE_CPU 36A

For Yonah CPU

C1201

4

Load line slope : -2.1mV/A

C1410

0.1 uF 50V 80-20% 0603 Y 5V LR

22

20

VIN

VDD

21

VSS

49

GND

2

PSI#

3

PGD_IN

4

RBIAS

5

VR_TT#

6

NTC

7

SOFT

37

VID0

38

VID1

39

VID2

40

VID3

41

VID4

42

VID5

43

VID6

44

VR_ON

45

DPRSLPVR

46

DPRSTP#

47

CLK_EN#

13

VDIFF

12

FB2

11

FB

10

COMP

9

VW

VSEN

RTN

DROOP

14

15

4

16

R1324

3.9KΩ 1% 1/10W SMT0603 LR

C1227

0.01uF 16V 10% SMT0402 X7R LR

CPUAGND

R1205

10Ω 1% 1/16W SMT0402 LR

R1206

10Ω 1% 1/16W SMT0402 LR

C1225

C1226

CPUAGND

C1411

0.1uF 10V 10% 0402 X5R LR

R1084

10KΩ 5% 1/16W SMT0402 LR(NU)

R1087

SHW 0 5% 1/16W 0402

1

48

U60

LNR-IC ISL6262CRZ-T QFN 48PIN INTERSIL LR

3V3

PGOOD

R1304

35

UGATE1

SPWR 0 5% 1/16W 0603

36

BOOT1

34

PHASE1

32

LGATE1

33

PGND1

24

ISEN1

0.22uF 10V 10% SMT0603 X7R LR

31

PVCC

R1314

27

UGATE2

SPWR 0 5% 1/16W 0603

26

BOOT2

28

PHASE2

30

LGATE2

29

PGND2

23

ISEN2

25

NC

OCSET

VSUM

VO

17

C1420

180pF 50V 5% SMT0402 NPO LR

DFB

CPUAGND

8

19

18

R1323

0.3 3uF 16V ± 1 0% S MT0 603 X7R LR

C1416

1KΩ 1% 1/16W SMT0402 LR

C1414 1000pF 50V 10% SMT0402 X7R LR

R1316 13.3KΩ 1% 1/10W SMT0603 LR

C1417

DCIN<36,46,47,48,49,50,52>

VCORE_PG <26>

C1204

0.22uF 10V 10% SMT0603 X7R LR

R1098

C1206

C1217

0.22uF 10V 10% SMT0603 X7R LR

C1215

0.22uF 10V 10% SMT0603 X7R LR

0.0 33uF 16 V ± 10 % S MT0 402 X7R LR

R1320

10KΩ 5% 1/16W SMT0402 LR(NU)

5VDDA <31,36,37,45,46,47,48>

C1202

4.7uF 10V +80-20% 0805 Y5V LR

R1111

10KΩ 5% 1/16W SMT0402 LR(NU)

VSUM

11K Ω 1% 1 /16 W SM T04 02 L R

R1319

2.61KΩ 1% 1/10W SMT0603 LR

R1321

THERMO-RES 10KΩ 5% B25/50=4250K± 2% B25/85=4300K SMT0603 NTC ERTJ1VR103J PANASONIC LR

C1418

0.22uF 10V 10% SMT0603 X7R LR

VCORE_CPU <9,33,36>

Close Output Cap

Calculation formula

3

DCIN_CPU<36,46,47,48,49,50,52>

12

C1268

C1527

+

4.7uF 25V ± 10% 1206 X5R TDK LR(N U)

E 4 70uF 25 V 20 % 1 05° SMT φ1 0 H= 10m m I mp=0 .15Ω M VY2 5VC4 70M J10E 0 N CC LR (NU )

Close L126

VSUM

IOC*Rdroop=Roc*10uA

If OCP=55A

R807=Roc=11.5Kohm

3

Q85

300mil

IRFR3707Z 30V 61A TO-252 IR LR

D S

D

C1196

C1197

C1269

4.7 uF 25V ± 10 % 1206 X5R T DK LR

4.7uF 25V ± 10% 1206 X5R TDK LR

4.7uF 25V ± 10% 1206 X5R TDK LR

VSUM

R1306 3.65KΩ 1% 1/10W SMT0603 LR

R1308 10KΩ 1% 1/16W SMT0402 LR

R1310 1Ω 1% 1/16W SMT0402 LR

DCIN_CPU<36,46,47,48,49,50,52>

40mils

40mils

R1325 3.65KΩ 1% 1/10W SMT0603 LR

R1326 10KΩ 1% 1/16W SMT0402 LR

R1327 1Ω 1% 1/16W SMT0402 LR

Assume R818=Rin=1K Ohm

R819=Rfb=[N*Rdroop/(DCR*G)-1]*Rin=5.69K ~ 5.11K

Rdroop:Intel spec. -2.1m Ohms

L/DCR=[Rn//RS(eqv)]*Cn

C782+C783=Cn=L/DCR/[Rn//RS(eqv)]=0.285uF

G

G

40mils

300mil

S

C1272

C1207

4.7 uF 25V ± 10 % 12 06 X5R TDK LR

4.7uF 25V ± 10% 1206 X5R TDK LR

2

DS

Q86

IRF R37 09Z 30V 86A TO -252 IR LR

G

Q87

IRFR3707Z 30V 61A TO-252 IR LR

D S

D

S

G

C1208

G

4.7uF 25V ± 10% 1206 X5R TDK LR

2

G

40mils

DS

G

20A, 1000mils

DS

Q88

IRF R37 09Z 30V 86A TO -252 IR LR

1

Boost Voltage 1.2V

Deeper Sleep Voltage 0. 748V

L126 Change to Mag.Layer

20A, 1000mils

PSI

Q98

D61

IRF R37 09Z 30V 86A TO -252 IR LR( NU)

DIODE S TKY SS34A 40V 3A DO-214AC(SMA) 2PIN PSI LR

G

L126

0.36uH ±20% 24A 11.5*10*4 MMD-1004C-R36M MAG.LAYERS LR

C1198

1000pF 50 V 10% 0603 X7R LR(NU)

R1301

SHW 0 5% 1/16 W 0 402

PSI

DS

Q99

D63

IRF R370 9Z 3 0V 8 6A T O-25 2 IR LR( NU)

DIODE S TKY SS34A 40V 3A DO-214AC (SMA) 2PIN P SI LR

R1081

SHW 0 5 % 1/16W 0402

L129

0.36uH ±20% 24A 11.5*10*4 MMD-1004C-R36M MAG.LAYERS LR

C1212

R1315

1000pF 50 V 10% 0603 X7R LR(NU)

SHW 0 5 % 1/16W 0402

Title

VA250W/D < VIA C7 + VN896 + VT8237A >

Size Document Number Rev

Custom

CPU Core Power

Date: Sheet of

C11 95 T2 20uF 2V -35 to +10% 9m Ω SMT 7343 EEF SX0 D221 EY PANA SON IC LR (NU)

C11 94 T22 0uF 2V -35 to + 10% 9mΩ SM T734 3 E EFSX 0D22 1EY PAN ASONIC LR

C11 93 T2 20uF 2V -35 to +10% 9m Ω SMT 7343 EEF SX0 D221 EY PANA SONIC LR

+

+

VCORE_CPU <9,33,36>

+

20A, 1000mils

C12 10 T2 20uF 2V -35 to +10% 9m Ω SMT 7343 EEF SX0 D221 EY PANA SONIC LR

C12 11 T2 20uF 2V -35 to +10% 9m Ω SMT 7343 EEF SX0 D221 EY PANA SON IC LR (NU)

C12 09 T2 20uF 2V -35 to +10% 9m Ω SMT 7343 EEF SX0 D221 EY PANA SONIC LR

R1107

SHW 0 5% 1 /16W 0 402

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

1

+

+

+

10 56Friday, October 20, 2006

0.2

8

www.bufanxiu.com

7

6

5

4

5VDDM<22,24,26,29,32,34,35,36,37,41,42,48,52>

3

2

1

THERMAL SENSOR

G

SMCLK_PMU

SMDAT_PMU

5VDDM

D76 DIODE STKY RB751V-40 40V 200mA SOD-323 2PIN PSI LR

R542

10KΩ 5% 1/16W SMT0402 LR

TRACE 30MIL

16

C117

1uF 10V +80-20% SMT0603 Y5V LMK107F105ZA-T TAIYO LR

3

5

2

6

7

8

9

20MIL

R543

10KΩ 5% 1/16W SMT0402 LR

DXP2

SGND2

Place this TR closed to

VGA Chip.

C1298

30mil

0.1uF 10V 10% SMT0402 X5R LR

L58

SPWR 0 5% 1/16W 0603

SUSCLK

3VDDM<10,12,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

R521

10KΩ 5% 1/16W SMT0402 LR

2.2uF 10V ± 10% SMT0805 X5R C2012X5R 1A225KT TDK LR

U42

1

C701

15

10

14

13

12

11

LNR-IC G796S1U SSOP 16PIN GMT LR

Test

DVCC

THERM#

SCL

SDA

ALERT#

CLK

THERM_SET

GND

4

FAN1

FG1

VCC

DXP1

SGND1

DXP2

SGND2

D D

FAN_ON<24>

3VDDM<10,12,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

3VDDS<21,23,24,25,26,28,30,33,34,36,37,39,45,48>

5VDDM

0.1uF 10V 10% SMT0402 X5R LR(NU)

C C

from OVP &

DCON_HOTDOWN

SUSCLK_SB<24>

SMCLK_PMU<33,50>

SMDAT_PMU<33,50>

C1299

R519

10KΩ 5% 1/16W SMT0402 LR(NU)

HOT_DOWN0

R1419 SHW 0 5% 1/16W 0402

R1420 SHW 0 5% 1/16W 0402

3VDDA<21,23,24,25,26,28,30,33,34,36,37,39,45,48>

R533

1KΩ 5% 1/16W SMT0402 LR

1253

U43

DL-IC NC7SZ126P5X SC-70 5PIN FAIRCHILD LR

R526 22Ω 5% 1/16W SMT0402 LR Sn

4

R516

10KΩ 5% 1/16W SMT0402 LR(NU)

R520

10KΩ 5% 1/16W SMT0402 LR

SCL_TH

SDA_TH

SUSTAT_B0 <33,39,42,45,46,47,48>

SUSCLK

TRANS M-FET-N 2N7002 60V 115mA SOT-23 3PIN PSI LR (NU)

D S

Q103

D S

Q104

TRANS M-FET-N 2N7002 60V 115mA SOT-23 3PIN PSI LR (NU)

PN

C525

2200pF 50V 10% SMT0402 X7R LR

SCL_TH

4.7KΩ 5% 1010 1/16W 4P2R LR (NU)

G

SDA_TH

C526

1000pF 50V 10% SMT0402 X7R LR

R544

100Ω 1% 1/10W SMT0603 LR

C527

0.1uF 16V 80-20% SMT0402 Y5V LR

THERMDA <8>

Trace=10mil and together

THERMDC <8>

RP88

124

2005.2.15

5VDDM <22,24,26,29,32,34,35,36,37,41,42,48,52>

C1296

3

33pF 50V 5% SMT0402 NPO LR(NU)

C1297

33pF 50V 5% SMT0402 NPO LR(NU)

R978SPWR 0 5% 1/16W 0603

L27SPWR 0 5% 1/16W 0603

1

1

CN9

2

2

20-24197-20

3

3

CON ENTERY SMT 3PIN P=1.25 3802-03

1.Far away the CRT,clock generator,memory bus,PCI bus.

2.As close CPU as possible.

10 mil

10 mil

B B

6mil

VDDS0 <33>

Q84

HOT_DOWN0

A A

8

7

6

B

TR NPN DTC144EUAT106 50V 100mA UMT3(SC-70) 3PIN ROHM LR

E C

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

Date: Sheet of

2

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<Thermal / RTC>

1

5VDDM<22,24,26,29,32,34,35,36,37,41,42,48,52>

5VDDM

3VDDS<21,23,24,25,26,28,30,33,34,36,37,39,45,48>

3VDDS

11 56Friday, October 20, 2006

0.2

5

www.bufanxiu.com

3VDDM_CLK

C224

C213

D D

EMI

requst

4/2

0.1uF 16V 80-20% SMT0 603 Y5V LR

0.1uF 16V 80-20% SMT0603 Y5V LR

33pF 50V 5% SMT0402 NPO LR(NU)

ICH_SMBDAT<13,18,19,24>

ICH_SMBCLK<13,18,19,24>

Clock Latout Guideline

CLOCKS

CPU_BCLK[1..0]

HOST

MCH_BCLK[1..0]

Clock

ITP_BCLK[1..0]

CLK66

CLK_ICH66

Clock

CLK_MCH66

C C

CLK_AGP

CLK_ICHPCI

CLK33

CLK_SIOPCI

Clock

CLK_FWHPCI

PCI

CLK_MINIPCI

Clock

CLK_1394PCI

CLK_PMU08PCI

CLK_CBPCI

CLK_SIO14

CLK14

CLK_ICH14

Clock

CLK_TV14

CLK_ICH48

CLK_MCH48

B B

4.5" ~ 9.0 "

MAX : 8.5"

4.5" ~ 9.0 "

3.5" ~ 12.5"

LENGTH

2" ~ 8 "

4.5"~9.0"

2.0"~9.0"

TRACE / SPACE

5 / 20 mils

(5 mil space

between 1 &

0)

5 / 20 mils

5 / 20 mils

5 / 20 mils

5 / 20 mils

5 / 20 mils

1.

Differentials pairs with

the same length

(within 10 mil)

2.CPU & NB trace

mismatch within

20 mil

Length mismatch

within 100 mils

Length same as

CLK66 Clock

Length mismatch

within 100mils

1.Making PCI length with

minimum various

2. Length Require

CLK33-2.5"

3. Length mismatch

+/- 2.0"

1. Length mismatch

+/- 500 mils

DISPCLKI, DISPCLKO

L76

3VDDM

SPWR 0 5% 1/16W 0603

10uF 10V +80-20% SMT0805 Y5V LR

1uF 10V +80-20% SMT0603 Y5V LMK107F105ZA-T TAIYO LR

3VDDM_CLK

C1300

33pF 50V 5% SMT0402 NPO LR(NU)

C1301

R977 4.7KΩ 5% 1/16W SMT0402 LR

3VDDM<10,11,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

CLK_ENB<10>

NOTES

Clock Package Length

Banais Processor Package Length 485 mils

Montara-GM GMCH Package Length 1142 mils

CPU Socket Equivalent Length 157 mils

GND Shielding

GND Shielding

10 mil space

10 mil space

Change to 05-23728-01 libarary 2006.07.25 Modify

3VDDM<10,11,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

R663

10KΩ 1% 1/16W SMT0402 LR

DISPCLKO<16>

A A

5

SSON

ASIC Spread Spectrum for EMI ASM3P2598AF-06-OR TSOT-23 6PIN ALSC LR

4

>60mil

C720

1

2

0.01uF 16V 10% SMT0402 X7R LR

C214

4.7KΩ 5% 1010 1/16W 4P2R LR(NU)

BIOS not

ready

R1067

R1068

Q82

B

TR NPN DTC144EUAT106 50V 100mA UMT3(SC-70) 3PIN ROHM LR

E C

FREQ XTL 14.318180MHz HC-49/U-S SMD 2PIN 18pF ±30ppm NXE14.31818AC18F NSK LR

FS4

0 0

0

0

0

0 0

0

0 1

0

0

0

0

0

0

0

U75

6

VSS

SSON

5

NC

ModOUT

43

VDDCLKIN

0.1uF 16V 80-20% SMT0402 Y5V LR

4

0.01uF 16V 10% SMT0402 X7R LR

C216

475Ω 1% 1/10W SMT0603 LR

5 mil space

5 mil space

5 mil space

0.01uF 16V 10% SMT0402 X7R LR

C223

C215

C217

0.01uF 16V 10% SMT0402 X7R LR

3VDDM<10,11,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

4

3

RP83

1

2

SHW 0 5% 1/16W 0402

SDAT

SCLK

SHW 0 5% 1/16W 0402

VTTPWRGD

R201

FS2 AGP

IREF

Y4

X1_CLK

C724

10pF 50V ±0. 5pF SMT0402 NPO LR

0

0

0

0

1

1

1

3VDDM<10,11,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

CPU

266.00M

0

0

1

133.00M

0

200.00M

1

1

166.67M

333.33M

0 14.318M

0

100.00M

1

0

0

1

400.00M

1

200.00M1

1

R651

22Ω 1% 1/16W SMT0402 LR

C694

3

U61

X1_CLK

6

X1

X2_CLK

7

X2

1

VDDA

3

VDDREF

10

VDDPCI1

16

VDDPCI2

PCI6

20

TURBO/PCI6

22

VDD48

26

VDD3V66

39

VDDPCIEX_1

45

VDDPCIEX_2

49

FS0

FS1

FS2

FS3

PCI33_2

PCI33_3

PCI33_4

PCI33_5

X2_CLK

C723

10pF 50V ±0. 5pF SMT0402 NPO LR

DISPCLKI <16>

VDDCPU

4

FS0/REF0

5

FS1/REF1

11

FS2/PCI0

12

FS3/PCI1

13

PCI2/TB_EN

14

PCI3

17

PCI4

18

PCI5

MODE

23

48MHz/Mode0

SEL_48M

24

SEL24_48#/24_48MHz

SCLK

31

SCLK

SDAT

48

SDATA

VTTPWRGD

9

VTTPWGD/PD

21

RESET

IREF

55

IREF

Clock Layout :

1. Close to Clock generator

2. Trace as short as possible and use 12 mil

3. Place crystal within 500 mils of CLK Generator

PCIFS0FS3

33.33M

66.67M

33.33M

66.67M

66.67M 14.318M

33.33M

66.67M

33.33M

66.67M0

33.33M

33.33M

66.67M

66.67M

33.33M

33.33M

66.67M

CPUT0

CPUC0

CPUT1

CPUC1

CPUT2/PCIEXT0

CPUC2/PCIEXC0

PCIEXT1

PCIEXC1

33Ω 5% SMT1010 1/16W 4P2R RS2N-33R0-J2N CYNTEC LR

PCIEXT2

PCIEXC2

PCIEXT3

PCIEXC3

PCIEXT4/PEREQ1

PCIEXC4/PEREQ2

PCIEXT5/CPU_Stop

PCIEXC5/PCIEX_Stop

3V66_0

FS4/3V66_1

ITP_EN/3V66_2

GND

GNDREF

GNDPCI1

GNDPCI2

GND48

GND3V66

GNDPCIEX_1

GNDPCI EX_2

GNDCPU

GND

40

52

56

ASIC CLOCK-G/Buffers ICS953009AFLF-T SSOP 56PIN ICS LR

REFFS1

14.318M

14.318M

14.318M

14.318M

14.318M

14.318M

3

CPUT0

54

CPUC0

53

CPUT1

51

CPUC1

50

49.9Ω 1% 1/16W SMT0402 LR

47

46

44

43

42

41

38

37

36

35

CPUSTP0_I

34

PCISTP0_I

33

CLK66M0

29

FS4

28

CLK66_2

27

2

8

15

19

25

30

32

R982

R984

49.9Ω 1% 1/16W SMT0402 LR

RP45

124

3

DIODE STKY RB751V-40 40V 200mA SOD-323 2PIN PSI LR

CPUSTP0_I

PCISTP0_I

DIODE STKY RB751V-40 40V 200mA SOD-323 2PIN PSI LR

H_BSEL0<8>

H_BSEL1<8>

For Yonah selection. (533 or 667)

H_BSEL2<8>

For C7 selection. (533 or 400)

Q118

TRANS NPN MMBT2222A 40V 600mA SOT-23 3PIN PSI LR

For (C7 800)

Q105

TRANS NPN MMBT2222A 40V 600mA SOT-23 3PIN PSI LR

Q117

TRANS NPN MMBT2222A 40V 600mA SOT-23 3PIN PSI LR

FS1

FS0

MODE

PEXCLKP_NB <17>

PEXCLKN_NB <17>

CLK66_2

CLK66_2

FS2

FS3

PCI33_2

PCI33_3

PCI33_4

PCI33_5

CPUT1

CPUC1

33Ω 5% SMT1010 1/16W 4P2R RS2N-33R0-J2N CYNTEC LR

CPUT0

CPUC0

33Ω 5% SMT1010 1/16W 4P2R RS2N-33R0-J2N CYNTEC LR

10KΩ 5% 1/16W SMT0402 LR

R1427

R1428

10KΩ 5% 1/16W SMT0402 LR

P N

P N

3VDDM<10,11,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

VCCP <8,9,14,17,25,26,38,46>

R219

10KΩ 5% 1/16W SMT0402 LR

R1414

10KΩ 5% 1/16W SMT0402 LR

B

10KΩ 5% 1/16W SMT0402 LR

R1409

E C

(This bit can float)

3VDDM<10,11,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

VCCP <8,9,14,17,25,26,38,46>

R220

10KΩ 5% 1/16W SMT0402 LR

R1408

10KΩ 5% 1/16W SMT0402 LR

B

10KΩ 5% 1/16W SMT0402 LR

R221

E C

3VDDM<10,11,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

VCCP <8,9,14,17,25,26,38,46>

R1413

10KΩ 5% 1/16W SMT0402 LR

R1412

10KΩ 5% 1/16W SMT0402 LR

B

10KΩ 5% 1/16W SMT0402 LR

R217

E C

(This bit can float)

2

Damping resistor

close to IC.

R980 33Ω 1% 1/16W SMT0402 LR

R981 33Ω 1% 1/16W SMT0402 LR

R983 33Ω 1% 1/16W SMT0402 LR

R986 22Ω 5% 1/16W SMT0402 LR Sn

R987 22Ω 5% 1/16W SMT0402 LR Sn

R988 33Ω 1% 1/16W SMT0402 LR

R990 33Ω 1% 1/16W SMT0402 LR

R992 33Ω 1% 1/16W SMT0402 LR(NU)

R993 33Ω 1% 1/16W SMT0402 LR

R994 33Ω 1% 1/16W SMT0402 LR

R1020 33Ω 5% 1/16W SMT0402 LR Sn

RP49

124

3

RP50

124

3

SEL_48M

D80

D81

Under

500mil

Under

200mil

R692

10KΩ 5% 1/16W SMT0402 LR

3VDDM

CPUSTP0 <24>

PCISTP0 <24>

FSBSEL0 <37>

FSO0

FSBSEL1 <37>

FSO1

(Can't be floating)

FSBSEL2 <37>

FSO2

2

1

FSO1

CLK14M_SB <24>

FSO0

CLK14M_GUI <16>

CLK48M_SB <23>

CLK66M_NB <17>

CLK66M_SB <25>

FSO2

CLK33M_SB <25>

FSO3

CLK33M_EC <33>

CLK33M_APIC <25>

CLK33M_KBC <34 >

Under

R995 49.9Ω 1% 1/16W SMT0402 LR

500mil

R996 49.9Ω 1% 1/16W SMT0402 LR

R997 49.9Ω 1% 1/16W SMT0402 LR

R998 49.9Ω 1% 1/16W SMT0402 LR

Under

500mil

GND Shielding

GND Shielding

CPU_BCLK <8>

CPU_BCLK0 <8>

HCLKNB <14>

HCLKNB0 <14>

HCLK+

HCLK-

CLK33M_FWH <38>

CLK33M_MINI <29>

20 mil space

5 mil space

20 mil space

(5 mil width for differential signals and GND shiekding)

CLK14M_SB

C732 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK14M_GUI

C729 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK48M_SB

C230 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK66M_NB

C697 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK66M_SB

C698 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK33M_SB

C241 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK33M_EC

C239 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK33M_APIC

C237 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR (NU)

CLK33M_KBC

C235 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK33M_FWH

C234 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CLK33M_MINI

C231 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CPU_BCLK

C709 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

CPU_BCLK0

C704 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

HCLKNB

C707 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

HCLKNB0

C708 5pF 50V ± 0.5pF -55 TO +125C SMT0402 NPO LR

MODE

FSO3

FS4

Default 533

Only FS1 no 120K inernal pull down

R1409,R221,R217, R214,R1410,

(R742,R1411) should be very,

very close to their lines.

Q118,Q105,Q117 needn't.

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet of

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<Clock-Gen>

1

5 mil space

5 mil space

5 mil space

5 mil space

3VDDM

12 56Friday, October 20, 2006

3VDDM

3VDDM<10,11,16,17,18,19,20,21,22,23,24,25,26,29,36,37,38,41,42,45,46,48,52>

R215 10KΩ 5% 1/16W SMT0402 LR

R214 10KΩ 5% 1/16W SMT0402 LR(NU)

R742 10KΩ 5% 1/16W SMT0402 LR(NU)

R1410 10KΩ 5% 1/16W SMT0402 LR(NU)

R1411 10KΩ 5% 1/16W SMT0402 LR(NU)

0.2

10

www.bufanxiu.com

INPUT

H H

G G

FB_OUT

FB_IN

DDRCLK0

DDRCLK0#

DDRCLK1

DDRCLK1#

DDRCLK2

DDRCLK2#

L2: 6"

22

歐姆

0

歐姆

C_open

0

歐姆

DDRCLK3

DDRCLK3#

DDRCLK4

DDRCLK4#

DDRCLK5

DDRCLK5#

F F

C_open

DDR Clock Buffer

FWDSDCLKOU

L4: 12.6"

L4:L2+L3-L1+5.6"

10PF

9

22

10PF

L1=LMD1+LMD2

歐姆

L3: 4"

L3: 4"

8

VIA

VN800

DIMM1 DIMM2

0.1uF 16V 80-20% SMT0402 Y5V LR

ICH_SMBDAT<12,18,19,24>

ICH_SMBCLK<12,18,19,24>

DCLKO+<15>

DCLKO-<15>

7

2.5VDDM<8,20,23,24,25,26,36,45>

C254

Close to clock buffer

C248

0.1uF 16V 80-20% SMT0402 Y5V LR

R1400

100Ω 1% 1/16W SMT0402 LR

6

1.8VDDM_CLK

U37

21

VDD2.5/1.8

27

VDD2.5/1.8

10

VDD2.5/1.8

26

AVDD25

1

AVDD25

16

SDATA

15

SCLK

3

BUF_INT

4

BUF_INC

9

GND

22

GND

28

GND

25

AGND

2

AGND

ASIC CLOCK-BUFFER ICS9P936AFLF-T SSOP 28PIN ICS LR

FBOUT_T

FBOUT_C

5

DDR CLOCK BUFFER

EMI solution 2006.0627

DDRT0

RP51 22Ω 5% SMT1010 1/16W 4P2R RS2N-22R0-J2N CYNTEC LR

DDRT0

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

DDRT4

DDRC4

DDRT5

DDRC5

5

6

7

8

13

14

18

17

20

19

24

23

11

12

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

3/30 modify

GGT request

3

124

RP52 22Ω 5% SMT1010 1/16W 4P2R RS2N-22R0-J2N CYNTEC LR

3

124

RP53 22Ω 5% SMT1010 1/16W 4P2R RS2N-22R0-J2N CYNTEC LR

3

124

RP54 22Ω 5% SMT1010 1/16W 4P2R RS2N-22R0-J2N CYNTEC LR

124

3

R508

22Ω 1% 1/16W SMT0402 LR

4

DCLKI <15>

C500

10pF 50V 5% SMT0402 NPO LR

3

C496 10pF 50V ±0.5pF SMT0402 NPO LR

C497 10pF 50V ±0.5pF SMT0402 NPO LR

C498 10pF 50V ±0.5pF SMT0402 NPO LR

C499 10pF 50V ±0.5pF SMT0402 NPO LR

2

C440 10pF 50V ±0.5pF SMT0402 NPO LR

C501 10pF 50V ±0.5pF SMT0402 NPO LR

C441 10pF 50V ±0.5pF SMT0402 NPO LR

C502 10pF 50V ±0.5pF SMT0402 NPO LR

1

M_CLK_DDR0 <19>

M_CLK_DDR00 <19>

M_CLK_DDR1 <19>

M_CLK_DDR10 <19>

M_CLK_DDR2 <18>

M_CLK_DDR20 <18>

M_CLK_DDR3 <18>

M_CLK_DDR30 <18>

EMI solution 2006.0627

E E

1.8VDDM<45>

D D

C510

L57

SPWR 0 5% 1/16W 0603

1.8VDDM_CLK

Mount these capacitor 2006.0602 Modify

>40 mil

C97

C504

+

C C

0.1uF 16V 80-20% SMT0402 Y5V LR

B B

T10uF 10V ± 20% SMT3216 ESR=4.0Ω T491A106M010AT KEMET LR

A A

10

9

8

C99

C108

0.1uF 16V 80-20% SMT0603 Y5V LR

0.1uF 16V 80-20% SMT0603 Y5V LR

0.1uF 16V 80-20% SMT0603 Y5V LR

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

7

6

5

4

3

Date: Sheet of

(886-2)8751-8751

VA250W/D < VIA C7 + VN896 + VT8237A >

<clock buffer>

2

13 56Friday, October 20, 2006

0.2

1

10

www.bufanxiu.com

H H

G G

F F

E E

D D

C C

9

AGTL+_HA0[31..3]<8>

AGTL+_HREQ0[4..0]<8>

AGTL+_HD0[63..0]<8>

8

AGTL+_ADSTB00<8>

AGTL+_ADSTB10<8>

AGTL+_ADS0<8>

AGTL+_BNR0<8>

AGTL+_BPRI0<8>

AGTL+_BR00<8>

AGTL+_DBSY0<8>

AGTL+_DEFER0<8>

AGTL+_DRDY0<8>

AGTL+_HIT0<8>

AGTL+_HITM0<8>

AGTL+_LOCK0<8>

AGTL+_TRDY0<8>

AGTL+_HREQ0[4..0]<8>

AGTL+_RS0[2..0]<8>

AGTL+_DINV00<8>

AGTL+_DINV10<8>

AGTL+_DINV20<8>

AGTL+_DINV30<8>

AGTL+_CPURST0<8>

HCLKNB<12>

HCLKNB0<12>

GTLVREF_NB

R1026 180Ω 1% 1/10W SMT0603 LR

VCCP<8,9,12,17,25,26,38,46>

R1027 360Ω 1% 1/10W SMT0603 LR

AGTL+_HA03

AGTL+_HA04

AGTL+_HA05

AGTL+_HA06

AGTL+_HA07

AGTL+_HA08

AGTL+_HA09

AGTL+_HA010

AGTL+_HA011

AGTL+_HA012

AGTL+_HA013

AGTL+_HA014

AGTL+_HA015

AGTL+_HA016

AGTL+_HA017

AGTL+_HA018

AGTL+_HA019

AGTL+_HA020

AGTL+_HA021

AGTL+_HA022

AGTL+_HA023

AGTL+_HA024

AGTL+_HA025

AGTL+_HA026

AGTL+_HA027

AGTL+_HA028

AGTL+_HA029

AGTL+_HA030

AGTL+_HA031

AGTL+_HREQ00

AGTL+_HREQ01

AGTL+_HREQ02

AGTL+_HREQ03

AGTL+_HREQ04

AGTL+_RS00

AGTL+_RS01

AGTL+_RS02

7

A17

A18

A19

A20

A21

U65A

M33

HA03#

N34

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

HA04#

R33

HA05#

T33

HA06#

R34

HA07#

P36

HA08#

P34

HA09#

N35

HA10#

R36

HA11#

U36

HA12#

U34

HA13#

U35

HA14#

T30

HA15#

U32

HA16#

W35

HA17#

V32

HA18#

V36

HA19#

V34

HA20#

W36

HA21#

W34

HA22#

AA36

HA23#

V33

HA24#

AA34

HA25#

Y35

HA26#

Y33

HA27#

AA32

HA28#

W32

HA29#

V31

HA30#

W31

HA31#

Y31

HA32#

Y31, AB31 no pad on VN896

AB31

HA33#

R35

HADSTB0P#

W33

HADSTB1#

L35

ADS#

K35

BNR#

J32

BPRI#

M34

BREQ0#

K32

DBSY#

J33

DEFER#

K33

DRDY#

L36

HIT#

L34

HITM#

J34

HLOCK#

M35

HTRDY#

T32

HREQ0#

T31

HREQ1#

R32

HREQ2#

M32

HREQ3#

M31

HREQ4#

J35

RS0#

N36

RS1#

J36

RS2#

C31

HDBI0#

E35

HDBI1#

G27

HDBI2#

D22

HDBI3#

F22

CPURST#

AC29

HCLK+

AC30

HCLK-

U30

GTLVREF0

J25

GTLVREF1

G22

GTLCOMPP

H22

GTLCOMPN

ASIC NB VN896 HSBGA 951PIN VER:CD VIA LR

GND

GND

GND

GND

GND

GND

A1A2A8

A10

A22

A3

VCCP<8,9,12,17,25,26,38,46>

B17

B18

B19

VTT_6

VTT_7

GND

GND

A25

A27

A29

B20

B21

C17

C18

C19

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

GND

GND

GND

GND

GND

GND

A31

A33

A35B2B3B4B36C2C3C4C5E6C26

6

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21