5

hexainf@hotmail.com

GRATIS - FOR FREE

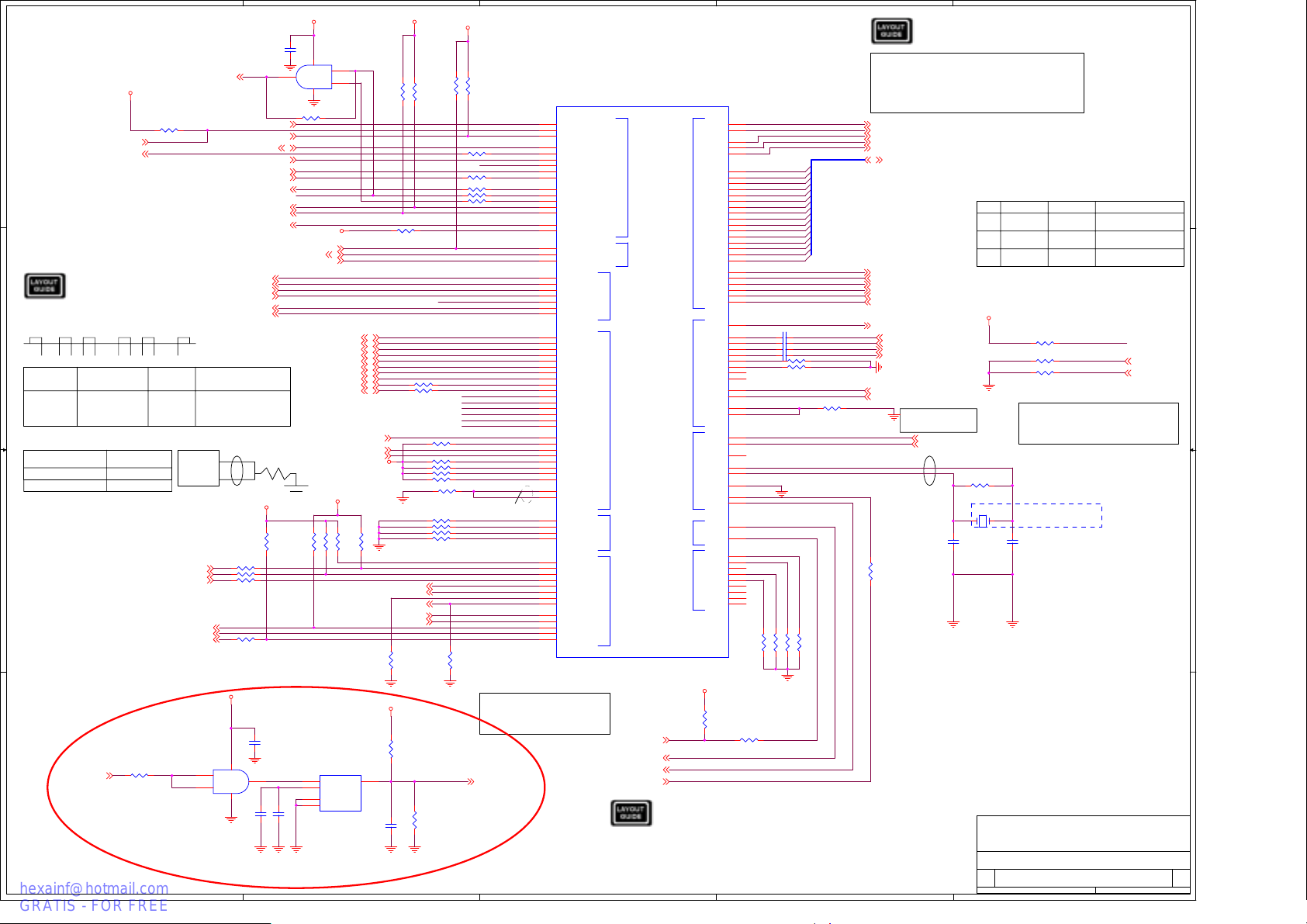

FIC PS1 (MD34)

Rev: 0.2

4

3

2

1

First International Computer,Inc

D D

Protable Computer Group HW Department

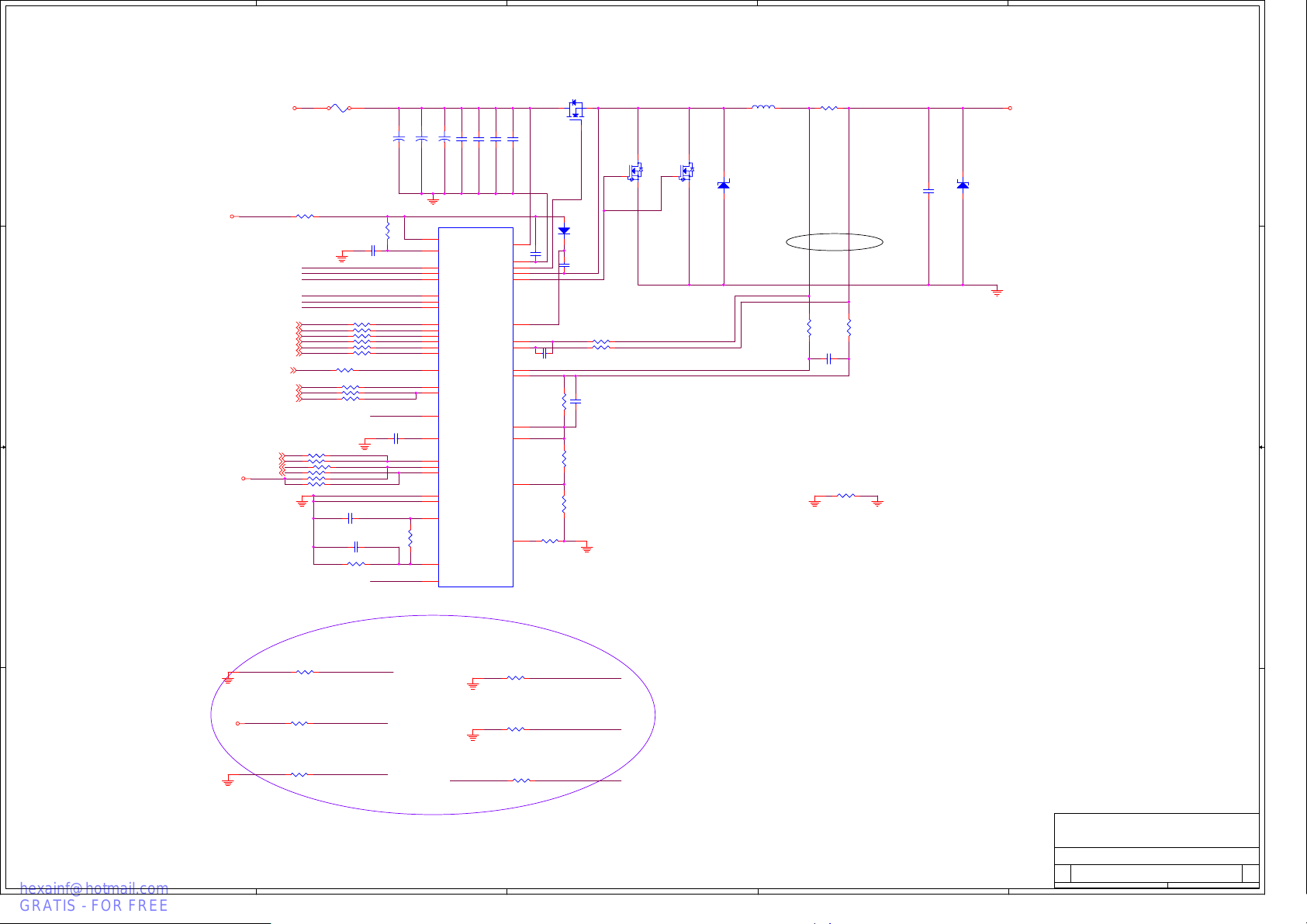

Board name : Mother Board Schematic

Project : PS1(MD34)

C C

Version : 0.2

1. Schematic Page Description :

2. PCI & IRQ & DMA Description :

3. Block Diagram :

4. Net name Description :

Initial Date : August 20 , 2003

5. Board Stack up Description :

6. Schematic modify Item and History :

7. power on & off & S3 Sequence :

8. Layout Guideline :

9. switch setting

B B

10. Original Source

Manager Sign by : Eric Yang

Drawing by : Joyce Chiu & Winky Hsu

All of Check by : Tin Tang

LAN Circuit check by : Spruce Wu

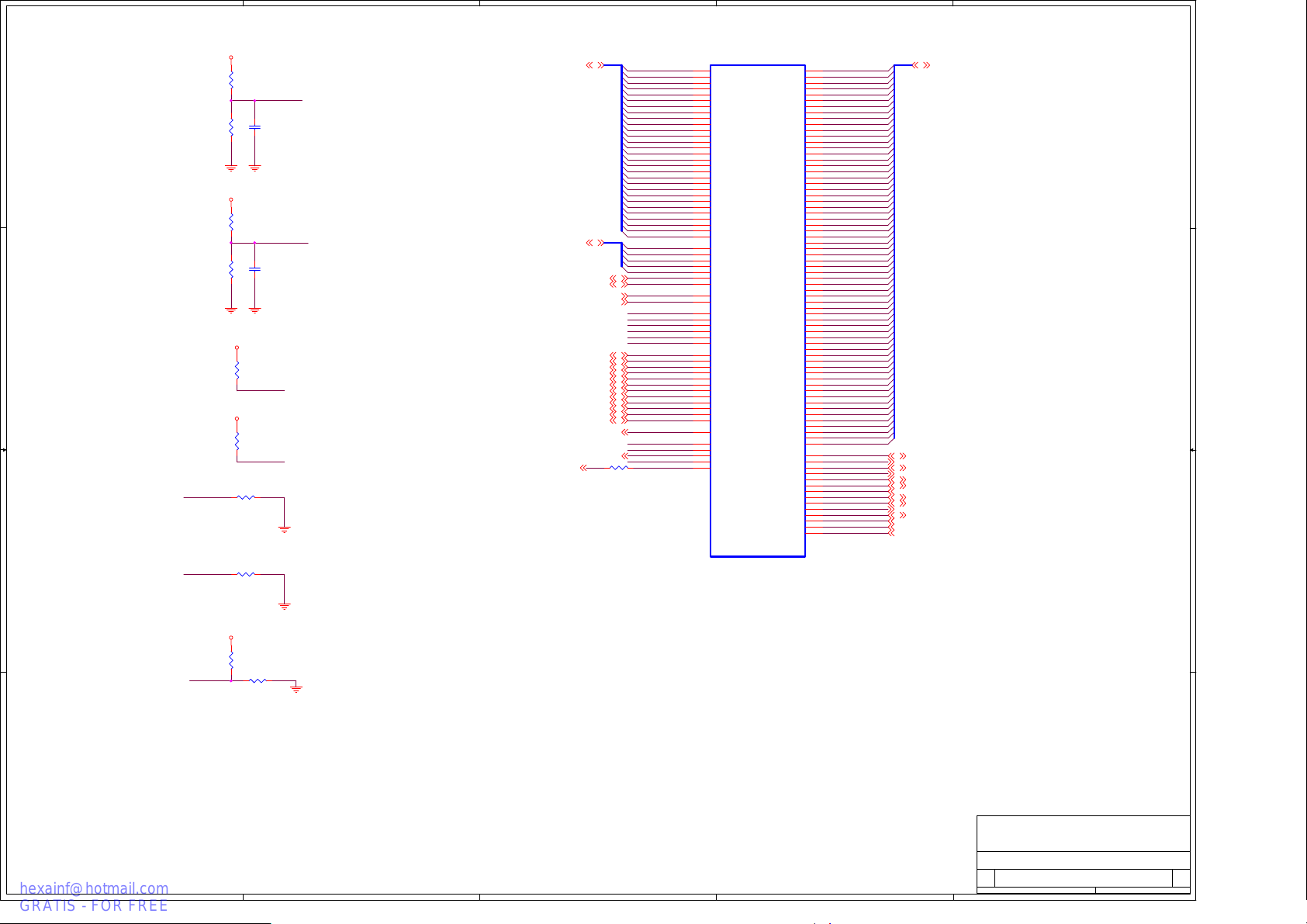

A A

Audio Circuit check by : Jimmys Ho

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

Total confirm by : Intel INc.

5

4

3

2

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

Title

Date: Sheet

1

164Friday, May 07, 2004

of

0.2

8

hexainf@hotmail.com

GRATIS - FOR FREE

7

6

5

4

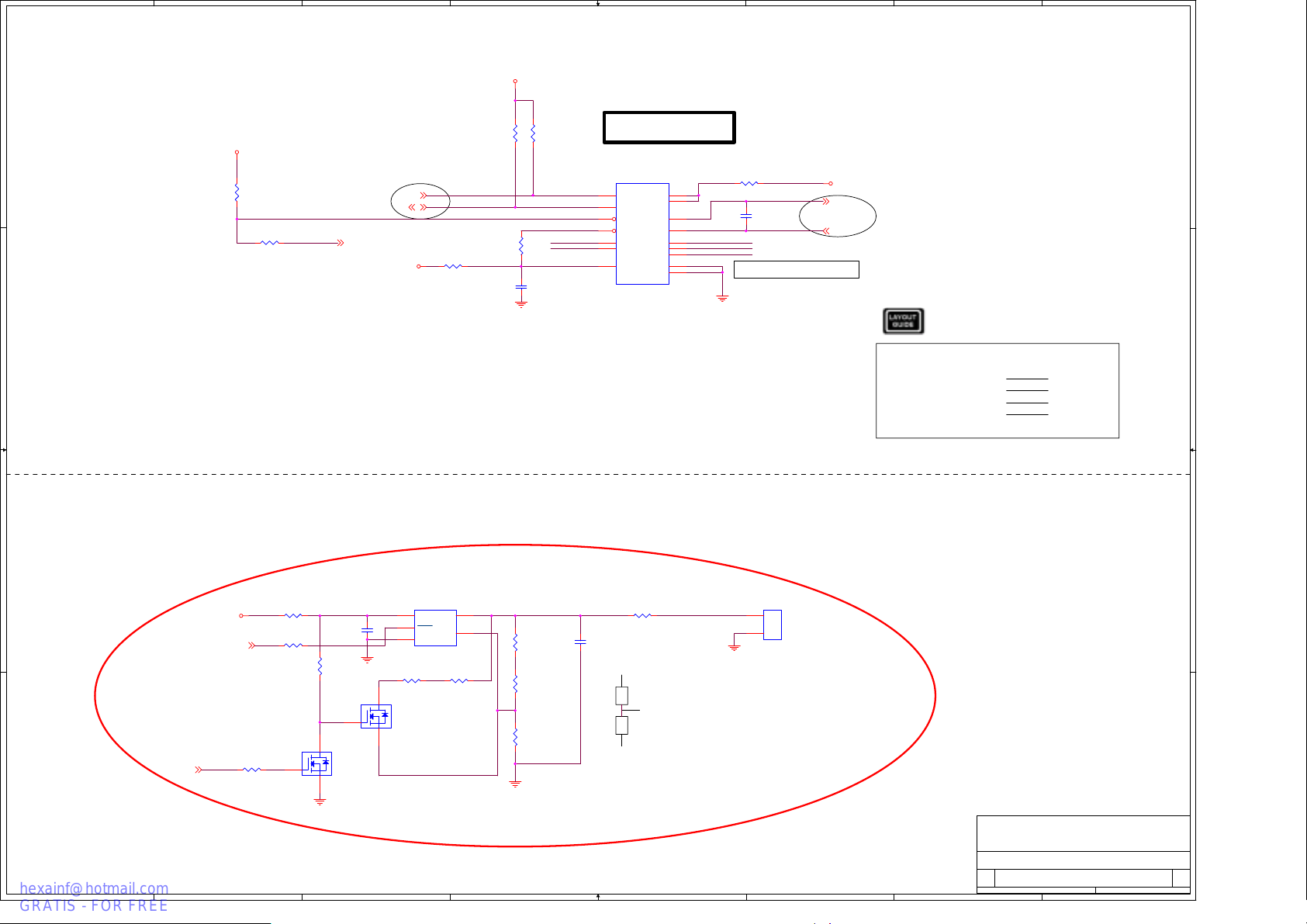

1. Schematic Page Description :

3

2

1

D D

1. Title

2. Schematic Page Description

3. Block Diagram

4. ANNOTATIONS

5. Schematic Modify

6. Timing Diagram

7. CPU Layout Guideline

8. DDR & CLK GEN Layout Guideline

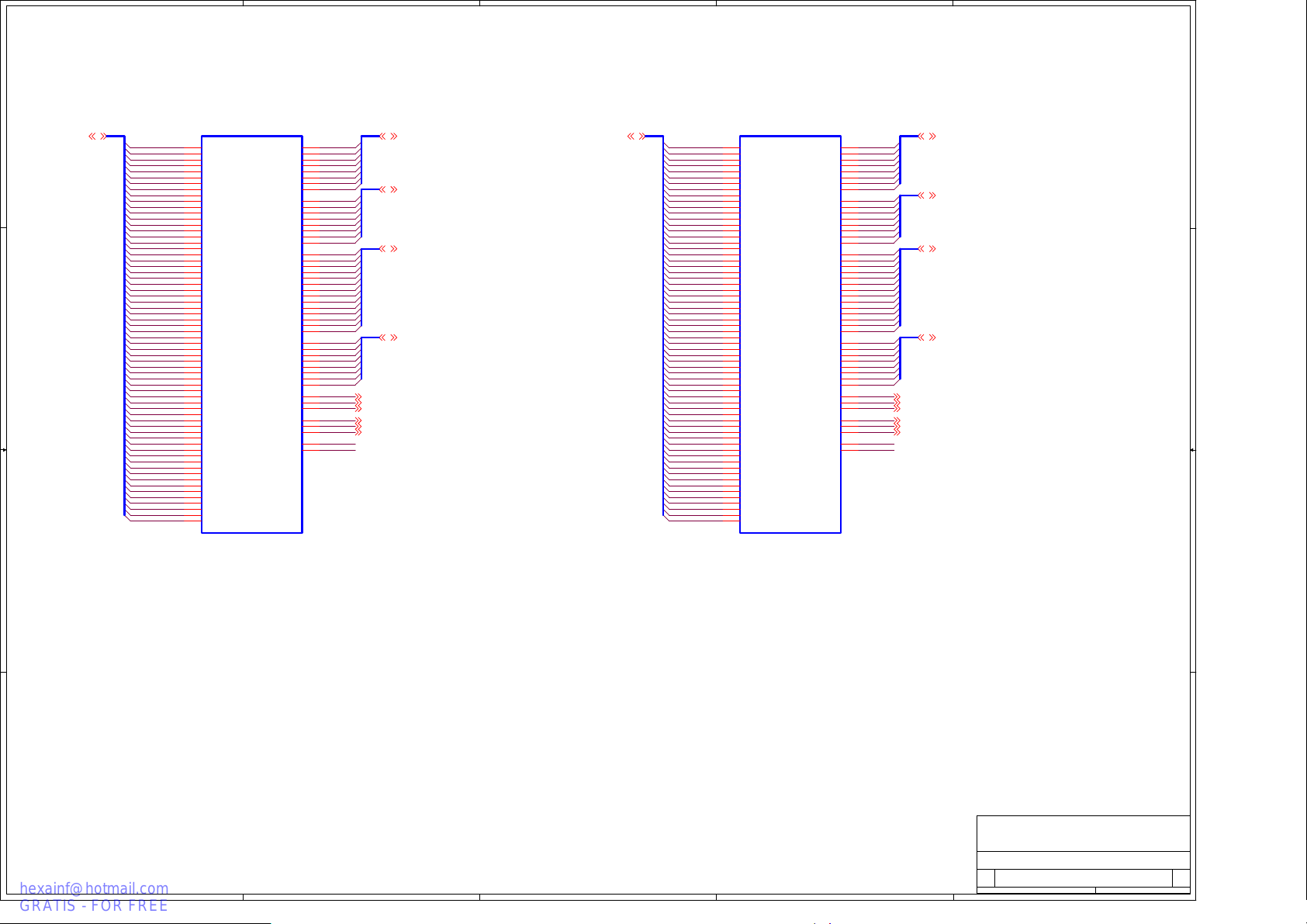

9. mFcPGA Dothan (1/2)

10. mFcPGA Dothan (2/2)

11. POWER (CPU CORE)

12. Thermal / FAN CNN

C C

13. ALVISO (1/6)(LVDS/PCI/VGA/TV)

14. ALVISO (2/6)(DMI/CLK/PM)

15. ALVISO (3/6)(DDR II)

16. ALVISO (4/6)(HOST)

17. ALVISO (5/6)(POWER)

18. ALVISO (6/6)(VSS/NCTF)

19. ICH6-M (1/4)(PCI/CPU/IRQ/LAN)

20. ICH6-M (2/4)(IDE/AC97/USB2/PMU/GPIO)

2. PCI & IRQ & DMA Description :

B B

IDSEL

AD17

AD23 CardBus (TI 4510)

AD24 LAN 82562EZ

IRQA

IRQB

IRQC

IRQD

BUSMASTER

A A

REQ

REQ0 / GNT0

REQ1 / GNT1

REQ2 / GNT2

CHIP

Mini PCI(Wireless LAN)

CHIPPCIINT

MiniPCI/CardBus

MiniPCI/CardBus

VGA/LAN

ICH6-M Embeded USB2.0

CHIP

MiniPCI

CardBus

Mini PCI(Wireless LAN)

LAN(82562EZ)REQ4 / GNT4

8

7

21. ICH6-M (3/4)(POWER)

22. ICH6-M (4/4)(GROUND)

23. Clock Generator

24. DDR SO-DIMM1

25. DDR SO-DIMM2

26. TI 4510(CARDBUS)

27. TI 4510(IEE1394)

28. CARDBUS POWER SW./CNN

29. CRT Port / TV OUT

30. LED /RJ 11/ITP PORT

31. LCD CNN

32. LPC PMU08

33. MDC CNN/CD-L/R

34. INTER /MAIL SW/PCBEEP

35. RTC / Main SW / SMBUS

36. HDD / CD-ROM CNN

37. Calexico MINI PCI

38. USB CNN

39. Firm Ware Hub (FWH)

40. LPC KBC M3885X

IRQ0

IRQ1

IRQ2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8

IRQ9

IRQ10

IRQ11

IRQ12

IRQ13

IRQ14

IRQ15

6

System timer

Keyboard

(Casacde)

LAN / MODEM

Serial Port

AUDIO / VGA / USB

FLOPPY DISK

LPT

RTC

ACPI

MODEM/LAN

Cardbus

PS/2 mouse

FPU

HDD

CDROM

5

41. PCI / LPC Pull Up/Down

42. DIP/LID SW; SCREW

43. Reset Circuit

44. DUAL_LAN_82562EZ

45. Over Voltage Protect

46. Power (DDR 1.8VDDS/ 0.9VDDM/1.5VDDM)

47. Power (1.5VDDA/VDDS/1.8VDDM/2.5VDDM)

48. ADIN&DCIN

49. MAIN BATTERY CNN

50. Battery Select

51. Charge Circuit

52. Battery Voltage Sense

53. Power (PMU3V/5V)

54. Power (3VDDS/5VDDS/3VDDM/5VDDM)

55. Power (VCCP/VCORE_GMCH)

56. Power (LAN1.0VDDM)

57. Power (3VDDA/5VDDA)

58. AC97 CODEC (ALC655)

59. AUDIO AMP / SPEAKER

60. HEADPHONE & SPDIF

DMA Channel

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

4

3

DeviceIRQ Channel Desciption

MODEM / LAN

ECP

FLOPPY DISK

AUDIO

(Cascade)

Unused

Unused

Unused

61. MICIN

62. ICSI_IC1210

63. CARD CONN

64. SATA TO PATA Bridge

65. POWER TIMING

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

Schematic Page & PCI & IRQ & DMA Description

Date: Sheet

2

264Friday, May 07, 2004

of

1

0.2

8

hexainf@hotmail.com

GRATIS - FOR FREE

FIC PS1 (MD34)

Rev: 0.2

7

6

5

4

3

2

1

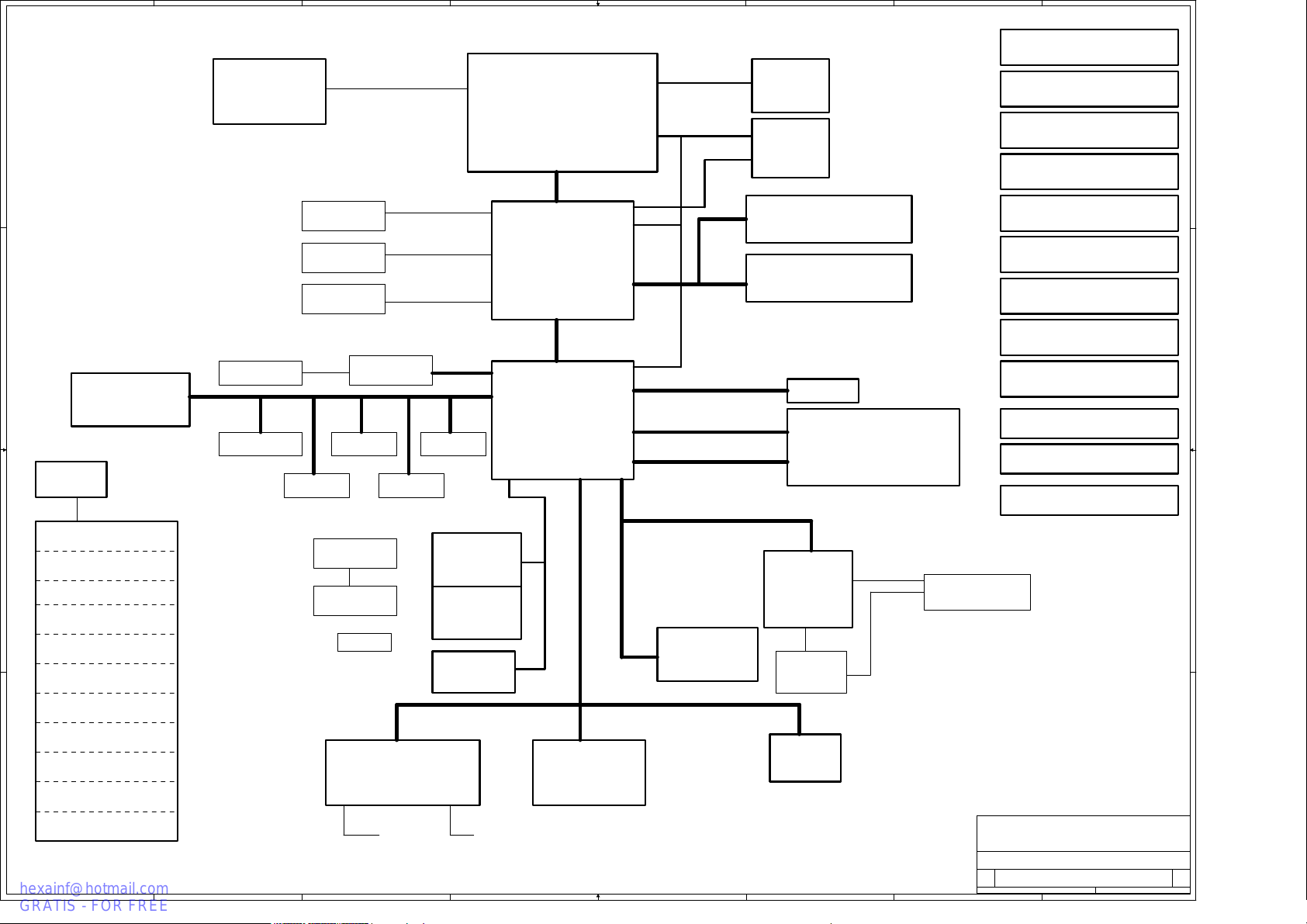

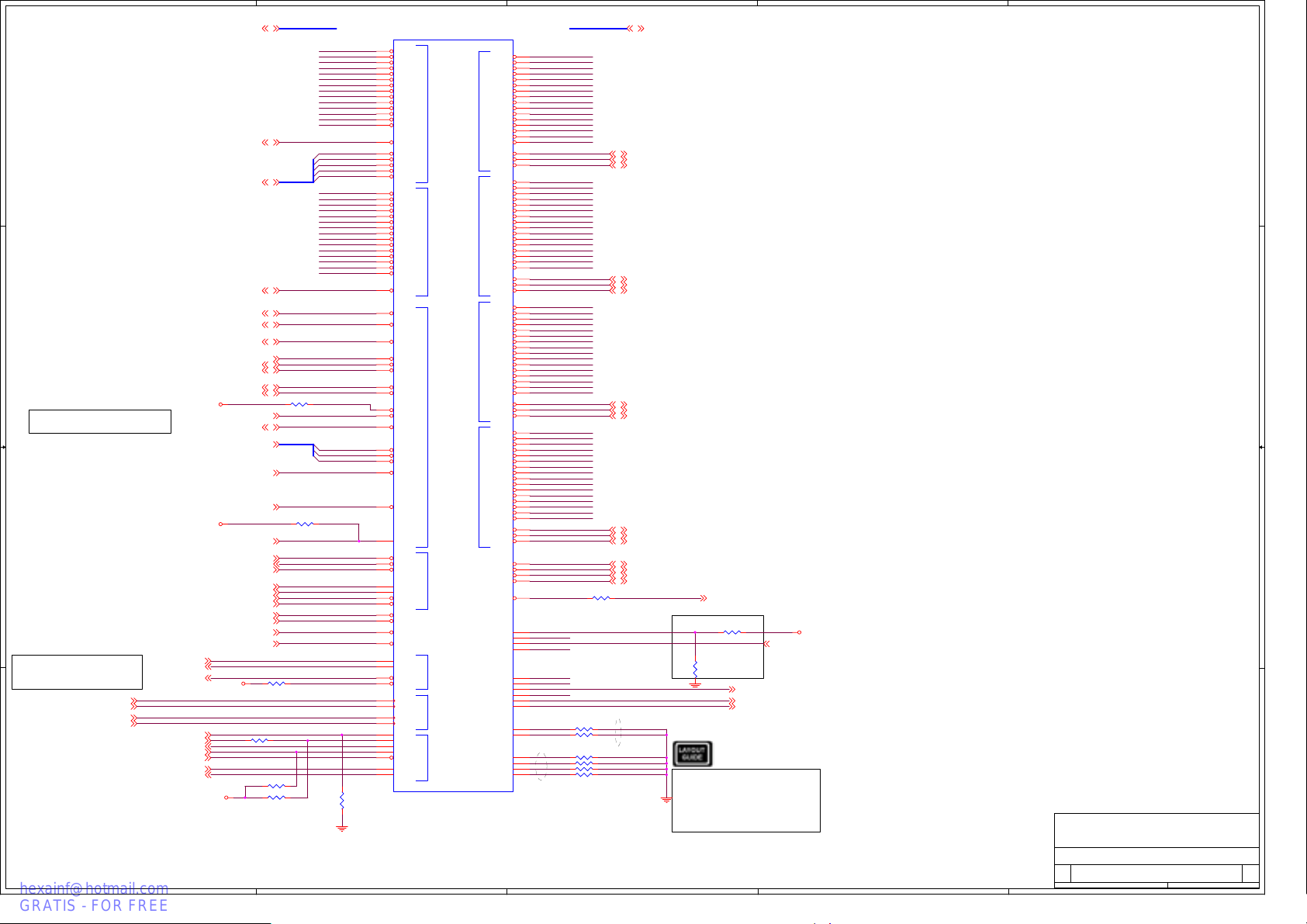

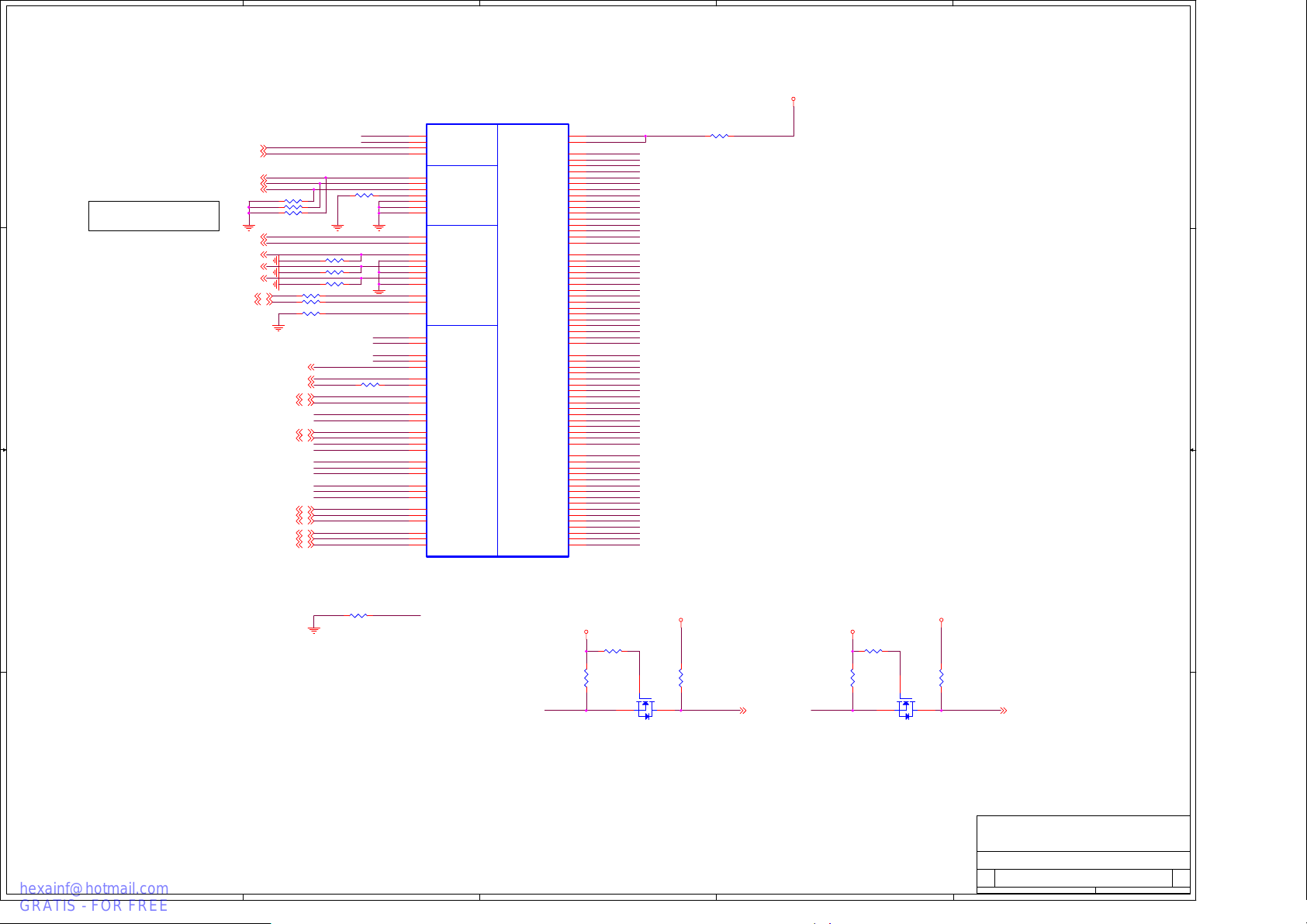

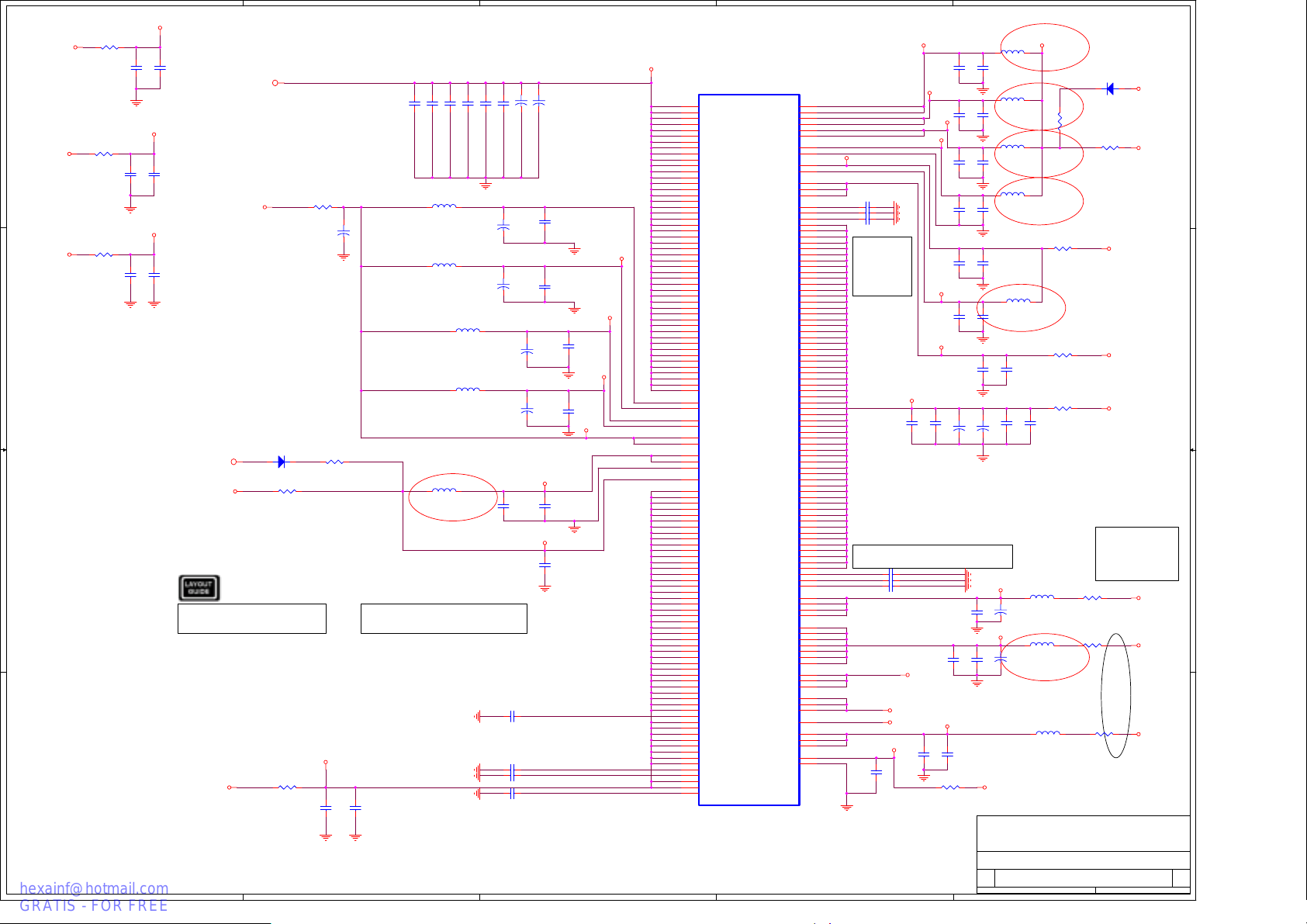

3. Block Diagram :

Thermal

Sensor

GMT767

D D

P12

Intel

Dothan/Yonah

Processor

P9,10

Host Bus

CRT

TV Port

LCD

C C

HDD

ICSI IC1210

P36

Card Reader

USB5

ACIN

P48

PMU3V/5V

B B

3VDDA/5VDDA

3VDDS/5VDDS

3VDDM/5VDDM

2.5VDDM

1.5VDDA/DDS

1.8VDDM

1.5VDDM

DDR_1.8VDDS

A A

DDR_0.9VDDM

LAN_1V

8

P53

P57

P54

P54

P47

P47

P47

P56

P46

P46

P56

P62

USB4

RESERVE

7

USB2

P37

USB1

USB3

P29

P29

P31

SATA to PATA

I/F Bridge

USB 2.0

USB0

USB2

P38

P38

AUDIO AMP

HEADPHONE

Mic IN

P59

P60

P61

K/B CTRL

LPC M3885X

6

SATA BUS

P64

USB0

USB1

USB1

P38

Dual Layout

MDC CNN

USB0

P38

AZALIA

CODEC

AC'97

CODEC

ALC655

GPINT K/B

ALVISO

GMCH

1257

uFCBGA

P13,14,15,16,17,18

DMI Interface

ICH6-M

609 BGA

P19,20,21,22

AC-Link

P58

P58

P33

FLASH ROM

( F/W Hub)

4Mb/8Mb

5

Mem Bus

IDE BUS

PCI_E

LCI

32Bit PCI BUS

Mini PCI

Calexico2

LPC BUS

P39P40

4

CPU

CORE

P11

VCCP

CPU

VCRE

GMCH

P55

DDRII

DIMM1(Socket)

400MHZ/533MHZ

DDRII

DIMM0(Socket)

400MHZ/533MHZ

CDROM

P36

INTEL

DUAL LAN

82562EZ(10/100)/

82570(Giga)

Dual Layout

PCMCIA

TI 4510

(1394)

P26,27

P37

TPS 2211

P28

LPC

PMU08

P32

3

P24

P25

P44

PCMCIA SLOT0

CLK CY28411

PCI/LPC Pull up/Down

LID/DIP SW

MAIN SW CNN

Over Voltage

Protect

Battery

charger

BAT CON

Battery Select

Battery Voltage

sense

FAN CNN

RTC

RESET

P28

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

BLOCK DIAGRAM

Date: Sheet

2

364Friday, May 07, 2004

of

1

P23

P41

P42

P35

P45

P51

P49

P50

P52

P12

P35

P43

0.2

8

hexainf@hotmail.com

GRATIS - FOR FREE

7

6

5

4

3

2

1

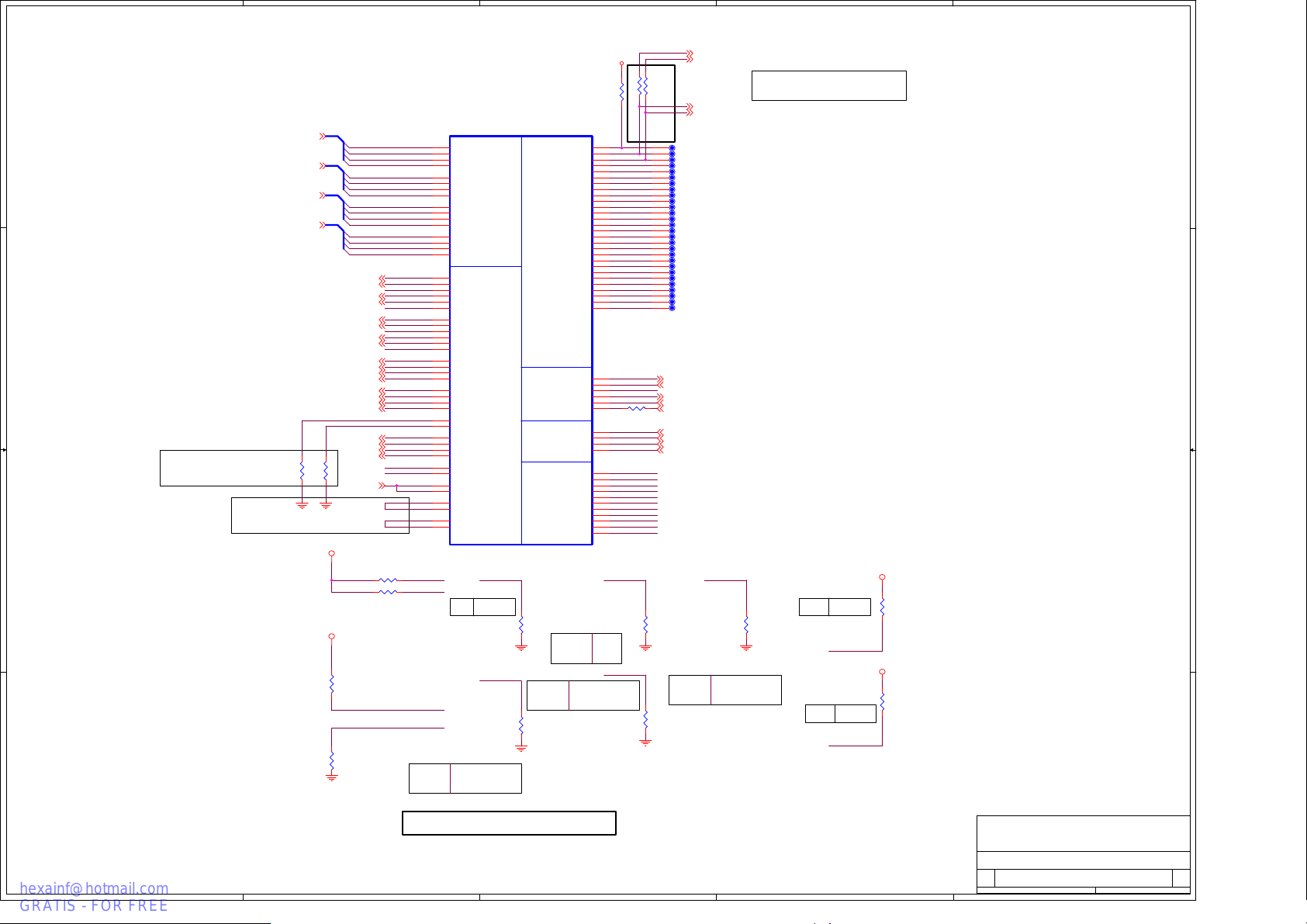

4. Net name Description :

Voltage Rails

DCIN

PMU5V 5.0V always on power rail by LATCH or ACIN

D D

PMU3V 3.3V always on power rail by LATCH or ACIN

3VDDA 3.3V always on power rail by DCON or PSUSC0

3VDDS 3.3V power rail

5VDDS 5.0V power rail

3VDDM

Vcore_CPU

VCCP 1.05V for AGTL+ Termination Voltage

Vcore_MGCH

1.5VDDM 1.5V switched power rail

1.5VDDS 1.5V power rail

1.5VDDA 1.5V always on power rail

2.5VDDM 2.5V power rail for GMCH GIO

DDR_1.8VDDS 1.8V power rail for DDRII

DDR_0.9VDDM 0.9V DDRII Termination Voltage

C C

Part Naming Conventions

C

CN

D

F

L

Q

R

B B

RP

U

Y

Capacitor

=

=

Connector

=

Diode

=

Fuse

=

Inductor

Transistor

=

=

Resistor

=

Resistor Pack

=

Arbitrary Logic Device

=

Crystal and Osc

Net Name Suffix

0=

Active Low signal

Signal Conditioning

=

_D_

_Q_

_L_

A A

Damped (by a resistor)

=

Isolated (by a Q-switch)

=

Filtered (by an inductor or bead)

8

Primary DC system power supply

5.0V always on power rail by DCON or PSUSC05VDDA

3.3V switched power rail

5.0V switched power rail5VDDM

Core Voltage 1.468V~0.956V for CPU

1.05V or 1.5V for ALVISO core

1.8V for CPU PLL Voltage1.8VDDM

7

6

POWER RAIL

VCORE_CPU

VCCP

VCCP_MGCH

VCORE_MGCH ALVISO

1.8VDDM/1.5VDDM

DDR_1.8VDDS 1.8V

1.5VDDM

1.5VDDS

1.5VDDA

2.5VDDM

0.9VDDM 0.9V

3VDDM

3VDDS

3VDDA

5VDDM

5VDDS PCMCIA VCCA

5VDDA

PMU3V

PMU5V 0.0615A

DESTINATION

Dothan

Dothan

ALVISO

Dothan (PLL)

ALVISO

DDR2 MODULE

ALVISO

(LVDS, TVDAC,PCIE)

ICH6M (PLL)

ICH6M

(SUS/LAN)

ALVISO 2.5V

(PCIE_A,LVDSIO,CRTDAC,HV)

DDR RAM

ICH6M

ALVISO (TV DAC)

TI4510

MiniPCI

FWH BIOS

LPC KBC

AC97 CODEC

CLK GEN

LVDS

TI4510

MiniPCI

PCMCIA VCCA

ICH6M

AMP2020

CDROM

HDD

INT KB/ INT MS

INVERTER

ICH6M

USB

PMU08

PMU08

5

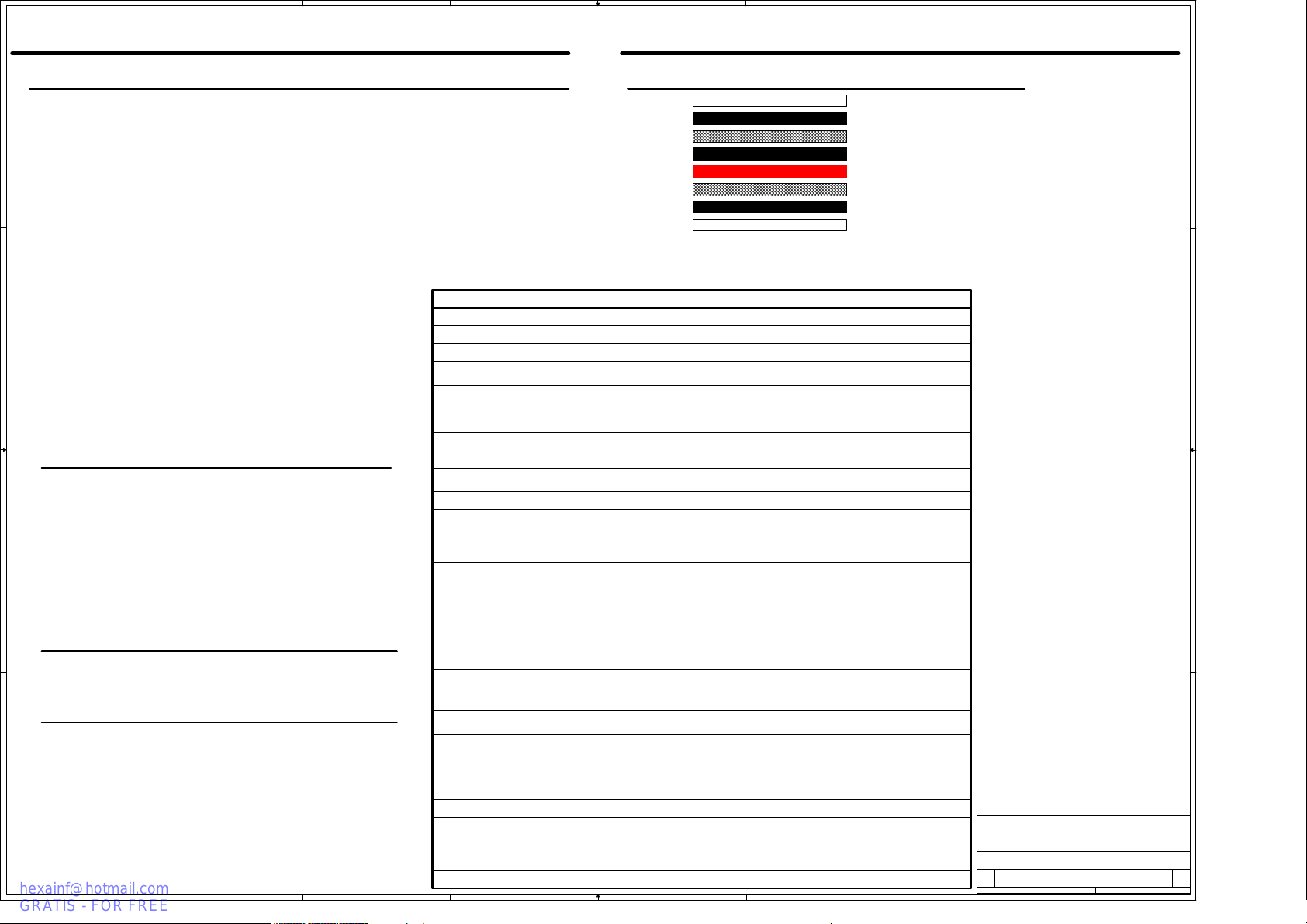

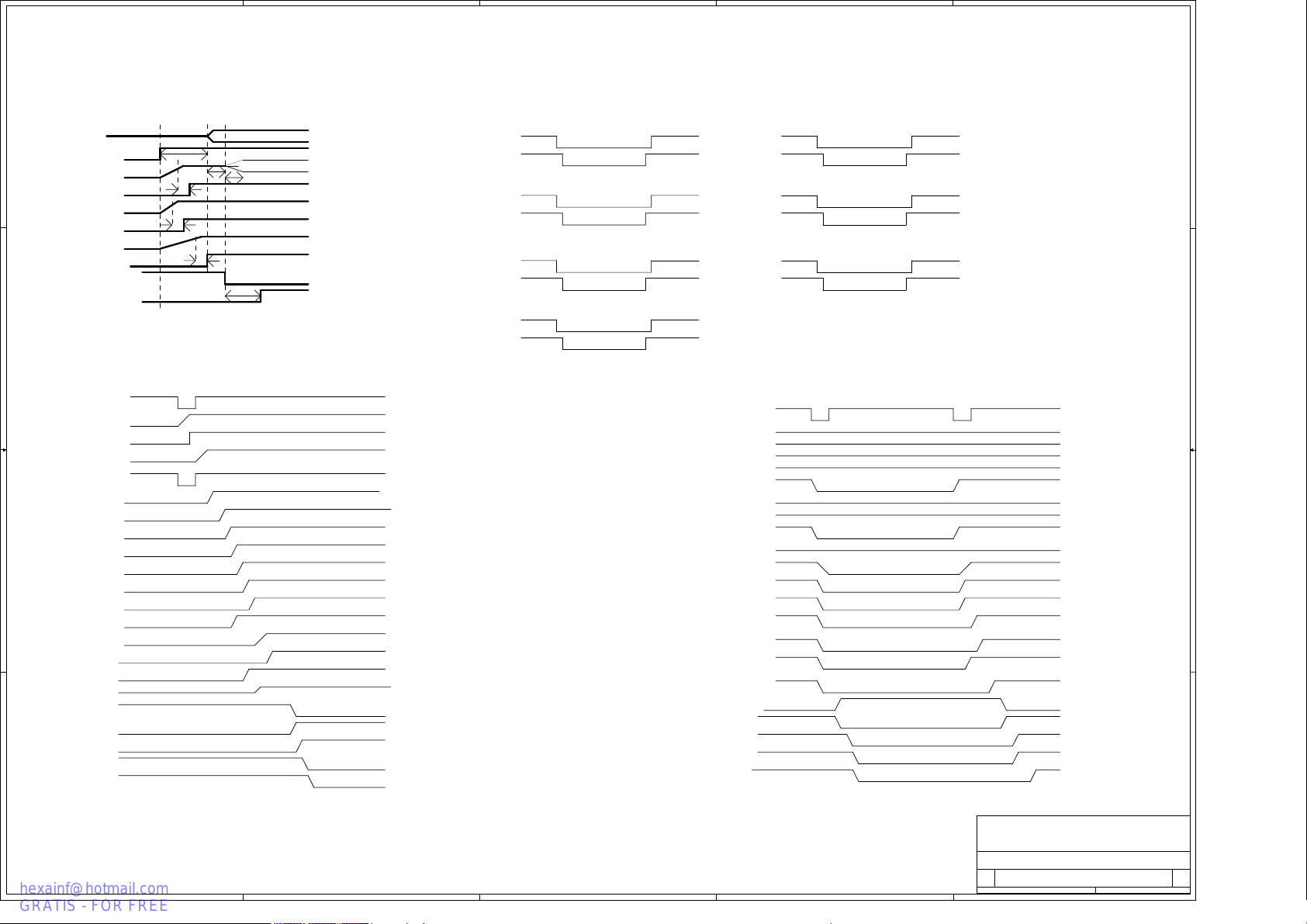

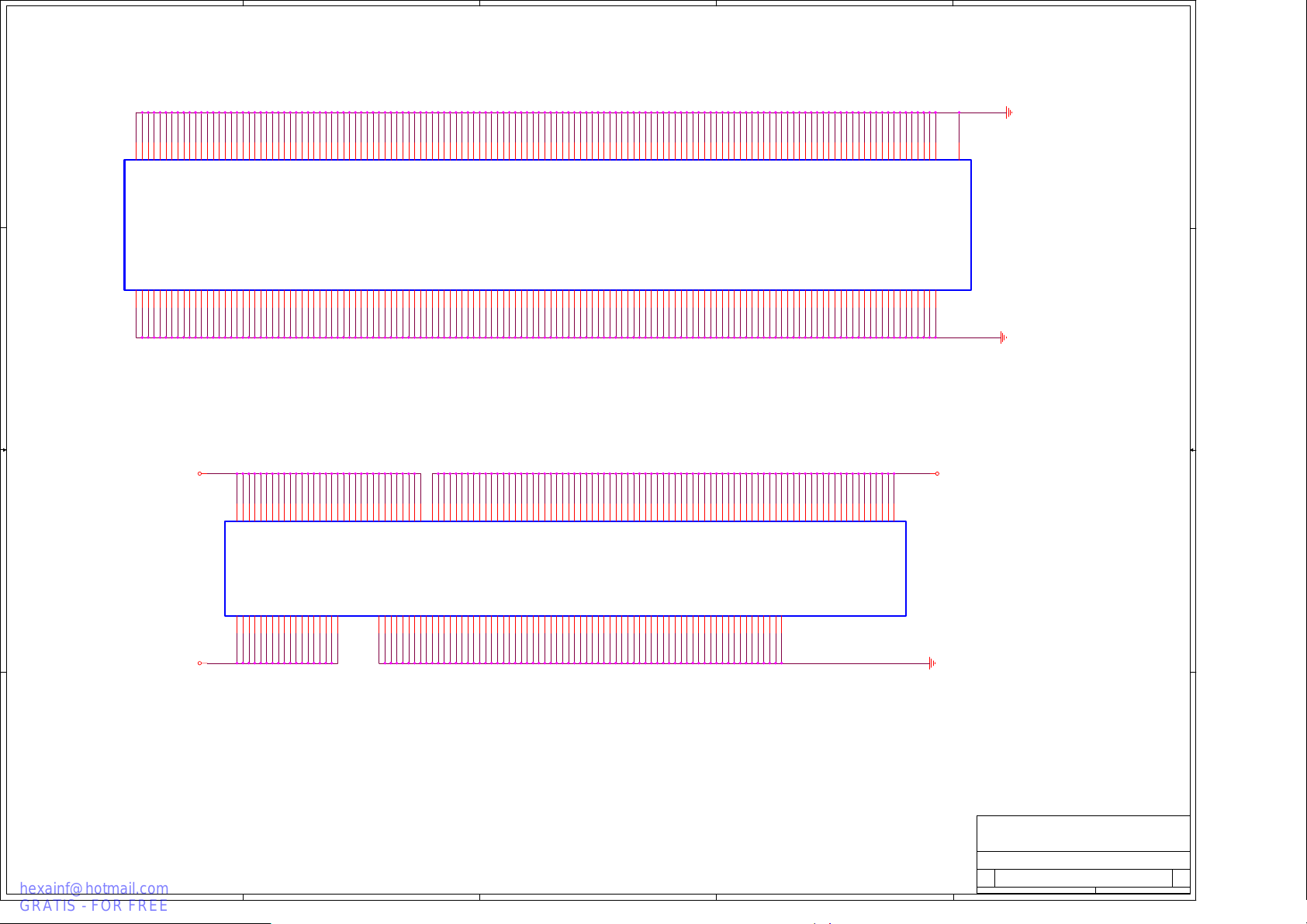

5.Board Stack up Description

PCB Layers

Layer 1

Layer 2

Layer 3

Layer 4

Layer 5

Layer 6

Layer 7

Layer 8

Layers : 8 Depth 1.2mm Impence 55 ohms +/- 10%

(DDR2)

(CORE)

(SUS)ICH6M

(IO)

(SUS)

VOLTAGE

0.956~1.308V

1.05V

1.05V

1.05V 4A

1.8V

1.5V

(VCCASM)

(DMI)

1.5V

1.5V

3.3V

3.3V

3.3V

4

S0 CURRENT

27A

2.5A

0.85A

0.2A

2.7A

1.8A

2.95A

0.15A

0.2A

0.13A

0.024A (Evaluation)

0.0461A

0.36A

0.4A

0.36A

0.4A

0.0615A (Idle)

0.0461A

0.0461A

0.0615A

7mA

0.0615A

Component Side, Microstrip signal Layer

Ground Plane

Stripline Layer(High Speed)

Ground 1 Plane

Power Plane

Stripline Layer(High Speed)

Ground 2 Plane

Solder Side,Microstrip signal Layer

(Evaluation)0.6A

(Idle)

(Run)

(Run)

(Run)

(Run)

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

ANNOTATIONS

Date: Sheet

2

3

(Idle)

(Idle)

(Idle)

0.338A

0.677~0.8A

0.52A

0.569A

464Friday, May 07, 2004

1

0.2

of

5

hexainf@hotmail.com

GRATIS - FOR FREE

4

3

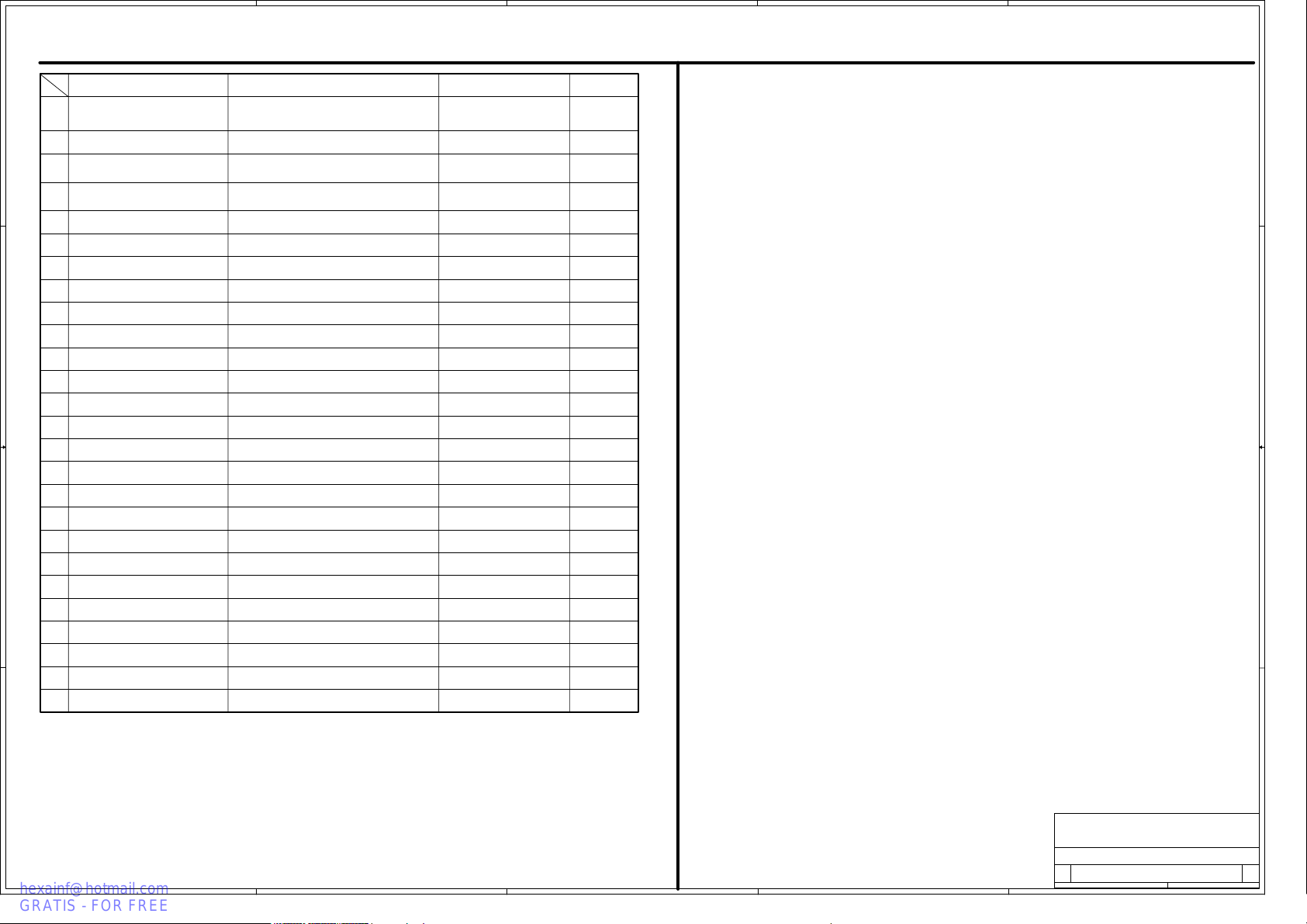

6.Schematic modify Item and History :

2

1

PHASE INSOLUTIONROOT CAUSEBUG

D D

1

SATA HDD can't assembly SATA HDD CNN Reversed Modify SATA HDD CNN V0.2

2

defined

V0.2CRT NO display CRT CNN PIN defined error Chnaged CRT CNN PIN

HISTORY:

3

4

5

6

7

8

9

C C

10

11

12

13

14

15

16

17

B B

A A

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

Version Notice

5

4

3

2

Date: Sheet

1

564Friday, May 07, 2004

of

0.2

5

hexainf@hotmail.com

GRATIS - FOR FREE

4

3

7. power on & off & S3 Sequence :

2

1

D D

Power On Sequencing Timing Diagram

VID

VR_ON

Vcc-core

CPU_UP

Tboot

Tsft_star_vcc

Tcpu_up

Vboot

Tboot-vid-tr

Vid

Vccp

Vccp_UP

Tvccp_up

ICH6M Timing

3.3VDDM

2.5VDDM

MAX Delta

Voltage=300mV

3.3VDDM(LAN)

2.5VDDM(LAN)

MAX Delta

Voltage=300mV

3.3VDDA

1.5VDDA

MAX Delta

Voltage=300mV

3.3VDDS(LAN)

2.5VDDS(LAN)

MAX Delta

Voltage=300mV

Vccgmch

GMCHPWRGD

Tgmch_pwrgd

CLK_ENABLE#

IMVP4_PWRGD

C C

BATTERY ONLY POWER ON TIMING

POWSW0

PMU5V/PMU3V

DCON

VDDA

MAINSW0_ICH

PM_RSTRST0

PM_SLP_S30/S40/S50

PSUSC0

B B

A A

SUSTAT_B0

VDDM,VDDS

PM_PWROK

SYS_PWROK

VRON_VCCP

VCCP/1.2VDDM

VCORE_ON

VR_ON

VCORE_CPU

CK408_PWRGD0

PM_VGATE

CPU_PWRGD

PCI_RST0

AGTL+_CPURST0

Tcpu_pwrgd

To ICH4

To ICH4

From ICH4

From ASIC_B0

From ASIC_B0

To clock generator

To ODEM and ICH4

From ICH4 to CPU

To ODEM/other PCI device

From ODEM to CPU

1.5VDDM

VCCP

MAX Delta

Voltage=300mV

5VREF

3VDDM

MAX Delta

Voltage=300mV

5VREF_SUS

3VDDA

MAX Delta

Voltage=300mV

No Requirement

3VDDM<--->1.5VDDM

2.5VDDM<--->1.5VDDM

2.5VDDM<--->5VREF

1.5VDDM<--->5VREF

S3 SUSPEND AND RESUME TIMING

POWSW0

PMU5V/PMU3V

PM_RSMRST0

PM_SLP_S30

PM_SLP_S40/S50

PSUSC0

SUSTAT_B0

PM_PWROK

SYS_PWROK

VRON_VCCP

VCCP,1.2VDDM

VCORE_ON

VCORE_CPU

CK408_PWRGD0

PM_VGATE

CPU_PWRGOOD

PCI_RST0

AGTL+_CPURST0

DCON

VDDA

VDDS

VDDM

VR_ON

H

H

H

H

H

H

H

To ICH4_M

From ICH4_M

From ICH4_M

From ASIC_B0

From ASIC_B0

1.5VDDS AND

DDR_PWRGD

To clock

Generator

ToICH4 and ODEM

From ICH4 to CPU

To ODEM/other

PCI device

From ODEM to CPU

5

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

Montara GM power on/off s3 timing 0.2

4

3

2

Date: Sheet

1

664Friday, May 07, 2004

of

5

hexainf@hotmail.com

GRATIS - FOR FREE

4

3

2

1

8. Layout Guideline :

System Bus Common Clock Signal Layout Guide :

ADS# , BNR# , BPRI# , BR0# , DBSY# , DEFER# , DPWR# , DR DY # , HI T# , H IT M# , LO CK # ,

RS[2..0]# , TRDY# , RESET#.

Transmission Line Type Total Trace Length Normal Impedance Spacing (mils)

Strip-line(Int. Layer)

D D

Micro-strip(Ext. Layer)

Source Synchronous DATA :

Signals Name

DATA#[15..0] , DINV0#

DATA#[31..16] , DINV1#

DATA#[47..32] , DIN V2# +/- 25 mils

DATA#[63..48] , DINV3#

Topology1:

DATA#[63..0] , DINV#[3..0] , DSTBN#[3..0] , DSTBP#[3..0]

Signal Names Data to Data Strobe to

DATA#[63..0]

DINV#[3..0]

DSTBN#[3..0]

DSTBP#[3..0]

No trace witdth to trace space ratio requirement relaxation

C C

B B

A A

NOTE:

allowedcomplementary strobes.

The only recommended trace spacing ratio is 3:1

Topology2:

DATA#[63..0] , DINV#[3..0] , DSTBN#[3..0] , DSTBP#[3..0]

Signal Names Data to Data Strobe to

DATA#[63..0]

DINV#[3..0]

DSTBN#[3..0]

DSTBP#[3..0]

No trace witdth to trace space ratio requirement relaxation

NOTE:

allowedcomplementary strobes.

The only recommended trace spacing ratio is 3:1

Topology3:

DATA#[63..0] , DINV#[3..0] , DSTBN#[3..0] , DSTBP#[3..0]

Signal Names Data to Data Strobe to

DATA#[63..0]

DINV#[3..0]

DSTBN#[3..0]

DSTBP#[3..0]

No trace witdth to trace space ratio requirement relaxation

NOTE:

allowedcomplementary strobes.

The only recommended trace spacing ratio is 3:1

Source Synchronous ADDRESS :

Address#[31..3] , REQ#[4..0] , ADSTB#[1..0]

Transmission Line Type

Strip-line

Signals Name

A#[16..3] , REQ#[4..0]

A#[31..17

5

1.0 ~ 6.5 inch 55+/-10% 4 & 8(Int. Layer )

Signals Matching

+/- 100 mils +/- 25 mils

+/- 100 mils

+/- 100 mils

+/- 100 mils

Transmission

Line Type

Strip-line

Strip-line

Strip-line

Strip-line

Transmission

Line Type

Strip-line

Strip-line

Strip-line

Strip-line

Transmission

Line Type

Strip-line

Strip-line

Strip-line

Strip-line

Total Trace Length

(inches) (inches)

Total Trace Length

(inches) (inches)

Total Trace Length

(inches) (inches)

Total Trace Length

Signals Matching

+/- 200 mils

+/- 200 mils

Strobes associated

with the group

DSTBP0#,DSTBN0#

DSTBP1#,DSTBN1#

DSTBP2#,DSTBN2#

DSTBP3#,DSTBN3#

Min Max

0.5

5.5

0.5

5.5

0.5

5.5

0.5

5.5

Min Max

0.5

3.0

0.5

3.0

0.5

3.0

0.5

3.0

Min Max

0.5

5.5

0.5

5.5

0.5

5.5

0.5

5.5

Strobes associated

with the group

ADSTB0#

ADSTB1#

Normal

Impedance

55+/-10%

55+/-10%

55+/-10%

55+/-10% 4 & 12

Normal

Impedance

55+/-10%

55+/-10%

55+/-10%

55+/-10% 4 & 12

Normal

Impedance

55+/-10%

55+/-10%

55+/-10%

55+/-10% 4 & 12

Normal Impedance

55+/-10%

5 & 10(Ext. Layer)

Strobe Matching

+/- 25 mils

+/- 25 mils

Spacing (mils)

Strobe to

Strobe

4 & 8

4 & 8

4 & 12

Spacing (mils)

Strobe to

Strobe

4 & 6

4 & 6

4 & 12

Spacing (mils)

Strobe to

Strobe

4 & 8

4 & 8

4 & 12

Spacing (mils)

4 & 80.5 ~ 6.5 inch

Strobe Matching

+/- 200 mils

+/- 200 mils

4

Data

Data

Data

NA

NA

4 & 8

4 & 8

NA

NA

4 & 6

4 & 6

NA

NA

4 & 8

4 & 8

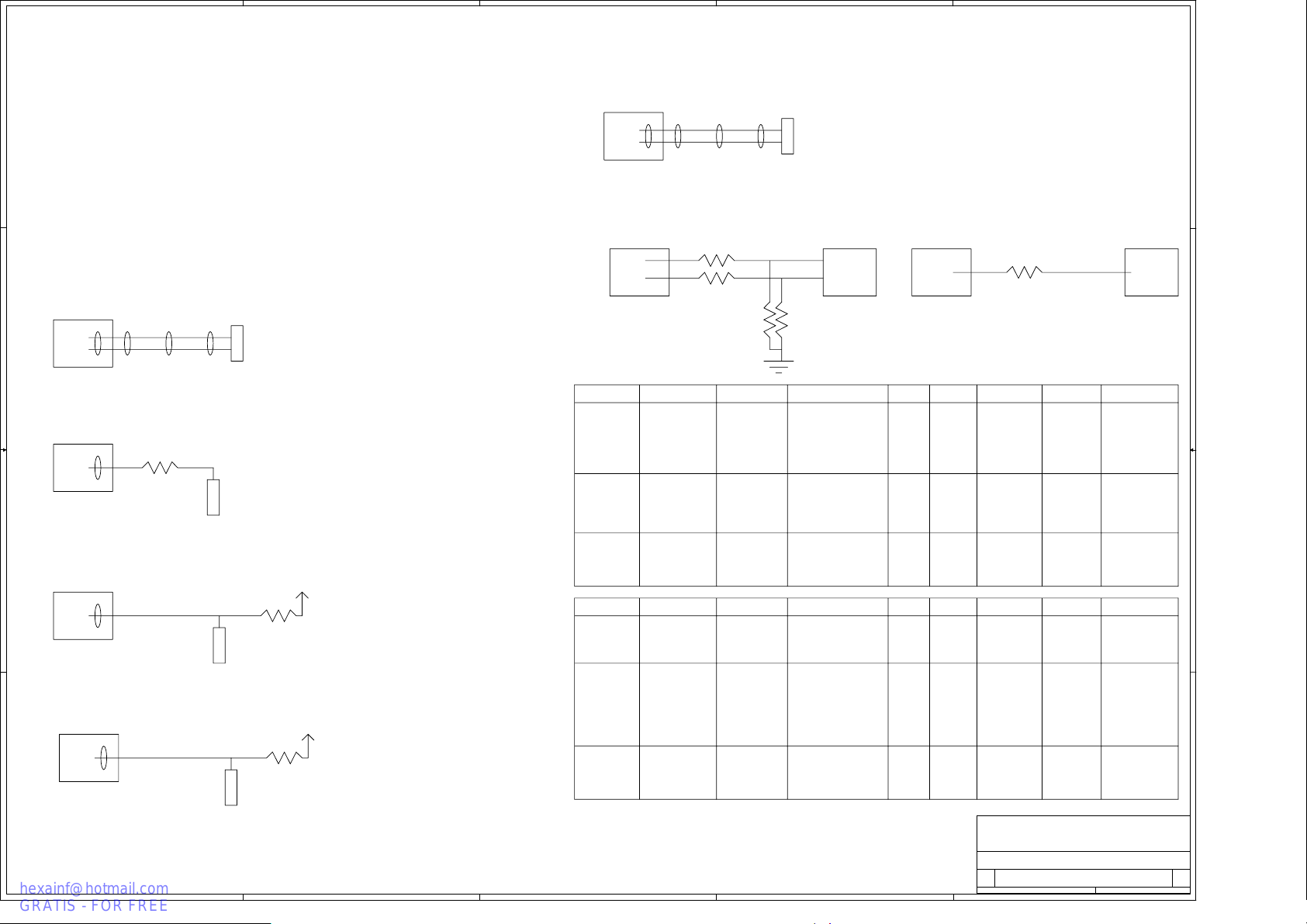

Topology : IERR# , FERR#

CPU

Receiver

L1

R1

Topology : PROCHOT#

CPU

VCCP

L1

L2

Topology : PWRGOOD

Topology : THERMTRIP#

MCH

CPU

Topology : CPUSLP#

ICH6

Topology : LINT1 / NMI , LINT0 / INTR , A20M# , IGNNE# , DPSLP# , SMI# , STPCLK#

Rtest

L2 L1

(No Stuff)

ICH6

L2

Rtt

Voltage

Translation

Device

L1

L2L1

L1

L3

CPUICH4

CPU

CPU

Receiver

ICH6-M

L3

VCCP

L2

L1

0.5" - 12"

Rtt

L2

Rss

L4

0" - 3.0"

0" - 3.0"

0.5" - 12"

L1

0.5" - 12"

0.5" - 12"

L1

VCCP

0.5" - 12"

Rtt

0.5" - 12"

VCCP

L1

0.5" - 12"

Rtt

0.5" - 12"

L1

MCH

0.5" - 12" Micro-strip

0.5" - 12"

Transmission Line

L1

Micro-strip0.5" - 12"

Strip-line0.5" - 12"

Topology : CPU RESET# without ITP

L1

1" - 6.5"

Transmission Line

Micro-strip1" - 6.5"

Strip-line

ICH6

CPU

L1

Topology : CPU RESET# with ITP

MCH

L1

VCCP

Rtt

L2

L3

Rs

ITP

1.0" - 6.0" 22.6 +/-1%

Differential Impedance Targets for Routing :

Signal Type

Host Clock

DMI

EXT-PCI

SDVO

LVDS

SATA

USB2.0

PCI EXPRESS

DDR2

3

Routing Geometry

5 -mil trace width on 7- mil spacing 100 Ω +/- 15 %

5 -mil trace width on 7- mil spacing

5 -mil trace width on 7- mil spacing

5 -mil trace width on 7- mil spacing

5 -mil trace width on 7- mil spacing 100 Ω +/- 15 %

5 -mil trace width on 7- mil spacing

4 -mil trace width on 7- mil spacing

5 -mil trace width on 7- mil spacing

5 -mil trace width on 7- mil spacing

L3

0" - 3.0"

L2

0" - 3.0"

0" - 3.0"

L2

0" - 3.0"

0" - 3.0"

L2

0" - 3.0"

0" - 3.0"

L2

0.5" -12.0"

0.5" - 12.0"

L2 + L3CPU

6.0" max

R1

56 +/-5%0" - 3.0" 56 +/-5%

56 +/-5% 56 +/-5%

Rtt

56 +/-5%

56 +/-5%

Rtt

330 +/-5%

330 +/-5%

Rtt

56 +/-5%

56 +/-5%

Rtest

0

0

L3

0.5" max

Impedance

100 Ω +/- 15 %

100 Ω +/- 15 %

100 Ω +/- 15 %

100 Ω +/- 15 %

90 Ω +/- 15 %

100 Ω +/- 15 %

85 Ω +/- 15 %

Rtt Transmission Line

Micro-strip

Strip-line

Transmission Line

Micro-strip

Strip-line

Transmission Line

Micro-strip

Strip-line

RsL1

Transmission Line

Rtt

54.9 +/-1%

Rss

75 +/-5%

75 +/-5%

Transmission Line

Strip-line

Signal Matching

+/- 20 mils

+/- 5 mils

+/- 20 mils

+/- 20 mils

+/- 20 mils

+/- 10 mils

+/- 75 mil

+/- 37 mils

+/- 20 mil

2

Micro-strip

Strip-line

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

Montara GM DDR Layout Guideline 0.2

Date: Sheet

1

764Friday, May 07, 2004

of

5

hexainf@hotmail.com

GRATIS - FOR FREE

4

3

2

1

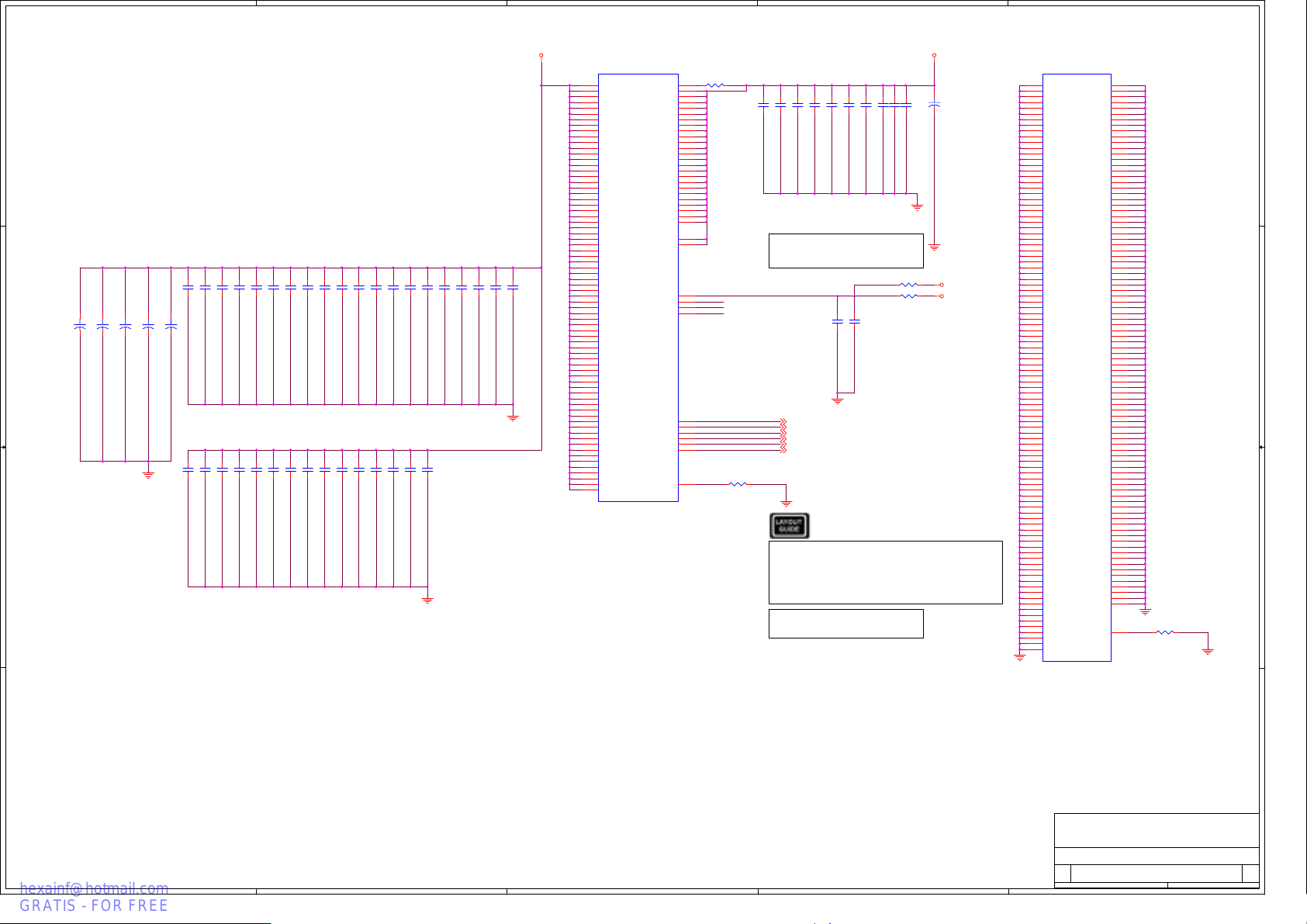

ALVISO DDR2 Layout Guidelines

Note that al l l e ng t h m a tc h i ng f o r m ul a s ar e b as e d o n GMCH die-pad to SO-DIMM pin total length

D D

C C

B B

A A

DDR2 Signal Groups

Group Signal Name

Clocks

Data

Control

Command

Compensation

Feedback

SCK[5:0]

SCK#[5:0]

SA_DQ[63:0] ; SB_DQ[63:0]

SA_DQS[7:0] ; SA_DQS[7:0]

SA_DM[7:0] ; SB_DM[7:0]

SCKE[3:0]

SCS#[3:0]

SM_ODT[3:0]

SA_MA[13:0] ; SB_MA[13:0]

SA_BA[1:0] ; SB_BA[1:0]

SA_RAS# ; SB_RAS#

SA_CAS# ; SB_CAS#

SA_WE# ; SB_WE#

SMRCOMPN ; SMRCOMPP

SMSLEWIN ; SMSLEWOUT

SMVREF[1:0]

SA_RCVENOUT# ; SB_RCVENOUT#

SA_RCVENIN# ; SB_RCVENIN#

Length Matching Formulas

Signal Group Minimum Length Maximum Length

Control to Clock

Command to Clock

CPC to Clock

Strobe to Clock

Data to Strobe

Clock Signals Topologies and Routing Guidelines

GMCH

Pin

P1

Package Length

Range

4/4/8 7/4/12 8/5/10

L2 S1

L1

SL SL

Min:0.5"

Max:5.0"

SO-DIMM PADS

MS

Data Signals Topologies and Routing Guidelines

4/4 8/8

P1

L1 L2

SO-DIMM

PADS

S1SL SL MS

5/10

GMCH

Pin

Package Length

Range

Control Signals Topologies and Routing Guidelines

GMCH

Pin

P1

Package Length

Range

4/4 8/8 4/8,5/10

L2

L1

SL SL

SO-DIMM PADS

L3

S1

MSMS

SL

56 ohm 5%

Command Signals Topologies and Routing Guidelines

GMCH

Pin

P1

Package Length

Range

L1

SL SL SL MSMS S1

5

L2 L3

SO-DIMM

PADS

Clock - 1.0"

Clock - 1.0"

Clock - 1.0"

Clock - 1.0"

Strobe - 25 mils Strobe + 25 mils

7 mil trace, 4 mil pair space

Clock length tolerence within the pair : +/- 10 mil

Clock to Clock Length Matching : +/- 10 mils

Minimum Pair to Pair Spacing : ? mils

Minimum Spacing to other DDR Signals : 12 mils

Minimum Spacing to other non-DDR Signals : 20 mils

Trace Length L1 : Max 0.5", S1 : Max 200 mils

Total Length --L1+L2+S1: Min 0.5" , Max 5.0"

Minimum Spacing to other DDR Signals : 12 mils

Minimum Spacing to other non-DDR Signals : 20 mils

Trace Width : 4mils

Trace Spacing : 6mils

Total Length --L1+L2+S1: Min 0.5" , Max 4.5"

Trace Length L1 : Max 0.5", S1 : Max 200 mils

DQ/DM to DQSLength Matching : +/- 10 mils

inner layerL2 Segment : 4 mils,Total

Length < /= 3000 mils

inner layerL2 Segment : 8 mils,Total

Length > 3000 mils

outer layerL2 Segment : 5 mils

inner layerL2 Segment : 6 mils,Total

Length < /= 3000 mils

inner layerL2 Segment : 8 mils,Total

Length > 3000 mils

outer layerL2 Segment : 10 mils

Minimum CTRL trace Spacing : 8 mils

Minimum Spacing to other DDR Signals : 12 mils

Minimum Spacing to other non-DDR Signals : 20 mils

Trace Length L1 : Max 0.5"

Total Length --L1+L2+S1: Min 0.5" , Max 4.5"

CTRL to SCK/SCK# Length Matching : (CTRL-1.5")

</= CTRL </= ( CLK 1.0")

Minimum Spacing to other DDR Signals : 12 mils

Minimum Spacing to other non-DDR Signals : 20 mils

Trace Width : 4mils

56 ohm 5%

Trace Spacing : 6mils

Total Length --L1+L2+S1: Min 0.5" , Max 4.5"

Trace Length L1 : Max 0.5", S1 : Max 200 mils

Trace Length L3 : Max 1.5"

Length Matching : CMD to SCK/SCK#

4

Clock + 0.5"

Clock + 2.0"

Clock + 0.5"

Clock + 0.5"

L3 : Max 1.5"

inner layerL2 Segment : 4 mils,Total

Length < /= 3000 mils

inner layerL2 Segment : 8 mils,Total

Length > 3000 mils

outer layerL2 Segment : 5 mils

inner layerL2 Segment : 6 mils,Total

Length < /= 3000 mils

inner layerL2 Segment : 8 mils,Total

Length > 3000 mils

outer layerL2 Segment : 10 mils

CMD , SODIMM0 P1+L1+L2

CMD , SODIMM1 P1+L1+L3

Min : Clock - 1.5" , Max : Clock -1.0"

Data Strobe Signals Topologies and Routing Guidelines

GMCH

Pin

P1

Package Length

Range

CK410-M

LENGTHCLOCKS

3

L1 : Max 0.5"

L2 : Max 200mils

L3 : Max 0.5"

L4 : Min 2" Max 8 "

L1 : Max 0.5"

L2 : Max 200mils

L3 : Max 200 mils

L4 : Min 200 mils

Max 12"

L1 : Max 0.5"

L2 : Max 200mils

L3 : Max 200 mils

L4 : Min 4" Max 10"

L1 : Max 0.5"

L2 : Min 2" Max 20"

L1 : Max 0.5"

L2 : Min 2" Max 20"

L2 : Z +(0" to 10")

,Max 20"

L2 : Z +(0" to 6")

,Max 20"

L1 : Max 0.5"

L2 : Max 18"

HCLKCPU[1..0]

HCLKNB[1..0]

HCLKITP[1..0]

SRC CLK

DOT CLK

CLOCKS TRACE MUTCHING

USB (48MHZ)

CLK

PCI/PCIF

CLK

PCLKICH

PCLKFWH

PCLKSIO

PCLKLAN

14MCLK_SIO

14MCLK_ICH

14MCLK_AC97

4/4/12

8/4/12

4/4/8

L2 S1

SL SL MS

RS

L1 L2

MS

L1 L2

MS

RS

4 / 7 mils

4 / 7 mils

50 mils

(spacing

to other)

4 / 7 mils

25 mils

(spacing

to other)

TRACE / SPACE SKEW

4 mils

(stripline)

20 mils

(spacing

to other)

4 mils

(stripline)

10 mils

(spacing

to other)

4 mils

(stripline)

10 mils

(spacing

to other)

5/5/10SO-DIMM PADS

L4

MS

MS

SL

L4

SL

L3L3

MS MS

TRACE MUTCHING

L1+/L1- : +/- 10 mils

L2+/L2- : +/- 10 mils

L3+/L3- : +/- 10 mils

L1+L2+L3 /L1- + L2- + L3-

: +/- 10 mils

L4+/L4- : 200 +/- 10

mils (for PGA Topology)

L4+/L4- : 500 +/- 10

mils (for BGA Topology)

L1+L2+L4 /L1- + L2- + L4-

: +/- 25 mils

+/- 10 mils 33 ohms

NA

NA

(L1+L2) to ICH6-M

must be within 500

nils to (L1+L2) to

SIO/AC97

CPU,GMCH

2

Minimum Spacing to other DDR Signals : 12 mils

Minimum Spacing to other non-DDR Signals : 20 mils

Trace Width : 4mils

DQS to DQS# Spacing : 4mils

Minmun DQS to DQ Spacing :

Total Length --L1+L2+S1: Min 0.5" , Max 4.5"

Trace Length L1 : Max 0.5", S1 : Max 200 mils

Length Matching : DQS to SCK/SCK#

33 ohms

+/- 5%

+/- 5% to

33 ohms

+/- 5%

+/- 5%

inner layerL2 Segment : 4 mils,Total

Length < /= 3000 mils

inner layerL2 Segment : 8 mils,Total

Length > 3000 mils

outer layerL2 Segment : 5 mils

outer layerL2 Segment : 5 mils

inner layerL2 Segment : 6 mils,Total

Length < /= 3000 mils

inner layerL2 Segment : 8 mils,Total

Length > 3000 mils

outer layerL2 Segment : 10 mils

( Clock - 1.0") </= DQS </= ( Clock + 0.5")

MS

CK410-M

49.9 ohms

+/- 1%

49.9 ohms

+/- 1%

49.9 ohms

+/- 1%

L1 L2 CPU,GMCHL4

MS

R1

RtRs

IMPEDANCE

100 ohms

+/- 15%

differential mode

55 ohms

+/- 15%

single mode

55 ohms

+/- 15%

100 ohms

+/- 15%

MS

MS

SKEW

350ps Total

Budget

100ps for flight

skew

100ps for pin to

pin skew

150ps for jitter

NA22 ohms

SL

SL

Differentials pairs with

the same length

(within 10 mil)

1.

2.CPU & NB trace

mismatch within

450 mil

* 66MCLK_ICH &

AGPCLK_GMCH

AGPCLK_ATI

Length mismatch

within 100 mils

1.Making PCI length with

2.Max skew = 1ns

IMPEDANCE

33 ohms

+/- 5%

12.1 ohms

+/- 1%

33 ohms

+/- 5%

12.1 ohms

+/- 1%

55 ohms

+/- 15%

55 ohms

+/- 15%

55 ohms

+/- 15%

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

DDRII/CLK Gen Layout Guideline 0.2

Date: Sheet

NONE

NONE

1

NOTESTRACE / SPACE

minimum various

NOTESR1LENGTH Rt

864Friday, May 07, 2004

of

A

hexainf@hotmail.com

GRATIS - FOR FREE

AGTL+_HA0[31..3]16 AGTL+_HD0[63..0] 16

AGTL+_HA03

AGTL+_HA04

AGTL+_HA05

AGTL+_HA06

AGTL+_HA07

AGTL+_HA08

AGTL+_HA09

AGTL+_HA010

AGTL+_HA011

AGTL+_HA012

AGTL+_HA013

AGTL+_HA014

4 4

AGTL+_ADSTB0016

AGTL+_HREQ0[4..0]16

AGTL+_ADSTB1016

AGTL+_ADS016

3 3

Place testpoint on IERR# with

a GND 0.1" away

2 2

THRMTRIP0 should coonect to

ICH6 and ALVISO without

T-ing (No stub)

CPU_BCLK23

CPU_BCLK023

CPU_ITP_BCLK23

CPU_ITP_BCLK023

1 1

THERMDA12

THERMDC12

THRMTRIP014,20

ITP_TDO_OD30

ITP_TRST030

AGTL+_PRDY030

AGTL+_PREQ030

A

AGTL+_BNR016

AGTL+_BR0016

AGTL+_DEFER016

AGTL+_DRDY016

AGTL+_DBSY016

AGTL+_HIT016

AGTL+_HITM016

VCCP10,17,19,20,21,23,30,55

AGTL+_LOCK016

AGTL+_RS0[2..0]16

AGTL+_CPURST016,30

VCCP10,17,19,20,21,23,30,55

CPU_PWRGOOD19

CPU_FERR0_OD19

VCCP10,17,19,20,21,23,30,55

ITP_TCK30

ITP_TDI30

ITP_TMS30

VCCP10,17,19,20,21,23,30,55

R663

56.2 1% 1/16W 0402

CPU_INIT019

AGTL+_TRDY016

CPU_A20M019

CPU_IGNNE019

CPU_INTR19

CPU_NMI19

CPU_SMI019

CPU_STPCLK019

CPU_SLP016,19

CPU_DPSLP019

AGTL+_BPRI016

AGTL+_DPWR016

R658 56 5% 1/16W 0402

R673 0 5% 1/16W 0603

R657

39.2 1% 1/16W 0603

R674

150 5% 1/16W 0603

AGTL+_HA015

AGTL+_HA016

AGTL+_HREQ00

AGTL+_HREQ01

AGTL+_HREQ02

AGTL+_HREQ03

AGTL+_HREQ04

AGTL+_HA017

AGTL+_HA018

AGTL+_HA019

AGTL+_HA020

AGTL+_HA021

AGTL+_HA022

AGTL+_HA023

AGTL+_HA024

AGTL+_HA025

AGTL+_HA026

AGTL+_HA027

AGTL+_HA028

AGTL+_HA029

AGTL+_HA030

AGTL+_HA031

CPU_IERR0_OD

AGTL+_RS00

AGTL+_RS01

AGTL+_RS02

R662

200 1% 1/16W 0603

B

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

AA3

Y3

AA2

U3

R2

P3

T2

P1

T1

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

N2

L1

N4

L4

H2

M2

K3

K4

A4

B5

J2

H1

K1

L2

M3

B11

E4

C2

D3

A3

D1

D4

B4

C6

A6

B7

J3

C19

B18

A18

C17

B17

B15

B14

A16

A15

A13

C12

A12

C11

B13

A10

B10

R84

27.4 1% 1/16W 0402

B

U6-1

A3#

A4#

A5#

A6#

A7#

A8#

Address Group0 Control Signal Legacy CPU Thermal Host CLK ITP700 PortAddress Group1

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

ADSTB0#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB1#

ADS#

BNR#

BR0#

DEFER#

DRDY#

DBSY#

HIT#

HITM#

IERR#

INIT#

LOCK#

RS0#

RS1#

RS2#

TRDY#

RESET#

PWRGOOD

A20M#

FERR#

IGNNE#

LINT0

LINT1

SMI#

STPCLK#

SLP#

DPSLP#

BPRI#

DPWR#

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

BCLK0

BCLK1

ITP_CLK0

ITP_CLK1

TCK

TDI

TDO

TMS

TRST#

PRDY#

PREQ#

SCKT Foxconn SMT PZ47903-2741-01

GTLREF2/DPRSTP#

Data Group0Data Group1Data Group2Data Group3

DINV0#

DSTBN0#

DSTBP0#

DINV1#

DSTBN1#

DSTBP1#

DINV2#

DSTBN2#

DSTBP2#

DINV3#

DSTBN3#

DSTBP3#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

GTLREF0/RSVD

GTLREF1

GTLREF3/RSVD

RSVD0

RSVD1

RSVD2/BSEL1

RSVD3

RSVD4/BSEL0

RSVD5/PSI#

TEST1

TEST2

COMP0

COMP1

COMP2

COMP3

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

AGTL+_HD00

A19

AGTL+_HD01

A25

AGTL+_HD02

A22

AGTL+_HD03

B21

AGTL+_HD04

A24

AGTL+_HD05

B26

AGTL+_HD06

A21

AGTL+_HD07

B20

AGTL+_HD08

C20

AGTL+_HD09

B24

AGTL+_HD010

D24

AGTL+_HD011

E24

AGTL+_HD012

C26

AGTL+_HD013

B23

AGTL+_HD014

E23

AGTL+_HD015

C25

D25

C23

C22

AGTL+_HD016

H23

AGTL+_HD017

G25

AGTL+_HD018

L23

AGTL+_HD019

M26

AGTL+_HD020

H24

AGTL+_HD021

F25

AGTL+_HD022

G24

AGTL+_HD023

J23

AGTL+_HD024

M23

AGTL+_HD025

J25

AGTL+_HD026

L26

AGTL+_HD027

N24

AGTL+_HD028

M25

AGTL+_HD029

H26

AGTL+_HD030

N25

AGTL+_HD031

K25

J26

K24

L24

AGTL+_HD032

Y26

AGTL+_HD033

AA24

AGTL+_HD034

T25

AGTL+_HD035

U23

AGTL+_HD036

V23

AGTL+_HD037

R24

AGTL+_HD038

R26

AGTL+_HD039

R23

AGTL+_HD040

AA23

AGTL+_HD041

U26

AGTL+_HD042

V24

AGTL+_HD043

U25

AGTL+_HD044

V26

AGTL+_HD045

Y23

AGTL+_HD046

AA26

AGTL+_HD047

Y25

T24

W25

W24

AGTL+_HD048

AB25

AGTL+_HD049

AC23

AGTL+_HD050

AB24

AGTL+_HD051

AC20

AGTL+_HD052

AC22

AGTL+_HD053

AC25

AGTL+_HD054

AD23

AGTL+_HD055

AE22

AGTL+_HD056

AF23

AGTL+_HD057

AD24

AGTL+_HD058

AF20

AGTL+_HD059

AE21

AGTL+_HD060

AD21

AGTL+_HD061

AF25

AGTL+_HD062

AF22

AGTL+_HD063

AF26

AD20

AE24

AE25

C8

B8

A9

C9

A7

AD26

CPU_NC_E26

E26

G1

CPU_NC_AC1

AC1

CPU_NC_B2

B2

CPU_NC_AF7

AF7

C14

CPU_NC_C3

C3

C16

E1

R664 1K 5% 1/16W 0402(NU)

C5

R656 1K 5% 1/16W 0402(NU)

F23

P25

P26

AB2

AB1

Less than 0.5"

AGTL+_HD0[63..0]AGTL+_HA0[31..3]

AGTL+_DINV00 16

AGTL+_DSTBN00 16

AGTL+_DSTBP00 16

AGTL+_DINV10 16

AGTL+_DSTBN10 16

AGTL+_DSTBP10 16

AGTL+_DINV20 16

AGTL+_DSTBN20 16

AGTL+_DSTBP20 16

AGTL+_DINV30 16

AGTL+_DSTBN30 16

AGTL+_DSTBP30 16

AGTL+_BPM00 30

AGTL+_BPM10 14,30

AGTL+_BPM20 14,30

R668 0 5% 1/16W 0402(NU)

AGTL+_BPM30 30

GTLREF = 2/3 VCCP

Max Length : 0.5"

Place within 2"

R644 27.4 1% 1/16W 0402

R647 54.9 1% 1/16W 0603

R623 27.4 1% 1/16W 0402

R620 54.9 1% 1/16W 0603

C

ITP_DBRESET0 20,30

R619

2K 1% 1/16W CF 0402

IMVP4 POWER STATUS INCADITOR

Comp(0,2) must be routed width

18 mils Zo=27.4ohm ,make trace

length shorter than 0.5"

Comp(1,3) must be routed width

5 mils Zo=55 ohm ,make trace

length shorter than 0.5"

C

R6171K 1% 1/16W 0402

CPU_BSEL1 23

CPU_BSEL0 23

PM_PSI0 11

VCCP 10,17,19,20,21,23,30,55

CPU_DPRSTP0 19

D

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

CPU ( Dothan ) 1/2

D

Date: Sheet

E

964Friday, May 07, 2004

E

of

0.2

A

hexainf@hotmail.com

GRATIS - FOR FREE

B

C

D

E

VCORE_CPU11,32

U6-2

D6 D10

VCC0 VCCP0

D8

VCC1

D18

VCC2

D20

VCC3

D22

VCC4

E5

VCC5

4 4

Intel Recommend Option 5

4 X 220UF & 35 X 10UF 0805 X5R

C482 10uF 6.3V 10% 0805 X5R TAIYO

C481 10uF 6.3V 10% 0805 X5R TAIYO

C479 10uF 6.3V 10% 0805 X5R TAIYO

C483 10uF 6.3V 10% 0805 X5R TAIYO

C495 220uF 2.5V 15m ohm 2R5TPE220MF SANYO

C47 220uF 2.5V 15m ohm 2R5TPE220MF SANYO

C494 SP220uF 2V 20% EEFSX0D221YR PANA(NU)

C496 220uF 2.5V 15m ohm 2R5TPE220MF SANYO

+

3 3

2 2

C48 220uF 2.5V 15m ohm 2R5TPE220MF SANYO

+

+

+

+

C512 10uF 6.3V 10% 0805 X5R TAIYO

C446 10uF 6.3V 10% 0805 X5R TAIYO

C51 10uF 6.3V 10% 0805 X5R TAIYO

C484 10uF 6.3V 10% 0805 X5R TAIYO

C508 10uF 6.3V 10% 0805 X5R TAIYO

C510 10uF 6.3V 10% 0805 X5R TAIYO

C513 10uF 6.3V 10% 0805 X5R TAIYO

C511 10uF 6.3V 10% 0805 X5R TAIYO

C50 10uF 6.3V 10% 0805 X5R TAIYO

C447 10uF 6.3V 10% 0805 X5R TAIYO

C445 10uF 6.3V 10% 0805 X5R TAIYO

C477 10uF 6.3V 10% 0805 X5R TAIYO

C478 10uF 6.3V 10% 0805 X5R TAIYO

C509 10uF 6.3V 10% 0805 X5R TAIYO

C42 10uF 6.3V 10% 0805 X5R TAIYO

C456 10uF 6.3V 10% 0805 X5R TAIYO

C454 10uF 6.3V 10% 0805 X5R TAIYO

C41 10uF 6.3V 10% 0805 X5R TAIYO

C52 10uF 6.3V 10% 0805 X5R TAIYO

C458 10uF 6.3V 10% 0805 X5R TAIYO

C455 10uF 6.3V 10% 0805 X5R TAIYO

C444 10uF 6.3V 10% 0805 X5R TAIYO

C40 10uF 6.3V 10% 0805 X5R TAIYO

C453 10uF 6.3V 10% 0805 X5R TAIYO

C476 10uF 6.3V 10% 0805 X5R TAIYO

C448 10uF 6.3V 10% 0805 X5R TAIYO

C449 10uF 6.3V 10% 0805 X5R TAIYO

C480 10uF 6.3V 10% 0805 X5R TAIYO

C457 10uF 6.3V 10% 0805 X5R TAIYO

C443 10uF 6.3V 10% 0805 X5R TAIYO

C452 10uF 6.3V 10% 0805 X5R TAIYO

E7

VCC6

E9

VCC7

E17

VCC8

E19

VCC9

E21

VCC10

F6

VCC11

F8

VCC12

F18

VCC13

F20

VCC14

F22

VCC15

G5

VCC16

G21

VCC17

H6

VCC18

H22

VCC19

J5

VCC20

J21

VCC21

K22

VCC22

U5

VCC23

V6

VCC24

V22

VCC25

W5

VCC26

W21

VCC27

Y6

VCC28

Y22

VCC29

AA5

VCC30

AA7

VCC31

AA9

VCC32

AA11

VCC33

AA13

VCC34

AA15

VCC35

AA17

VCC36

AA19

VCC37

AA21

VCC38

AB6

VCC39

AB8

VCC40

AB10

VCC41

AB12

VCC42

AB14

VCC43

AB16

VCC44

AB18

VCC45

AB20

VCC46

AB22

VCC47

AC9

VCC48

AC11

VCC49

AC13

VCC50

AC15

VCC51

AC17

VCC52

AC19

VCC53

AD8

VCC54

AD10

VCC55

AD12

VCC56

AD14

VCC57

AD16

VCC58

AD18

VCC59

AE9

VCC60

AE11

VCC61

AE13

VCC62

AE15

VCC63

AE17

VCC64

AE19

VCC65

AF8

VCC66

AF10

VCC67

AF12

VCC68

AF14

VCC69

AF16

VCC70

AF18

VCC71

SCKT Foxconn SMT PZ47903-2741-01

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCQ0

VCCQ1

VCCA0

VCCA1

VCCA2

VCCA3

VID0

VID1

VID2

VID3

VID4

VID5

VCCsense

R659 0 5% 1/16W 0402

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L5

L21

M6

M22

N5

N21

P6

P22

R5

R21

T6

T22

U21

P23

W4

F26

VCCA1

B1

VCCA2

N1

VCCA3

AC26

E2

F2

F3

G3

G4

H4

R46

AE7

54.9 1% 1/16W 0603(NU)

C103 0.1uF 16V 10% 0603 X7R

C90 0.1uF 16V 10% 0603 X7R

C100 0.1uF 16V 10% 0603 X7R

Note: Dothan Processor 533MHZ A2

STEP use both 1.8V&1.5V

Dothan Processor 533MHZ B

STEP only use 1.5V

VR_VID0 11

VR_VID1 11

VR_VID2 11

VR_VID3 11

VR_VID4 11

VR_VID5 11

Layout note :

Provide a test point (with no stub) to connect a

differential probe between VCCSENSE and VSSENSE

at the location where the two 54.9ohm resistors

terminate the 55ohm transmission line

Layout note :

VCCSENSE and VSSENSE lines

should be of equal length

C109 0.1uF 16V 10% 0603 X7R

C95 0.1uF 16V 10% 0603 X7R

C110 0.1uF 16V 10% 0603 X7R

C112 10uF 6.3V 10% 0805 X5R TAIYO

C470 0.01uF 16V 10% 0402 X7R

C89 0.1uF 16V 10% 0603 X7R

VCCP9,17,19,20,21,23,30,55

C96 0.1uF 16V 10% 0603 X7R

C104 0.1uF 16V 10% 0603 X7R

C99 0.1uF 16V 10% 0603 X7R

R1120 5% 1/8W 0805

R1110 5% 1/8W 0805(NU)

C521

12

+

T150uF 2V ±20% 18mΩ SMT7343 LOW ESR EEFCD0D151R PANASONIC

1.5VDDM 13,17,19,21,46

1.8VDDM 47,64

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

U6-3

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSSsense

R6

R22

R25

T3

T5

T21

T23

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

AF6

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

SCKT Foxconn SMT PZ47903-2741-01

R47

54.9 1% 1/16W 0603(NU)

One Ground

One Via

1 1

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

CPU ( Dothan ) 2/2

A

B

C

D

Date: Sheet

E

10 64Friday, May 07, 2004

of

0.2

5

hexainf@hotmail.com

GRATIS - FOR FREE

4

3

2

1

T15uF 25V ±20% 90mΩ 7343 25TQC15M SANYO(NU)

T15uF 25V ±20% 90mΩ 7343 25TQC15M SANYO

C872

C886

R1155

T15uF 25V ±20% 90mΩ 7343 25TQC15M SANYO

C874

C873

+

+

U66

30

VDD

10

VCC

4

S0

5

S1

6

S2

1

B0

2

B1

3

B2

26

D0

25

D1

24

D2

23

D3

22

D4

21

D5

7

SHDN#

35

SUS

20

DPSLP#

40

TON

12

CC

36

SYSPOK

38

CLKEN#

37

IMVPOK

11

GND

41

TP

8

REF

9

ILIM

27

DDO#

ASIC MAX1907EGL QFN 40PIN MAXIM

+

VCORE_CPU

F12

DCIN31,46,48,53,55,57

VR_VID010

VR_VID110

VR_VID210

VR_VID310

VR_VID410

VR_VID510

VRON_VCCP46,55

PM_DPRSLPVR20

STPCPU020,23

PM_PSI09

PM_VGATE14,20

VCORE_AGround

FUSE 5A 32V TR/3216FF BUSSMAN

R1129

0 5% 1/16W CF SMT0603

1 2

VCORE_AGround

SUS0

SUS1

SUS2

BOOT0

BOOT1

BOOT2

R1141 0 5% 1/16W CF SMT0603

VCORE_AGround

R1146 0 5% 1/16W 0603(NU)

R1148 0 5% 1/16W 0603

R1149 0 5% 1/16W 0603

R1150 0 5% 1/16W 0603

R1151 10K 5% 1/16W 0603

R1152 10K 5% 1/16W 0603

D D

5VDDM12,21,29,30,31,36,37,40,42,47,54,59,60,61

C C

SYS_PWROK20,34

VCORE_ON55

CK408_PWRGD023

3VDDM13,17,19,20,21,23,24,25,26,29,31,32,34,35,36,37,39,40,41,42,44,54,55,58,59,62,64

B B

DCIN _CPU

>40mil

R1130

10 5% 1/16W 0603

C880

1uF 10V 10% 0805 X7R

R1131 0 5% 1/16W 0603

R1134 0 5% 1/16W 0603

R1135 0 5% 1/16W 0603

R1136 0 5% 1/16W 0603

R1138 0 5% 1/16W 0603

R1140 0 5% 1/16W 0603

1 2

R1142 0 5% 1/16W 0603

R1143 0 5% 1/16W 0603

R1144 0 5% 1/16W 0603(NU)

MAX1907_P40

270pF 50V 5% 0603 NPO

VCORE_AGround need 2 VIA to GND_POWER

MAX1987REF

C887

0.22uF 10V 10% 0603 X7R

100K 1% 1/16W 0603

C888

100pF 50V 5% 0603 NPO

R1157

49.9K 1% 1/16W 0603

MAX1907_P27

C8774.7uF 25V ±10% SMT1206 X5R TMK316BJ475KL-T TAIYO

4.7uF 25V ±10% SMT1206 X5R TMK316BJ475KL-T TAIYO

4.7uF 25V ±10% SMT1206 X5R TMK316BJ475KL-T TAIYO

C876

C875

C878 0.01uF 25V 80-20% 0603 Y5V

34

V+

C881

28

PGND

33

DH

32

LX

29

DL

31

BST

18

CSP

19

CSN

C883 4700pF 50V 10% 0603 X7R

17

OAIN+

16

OAIN-

1.5K 1% 1/16W 0603

15

FB

14

NEG

13

POS

39

TIME

62K 1% 1/16W 0603

Q102

M-FET-N FDD6690A 30V 46A TO-252 3PIN FAIRCHILD

DGS

>40mil

Q103

G

G

>40mil

PN

D90

2.2uF 10V 10% 0805 X7R

DIODE STKY CH751H-40 40V 0.03A SOD-323 CHENMKO

C882

0.1uF 50V 10% 0805 X7R

R1137 200 5% 1/10W 0603

R1139

200 5% 1/10W 0603

R1145

C885

100pF 50V 5% 0603 NPO

R1147

2.74K 1% 1/8W 0805

R1154

100K 1% 1/16W 0603

R1156

VCORE_AGround

0.62uH 30A SPM12550T-R62M300 ±20% TDK

TR M-FET-N FDD6688 84A 30V TO252 FAIRCHILD

DS

D

S

TR M-FET-N FDD6688 84A 30V TO252 FAIRCHILD

DS

D

Q104

G

G

>40mil

D88

S

P N

DIODE 3A 30V EC31QS03L NIEC

RES 1mΩ 5% 2W MF SMT7520 RL7520WT-R003-J CYNTEC

L89

VCORE_AGround

R1128

Kelvin connections

R1132

750 1% 1/16W 0603

C884

NU_470pF 50V 5% 0603 NPO

R1153 0 5% 1/16W 0603

1K 1% 1/16W 0603

R1133

For CPU

Tolerance :Static:±20mV Ripple:±30mV

Voutput:0.700~1.708 step16mV

Load line slope:3mV/A

Max Current : 25A

DIODE ZENER RLZ2.4B 2.53V 0.02A 4% 0.4W

D89

C879 1uF +80-20% 16V 0805 Y5V(NU)

VCORE_CPU 10,32

Vsus:0.748V

R1158

SUS1

SUS2

SUS0

VCORE_AGround

VCORE_AGround

4

VCORE_AGround

5VDDM12,21,29,30,31,36,37,40,42,47,54,59,60,61

A A

5

VCORE_AGround

0 5% 1/16W 0603

R1160

0 5% 1/16W 0603

R1162

0 5% 1/16W 0603(NU)

Vboot:1.196V

R1159

0 5% 1/16W 0603

R1161

0 5% 1/16W 0603

MAX1987REF BOOT2

R1163

0 5% 1/16W 0603(NU)

BOOT0

BOOT1

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

Vcore

3

2

Date: Sheet

1

11 64Friday, May 07, 2004

of

0.2

8

hexainf@hotmail.com

GRATIS - FOR FREE

7

6

5

4

3

2

1

3VDDS19,26,32,33,34,35,37,43,44,45,46,54,60

THERMAL SENSOR

D D

3VDDS19,26,32,33,34,35,37,43,44,45,46,54,60

R964

10K 5% 1/16W 0402

R965 0 5% 1/16W 0402

C C

Trace=10mil and together

QSMCLK_PMU35

QSMDAT_PMU35

HOT_DOWN 45,48

3VDDS19,26,32,33,34,35,37,43,44,45,46,54,60

1K 5% 1/16W 0402

R124 200 5% 1/16W 0603

C 0.1uF 16V 80-20% 0402 Y5V

R113

R119

C115

10K 5% 1/16W 0402

R117

10K 5% 1/16W 0402

10mil

Thermal Power Consumption:

Icc: Max 180uA

Icc stdby: Max 10uA

Address:1001 110X

U7

LNR-IC GMTG767 SSOP 16PIN GMT

14

SCLK

12

SDATA

11

ALERT#

15

STBY#

1

TEST

16

TEST

2

VDD

ADD1

ADD0

6

10

3

D+

4

D-

5

NC

9

NC

13

NC

7

GND

8

GND

NC_767_5NC_767_1

NC_767_9NC_767_16

NC_767_13

R970 1K 5% 1/16W 0402

trace10mil and together

C114

2200pF 50V 10% 0402 X7R

AT=2200PF SHOULD BE PLACED

AS CLOSE AS POSSIBLE TO THE G767

3VDDS 19,26,32,33,34,35,37,43,44,45,46,54,60

THERMDA 9

THERMDC 9

1.Far away the CRT,clock generator,memory bus,PCI bus.

2.As close CPU as possible.

10 mil

10 mil

10 mil

MINIMUM

10 mil

GND

THERMDA

THERMDC

GND

B B

Fan control

20mil

R978 0 5% 1/16W CF SMT0603

R671

1 2

1 2

1 2

0 5% 1/16W CF SMT0603

5VDDM11,21,29,30,31,36,37,40,42,47,54,59,60,61

FAN_ON20

Hi_On Low_Off

Hi_High Speed Low_Low Speed

Hi_4.6V Low_3.6V

A A

8

FAN_CTRL20

0 5% 1/16W CF SMT0603

7

R679

G

1uF 10V +80-20% 0603 Y5V

C523

R1010

10K 1% 1/16W 0603

G

DS

Q97

TR M-FET-N 2N7002E 60V 190mA SOT-23 SILICONIX

U39

1 5

IN OUT

3

SHDN

4

ADJ

2

GND

LNR-IC G916T1U ADJ SOT23-5 5PIN GMT

R669 33K 5% 1/16W 0603

DS

TR M-FET-N 2N7002E 60V 190mA SOT-23 SILICONIX

6

R980560 5% 1/16W 0603

Q57

R676

15K 1% 1/16W 0603

R981

120 5% 1/16W 0603

R670

5.6K 5% 1/16W 0603

5

20mil

R979 0 5% 1/16W 0603

C522

1uF 10V +80-20% 0603 Y5V

Vout

R1

R2

GND

Vout=Vref(1+R1/R2)

FB

R1=R2(Vout/Vref-1)

G916 Vref=1.25V

4

CN14

1

1

2

2

CON ENTERY W-B SMT 2PIN P=1.25 3801-02-1

20-24902-00

3

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

Thermal / FAN CNN

Date: Sheet

2

of

12 64Friday, May 07, 2004

1

0.2

5

hexainf@hotmail.com

GRATIS - FOR FREE

4

3

1.5VDDM10,17,19,21,46

2

1

D D

MCH_CLK_3GPLL023

MCH_CLK_3GPLL23

TV_DACA_OUT29

TV_DACB_OUT29

TV_DACC_OUT29

Note:

CRT_Red,CRT_Green,CRT_Blue

are groud reference

C C

B B

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

R188150 1% 1/16W 0402

R186150 1% 1/16W 0402

R177150 1% 1/16W 0402

VECLK29

VEDAT29

BLUE29

GREEN29

RED29

VSYNC29

HSYNC29

R721 39 1% 1/16W 0603

R720 39 1% 1/16W 0603

R734 255 1% 0402

10 mil

LVDS_ENALCD31

LVDS_ENABKL31,41

LCD_BRIGHTNESS31

DDC_PDATA31

DDC_PCLK31

LVDS_TXCLK_LN31

LVDS_TXCLK_LP31

LVDS_TXOUT_L2P31

LVDS_TXOUT_L1P31

LVDS_TXOUT_L0P31

LVDS_TXOUT_L2N31

LVDS_TXOUT_L1N31

LVDS_TXOUT_L0N31

NC_ALVISO_H24

NC_ALVISO_H25

R715

4.99K 1% 1/16W MF SMT0603

R705150 1% 1/16W 0402

R708150 1% 1/16W 0402

R710150 1% 1/16W 0402

10 mil

10 mil

R722

0 5% 1/16W 0402(NU)

LCTLA_CLK

LCTLB_DATA

NC_LVDS_TXCLK_UN

NC_LVDS_TXCLK_UP

NC_LVDS_TXOUT_U2P

NC_LVDS_TXOUT_U1P

NC_LVDS_TXOUT_U0P

NC_LVDS_TXOUT_U2N

NC_LVDS_TXOUT_U1N

NC_LVDS_TXOUT_U0N

TVREF

LIBG

NC_LVDS_LVBG

NC_LVDS_REFH

NC_LVDS_REFL

U10A

H24

SDVOCTRL_DATA

H25

SDVOCTRL_CLK

AB29

GCLKN

AC29

GCLKP

A15

TVDAC_A

C16

TVDAC_B

A17

TVDAC_C

J18

TV_REFSET

B15

TV_IRTNA

B16

TV_IRTNB

B17

TV_IRTNC

E24

DDCACLK

E23

DDCADATA

E21

BLUE

D21

BLUE#

C20

GREEN

B20

GREEN#

A19

RED

B19

RED#

H21

VSYNC

G21

HSYNC

J20

REFSET

C33

LIBG

C31

LVBG

F28

LVREFH

F27

LVREFL

F26

LVDDEN

F25

PANELBKLTEN

E25

PANELBKLTCTL

F22

DDCPDATA

F23

DDCPCLK

C23

LCTLACLK

C22

LCTLBDATA

B30

ICLKAN

B29

ICLKAP

C25

ICLKBN

C24

ICLKBP

C26

LBDATAP2

D27

LBDATAP1

C28

LBDATAP0

C27

LBDATAN2

D28

LBDATAN1

C29

LBDATAN0

B31

LADATAP2

A33

LADATAP1

A34

LADATAP0

B32

LADATAN2

B33

LADATAN1

B34

LADATAN0

ASIC ALVIO GMCH FCBGA 1257PIN INTEL

LVDS

D36

EXP_COMPI

D34

EXP_ICOMPO

E30

EXP_RXN0

MISC

TV

VGA

PCI-EXPRESS GRAPHICS

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

NC_PEG_RXN0

NC_PEG_RXN1

NC_PEG_RXN2

NC_PEG_RXN3

NC_PEG_RXN4

NC_PEG_RXN5

NC_PEG_RXN6

NC_PEG_RXN7

NC_PEG_RXN8

NC_PEG_RXN9

NC_PEG_RXN10

NC_PEG_RXN11

NC_PEG_RXN12

NC_PEG_RXN13

NC_PEG_RXN14

NC_PEG_RXN15

NC_PEG_RXP0

NC_PEG_RXP1

NC_PEG_RXP2

NC_PEG_RXP3

NC_PEG_RXP4

NC_PEG_RXP5

NC_PEG_RXP6

NC_PEG_RXP7

NC_PEG_RXP8

NC_PEG_RXP9

NC_PEG_RXP10

NC_PEG_RXP11

NC_PEG_RXP12

NC_PEG_RXP13

NC_PEG_RXP14

NC_PEG_RXP15

NC_PEG_TXN0

NC_PEG_TXN1

NC_PEG_TXN2

NC_PEG_TXN3

NC_PEG_TXN4

NC_PEG_TXN5

NC_PEG_TXN6

NC_PEG_TXN7

NC_PEG_TXN8

NC_PEG_TXN9

NC_PEG_TXN10

NC_PEG_TXN11

NC_PEG_TXN12

NC_PEG_TXN13

NC_PEG_TXN14

NC_PEG_TXN15

NC_PEG_TXP0

NC_PEG_TXP1

NC_PEG_TXP2

NC_PEG_TXP3

NC_PEG_TXP4

NC_PEG_TXP5

NC_PEG_TXP6

NC_PEG_TXP7

NC_PEG_TXP8

NC_PEG_TXP9

NC_PEG_TXP10

NC_PEG_TXP11

NC_PEG_TXP12

NC_PEG_TXP13

NC_PEG_TXP14

NC_PEG_TXP15

R745

24.9 1% 1/16W MF 0603

R739

LIBG

1.5K 1% 1/16W 0402

A A

5

4

2.5VDDM14,17,21,29,31,47,62 2.5VDDM14,17,21,29,31,47,62

R743

R732

2.2K 1% 1/16W 0603

LCTLA_CLK LCTLB_DATA

3

3VDDM11,17,19,20,21,23,24,25,26,29,31,32,34,35,36,37,39,40,41,42,44,54,55,58,59,62,64 3VDDM11,17,19,20,21,23,24,25,26,29,31,32,34,35,36,37,39,40,41,42,44,54,55,58,59,62,64

10K 5% 1/16W 0402

R741

G

M-FET-N 2N7002 60V 115MA TO-236AB

2.2K 1% 1/16W 0603

Q59

L_CLKCTLA

DS

L_CLKCTLA 23,31

2.2K 1% 1/16W 0603

R731

2

R742

10K 5% 1/16W 0402

G

Q58

M-FET-N 2N7002 60V 115MA TO-236AB

DS

R740

2.2K 1% 1/16W 0603

L_CLKCTLB

L_CLKCTLB 23,31

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

ALVISO(LVDS/PCIE/VGA/TV/MISC) 0.2

Date: Sheet

1

13 64Friday, May 07, 2004

of

5

hexainf@hotmail.com

GRATIS - FOR FREE

4

3

2

1

For ITP Port used only

VCCP_GMCH16,17,18

R695

R694 0 5% 1/16W 0402(NU)

R700 10K 5% 1/16W 0402

D D

DMI_TXN[3..0]19

DMI_TXP[3..0]19

DMI_RXN[3..0]19

DMI_RXP[3..0]19

MGH_SMCLK_DDR024

MGH_SMCLK_DDR124

MGH_SMCLK_DDR325

MGH_SMCLK_DDR425

MGH_SMCLK_DDR0024

MGH_SMCLK_DDR1024

R719 40.2 1% 1/16W 0603

MGH_SMCLK_DDR3025

MGH_SMCLK_DDR4025

2.5VDDM13,17,21,29,31,47,62

DDR_1.8VDDS17,24,44,46,47

MGH_SM_CKE024

MGH_SM_CKE124

MGH_SM_CKE225

MGH_SM_CKE325

MGH_SM_CS0024

MGH_SM_CS1024

MGH_SM_CS2024,25

MGH_SM_CS3024,25

M_OCDCOMP0

M_OCDCOMP1

MCH_ODT024

MCH_ODT124

R714 40.2 1% 1/16W 0603

MCH_ODT225

MCH_ODT325

C C

Laout note:

Route as short as possible

Laout note:

Route as short as possible

B B

A A

DDR_VREF24,25,46

R690

80.6 1% 0603

R691

80.6 1% 0603

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

NC_ALVISO_AE11

NC_ALVISO_AC10

NC_ALVISO_AE10

NC_ALVISO_AD10

MGH_RCOMP0

MGH_RCOMP

MGH_SMXSLEW

MGH_SMYSLEW

R730

10K 5% 1/16W 0402

R733

10K 5% 1/16W 0402

MGH_RCOMP0

MGH_RCOMP

AA31

AB35

AC31

AD35

AA35

AB31

AC35

AA33

AB37

AC33

AD37

AA37

AB33

AC37

AM33

AE11

AC10

AN33

AE10

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AM11

AN10

AK10

AK11

AF37

AE27

AE28

AF10

PM_EXTTS00

PM_EXTTS10

CFG7

(CPU Strap) LOW=DT/Transportable CPU

U10B

DMIRXN0

DMIRXN1

DMIRXN2

DMIRXN3

Y31

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN0

DMITXN1

DMITXN2

DMITXN3

Y33

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

AL1

SM_CK1

SM_CK2

AJ34

SM_CK3

AF6

SM_CK4

SM_CK5

SM_CK0#

AK1

SM_CK1#

SM_CK2#

AJ33

SM_CK3#

AF5

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

AL15

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

AD1

SMVREF1

SMXSLEWIN

SMXSLEWOUT

AF9

SMYSLEWIN

SMYSLEWOUT

ASIC ALVIO GMCH FCBGA 1257PIN INTEL

CFG5 LOW=DMIx2

HIGH=Mobile CPU

DDR MUXING

CFG5

HIGH=DMIx4

CFG7

DMI

CFG/RSVD

PM

CLKS

NC

R711

2.2K 5% 1/16W 0402(NU)

CFG9

Graphics

Lane

R190

2.2K 5% 1/16W 0402(NU)

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

DREFCLKN

DREFCLKP

DREF_SSCLKN

DREF_SSCLKP

NC10

CFG6

LOW=Reverse LanePCIE

HIGH=Normal

operation

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

100 1% 1/16W 0402

A24

A23

C37

D37

NC_ALVISO_AP37

AP37

NC_ALVISO_AN37

AN37

NC_ALVISO_AP36

AP36

NC_ALVISO_AP2

AP2

NC_ALVISO_AP1

AP1

NC_ALVISO_AN1

AN1

NC_ALVISO_B1

B1

NC_ALVISO_A2

A2

NC_ALVISO_B37

B37

NC_ALVISO_A36

A36

NC_ALVISO_A37

A37

CFG6

LOW=DDR2(DDR Strap)

NC=DDR

CFG9

CFG0

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

PM_EXTTS00

PM_EXTTS10

R727

0 5% 1/16W 0402(NU)

T13

1

T14

1

T15

1

T16

1

T17

1

T18

1

T19

1

T20

1

T21

1

T22

1

T23

1

T24

1

T25

1

T26

1

T27

1

T28

1

T29

1

T30

1

T31

1

T32

1

T33

1

T34

1

T35

1

T36

1

T37

1

T38

1

T39

1

T40

1

PM_BMBUSY0 20

PM_EXTTS00

THRMTRIP0 9,20

PM_VGATE 11,20

PLT_RST0 19,36,39

MCH_DREFCLK0 23

MCH_DREFCLK 23

MCH_SSCLK0 23

MCH_SSCLK 23

R174

2.2K 5% 1/16W 0402

CFG16

(FSB

Dynamic

ODT)

R699

2.2K 5% 1/16W 0402

AGTL+_BPM20 9,30

AGTL+_BPM10 9,30

MCH_BSEL1 23

MCH_BSEL0 23

CFG16

LOW=DT/Transportable CPU

HIGH=Mobile CPU

CFG[2:0] 10k ohms pull up or

pull down or direct connect

form processor

2.5VDDM13,17,21,29,31,47,62

LOW=1.05V

CFG18

HIGH=1.5V

(VCC SEL)

R712

2.2K 5% 1/16W 0402(NU)

CFG18

2.5VDDM13,17,21,29,31,47,62

LOW=1.05VCFG19

HIGH=1.2V

(VTT SEL)

CFG19

R726

1K 5% 1/16W 0402(NU)

R723

1K 5% 1/16W 0402(NU)

5

CFG[17:3] have internal pullup resistors

CFG[19:18] have internal pulldwon resistors

4

3

2

FIC International Computer, Inc.

7FL.,NO266,SEC.1,WENHWA 2nd RD. LINKOU HSIANG,

244 TAIPEI, TAIWAN,ROC

(886-2)2600-8818

Title

PS1(MD34)

Size Document Number Rev

C

ALVISO(DMI/CLK/PM) 0.2

Date: Sheet

1

14 64Friday, May 07, 2004

of

5

hexainf@hotmail.com

GRATIS - FOR FREE

4

3

2

1

D D

SMA_DATA[63..0]24

C C

B B

SMA_DATA0

SMA_DATA1

SMA_DATA2

SMA_DATA3

SMA_DATA4

SMA_DATA5

SMA_DATA6

SMA_DATA7

SMA_DATA8

SMA_DATA9

SMA_DATA10

SMA_DATA11

SMA_DATA12

SMA_DATA13

SMA_DATA14

SMA_DATA15

SMA_DATA16

SMA_DATA17

SMA_DATA18

SMA_DATA19

SMA_DATA20

SMA_DATA21

SMA_DATA22

SMA_DATA23

SMA_DATA24

SMA_DATA25

SMA_DATA26

SMA_DATA27

SMA_DATA28

SMA_DATA29

SMA_DATA30

SMA_DATA31

SMA_DATA32

SMA_DATA33

SMA_DATA34

SMA_DATA35

SMA_DATA36

SMA_DATA37

SMA_DATA38

SMA_DATA39

SMA_DATA40

SMA_DATA41

SMA_DATA42

SMA_DATA43

SMA_DATA44

SMA_DATA45

SMA_DATA46

SMA_DATA47

SMA_DATA48

SMA_DATA49

SMA_DATA50

SMA_DATA51

SMA_DATA52

SMA_DATA53

SMA_DATA54

SMA_DATA55

SMA_DATA56

SMA_DATA57

SMA_DATA58

SMA_DATA59

SMA_DATA60

SMA_DATA61

SMA_DATA62

SMA_DATA63

U10C

AG35

SADQ0

AH35

SADQ1

AL35

SADQ2

AL37

SADQ3

AH36

SADQ4

AJ35

SADQ5

AK37

SADQ6

AL34

SADQ7

AM36

SADQ8

AN35

SADQ9

AP32

SADQ10

AM31

SADQ11

AM34

SADQ12

AM35

SADQ13

AL32

SADQ14

AM32

SADQ15

AN31

SADQ16

AP31

SADQ17

AN28

SADQ18

AP28

SADQ19

AL30

SADQ20

AM30

SADQ21

AM28

SADQ22

AL28

SADQ23

AP27

SADQ24

AM27

SADQ25

AM23

SADQ26

AM22

SADQ27

AL23

SADQ28

AM24

SADQ29

AN22

SADQ30

AP22

SADQ31

AM9

SADQ32

AL9

SADQ33

AL6

SADQ34

AP7

SADQ35

AP11

SADQ36

AP10

SADQ37

AL7

SADQ38

AM7

SADQ39

AN5

SADQ40

AN6

SADQ41

AN3

SADQ42

AP3

SADQ43

AP6

SADQ44

AM6

SADQ45

AL4

SADQ46

AM3

SADQ47

AK2

SADQ48

AK3

SADQ49

AG2

SADQ50

AG1

SADQ51

AL3

SADQ52

AM2

SADQ53

AH3

SADQ54

AG3

SADQ55

AF3

SADQ56

AE3

SADQ57

AD6

SADQ58

AC4

SADQ59

AF2

SADQ60

AF1

SADQ61

AD4

SADQ62

AD5

SADQ63

ASIC ALVIO GMCH FCBGA 1257PIN INTEL

SARCVENOUT#

DDR SYSTEM MEMORY A

SADQS0

SADQS1

SADQS2

SADQS3

SADQS4

SADQS5

SADQS6

SADQS7

SADQS0#

SADQS1#

SADQS2#

SADQS3#

SADQS4#

SADQS5#

SADQS6#

SADQS7#

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_A13

SADM0

SADM1

SADM2

SADM3

SADM4

SADM5

SADM6

SADM7

SABS0#

SABS1#

SABS2#

SARAS#

SACAS#

SAWE#

SARCVENIN#

SMA_SBS00 24

SMA_SBS10 24

SMA_SBS20 24

SMA_SRAS0 24

SMA_SCAS0 24

SMA_SWE0 24

SMA_SDQS[7..0] 24

SMA_SDQSN[7..0] 24