Page 1

5

4

3

2

1

First International Computer,Inc

HW Design Team II

D D

Page Description

PAGE 01 Title

Board name : Mother Board Schematic

Project Code : P09110

PAGE 02 Block diargram

PAGE 03 CPU DMI/PEG/FDI (1)

PAGE 04 CPU CLK/MISC/JTAG (2)

PAGE 05 CPU DDR3 (3)

PAGE 06 CPU POWER (4)

Project : PCA50D (Calpella Platform)

PAGE 07 CPU Graphic Power (5)

PAGE 08 CPU Ground (6)

Version : 0.2

C C

Initial Date :

PAGE 09 CPU Reserved (7)

PAGE 10 Thermal/Fan Control

PAGE 11 Clock Generator

PAGE 12 DDR3 SDRAM SO-DIMM0

PAGE 13 DDR3 SDRAM SO-DIMM1

PAGE 14 PCH HDA/JTAG/SATA (1)

PAGE 15 PCH PCI-E/SMBUS/CLK (2)

PAGE 16 PCH DMI/FDI/GPIO (3)

PAGE 17 PCH LVDS/DDI (4)

PAGE 18 PCH PCI/USB/NVRAM (5)

PAGE 19 PCH GPIO/NCTF/RSVD (6)

PAGE 20 PCH POWER (7)

PAGE 21 PCH POWER (8)

PAGE 22 PCH Ground (9)

PAGE 23 Reset Circuit

B B

Leader Sign by: Jimmy Chang

PAGE 24 M92-M2 PCIE Graphic (1)

PAGE 25 M92-M2 Main IO (2)

PAGE 26 M92-M2 DP Power (3)

Drawing by : Sam Hong

PAGE 27 M92-M2 Ground (4)

PAGE 28 M92-M2 Power (5)

PAGE 29 M92-M2 Memory I/F (6)

Total confirm by:

PAGE 30 Switchable Graphic MUX

PAGE 31 Graphic Memory GDDR# A

PAGE 32 Graphic Memory GDDR# B

PAGE 33 LVDS /LCD CNN

PAGE 34 CRT

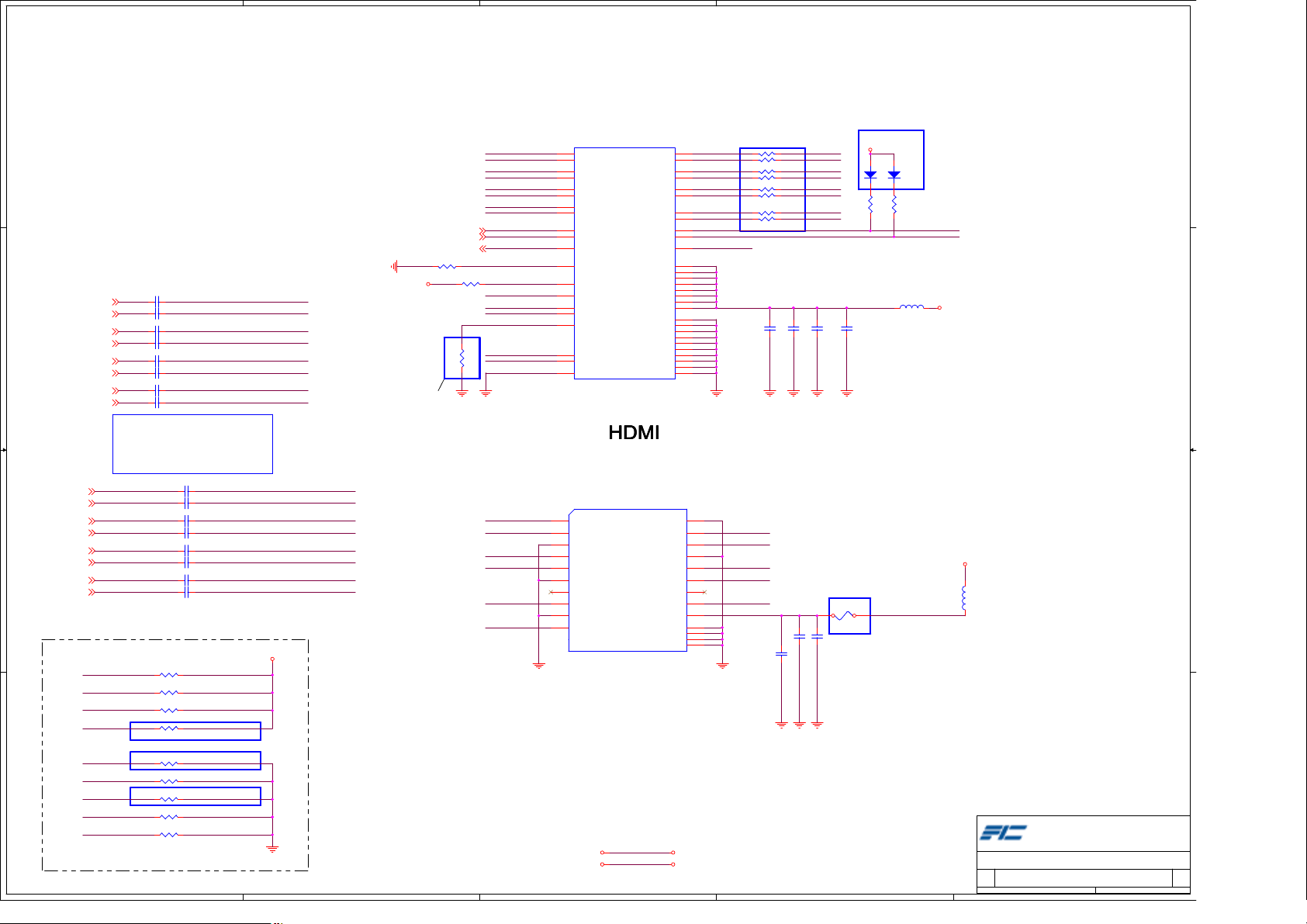

PAGE 35 HDMI CNN

PAGE 36 Card Reader AU6433-GEF

PAGE 37 Audio ALC 272 + APA2068

PAGE 38 Audio CN /Int. Speaker

PAGE 39 LAN RTL 8103EL/8111DL

PAGE 40 Transfomer

PAGE 41 NEW CARD ( Express Card)

PAGE 42 Mini Card (Wirless LAN)

PAGE 43 Mini Card (HSDPA)

PAGE 44 USB/eSATA+USB

PAGE 45 HDD /ODD /Int. KB /SW

PAGE 46 WEB-CAM /BT /MDC /MMB

PAGE 47 Led /LID /GLIDE PAD

PAGE 48 EC IT8512E

PAGE 49 Power Block

PAGE 50 ACIN /BATIN / DCIN

PAGE 51 Charger

PAGE 52 3/5 VDDA/S/M

PAGE 53 1.5VDDS/M 0.75 VDDS

PAGE 54 1.1VDDM_VTT/1.05VDDM

PAGE 55 CPU Core Power

PAGE 56 Gfx VGA Power

PAGE 57 VGA_CORE / 1.8vddm

PAGE 58 DB USB /RJ11 Board

PAGE 59 DB PWRBTN Board

PAGE 58 DB MMB Board

A A

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

(886-2) 8751-8751

PCA50D (Intel Calpella +AMD GPU M92-M)

Title(P09110)

1

1 60Wednesday, August 19, 2009

0.2

Page 2

5

4

3

2

1

PCA50D Block Diagram :

CH. A

CH. B

<512Kbit>

SPI Flash

VBIOS

PCIE Graphics x16

CKD Supports Gen 2

ARD Supports Gen 1 ONLY

ATI

M92 M2 /962pin

/M96LP

MUX

R/G /B

H / VSYNC

DDC

Data Pair x 3

CLK Pair x 1

CTL Signals

MUX

Main Link x 4

Auxiliary

HPD

Data Pair x 3

CLK Pair x 1

CTL Signals

L P C

L P C

L P CL P C

G1 Socket/rPGA 988 Pin

Arrandale ONLY

R/G /B

H / VSYNC

DDC

TMDS x 4

DDC

HPD

Intel

Clarksfield / Arrandale

Processor

F D I

F D I

F D I F D I

C R T

C R T

C R TC R T

dGPU_SELx#

P E C I

P E C I

P E C IP E C I

DMI *4

Banndwidth 2G

(TX 1G,RX 1G)

S A T A

S A T A

S A T AS A T A

Intel

U S B

U S B

Ibex Peak - M

L V D S

L V D S

L V D S L V D S

C h a n n e l A

C h a n n e l A

C h a n n e l AC h a n n e l A

PCH

FCBGA

27mm x 25 mm

1071 Pin

D D I

D D I

D D I D D I

P o r t C

P o r t C

P o r t CP o r t C

S P I

S P I

S P IS P I

U S BU S B

M E

M E

M EM E

P C I E

P C I E

P C I EP C I E

H D A

H D A

H D AH D A

Dual Channel DDR3 @ 1.5V

CKD Supports DDR3 800/1067/1333

ARD Supports DDR3 800/1067 ONLY

S A T A G e n 1 & G e n 2

S A T A G e n 1 & G e n 2

S A T A G e n 1 & G e n 2S A T A G e n 1 & G e n 2

BT

Module

U S B 1 . 0 / 2 . 0

U S B 1 . 0 / 2 . 0

U S B 1 . 0 / 2 . 0U S B 1 . 0 / 2 . 0

USB CONN USB CONN

U S B 1 . 0 / 2 . 0

U S B 1 . 0 / 2 . 0

U S B 1 . 0 / 2 . 0U S B 1 . 0 / 2 . 0

MINI CARD

Half Size

FP

Module

EXPRESS

CARD

P C I E G e n 1

P C I E G e n 1

P C I E G e n 1P C I E G e n 1

Port 9

Port 12

Port 3 Port 1Port 2

G D D R 3

G D D R 3

G D D R 3G D D R 3

32x32Mb

D D

G D D R 3

G D D R 3

G D D R 3G D D R 3

32x32Mb

G D D R 3

G D D R 3

G D D R 3G D D R 3

32x32Mb

G D D R 3

G D D R 3

G D D R 3G D D R 3

32x32Mb

CRT

D-Sub 15 Pin

C C

M96 ONLY

MUX

LVDS To

Panel

Aspect Ratio 16:9

1366 x 768

HDMI

CONNECTOR

B B

IMVP 6.5

VCORE_CPU &

VCORE_iGPU

S O D I M M 1

S O D I M M 0

S O D I M M 0

S O D I M M 0S O D I M M 0

Port 0 Port 4 Port 5

H D D

H D D

H D DH D D

Port 10 Port 11

<HSDPA><WiFi>

Port 4

Realtek

RTL8103EL

RTL8111DL

S O D I M M 1

S O D I M M 1S O D I M M 1

O D D

O D D

O D DO D D

Port 4Port 8Port 5 Port 3

MINI CARD

Full Size

SIM Card

CONN

E-SATA

& USB

Port 0

Port 2

WEB-CAM

Digital MIC

ALCOR

AU6433-GEF

QFN 28 Pin

3 IN 1

CardReader

LQFP 48 Pin

EC / KBC

ITE IT8512

LQFP 128 Pin

S P I

G l id e

G l i d e

G l i d eG l i d e

P a d

P a d

P a dP a d

P S 2S M B / I N T

P S 2P S 2

S M B / I N T M A T R I X

A A

S M B / I N TS M B / I N T

M M B

M M BM M B

5

M A T R I X

M A T R I XM A T R I X

I n t . K B

I n t . K BM M B

I n t . K BI n t . K B

SPI Flash

EC

<2MB>

4

S P IP S 2

S P IS P I

SPI Flash

ME F/W & BIOS

<4MB>

E x t . M i c I n

E x t . M i c I nE x t . M i c I n

Audio Codec

Realtek

ALC272

H P

H PE x t . M i c I n

H PH P

3

Ext. AMP

APA2030

RJ-45 CONN

MDC RJ-11 CONN

I n t . S p e a k e r

I n t . S p e a k e r

I n t . S p e a k e rI n t . S p e a k e r

1 . 5 W x 2

1 . 5 W x 2

1 . 5 W x 21 . 5 W x 2

2

D i g i t a l M i c

D i g i t a l M i c

D i g i t a l M i cD i g i t a l M i c

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet of

(886-2) 8751-8751

PCA50D (Intel Calpella +AMD GPU M92-M)

Block Diagram(P09110)

1

2 60Wednesday, August 19, 2009

0.2

Page 3

5

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L DA R R A N D A L E / C L A R K F I E L D

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

D D

DMI_TXN0[16]

DMI_TXN1[16]

DMI_TXN2[16]

DMI_TXN3[16]

DMI_TXP0[16]

DMI_TXP1[16]

DMI_TXP2[16]

DMI_TXP3[16]

DMI_RXN0[16]

DMI_RXN1[16]

DMI_RXN2[16]

DMI_RXN3[16]

DMI_RXP0[16]

DMI_RXP1[16]

DMI_RXP2[16]

C C

To PCH (P2P)

Refer to PDG P.79

Arrandale

ONLY

B B

DMI_RXP3[16]

FDI_TXN[7:0][16]

FDI_TXP[7:0][16]

FDI_FSYNC0[16]

FDI_FSYNC1[16]

FDI_INT[16]

FDI_LSYNC0[16]

FDI_LSYNC1[16]

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

4

D M I , P E G , F D I

D M I , P E G , F D I

D M I , P E G , F D I

D M I , P E G , F D I

(

(

(

(

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

U13A

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

mPGA989B

DMI Intel(R) FDI

PCI EXPRESS -- GRAPHICS

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

3

)

)

)

)

All COMP use 10-mils trace width for routing less than 500 mils,

or 20-mils trace width for routing between 500 and 1000 mils;

Keep 20-mils spacing to other signals to minimize crosstalk

PEG_IRCOMP_R

EXP_RBIAS

CPU_PEG_TXN15

CPU_PEG_TXN14

CPU_PEG_TXN13

CPU_PEG_TXN12

CPU_PEG_TXN11

CPU_PEG_TXN10

CPU_PEG_TXN9

CPU_PEG_TXN8

CPU_PEG_TXN7

CPU_PEG_TXN6

CPU_PEG_TXN5

CPU_PEG_TXN4

CPU_PEG_TXN3

CPU_PEG_TXN2

CPU_PEG_TXN1

CPU_PEG_TXN0

CPU_PEG_TXP15

CPU_PEG_TXP14

CPU_PEG_TXP13

CPU_PEG_TXP12

CPU_PEG_TXP11

CPU_PEG_TXP10

CPU_PEG_TXP9

CPU_PEG_TXP8

CPU_PEG_TXP7

CPU_PEG_TXP6

CPU_PEG_TXP5

CPU_PEG_TXP4

CPU_PEG_TXP3

CPU_PEG_TXP2

CPU_PEG_TXP1

CPU_PEG_TXP0

R127 49.9Ω 1% 1/16W SMT0402 LR

R126 RES 750Ω 1% 1/16W SMT0402 LR

C179 0.1uF 10V 10% SMT0402 X5R LR

C174 0.1uF 10V 10% SMT0402 X5R LR

C176 0.1uF 10V 10% SMT0402 X5R LR

C169 0.1uF 10V 10% SMT0402 X5R LR

C164 0.1uF 10V 10% SMT0402 X5R LR

C161 0.1uF 10V 10% SMT0402 X5R LR

C159 0.1uF 10V 10% SMT0402 X5R LR

C152 0.1uF 10V 10% SMT0402 X5R LR

C146 0.1uF 10V 10% SMT0402 X5R LR

C144 0.1uF 10V 10% SMT0402 X5R LR

C125 0.1uF 10V 10% SMT0402 X5R LR

C142 0.1uF 10V 10% SMT0402 X5R LR

C123 0.1uF 10V 10% SMT0402 X5R LR

C140 0.1uF 10V 10% SMT0402 X5R LR

C121 0.1uF 10V 10% SMT0402 X5R LR

C138 0.1uF 10V 10% SMT0402 X5R LR

C178 0.1uF 10V 10% SMT0402 X5R LR

C170 0.1uF 10V 10% SMT0402 X5R LR

C173 0.1uF 10V 10% SMT0402 X5R LR

C167 0.1uF 10V 10% SMT0402 X5R LR

C162 0.1uF 10V 10% SMT0402 X5R LR

C160 0.1uF 10V 10% SMT0402 X5R LR

C153 0.1uF 10V 10% SMT0402 X5R LR

C147 0.1uF 10V 10% SMT0402 X5R LR

C136 0.1uF 10V 10% SMT0402 X5R LR

C143 0.1uF 10V 10% SMT0402 X5R LR

C124 0.1uF 10V 10% SMT0402 X5R LR

C141 0.1uF 10V 10% SMT0402 X5R LR

C122 0.1uF 10V 10% SMT0402 X5R LR

C139 0.1uF 10V 10% SMT0402 X5R LR

C120 0.1uF 10V 10% SMT0402 X5R LR

C137 0.1uF 10V 10% SMT0402 X5R LR

PEG_RXN15

PEG_RXN14

PEG_RXN13

PEG_RXN12

PEG_RXN11

PEG_RXN10

PEG_RXN9

PEG_RXN8

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP15

PEG_RXP14

PEG_RXP13

PEG_RXP12

PEG_RXP11

PEG_RXP10

PEG_RXP9

PEG_RXP8

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

PEG_TXN15

PEG_TXN14

PEG_TXN13

PEG_TXN12

PEG_TXN11

PEG_TXN10

PEG_TXN9

PEG_TXN8

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP15

PEG_TXP14

PEG_TXP13

PEG_TXP12

PEG_TXP11

PEG_TXP10

PEG_TXP9

PEG_TXP8

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

2

PEG_RXN[15:0] [24]

PEG_RXP[15:0] [24]

PEG_TXN[15:0] [24]

PEG_TXP[15:0] [24]

To ATI M92/96 (P2P)

PEG Lane Numbers Reversed

Refer to PDG P.59

Lane Reversal :

CFG3 have to Pull-Down

Pls refer P.9

1

A A

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

(886-2) 8751-8751

PCA50D (Intel Calpella +AMD GPU M92-M)

PROCESSOR DMI/PGE/FDI(P09110)

1

3 60Wednesday, August 19, 2009

0.2

Page 4

5

4

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L DA R R A N D A L E / C L A R K F I E L D

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

C L K , M I S C , J T A G

C L K , M I S C , J T A G

C L K , M I S C , J T A G

C L K , M I S C , J T A G

(

(

(

(

3

)

)

)

)

2

1

D D

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_CATERR#

Layout note:Zo=50 ohm,

15'' max for PECI

H_PROCHOT# Comes from EC

have to "OD" type

C C

VTTPWRGOOD Comes from EC

should be level shift to 1.1VDDM_VTT

J T A G

J T A G

B B

A A

J T A GJ T A G

M A P P I N G

M A P P I N G

M A P P I N GM A P P I N G

XDP_TDI_R XDP_TDI

XDP_TDO_M XDP_TDO

XDP_TDI_M

XDP_TDO_R

Scan Chain

(Default)

CPU Only

GMCH Only

XDP_DBRESET#

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TRST#

XDP_TCLK

R193 0Ω 5% 1/16W SMT0402 LR

R195 0Ω 5% 1/16W SMT0402 LR(NU)

R194

0Ω 5% 1/16W SMT0402 LR

R216 0Ω 5% 1/16W SMT0402 LR(NU)

R217 0Ω 5% 1/16W SMT0402 LR

STUFF -> R193, R194, R217

NO STUFF -> R195, R216

STUFF -> R193, R195

NO STUFF -> R194,R216,R217

STUFF -> R216, R217

NO STUFF -> R193,R194,R195

R218 RES 1KΩ 5% 1/16W SMT0402 LR

R225 51Ω 5% 1/16W SMT0402 LR(NU)

R215 51Ω 5% 1/16W SMT0402 LR(NU)

R192 51Ω 5% 1/16W SMT0402 LR(NU)

R224 51Ω 5% 1/16W SMT0402 LR

R196 51Ω 5% 1/16W SMT0402 LR(NU)

5

0420 Add EC path

H_PROCHOT#[48,55]

H_PM_SYNC[16]

PM_DRAM_PWRGD[16]

3VDDM

1.1VDDM_VTT

H_PECI[19]

H_THRMTRIP#[19]

TP6

H_CPUPWRGD[19]

H_VTTPWRGD[23]

PLTRST#[18,24,39,41,42,43,48]

PDG V1.5 Update

Voltage Divider Ratio

V0.2 change to 1.1S_PGD

V0.2 0804

BLOCK 5

TP19

1

H_PROCHOT#_D

R219

SHW 0 5% 1/16W 0402

H_THRMTRIP#_R

R214

SHW 0 5% 1/16W 0402

TP5

1

H_CPURST#_R

TP8

1

SYS_AGENT_PWROK

R186

1

R183

R201

1.5VDDM_PWRGD[23]

1.1VDDM_PWRGD[23,48,54]

3.3.4 SM_DRAMPWROK to Processor Should Be Held Low during S3

AND gate is used to provide DRAMPWRGD signal to CPU during S3 exit

SHW 0 5% 1/16W 0402

VDDPWRGOOD_R

SHW 0 5% 1/16W 0402

TP4

1

PLT_RST#_R

1.5KΩ 1% 1/16W SMT0402 LR

R221 750Ω 1% 1/16W SMT0402 LR

P W R G O O D P U L L

P W R G O O D P U L L

P W R G O O D P U L LP W R G O O D P U L L

U P

U P

U PU P

MoW WW14 Update

Voltage Divider Ratio

3VDDA

C1137 0.1uF 10V 10% SMT0402 X5R LR

DL-IC NC7S08P5X_NL SC70 5PIN FAIRCHILD LR

4

U70

53

1

2

AT23

AT24

G16

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

4

U13B

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

mPGA989B

R1075

1.5KΩ 1% 1/16W SMT0402 LR

1.5M_1.1M_PWRGD [53]

MISC THERMAL

CLOCKS

DDR3

MISC

PWR MANAGEMENT

JTAG & BPM

DDR_1.5_VDDQ

V0.2 0814 Change NET

V0.2 0801 Change to NU

R184

RES 1.1KΩ 1% 1/16W SMT0402 LR(NU)

VDDPWRGOOD_R

V0.2 0801 Change to 750 ohm

R208

750Ω 1% 1/16W SMT0402 LR

3

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

TCK

AP28

TMS

AT27

AT29

TDI

AR27

TDO

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

CPUDRAM_RST

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

PM_EXTTS#[0]

PM_EXTTS#[1]

R210

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

XDP_DBRESET#

P U l l U P

P U l l U P

P U l l U PP U l l U P

S I G N A L S

S I G N A L S

S I G N A L SS I G N A L S

PM_EXTTS#[0]

PM_EXTTS#[1]

H_CATERR#

H_PROCHOT#_D

H_CPURST#_R

XDP_TDO_R

0312 add follow check list

SHW 0 5% 1/16W 0402

1

1

1

R187

R188

R185 49.9Ω 1% 1/16W SMT0402 LR

R220 68Ω 5% 1/16W SMT0402 LR

R223 68Ω 5% 1/16W SMT0402 LR(NU)

R229 51Ω 5% 1/16W SMT0402 LR

0311

PDG V1.5 Update

TP10

1

BCLK_CPU_P [19]

BCLK_CPU_N [19]

TP11

1

CLK_EXP_P [15]

CLK_EXP_N [15]

CLK_DP_P [15]

CLK_DP_N [15]

V0.2 0731 CHANGE NET

FOR S3 power reduce

V0.2 0812 DELETE NET

PM_EXTTS#1_R [12,13]

TP18

TP9

TP7

0311

PDG V1.5 Update

V0.2 0804 SM_DRAMRST# Should Be Held High during S3

1KΩ 5% 1/16W SMT0402 LR

R1077

CPUDRAM_RST

100KΩ 1% 1/16W SMT0402 LR

BLOCK 3 and BLOCK6

fet is uded to isolate DDR RESET from CPU to memory during suspend

Use a 3.3V SUS well GPIO form PCH or 3.3V GPIO form embedded controller

10KΩ 5% 1/16W SMT0402 LR

10KΩ 5% 1/16W SMT0402 LR

DDR_1.5_VDDQ[7,23]

1.5VDDS[7,12,13,53]

3VDDA[14,15,16,18,19,21,23,33,39,41,42,43,46,47,48,52,53]

1.1VDDM_VTT[6,7,19,20,21,54,55]

3VDDM[10,11,12,13,14,15,16,17,18,19,20,21,23,24,25,28,33,34,35,36,37,39,41,42,43,46,47,48,52,54,55,56,57]

1.1VDDM_VTT

1.1VDDM_VTT

DDR_1.5_VDDQ

1.5VDDS

3VDDA

1.1VDDM_VTT

3VDDM

2

0Ω 5% 1/16W SMT0402 LR(NU)

S

Q123

TRANS M-FET-N BSS138_NL 50V 0.22A SOT-23 3PIN FAIRCHILD LR

R1080

DDR_1.5_VDDQ

1.5VDDS

3VDDA

1.1VDDM_VTT

3VDDM

G

C O M P E N S A T I O N

C O M P E N S A T I O N

C O M P E N S A T I O NC O M P E N S A T I O N

P r o c e s s o r

P r o c e s s o r

P r o c e s s o rP r o c e s s o r

H_COMP0

H_COMP1

H_COMP2

H_COMP3

All COMP use 10-mils trace width for routing less than 500 mils,

or 20-mils trace width for routing between 500 and 1000 mils;

Keep 20-mils spacing to other signals to minimize crosstalk

D D R 3

D D R 3

D D R 3D D R 3

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

Title

Size Document Number Rev

Date: Sheet of

1.5VDDS

R1076

D

VGS<1.5V

C1135

470pF 50V 10% SMT0402 X7R LR

R191 49.9Ω 1% 1/16W SMT0402 LR

R123 49.9Ω 1% 1/16W SMT0402 LR

R222 20Ω 1% 1/16W SMT0402 LR

R190 20Ω 1% 1/16W SMT0402 LRR189 12.4KΩ 1% 1/16W SMT0402 LR(NU)

R205 130 Ω 1% 1/16W SMT0402 LR

R204 24.9Ω 1% 1/16W SMT0402 LR

R203 100Ω 1% 1/16W SMT0402 LR

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2) 8751-8751

DDR3_DRAMRST# [12,13]

DRAMRST_CNTRL_PCH [12,13,19]

PCA50D (Intel Calpella +AMD GPU M92-M)

C

PROCESSOR CLK/MISC/JTAG(P09110)

1

4 60Wednesday, August 19, 2009

0.2

Page 5

5

U13C

4

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L DA R R A N D A L E / C L A R K F I E L D

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

(

(

(

(

D D R 3

D D R 3

D D R 3

D D R 3

3

)

)

)

)

U13D

2

1

AA6

SA_CK[0]

M_A_DQ[63:0][12]

D D

C C

B B

M_A_CAS#[12]

M_A_RAS#[12]

M_A_WE#[12]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS0[12]

M_A_BS1[12]

M_A_BS2[12]

AJ10

AL10

AK12

AK11

AM10

AR11

AL11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

A10

SA_DQ[0]

C10

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

B10

SA_DQ[4]

D10

SA_DQ[5]

E10

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

H10

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

G10

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

AH5

SA_DQ[32]

AF5

SA_DQ[33]

AK6

SA_DQ[34]

AK7

SA_DQ[35]

AF6

SA_DQ[36]

AG5

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

AK8

SA_DQ[44]

AL7

SA_DQ[45]

SA_DQ[46]

AL8

SA_DQ[47]

AN8

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

AM9

SA_DQ[52]

AN9

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AC3

SA_BS[0]

AB2

SA_BS[1]

U7

SA_BS[2]

AE1

SA_CAS#

AB3

SA_RAS#

AE9

SA_WE#

DDR SYSTEM MEMORY A

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 [12]

M_CLK_DDR#0 [12]

M_CKE0 [12]

M_CLK_DDR1 [12]

M_CLK_DDR#1 [12]

M_CKE1 [12]

M_CS#0 [12]

M_CS#1 [12]

M_ODT0 [12]

M_ODT1 [12]

M_A_DM[7:0] [12]

M_A_DQS#[7:0] [12]

M_A_DQS[7:0] [12]

M_A_A[15:0] [12]

M_B_DQ[63:0][13]

M_B_CAS#[13]

M_B_RAS#[13]

M_B_WE#[13]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS0[13]

M_B_BS1[13]

M_B_BS2[13]

AR10

AT10

B5

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

DDR SYSTEM MEMORY - B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

M_B_DM0

D4

M_B_DM1

E1

M_B_DM2

H3

M_B_DM3

K1

M_B_DM4

AH1

M_B_DM5

AL2

M_B_DM6

AR4

M_B_DM7

AT8

M_B_DQS#0

D5

M_B_DQS#1

F4

M_B_DQS#2

J4

M_B_DQS#3

L4

M_B_DQS#4

AH2

M_B_DQS#5

AL4

M_B_DQS#6

AR5

M_B_DQS#7

AR8

M_B_DQS0

C5

M_B_DQS1

E3

M_B_DQS2

H4

M_B_DQS3

M5

M_B_DQS4

AG2

M_B_DQS5

AL5

M_B_DQS6

AP5

M_B_DQS7

AR7

M_B_A0

U5

M_B_A1

V2

M_B_A2

T5

M_B_A3

V3

M_B_A4

R1

M_B_A5

T8

M_B_A6

R2

M_B_A7

R6

M_B_A8

R4

M_B_A9

R5

M_B_A10

AB5

M_B_A11

P3

M_B_A12

R3

M_B_A13

AF7

M_B_A14

P5

M_B_A15

N1

M_CLK_DDR2 [13]

M_CLK_DDR#2 [13]

M_CKE2 [13]

M_CLK_DDR3 [13]

M_CLK_DDR#3 [13]

M_CKE3 [13]

M_CS#2 [13]

M_CS#3 [13]

M_ODT2 [13]

M_ODT3 [13]

M_B_DM[7:0] [13]

M_B_DQS#[7:0] [13]

M_B_DQS[7:0] [13]

M_B_A[15:0] [13]

mPGA989B

mPGA989B

A A

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

(886-2) 8751-8751

PCA50D (Intel Calpella +AMD GPU M92-M)

PROCESSOR DDR3(P09110)

1

5 60Wednesday, August 19, 2009

0.2

Page 6

5

P R O C E S S O R C O R E

P R O C E S S O R C O R E

P R O C E S S O R C O R EP R O C E S S O R C O R E

P O W E R

P O W E R

VCORE_CPU

C221 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

Guide Bulk 4+2x 470uF x 4+2

D D

Schematic Bulk 6x 7343 220uF

C642 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C C

9 x 0 8 0 5 1 0 u F b e t w e e n i n d u c t o r a n d s o c k e t

9 x 0 8 0 5 1 0 u F b e t w e e n i n d u c t o r a n d s o c k e t

9 x 0 8 0 5 1 0 u F b e t w e e n i n d u c t o r a n d s o c k e t9 x 0 8 0 5 1 0 u F b e t w e e n i n d u c t o r a n d s o c k e t

o n t o p l a y e r

o n t o p l a y e r

o n t o p l a y e ro n t o p l a y e r

C185 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C655 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

B B

P O W E RP O W E R

1 2 x 0 8 0 5 2 2 u F i n s i d e c a v i t y

1 2 x 0 8 0 5 2 2 u F i n s i d e c a v i t y

1 2 x 0 8 0 5 2 2 u F i n s i d e c a v i t y1 2 x 0 8 0 5 2 2 u F i n s id e c a v i t y

52A 18A

C199 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C190 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C740 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C186 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

7 x 0 8 0 5 1 0 u F u n d e r c a v i t y

7 x 0 8 0 5 1 0 u F u n d e r c a v i t y

7 x 0 8 0 5 1 0 u F u n d e r c a v i t y7 x 0 8 0 5 1 0 u F u n d e r c a v i t y

C623 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C684 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C645 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C662 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C683 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C700 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C214 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C723 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C217 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C191 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C701 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C187 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C222 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C200 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C725 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C231 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C220 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

4

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L DA R R A N D A L E / C L A R K F I E L D

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

C216 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C227 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C228 22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

(

(

(

(

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

P O W E R

P O W E R

P O W E R

P O W E R

U13F

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

CPU CORE SUPPLY

)

)

)

)

1.1V RAIL POWER

POWER

PROC_DPRSLPVR

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

3

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

2

1

1.1VDDM_VTT

1.1VDDM_VCCTT

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

1.1VDDM_VTTA_QPI

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

PSI#

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

PM_DPRSLPVR_R

C111

C114

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

VTT_43

VTT_44

PSI# [55]

H_VID[0:6] [55]

R174

SHW 0 5% 1/16W 0402

H_VTTVID1 [54]

C145

C130

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

TP12

1

TP13

1

VCORE_CPU

AN35

AJ34

AJ35

B15

A15

VSSSENSE_VTT

IMVP_IMON [55]

0423 DLE SHOW PAD

VTTSENSE [54]

R122

0Ω 5% 1/16W SMT0402 LR(NU)

R167

100Ω 1% 1/16W SMT0402 LR

R164 100Ω 1% 1/16W SMT0402 LR

P R O C E S S O R U N C O R E

P R O C E S S O R U N C O R E

P R O C E S S O R U N C O R EP R O C E S S O R U N C O R E

P O W E R

P O W E R

P O W E RP O W E R

C523

C524

C526

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C706

PM_DPRSLPVR [55]

VCCSENSE [55]

VSSSENSE [55]

Route VCCSENSE and VSSSENSE traces width 18-mils and 7-mils spacing

at 27.4 ohms with 50mil spacing with other signals. Place PU and PD

within 2 inch of CPU

C522

C525

C226

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

22uF 6.3V ±20% SMT0805 X5R TDK LR

22uF 6.3V ±20% SMT0805 X5R TDK LR(NU)

C692

Market Segment Identification

VID 2 1 0

1 0 0

1 0 0

Current Sense Configuration bits

1 0

VID POC Strap

DPRSLPVR DPRSLPVR = '1' for IMVP6.5 compliant controller

PSI# Reserved "default = 0" should be provided on the motherboard

Please note that the VTT Rail

Arrandale VTT_SELECT=1 / VTT=1.05V

Clarksfield VTT_SELECT=0 / VTT=1.1V

C189

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

VID POC Strap

Arrandale Standard Voltage (SV) 35W Supported

Clarksfield Standard Voltage (SV) 45W Supported

VID POC StrapVID 5 4 3

1 50A <ICC_CORE_MAX< 60A

Reserved "default = 0" should be provided on the motherboardVID 6

V0.2 0805 DEL R105

C129

C184

+

R105 Droop 50 mV

220uF 2V 20% ESR=9mΩ SMT7343 PANASONIC LR(NU)

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR(NU)

Guide

3x 330uF

7x 0805 22uF Under cavity of the socket

8x 0805 10uF Edge of the socket

Schematic

4x 7343 220uF

13x 0805 22uF

11x 0805 10uF

V0.2 0811 DEL R652

CHANGE TO SPWR

R652

SPWR 0 5% 1/4W 1206

R652 Droop 50 mV

SPWR 0 5% 1/16W 0603

SPWR 0 5% 1/16W 0603

V0.2 0813 DEL R641 R640

CHANGE TO SPWR

R641

R640

1.1VDDM_VTT

1.1VDDM_VTT

0309 change to 0 OHM (NU)

1.1VDDM_VTT

0330 VID resister change to 1K ohm

0331 VID POC strap change

R265

H_VID0[55]

A A

H_VID1[55]

H_VID2[55]

H_VID3[55]

H_VID4[55]

H_VID5[55]

H_VID6[55]

PSI#[55]

PM_DPRSLPVR[55]

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

R241

RES 1KΩ 5% 1/16W SMT0402 LR

5

R264

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

R239

RES 1KΩ 5% 1/16W SMT0402 LR

R259

RES 1KΩ 5% 1/16W SMT0402 LR

R232

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

4

R260

RES 1KΩ 5% 1/16W SMT0402 LR

R238

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

mPGA989B

R251

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

R231

RES 1KΩ 5% 1/16W SMT0402 LR

R252

RES 1KΩ 5% 1/16W SMT0402 LR

R237

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

3

R246

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

R230

RES 1KΩ 5% 1/16W SMT0402 LR

R254

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

R256

RES 1KΩ 5% 1/16W SMT0402 LR

2

R249

RES 1KΩ 5% 1/16W SMT0402 LR

0417 ADD

R247

RES 1KΩ 5% 1/16W SMT0402 LR(NU)

VCORE_CPU[55]

1.1VDDM_VTT[4,7,19,20,21,54,55]

Title

PCA50D (Intel Calpella +AMD GPU M92-M)

Size Document Number Rev

C

PROCESSOR POWER(P09110)

Date: Sheet of

VCORE_CPU

1.1VDDM_VTT

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2) 8751-8751

1

6 60Wednesday, August 19, 2009

VCORE_CPU

1.1VDDM_VTT

0.2

Page 7

5

4

3

2

1

A R R A N D A L E / C L A R K F I E L D P R O C E S S O R

A R R A N D A L E / C L A R K F I E L D P R O C E S S O R

A R R A N D A L E / C L A R K F I E L D P R O C E S S O R

P O W E R

P O W E R

P O W E R

P O W E R

D D

VCORE_IGFX

Guide

2+1x 330uF

2x 0805 22uF Edge of the socket

2x 0603 10uF Edge of the socket

Schematic

3x 7343 220uF

6x 0805 22uF

2x 0805 10uF

C C

V0.2 0811 CHANGE

1.1VDDM_VTT

1.1VDDM_VTT

B B

15A

R588 SPWR 0 5% 1/4W 1206

R588 Droop 5 mV

R101 SPWR 0 5% 1/4W 1206

R101 Droop 7 mV

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR(NU)

P-CAP 220uF 2V 20% ESR=9mΩ SMT7343 H=1.9mm PANASONIC LR(NU)

+

C246

C814

C724

C513

22uF 6.3V ±20% SMT0805 X5R TDK LR

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C113

C128

)

)

)

)

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR(NU)

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR(NU)

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR(NU)

C800

C224

C795

C629

22uF 6.3V ±20% SMT0805 X5R TDK LR(NU)

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C245

C239

C240

1.1VDDM_VCC_PEG_DMI

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR(NU)

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR(NU)

22uF 6.3V ±20% SMT0805 X5R C2012X5R0J226MT TDK LR

C126

C107

10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

1.1VDDM_VCC_FDI

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

J24

J23

H25

K26

J27

J26

J25

H27

G28

G27

G26

F26

E26

E25

U13G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VTT1_45

VTT1_46

VTT1_47

VTT1_48

VTT1_49

VTT1_50

VTT1_51

VTT1_52

VTT1_53

VTT1_54

VTT1_55

VTT1_56

VTT1_57

VTT1_58

mPGA989B

GRAPHICS

FDI PEG & DMI

POWER

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

GRAPHICS VIDs

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

DDR3 - 1.5V RAILS

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

1.1V1.8V

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

G R A P H I C S

G R A P H I C S

G R A P H I C SA R R A N D A L E / C L A R K F I E L D P R O C E S S O R

G R A P H I C S

(

(

(

(

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

DDR_1.5_VDDQ

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

1.1VDDM_VCCTTA_DDR

P10

N10

L10

K10

1.1VDDM_VCC_SA

J22

J20

J18

H21

H20

H19

1.8VDDM_VCCSFR

L26

L27

M26

VCC_AXG_SENSE [56]

VSS_AXG_SENSE [56]

GFXVR_VID_0 [56]

GFXVR_VID_1 [56]

GFXVR_VID_2 [56]

GFXVR_VID_3 [56]

GFXVR_VID_4 [56]

GFXVR_VID_5 [56]

GFXVR_VID_6 [56]

GFXVR_EN [56]

GFXVR_DPRSLPVR [56]

GFXVR_IMON [56]

6A

C620

C613

C687

C671

1uF 6.3V 10% SMT 0603 X5R TDK LR

C639

10uF 6.3V 10% SMT0805 X5R TDK LR

C519

22uF 6.3V ±20% SMT0805 X5R TDK LR

C505

C506

1uF 6.3V 10% SMT 0603 X5R TDK LR

C595

1uF 6.3V 10% SMT 0603 X5R TDK LR

1uF 6.3V 10% SMT 0603 X5R TDK LR

1uF 6.3V 10% SMT 0603 X5R TDK LR

C518

10uF 6.3V 10% SMT0805 X5R TDK LR(NU)

C628

22uF 6.3V ±20% SMT0805 X5R TDK LR(NU)

C504

C508

1uF 6.3V 10% SMT 0603 X5R TDK LR

4.7uF 6.3V 10% SMT0603 X5R H=0.8mm TDK LR

2.2uF 6.3V 10% SMT0603 X5R H=0.90mm(MAX) SAM LR

1uF 6.3V 10% SMT 0603 X5R TDK LR

C509

C712

1206 size refer S3_PowerReduce CRB

V0.2 0814 Change to NET

DDR_1.5_VDDQ 1.5VDDS

C1148 0.1uF 10V 10% SMT0402 X5R LR

C1145 0.1uF 10V 10% SMT0402 X5R LR

C1146 0.1uF 10V 10% SMT0402 X5R LR

C1147 0.1uF 10V 10% SMT0402 X5R LR

0520 DLE R

220uF 2V 20% ESR=9mΩ SMT7343 PANASONIC LR(NU)

C717

C731

+

22uF 6.3V ±20% SMT0805 X5R TDK LR

22uF 6.3V ±20% SMT0805 X5R TDK LR

Guide

1x 330uF

2x 0805 22uF Edge of the socket

5x 0603 1uF Edge of the socket

Schematic

1x 7343 220uF

2x 0805 22uF

5x 0603 1uF

Don't drop 30mV

JP17 JP_3720

JP16 JP_3720

237

V0.2 0811 CHANGE

R585 SPWR 0 5% 1/8W 0805

R585 Droop 14 mV

1.5VDDM

1.5VDDS

8

S

D

Q65

61

5

APM4340KC-TRL 30V 17A SOP-8 8PIN ANPEC LR

4

C446

1uF 16V 10% SMT0603 X5R TDK LF

V0.2 0814 Change control circuit

1.1VDDM_VTT

for S3 Power reduce

JP16 cut off

JP17 short

DDR_1.5V_ON [53]

1.1VDDM_VTT

R587 SPWR 0 5% 1/4W 1206

R585 Droop 22 mV

0.6A

22uF 6.3V ±20% SMT0805 X5R TDK LR

R592 SPWR 0 5% 1/4W 1206

Guide

1x 0805 2.2uF

2x 0805 1uF

1x 0805 22uF

1x 0603 4.7uF

Schematic

1x 0603 2.2uF

2x 0603 1uF

1x 0805 22uF

1x 0603 4.7uF

1.8VDDM

DDR_1.5_VDDQ[4,23]

1.5VDDM[41,42,43,53,57]

DDR_0.75VDDM[12,13,53]

VCORE_IGFX[56]

A A

5

4

3

2

1.1VDDM_VTT[4,6,19,20,21,54,55]

Title

PCA50D (Intel Calpella +AMD GPU M92-M)

Size Document Number Rev

C

PROCESSOR GRAPHIC POWER(P09110)

Date: Sheet of

DDR_1.5_VDDQ

1.5VDDM

DDR_0.75VDDM

5VDDA

5VDDA[21,44,47,52,53]

12V_LS

12V_LS[43,52,53]

VCORE_IGFX

1.1VDDM_VTT

1.5VDDS

1.5VDDS[4,12,13,53]

1.8VDDM

1.8VDDM[20,30,57]

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2) 8751-8751

1

DDR_1.5_VDDQ

1.5VDDM

DDR_0.75VDDM

5VDDA

12V_LS

VCORE_IGFX

1.1VDDM_VTT

1.5VDDS

1.8VDDM

7 60Wednesday, August 19, 2009

0.2

Page 8

5

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L DA R R A N D A L E / C L A R K F I E L D

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

D D

4

G R O U N D

G R O U N D

G R O U N D

G R O U N D

(

(

(

(

)

)

)

)

3

2

1

U13H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

VSS8

AR17

VSS9

AR15

VSS10

AR12

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

AP20

VSS15

AP17

VSS16

AP13

VSS17

AP10

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

AN34

VSS22

AN31

VSS23

AN23

VSS24

AN20

VSS25

AN17

VSS26

AM29

VSS27

AM27

C C

B B

AM25

AM20

AM17

AM14

AM11

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AG10

AE35

AM8

AM5

AM2

AL9

AL6

AL3

AJ8

AJ5

AJ2

AH9

AH6

AH3

AF8

AF4

AF2

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

mPGA989B

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

K27

K9

K6

K3

J32

J30

J21

J19

H35

H32

H28

H26

H24

H22

H18

H15

H13

H11

H8

H5

H2

G34

G31

G20

G9

G6

G3

F30

F27

F25

F22

F19

F16

E35

E32

E29

E24

E21

E18

E13

E11

E8

E5

E2

D33

D30

D26

D9

D6

D3

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

B8

B6

B4

A29

A27

A23

A9

U13I

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

mPGA989B

VSS

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

A A

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

(886-2) 8751-8751

PCA50D (Intel Calpella +AMD GPU M92-M)

PROCESSOR GROUND(P09110)

1

8 60Wednesday, August 19, 2009

0.2

Page 9

5

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L DA R R A N D A L E / C L A R K F I E L D

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

P R O C E S S O R

4

R E S E R V E D

R E S E R V E D

R E S E R V E D

R E S E R V E D

(

(

(

(

3

)

)

)

)

2

1

D D

CPU_DIMM0_VREF[12]

CPU_DIMM1_VREF[13]

CFG0

CFG3

CFG4

CFG7

C C

0Ω 5% 1/16W SMT0402 LR(NU)

R124

R125

0Ω 5% 1/16W SMT0402 LR(NU)

B B

TP_RSVD17_R

TP_RSVD18_R

AP25

AL25

AL24

AL22

AJ33

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

AG9

M27

L28

J17

H17

G25

G17

E31

E30

H16

B19

A19

A20

B20

U9

T9

AC9

AB9

C1

A3

J29

J28

A34

A33

C35

B35

U13E

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

SA_DIMM_VREF

SB_DIMM_VREF

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD_TP_86

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD_NCTF_23

RSVD_NCTF_24

RSVD26

RSVD27

RSVD_NCTF_28

RSVD_NCTF_29

RSVD_NCTF_30

RSVD_NCTF_31

mPGA989B

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD_TP_59

RSVD_TP_60

RESERVED

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD58

RSVD62

RSVD63

RSVD64

RSVD65

RSVD32

AJ13

RSVD33

AJ12

AH25

RSVD35

AK26

RSVD36

AL26

AR2

AJ26

AJ27

AP1

RSVD41

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

KEY

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

VSS

V S S(A P 3 4) c a n b e l e f t N C i s C R B i m p l e m e n t a t i o n ;

V S S(A P 3 4) c a n b e l e f t N C i s C R B i m p l e m e n t a t i o n ;

V S S(A P 3 4) c a n b e l e f t N C i s C R B i m p l e m e n t a t i o n ;V S S(A P 3 4) c a n b e l e f t N C i s C R B i m p l e m e n t a t i o n ;

E D S / D G r e c o m m e n d a t i o n t o G N D

E D S / D G r e c o m m e n d a t i o n t o G N D

E D S / D G r e c o m m e n d a t i o n t o G N DE D S / D G r e c o m m e n d a t i o n t o G N D

1

1

1

1

1

TP_RSVD64_R

TP_RSVD65_R

TP_RSVD86_R

TP14

TP15

TP16

TP17

TP3

0311

PDG V1.5 Update

0Ω 5% 1/16W SMT0402 LR(NU)

R207

R206

0Ω 5% 1/16W SMT0402 LR(NU)

R177 SHW 0 5% 1/16W 0402

C F G S t r a p s f o r P r o c e s s o r

C F G S t r a p s f o r P r o c e s s o r

C F G S t r a p s f o r P r o c e s s o rC F G S t r a p s f o r P r o c e s s o r

CFG0

R197

RES 3.01KΩ 1% 1/16W SMT0402 LR(NU)

CFG3

R200

RES 3.01KΩ 1% 1/16W SMT0402 LR

CFG4

R198

RES 3.01KΩ 1% 1/16W SMT0402 LR(NU)

CFG7

R199

RES 3.01KΩ 1% 1/16W SMT0402 LR(NU)

0424

Change to No_Stuff

Due to will with ES2 sample

P r o c e s s o r S t r a p s

P r o c e s s o r S t r a p s

P r o c e s s o r S t r a p sP r o c e s s o r S t r a p s

CFG0

CFG3

CFG4

1 = Single PEG

0 = Bifurcation enabled

1 = PEG Normal Operation

0 = PEG Lane Numbers Reversed (Default)

1 = Disabled; No Physical Display Port attached to Embeded Display Port

0 = Enabled; An external Display Port device is connected to the Embeded Display Port

CFG7 Stuff : For Clarksfield ES1 sample

A A

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

(886-2) 8751-8751

PCA50D (Intel Calpella +AMD GPU M92-M)

PROCRESS RESERVED(P09110)

1

9 60Wednesday, August 19, 2009

0.2

Page 10

5

D D

C C

4

0413 Pin Reversal

CN9

PAD1

1

2

3

PAD2

456

WAFER-M TIN

2.2KΩ 5% 1/16W SMT0402 LR

5VDDM

1

2

3

4

F A N

F A N

F A NF A N

C O N T R O L

C O N T R O L

C O N T R O LC O N T R O L

R147

FAN_PWM_CN

T H E R M A L

T H E R M A L

T H E R M A LT H E R M A L

S E N S O R

S E N S O R

S E N S O RS E N S O R

3

3VDDM5VDDM

R148

G

2.2KΩ 5% 1/16W SMT0402 LR

D

S

Q43

TRANS M-FET-N BSS138_NL 50V 0.22A SOT-23 3PIN FAIRCHILD LR

3VDDM

R145

1KΩ 1% 1/16W SMT0402 LR

FAN_PWM [48]

FAN_SPEED [48]

2

0424

Pls Check EC Output Type

Have leakage Path Existed ???

1

V0.2 0814 change to TMP431B

C849 0.1UF 16V 10% SMT0402 X7R LR

SYS_THRM_VCC

R741

20mil

U71

MMB_SMCLK[25,46,48]

MMB_SMDAT[25,46,48]

B B

A A

5

4

8

SCLK

7

SDATA

6

ALRT#

LNR-IC Temperature Sensor TMP431BDGKR 2.7-5.5V MSOP-8 8PIN TI LR

Address : 100 1101

Accuracy:

±1°C (+60°C to +100°C, remote)

±3°C (+60°C to + 100°C, local)

1

VCC

THER_S_D+

2

D+

THER_S_D-

3

D-

45

THM#GND

3

100Ω 5% 1/16W SMT0402 LR

B

TRANS NPN MMBT3904 40V 200mA SOT-23 3PIN PSI LR

3VDDM

Q101

E C

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

3VDDM[4,11,12,13,14,15,16,17,18,19,20,21,23,24,25,28,33,34,35,36,37,39,41,42,43,46,47,48,52,54,55,56,57]

5VDDM[15,17,20,21,30,33,34,35,37,39,44,45,46,47,48,52,54,55,56,57]

2

3VDDM

Title

5VDDM

Size Document Number Rev

C

Date: Sheet of

(886-2) 8751-8751

PCA50D (Intel Calpella +AMD GPU M92-M)

System Thermal Sensor /Fan CONN

1

10 60Wednesday, August 19, 2009

0.2

Page 11

5

D D

4

C L O C K

C L O C K

C L O C KC L O C K

G E N E R A T O R

G E N E R A T O R

G E N E R A T O RG E N E R A T O R

3

2

1

3VDDM

L85 600Ω±25% 100MHz 1000mA SMT0603 HCB1608KF-601T10 TAI-TECH LR

C989

10uF 6.3V 10% SMT0805 X5R TDK LR

C905 0.1uF 16V 20% SMT0402 X7R LR

C907 0.1uF 16V 20% SMT0402 X7R LR

C971 0.1uF 16V 20% SMT0402 X7R LR

0424 ADD 10u

C C

1.05VDDM

VDD_CK505

R798

10KΩ 5% 1/16W SMT0402 LR

VR_PWRGD_CLKEN#[55]

TRANS NPN RT1N441M-T111-1 50V 100mA SC-70 3PIN IDC LR

B B

B

Q103

E C

R809

100KΩ 1% 1/16W SMT0402 LR

33pF 50V 20% SMT0402 NPO LR

0409 add pull down resister

L81 600Ω±25% 100MHz 1000mA SMT0603 HCB1608KF-601T10 TAI-TECH LR

10uF 6.3V 10% SMT0805 X5R TDK LR

C924

C916

X'TAL 14.318180MHz 20pF ±30PPM 2PIN SMT8.0*4.5*1.4mm F81430020 eCERA LR

Y4

VDDIO_CLK

C906

0.1uF 10V 10% SMT0402 X5R LR

C942

33pF 50V 20% SMT0402 NPO LR

VDD_CK505

C984 0.1uF 16V 20% SMT0402 X7R LR

C944 0.1uF 16V 20% SMT0402 X7R LR

C928

0.1uF 10V 10% SMT0402 X5R LR

CKPWRGD

XTAL_IN

XTAL_OUT

U53

1

VDD48Mhz_3.3

5

VDD_27MHz

17

VDDSRC_3.3

24

VDDCPU_3.3

29

VDDREF_3.3

2

GND48Mhz

9

GND27Mhz

12

GNDSRC

21

GNDCPU

26

GNDREF

15

VDDSRC_IO

18

VDDCPU_IO

25

CLKPWRGD/PD#_3.3

28

X1

27

X2

33

GND

ASIC CLOCK GENERATOR ICS9LRS3199AKLFT MLF 32PIN VER:A IDT LR

CPU_STOP#

CPUT0_LPR

CPUC0_LPR

CPUT1_LPR

CPUC1_LPR

SATAT_LPR

SATAC_LPR

SRCT1_LPR

SRCC1_LPR

DOT96T_LPR

DOT96C_LPR

27MHz_nonSS

27MHz_SS

REF_3L/FSLC_3.3

USB48Mhz

SCLK_3.3

SDATA_3.3

16

23

22

20

19

10

11

13

14

3

4

6

7

30

8

32

31

CK_CPU_STOP#

CLK_27FIXCLK_27FIX

CLK_27SSCLK_27SS

CPU_BSELCPU_BSEL

CR_48M

VDD_CK505

R796

10KΩ 5% 1/16W SMT0402 LR(NU)

0424 RESERVE PU

R851 0Ω 5% 1/16W SMT0402 LR

R850 33Ω 5% 1/16W SMT0402 LR

R823 33Ω 5% 1/16W SMT0402 LR

R849 33Ω 5% 1/16W SMT0402 LR

C P U F r e q e n c y S t r a p s

C P U F r e q e n c y S t r a p s

C P U F r e q e n c y S t r a p sC P U F r e q e n c y S t r a p s

CLK_BUF_BCLK_P [15]

CLK_BUF_BCLK_N [15]

CLK_BUF_CKSSCD_P [15]

CLK_BUF_CKSSCD_N [15]

CLK_BUF_EXP_P [15]

CLK_BUF_EXP_N [15]

CLK_BUF_DOT96_P [15]

CLK_BUF_DOT96_N [15]

CLK_GPU_27M [25]

CLK_GPU_27M_SSIN [25]

CLK_BUF_REF14 [15]

CLK_48M_CR [36]

SMB_CLK_M [12,13,15,41,42,43]

SMB_DATA_M [12,13,15,41,42,43]

V0.2 0728 change 0 ohm

VDD_CK505

0430 ADD CAP for EMI (stuff)

CLK_GPU_27M

CLK_GPU_27M_SSIN

CLK_BUF_REF14

CLK_48M_CR

C983

MO-CAP 5pF 50V ±0.5pF SMT0402 NPO C1005NP0509DGT DARFON LR

C982

MO-CAP 5pF 50V ±0.5pF SMT0402 NPO C1005NP0509DGT DARFON LR

C963

MO-CAP 5pF 50V ±0.5pF SMT0402 NPO C1005NP0509DGT DARFON LR

C981

MO-CAP 5pF 50V ±0.5pF SMT0402 NPO C1005NP0509DGT DARFON LR

CPU_BSEL

R836

10KΩ 5% 1/16W SMT0402 LR(NU)

R837

10KΩ 5% 1/16W SMT0402 LR

0424 ADD PD

0311 change to NU

P in 3 0

P in 3 0 C P U_0

P in 3 0P i n 3 0

0

0

A A

0 0

1111

C P U_0

C P U_0C P U_0

1 3 3 M H z

1 3 3 M H z

1 3 3 M H z1 3 3 M H z

1 0 0 M H z

1 0 0 M H z 1 0 0 M H z

1 0 0 M H z1 0 0 M H z

1.05VDDM[20,21,54]

5

4

3

C P U_1

C P U_1

C P U_1C P U_1

1 3 3 M H z

1 3 3 M H z

1 3 3 M H z1 3 3 M H z

Default

1 0 0 M H z

1 0 0 M H z1 0 0 M H z

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

1.05VDDM

3VDDM

3VDDM[4,10,12,13,14,15,16,17,18,19,20,21,23,24,25,28,33,34,35,36,37,39,41,42,43,46,47,48,52,54,55,56,57]

2

1.05VDDM

3VDDM

Title

Size Document Number Rev

C

Date: Sheet of

(886-2) 8751-8751

PCA50D (Intel Calpella +AMD GPU M92-M)

Clock Generator (CK505)(P09110)

1

11 60Wednesday, August 19, 2009

0.2

Page 12

5

M_A_A[15:0][5]

D D

M_A_BS0[5]

M_A_BS1[5]

M_A_BS2[5]

M_CS#0[5]

M_CS#1[5]

M_CLK_DDR0[5]

M_CLK_DDR#0[5]

M_CLK_DDR1[5]

M_CLK_DDR#1[5]

M_CKE0[5]

M_CKE1[5]

M_A_CAS#[5]

M_A_RAS#[5]

M_A_WE#[5]

SMB_CLK_M[11,13,15,41,42,43]

SMB_DATA_M[11,13,15,41,42,43]

M_ODT0[5]

M_ODT1[5]

M_A_DM[7:0][5]

C C

M_A_DQS[7:0][5]

M_A_DQS#[7:0][5]

1.5VDDS

3VDDM

SPWR 0 5% 1/16W 0603

B B

R736

0.1uF 10V 10% SMT0402 X5R LR

PM_EXTTS#1_R[4,13]

0.1uF 10V 10% SMT0402 X5R LR

C803

C804

2.2uF 6.3V 10% SMT0603 X5R SAMSUNG LR

R735 0Ω 5% 1/16W SMT0402 LR

VREF_DQA

C473

DDR3_DRAMRST#[4,13]

2.2uF 6.3V 10% SMT0603 X5R SAMSUNG LR

C474

DDR_VDDPSD_A

EVENT_A

V0.2 0814 change NET

M_VREF

0.1uF 10V 10% SMT0402 X5R LR

C704

C705

2.2uF 6.3V 10% SMT0603 X5R SAMSUNG LR

4

D D R I I I S D R A M

D D R I I I S D R A M

D D R I I I S D R A MD D R I I I S D R A M

S O - D I M M 0

S O - D I M M 0

S O - D I M M 0S O - D I M M 0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

SA0_DIM0

SA1_DIM0

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

CN11

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ