Page 1

5

hexainf@hotmail.com

4

3

2

1

First International Computer,Inc

D D

Portable Computer Group HW Department

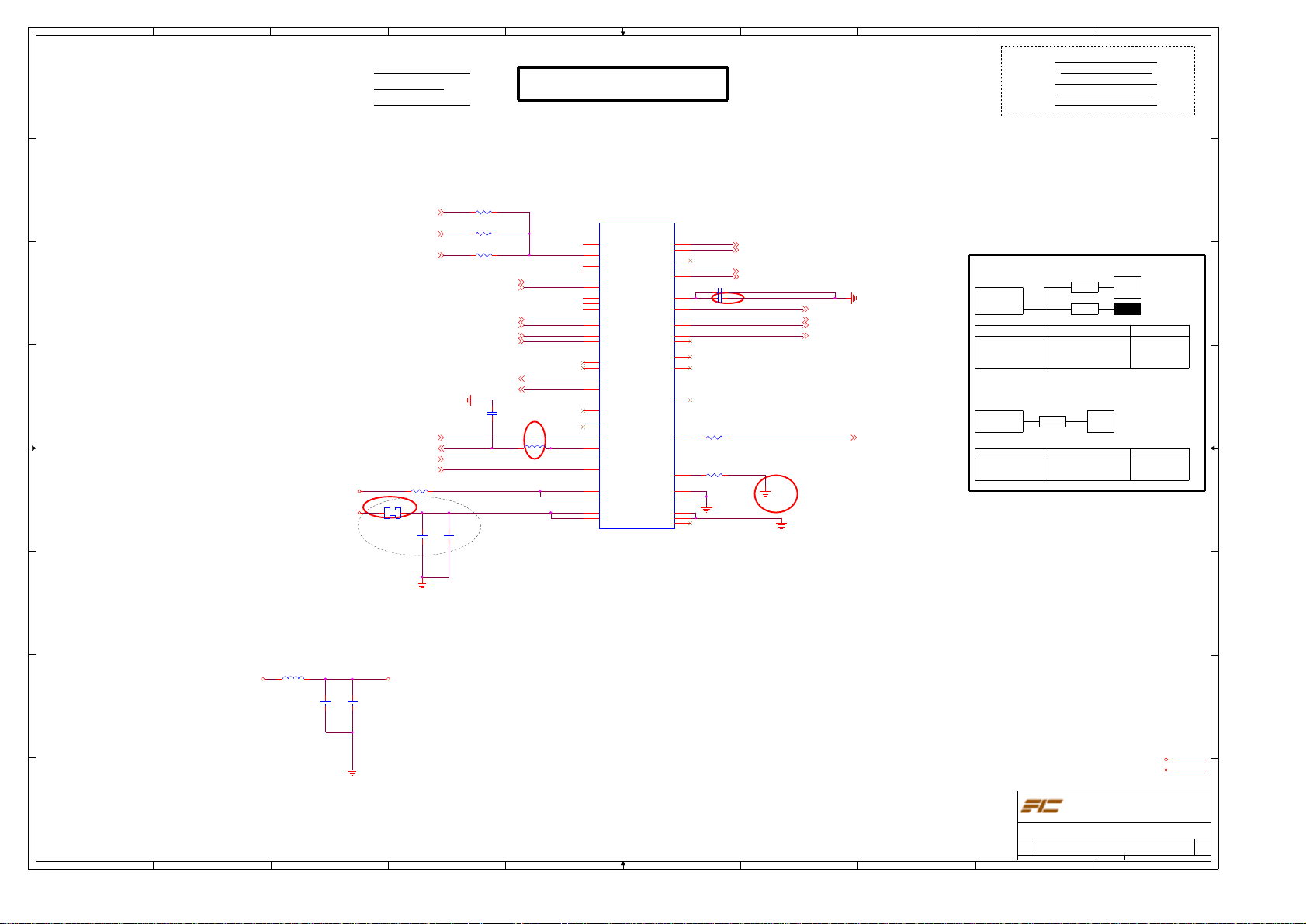

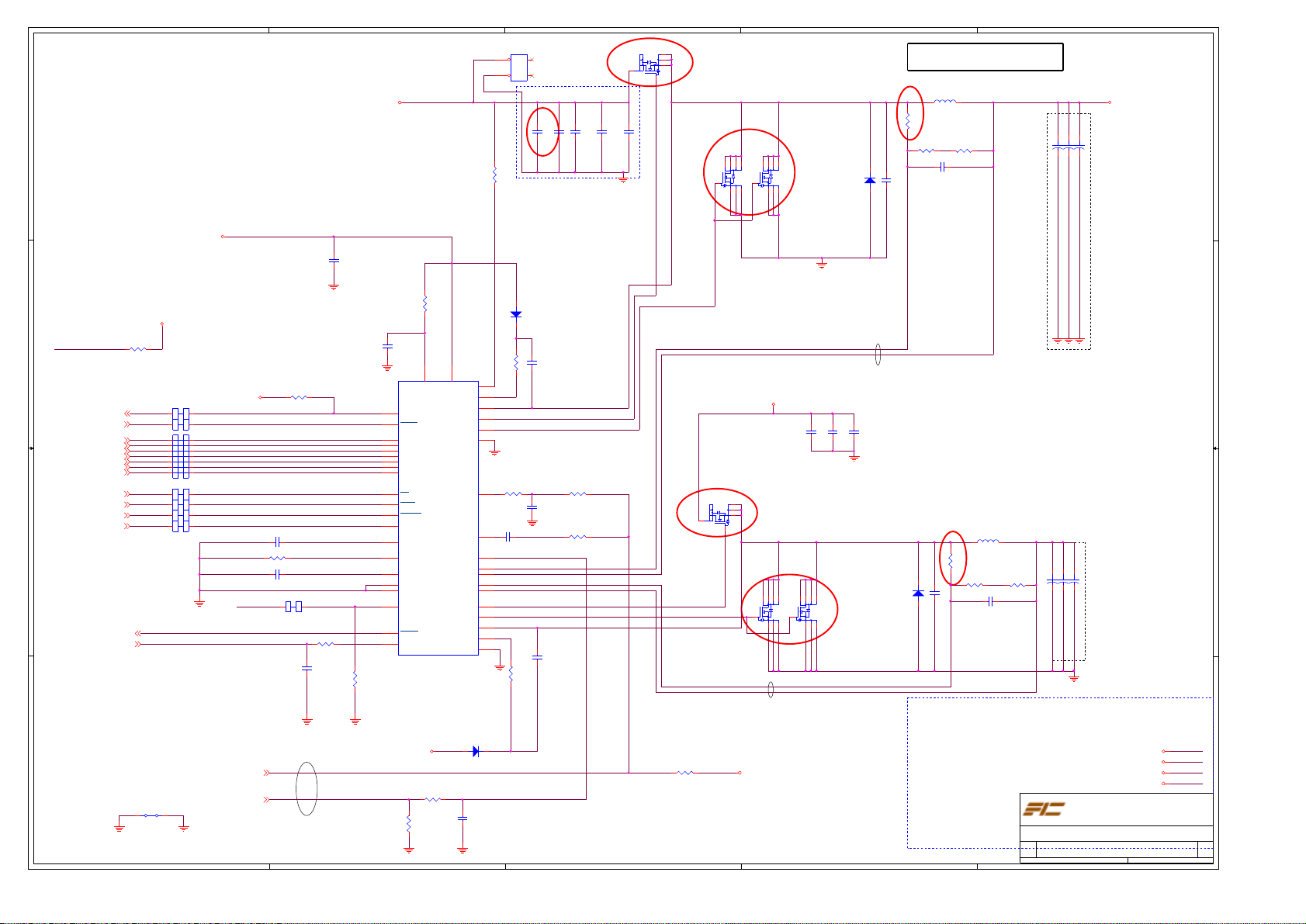

Board name : MotherBoard Schematic

Project :

C C

Version : 0.4

MR040T

Initial Date : Feb. 05 , 2007

1. Schematic Page Description :

2. PCI & IRQ & DMA Description :

3. Block Diagram :

4. Nat name Description :

5. Board Stack up Description :

6. Schematic modify Item and History :

7. power on & off & S3 Sequence :

8. Layout Guideline :

9. switch setting

B B

Manager Sign by: AVERY

Drawing by : Spruce

Total confirm by: AVERY

LAN Circuit check by:

A A

Audio Circuit check by:

5

檔

Title

Size Document Number Rev

C

4

3

2

Date: Sheet of

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

MR040T>Merom+Crestline GM965+ICH8M

Title

1

Confidential

1 56Monday, July 30, 2007

0.4

Page 2

8

7

6

1. Schematic Page Description :

MR040T Schematic Ver : 0.1

5

4

3

2

1

D D

C C

B B

1. Title

2. Schematic Page Description

3. Block Diagram

4. ANNOTATIONS

5. Schematic Modify

6. Timing Diagram

7. DDRII Layout Guideline

8. Merom Processor(1/2)

9. Merom Processor(2/2)

10. CPU Thermal

11. Crestline Host(1/6)

12. Crestline DMI/Graphic(2/6)

13. Crestline DDRII(3/6)

14. Crestline Power(4/6)

15. Crestline Power(5/6)

16. Crestline GND(6/6)

17. Clock Generator

18. DDRII SDRAM SO-DIMM0

19. DDRII SDRAM SO-DIMM1

20. ICH8M PCI/PCIE/DMI(1/4)

21. ICH8M CPU/IDE/SATA(2/4)

22. ICH8M GPIO(3/4)

23. ICH8M Power/GND(4/4)

24. Reset Circuit

25. Screw Hole

26. SPI

27. LCD CNN

28. CRT / TVOUT CNN

29. INT KB / LID / GP / SW CNN

30. DIP SW / LED

31. SATA & IDE CNN

32. USB CNN

33. Card Bus contrl

34. Card Bus CNN

35. PCIE GIGA LAN 88E8055

36. TRANSFORMER

37. Card-Reader(AU6371)

38. IEEE1394(VIA VT6311S)

2. PCI & IRQ & DMA Description :

39. Azalia ALC268 Codec

40. AMP MAXIM9789

41. SPDIF / MIC / HP / Int. MIC

42. Mini-UMTS / BT

43. Mini-WLAN / MDC / CCD

44. PMX

45. Power Block

46. CPU Core Power

47. ADPIN, BATIN, ADPOUT1

48. Charger, DCIN

49. 3/5VDDA/M , PMU3/5V

50. 1.05V/1.5VDDM

51. 1.8VDDS / 0.9VDDS

52. VDDCORE

53. 1.25VDDM / 2.5VDDM

54. USB Board

55. Modify list

IDSEL

AD17

AD27

AD29 Lan (Realtek RTL8101L)

BUSMASTER

REQ

REQ0 / GNT0

REQ1 / GNT1

A A

REQ2 / GNT2

REQ3 / GNT3

REQ4 / GNT4

CHIP CHIPPCIINT

Mini PCI (Wireless LAN)

X

CHIP

X

LAN (Realtek RTL8101L)

X

X

X

8

7

IRQ0

IRQ1

IRQ2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8

IRQ9

IRQ10

IRQ11

IRQ12

IRQ13

IRQ14

IRQ15

System timer

Keyboard

(Casacde)

LAN / MODEM

Serial Port

AUDIO / VGA / USB

FLOPPY DISK

LPT

RTC

ACPI

(Disable by default)

FIR

Cardbus

PS/2 mouse

FPU

HDD

CDROM

6

(MODEM/LAN)

5

DMA Channel

DMA0 FIR

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DeviceIRQ Channel Desciption

ECP

FLOPPY DISK

AUDIO

(Cascade)

Unused

Unused

Unused

4

(disable by default)

(MODEM / LAN)

3

IRQA

IRQB

IRQC

IRQD

IRQE / GPIO3

IRQE / GPIO4

IRQE / GPIO5

IEEE1394 (VIA VT6311S)

LAN (Realtek RTL8101L)

X

X

LAN (Realtek RTL8101L)IRQE / GPIO2

X

PASS0

CRISIS

2

20051228A

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet of

(886-2) 8751-8751

MR040T>Merom+Crestline GM965+ICH8M

Schematic Page Description

2 56Monday, July 30, 2007

1

0.4

檔

Page 3

8

hexainf@hotmail.com

7

6

5

4

3

2

1

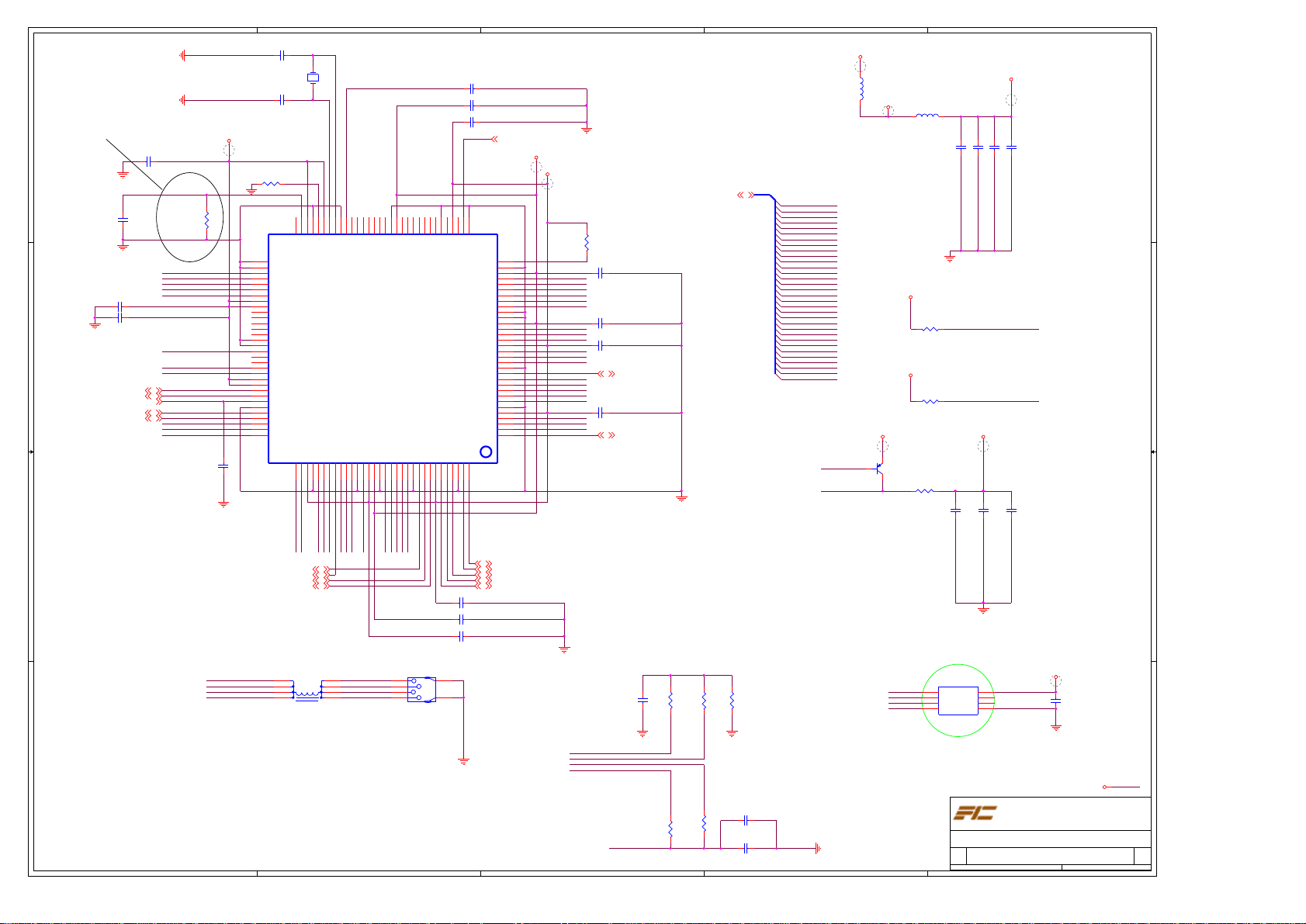

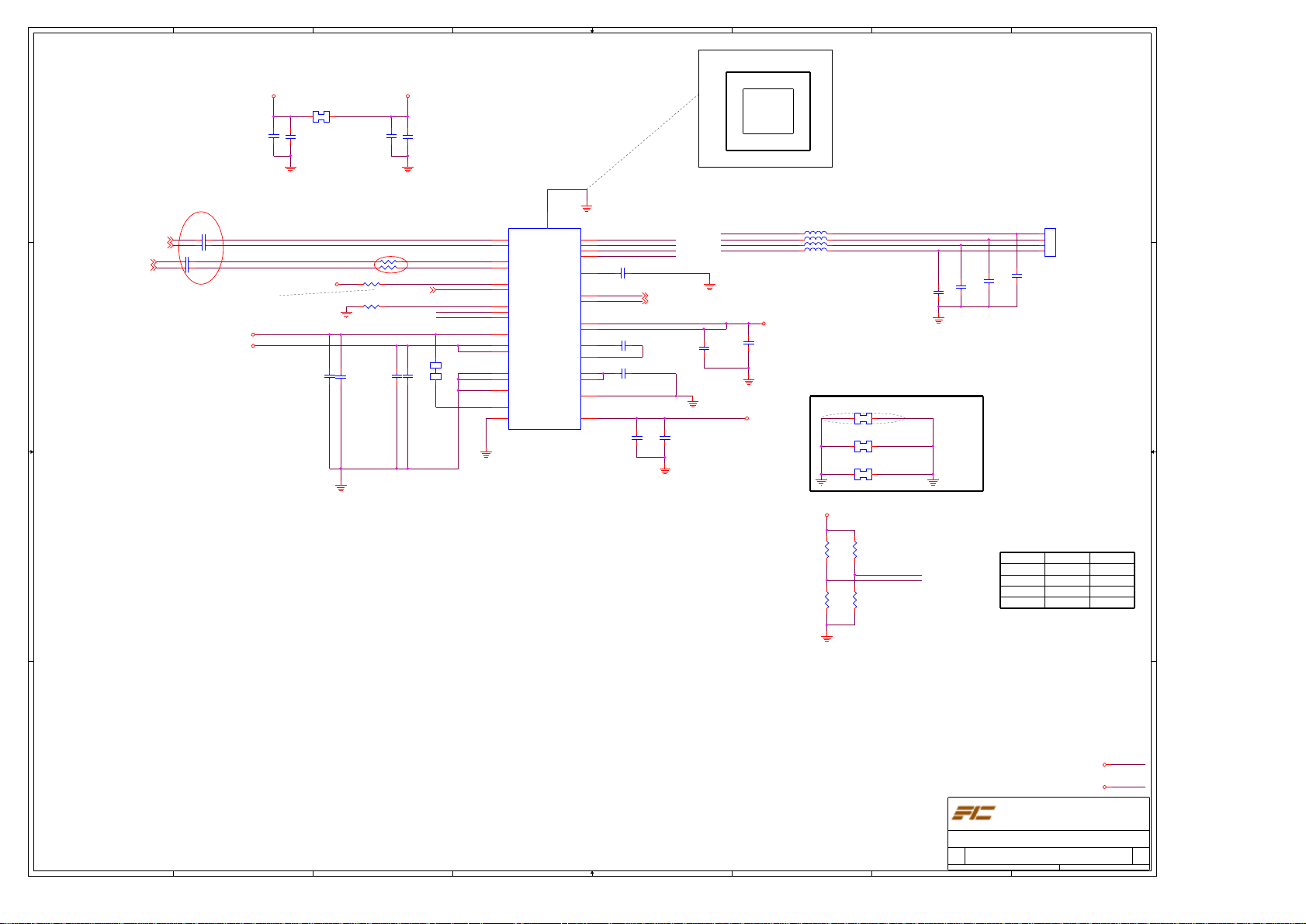

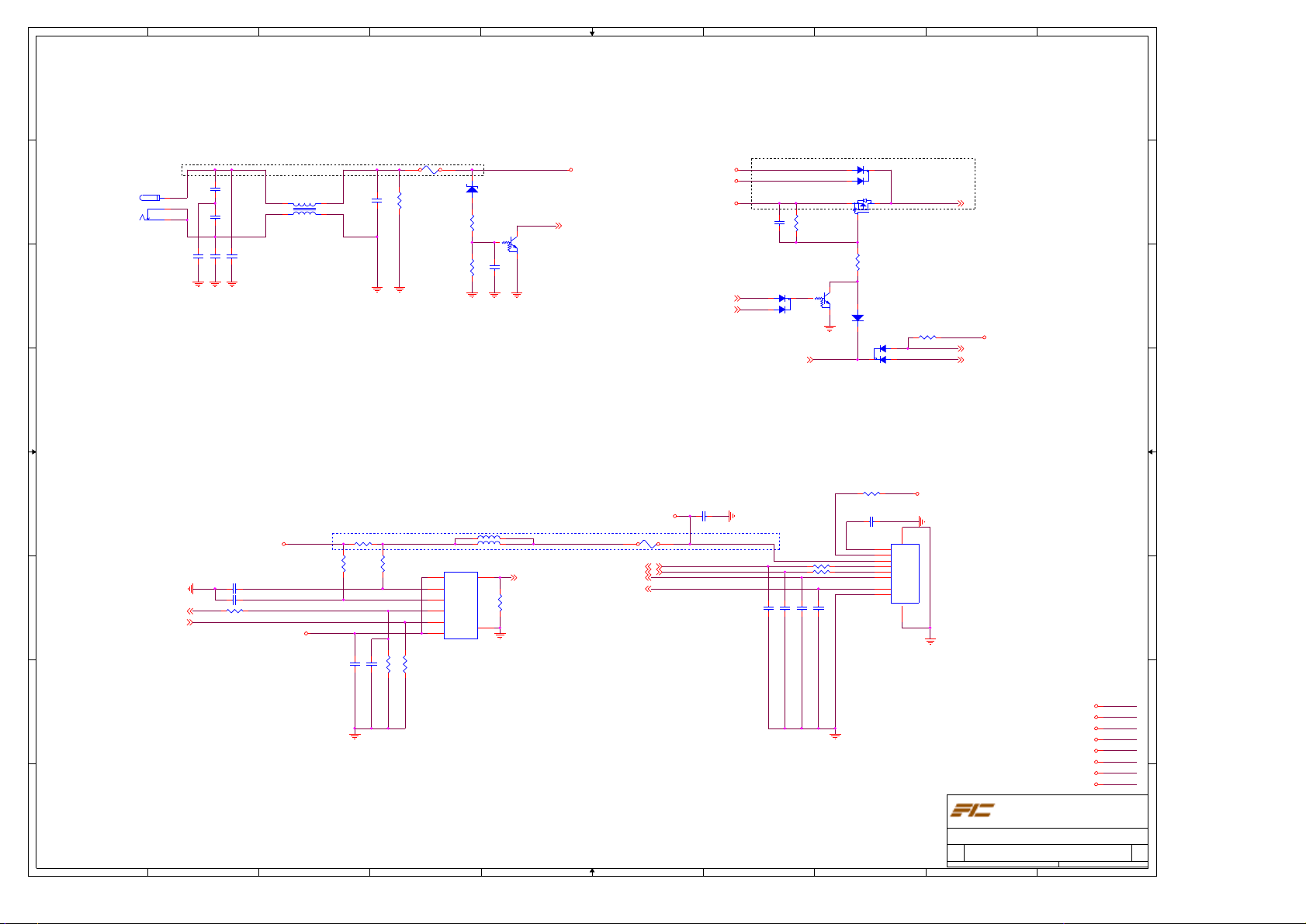

3. Block Diagram :

D D

Thermal

Sensor

S-Video

Port

CRT

C C

LCD

Battery CON

P47

ACIN / DCIN

DCIN+

B B

3VDDA

5VDDA

3VDDM/5VDDM

P47

P44

1.5VDDM

P49

P50

1.5VDDM/1.05VDDM

Battery Charger

P46

Battery Voltage Sense

1.8VDDS

P49

P49

DDRII Power

P51

P34

P52

P28

P28

P27

ALCOR

AU6371

CardReader

3 in 1

PMU3V

PMU5V

P49

P37

P37

BT

P42

CDROM

HDD

P10

USB 3

P54

P31

P31

CB1410

CARD BUS

USB 2.0

USB 0,1,2

PATA BUS

SATA BUS

P33

P34

(667/800 MHz)

P32

Intel

Merom

Processor

FSB

Intel

Crestline

(G)MCH

DMI

(x2/x4)

Intel

ICH8M

32Bit PCI BUS

P11~P16

P20~23

SPI BUS

P26

Flash ROM

P8~9

Mem_A Bus

Mem_B Bus

PCIE

PCIE MINI CARD

Azalia

LPC BUS

PMX

M38859

Int. KB

VIA

VT6311S

A A

OVP

P34

IEEE 1394

P38

CPU

CORE

P46

CPU

VCCP

P50

DDR2 533/667 MHz

DDRII SODIMM0 (A)

DDR2 533/667 MHz

DDRII SODIMM1 (B)

PCIE MINI CARD

P42

MDC

P54

P44

Glide Pad

P29P29

P18

P19

P43

Azalia Codec

ALC268

SPDIF OutMic In

P41

P41

CLK SLG8SP512TTR

Reset Circuit

Brightness Control

RTC Bat

Fan CNN

Lid Switch

MAIN SW CNN/DIP SW

LED

GIGA LAN

88E8055

RJ-45

P39

Audio AMP

MAX9789A

Headphone

P41

P35

P36

P40

SPK

P40

P29

P17

P24

P44

P21

P10

P30

P30

P54

8

檔

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

7

6

5

4

3

Date: Sheet of

2

(886-2) 8751-8751

MR040T>Merom+Crestline GM965+ICH8M

Block Diagram

3 56Monday, July 30, 2007

1

0.4

Page 4

8

7

6

5

4

3

2

1

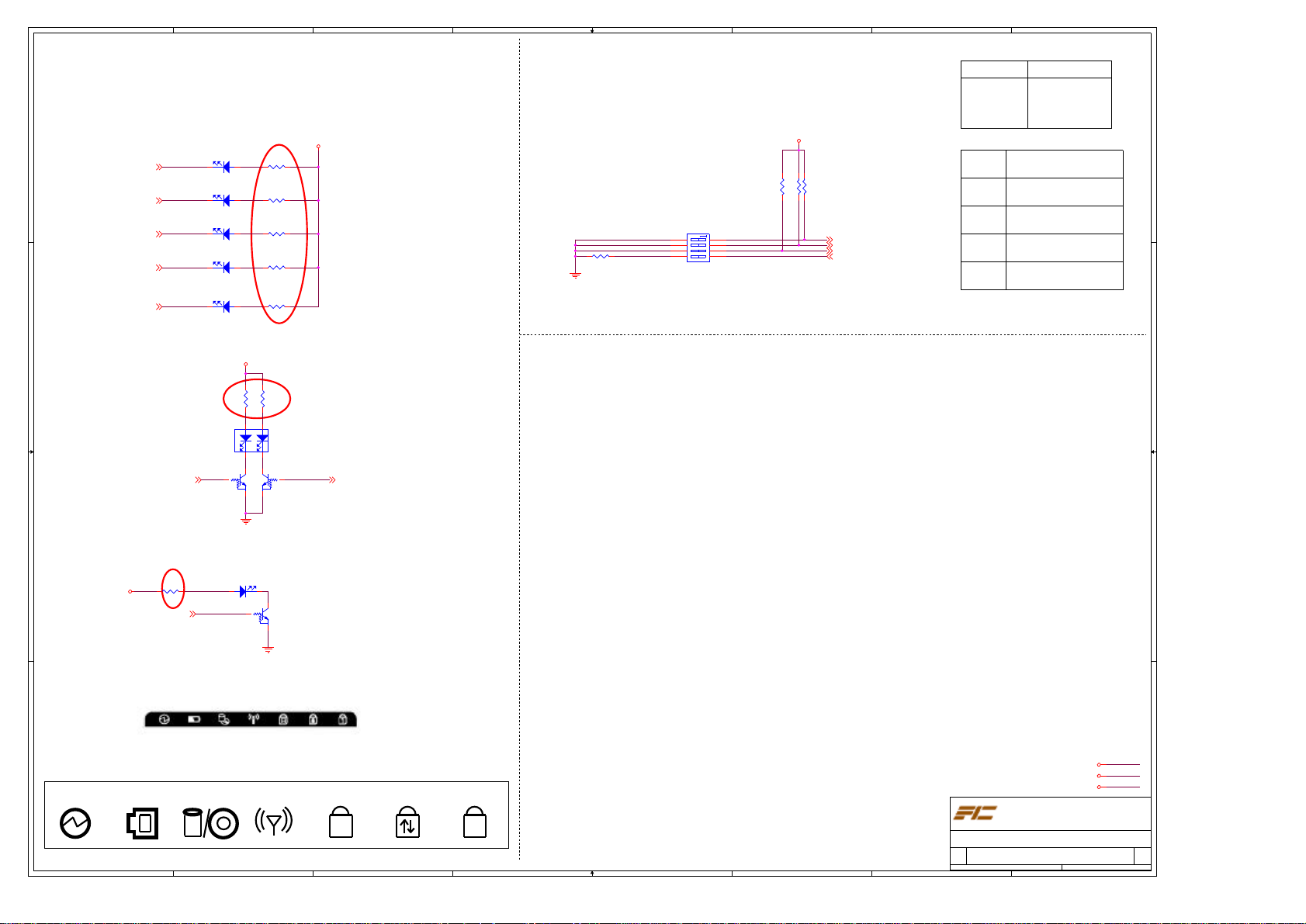

4. Nat name Description :

Voltage Rails

DCIN

PMU5V 5.0V always on power rail by LATCH or ACIN

D D

PMU3V 3.3V always on power rail by LATCH or ACIN

3VDDA 3.3V always on power rail by DCON

3VDDS 3.3V power rail by PSUSC#

5VDDS 5.0V power rail by PSUSC#

3VDDM

VCC_CORE

1.05VDDM

1.5VDDM

1.8VDDS

0.9VDDT_DDRII

Part Naming Conventions

C

=

Capacitor

CN

C C

D

F

L

Q

R

RP

U

Y

Connector

=

Diode

=

Fuse

=

Inductor

=

Transistor

=

Resistor

=

Resistor Pack

=

Arbitrary Logic Device

=

Crystal and Osc

=

Net Name Suffix

# =

B B

Active Low signal

Primary DC system power supply

5.0V always on power rail by DCON5VDDA

3.3V switched power rail by SUSTAT_B#

5.0V switched power rail by SUSTAT_B#5VDDM

Core Voltage for CPU

1.05V power rail for AGTL+ termination/Core for GMCH by SUSTAT_B#

1.5V power rail for CPU PLL/DMI;PCIE;DDRII DLLs for GMCH/Core;PCIE

for ICH7m by SUSTAT_B#

1.8V power rail for DDRII by PSUSC#

0.9V DDRII Termination Voltage by SUSTAT_B#

5. Board Stack up Description

PCB Layers

Layer 1

Layer 2

Layer 3

Layer 4

Layer 5

Layer 6

Layer 7

Layer 8

Layers : 8 Depth 1.2mm Impence 55 ohms +/- 10%

Host Clock

SRC Clock

Host Bus

DDR2 CLK

DDR2 Strobe

DDR2 Bus

DMI Bus

PCIE Bus

SATA

SDVO

LVDS

USB

IEEE1394

Lan

Single End Impedance

55 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

42 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

50 ohm +/- 15%

Component Side, Microstrip signal Layer

Ground Plane

Stripline Layer(High Speed)

Normal Signal / Ground 1 Plane

Power Plane

Stripline Layer(High Speed)

Ground 2 Plane

Solder Side,Microstrip signal Layer

Differential Impedance for Microstrip

95 ohm +/- 15%

95 ohm +/- 15%

70 ohm +/- 20%

95 ohm +/- 15%

95 ohm +/- 15%

95 ohm +/- 15%

95 ohm +/- 15%

100 ohm +/- 15%

90 ohm +/- 15%

110 ohm +/- 15%

Differential Impedance for Stripline

100 ohm +/- 15%

100 ohm +/- 15%

70 ohm +/- 20%

85 ohm +/- 20%

100 ohm +/- 15%

100 ohm +/- 15%

100 ohm +/- 15%

100 ohm +/- 15%

100 ohm +/- 15%

90 ohm +/- 15%

110 ohm +/- 15%

A A

Title

Size Document Number Rev

C

Date: Sheet of

8

7

6

5

4

3

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2) 8751-8751

MR040T>Merom+Crestline GM965+ICH8M

Annotations

4 56Monday, July 30, 2007

2

0.4

1

檔

Page 5

5

hexainf@hotmail.com

4

6.Schematic modify Item and History :

3

2

1

D D

Power Rail

VCC_CORE

1.25VDDM

C C

1.5VDDM

B B

1.8VDDS:

0.9VDDT_DDRII:

Ball Name

VCCP

VTT(VCCP)

VCC

VCC_PEG

VCCR_RX_DMI

VCC_AXM

VCC1_05

VCCSUS1_05

VCCCL1_05

VCCLAN1_05

VCCA_SM

VCCA_SM_CK

VCCA_PEG_PLL

VCCD_PEG_PLL

VCC_DMI

VCCA_HPLL

VCCD_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCC_AXG

VCC_AXF

VCC_DMI

VCCA

VCCD_QDAC

VCCD_TVDAC

VCCD_CRT

VCCD_QDAC

VCC1_5_A

VCC1_5_B

VCCSUS1_5

VCCGLAN1_5

VCCCL1_5

VCCUSBPLL

VCCDMIPLL

VCCSATAPLL

VCCGLANPLL

+1.5V

TBD

VCC_SM

VCC_SM_CK

VCCD_LVDS

VCC_TX_LVDS

VCCA_LVDS

1.8VDDS:

Destination S0 Current

HFM:

Merom

LFM:

Merom: AGTL+ termination

Crestline: AGTL+ termination

Crestline: Core chipset

Crestline: PCI Express Based Graphics

Crestline: Rx and I/O Logic for DMI

Crestline: Controller Link/ME voltage supply

ICH8M: ICH8 Core

ICH8M:

ICH8M:

ICH8M:

Crestline:

Crestline:

Crestline:

Crestline:

Crestline:

Crestline:

Crestline:

Crestline:

Crestline:

Crestline:

Crestline:

Crestline:

ICH8M:

Merom PLL

Crestline: TV DAC

Crestline: TV DAC

Crestline: CRT

Crestline: CRT

ICH8M: I/O

ICH8M: I/O

ICH8M: Resume well I/O

ICH8M: Integrated Gigabit LAN I/O

ICH8M: Controller Link

ICH8M: USB PLL

ICH8M: DMI PLL

ICH8M: SATA PLL

ICH8M: Integrated Gigabit LAN PLL

Mini Card:

Express Card:

Crestline: I/O Voltage

Crestline: Clock I/O Voltage

Crestline:

Crestline:

Crestline:

SO-DIMM:

DDRII Terminator:

Voltage

1.0375V~?~1.3000V

TBD~TBD

0.9975V~1.05V~1.1025V

0.9975V~1.05V~1.1025V

1.425V~1.5V~1.575V

1.425V~1.5V~1.575V

1.425V~1.5V~1.575V

1.425V~1.5V~1.575V

1.425V~1.5V~1.575V

1.7V~1.8V~1.9V

0.855V~0.9V~0.945V

44A

TBD

4.5A1.05VDDM 1.00V~1.05V~1.10V

0.8A

1.3A

130mA

1.5A

60mA

24mA

320mA

3.1A

1.0A

Power Rail

Ball Name

2.5VDDM

3VDDM VCCA_PEG_BG

VCC_HV

VCC_SYNC

VCCA_CRT_DAC

VCCA_TVA_DAC

VCCA_TVB_DAC

VCCA_TVC_DAC

VCCA_DAC_BG

3VDDS

3VDDA

5VDDM

5VDDS

PMU3V

Need Modify

Destination

945GM: PCIE analog

945GM: LVDS analog

945GM: LVDS I/O

945GM: CRT DAC

CH7307:

Crestline: PCI Express Base Graphics

Crestline: HV buffer power

Crestline: H/VSYNC power

Crestline: CRT DAC

Crestline: TV Out

Crestline: TV Out

Crestline: TV Out

Crestline: TV DAC

ICH7m:

Mini Card:

Express Card:

CLK Generator: ICS954226

KBC: KB3886

Flash ROM: BIOS

Azalia Codec: ALC260

Azalia MDC:

HDD: SATA

Lan: Broadcom BCM4401

Card Reader: SD/MMC/MS

Azalia MDC: For wake up

ICH7m:

ICH7m:

ICH7m:

LCD:

Azalia Codec: ALC260

Azalia MDC:

HDD: SATA

ODD: PATA

Audio AMP: G1420

Inverter:

USB: x 4 ports

EC: PMU08

ICH7m: RTC

Voltage

2.32V~2.5V~2.625V

2.375V~2.5V~2.625V

2.375V~2.5V~2.625V

2.32V~2.5V~2.625V

3.135V~3.3V~3.465V

3.135V~3.3V~3.465V

3.135V~3.3V~3.465V

3.0V~3.3V~3.6V

3.0V~3.3V~3.6V

3.0V~3.3V~3.6V

3.0V~3.3V~3.6V

4.75V~5.0V~5.25V

4.75V~5.0V~5.25V

5V

S0 Current

2mA

10mA

60mA

70mA

40mA

120mA

400mA

1.0A

Max: 1.0A ; R/W

Max: 1.8A ; R/W: 900mA

2.0A

A A

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

(886-2) 8751-8751

MR040T>Merom+Crestline GM965+ICH8M

Schematic Modify

1

5 56Monday, July 30, 2007

檔

0.4

Page 6

5

4

3

2

1

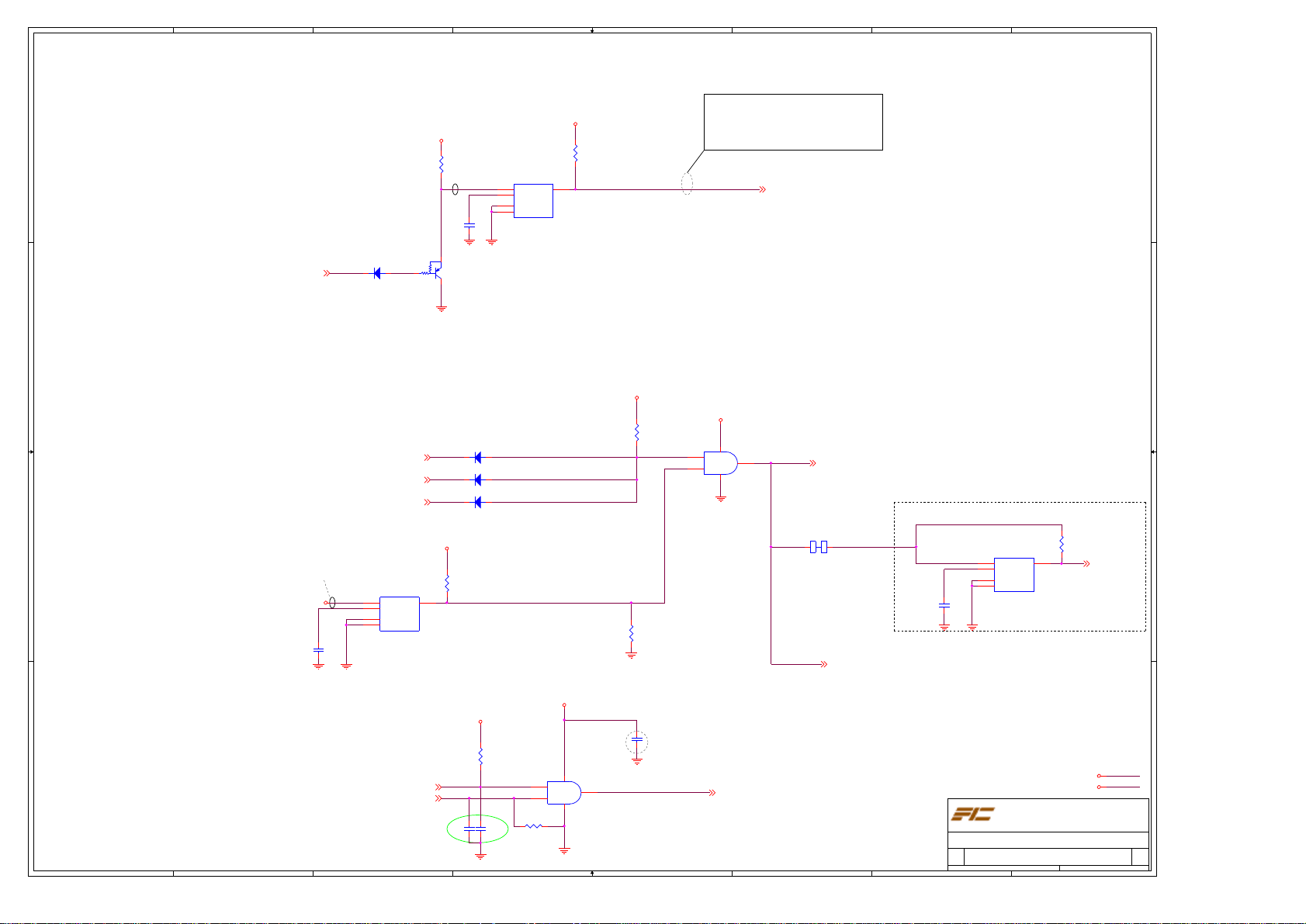

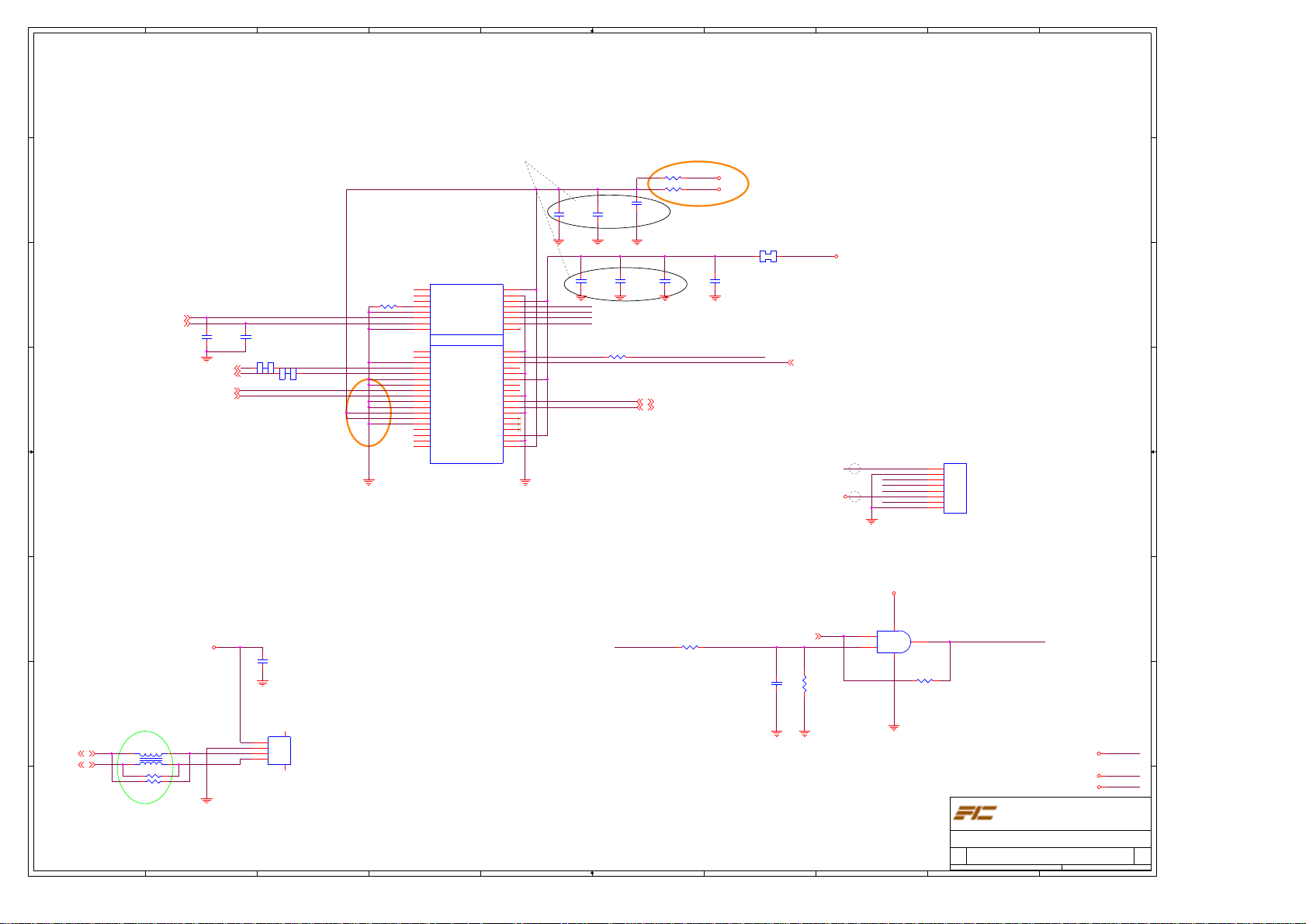

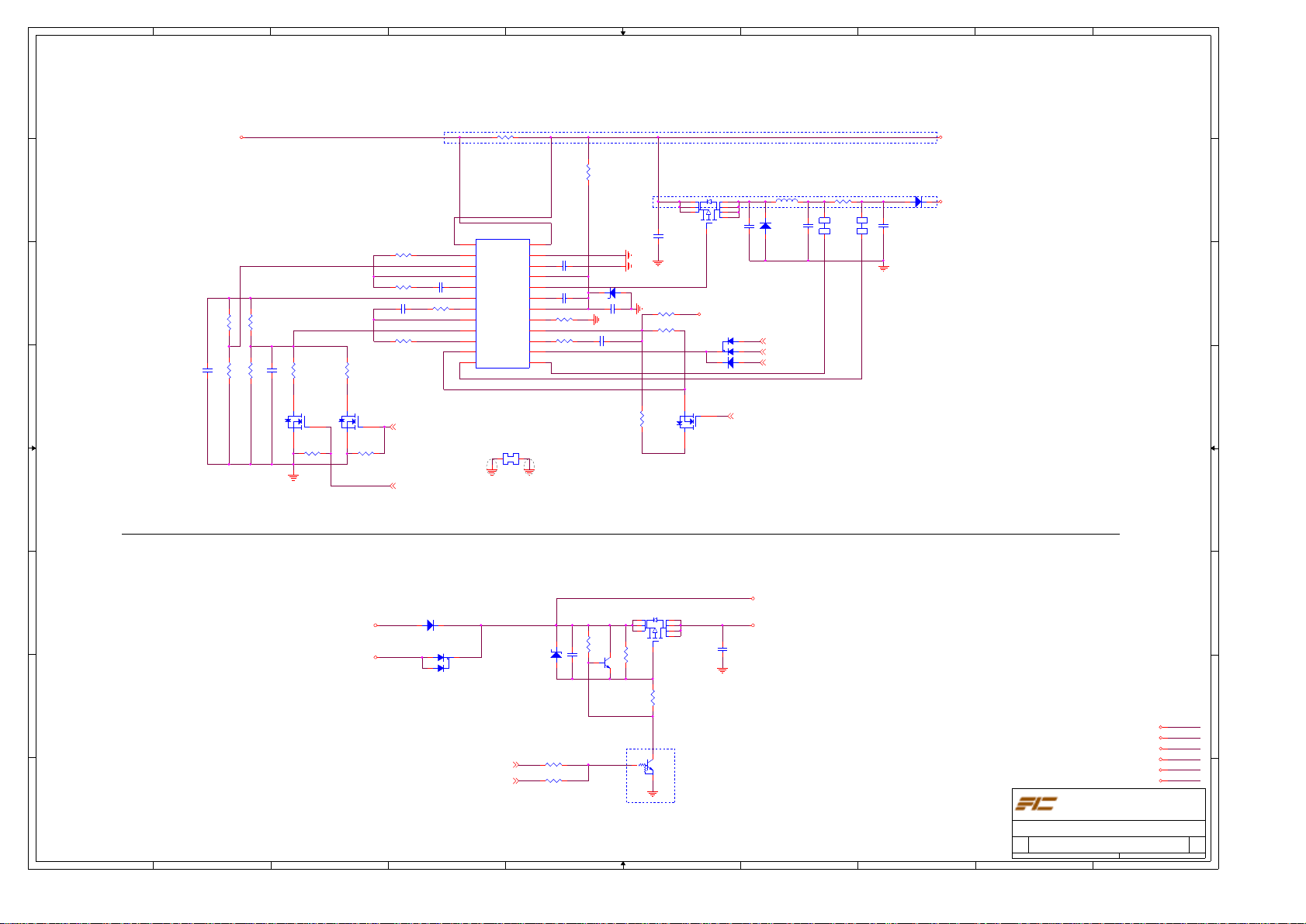

7. power on & off & S3 Sequence :

S3 SUSPEND AND RESUME TIMING

Power On Sequencing Timing Diag ram

D D

20060117A - DATA FROM NO.16809

PSI#

VID

t

SFT_START_VCC

VR_ON

-12%

t

-12%

t

Vccp_UP

BOOT

t

BOOT-VID-TR

V

CC-CORE

t

C C

CPU_UP

V

CCP

CPU_UP

Vccp_UP

-12%

V

CC_MCH

MCH_PWRGD

t

B B

MCH-PWRGD

CLK_ENABLE#

IMVP6_PWRGD

t

SFT_START_VCC

t

BOOT

t

BOOT-VID-TR

t

A A

CPU_UP

t

Vccp_UP

t

MCH-PWRGD

t

CPU_PWRGD

5

Max = 3 ms

Min = 10 us , Max = 100 us

Max = 100 us

Min = 10 us , Max = 30 us

Min = 10 us , Max = 30 us

Min = 10 us , Max = 30 us

Min = 3 ms , Max = 20 ms

t

CPU_PWRGD

4

POWSW0

PMU5V/PMU3V

PM_RSMRST0

PM_SLP_S30

PM_SLP_S40/S50

SUSTAT_B0

PM_PWROK

SYS_PWROK

VRON_VCCP

VCCP,1.2VDDM

VCORE_ON

VCORE_CPU

CK408_PWRGD0

PM_VGATE

CPU_PWRGOOD

PCI_RST0

AGTL+_CPURST0

BATTERY ONLY POWER ON TIMING

PMU5V/PMU3V

MAINSW0_ICH

PM_RSTRST0

PM_SLP_S30/S40/S50

SUSTAT_B0

VDDM,VDDS

SYS_PWROK

VRON_VCCP

VCCP/1.2VDDM

VCORE_ON

VCORE_CPU

CK408_PWRGD0

PM_VGATE

CPU_PWRGD

PCI_RST0

AGTL+_CPURST0

DCON

VDDA

PSUSC0

VDDS

VDDM

VR_ON

POWSW0

DCON

VDDA

PSUSC0

PM_PWROK

VR_ON

H

H

H

H

H

H

H

3

To ICH4_M

From ICH4_M

From ICH4_M

From ASIC_B0

From ASIC_B0

1.5VDDS AND

DDR_PWRGD

Generator

To clock

ToICH4 and ODEM

From ICH4 to CPU

To ODEM/other

PCI device

From ODEM to CPU

To ICH4

To ICH4

From ICH4

From ASIC_B0

From ASIC_B0

To clock generator

To ODEM and ICH4

From ICH4 to CPU

To ODEM/other PCI device

From ODEM to CPU

IMVP6 Power On Sequencing Timing Diagram

VID

VR_ON

Vcc-core

CPU_UP

Vccp

Vccp_UP

Vccgmch

GMCHPWRGD

CLK_ENABLE#

IMVP4_PWRGD

2

Tsft_star_vcc(3ms max)

Tboot

Tcpu_up

Tvccp_up

Tgmch_pwrgd

Title

Size Document Number Rev

C

Date: Sheet of

Vid

Vboot

Tboot-vid-tr(100uS max)

Tboot:10-100uS

Tcpu_pwrgd(3~20mS)

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2) 8751-8751

MR040T>Merom+Crestline GM965+ICH8M

Timing Diagram

1

6 56Monday, July 30, 2007

0.4

檔

Page 7

5

hexainf@hotmail.com

4

3

2

1

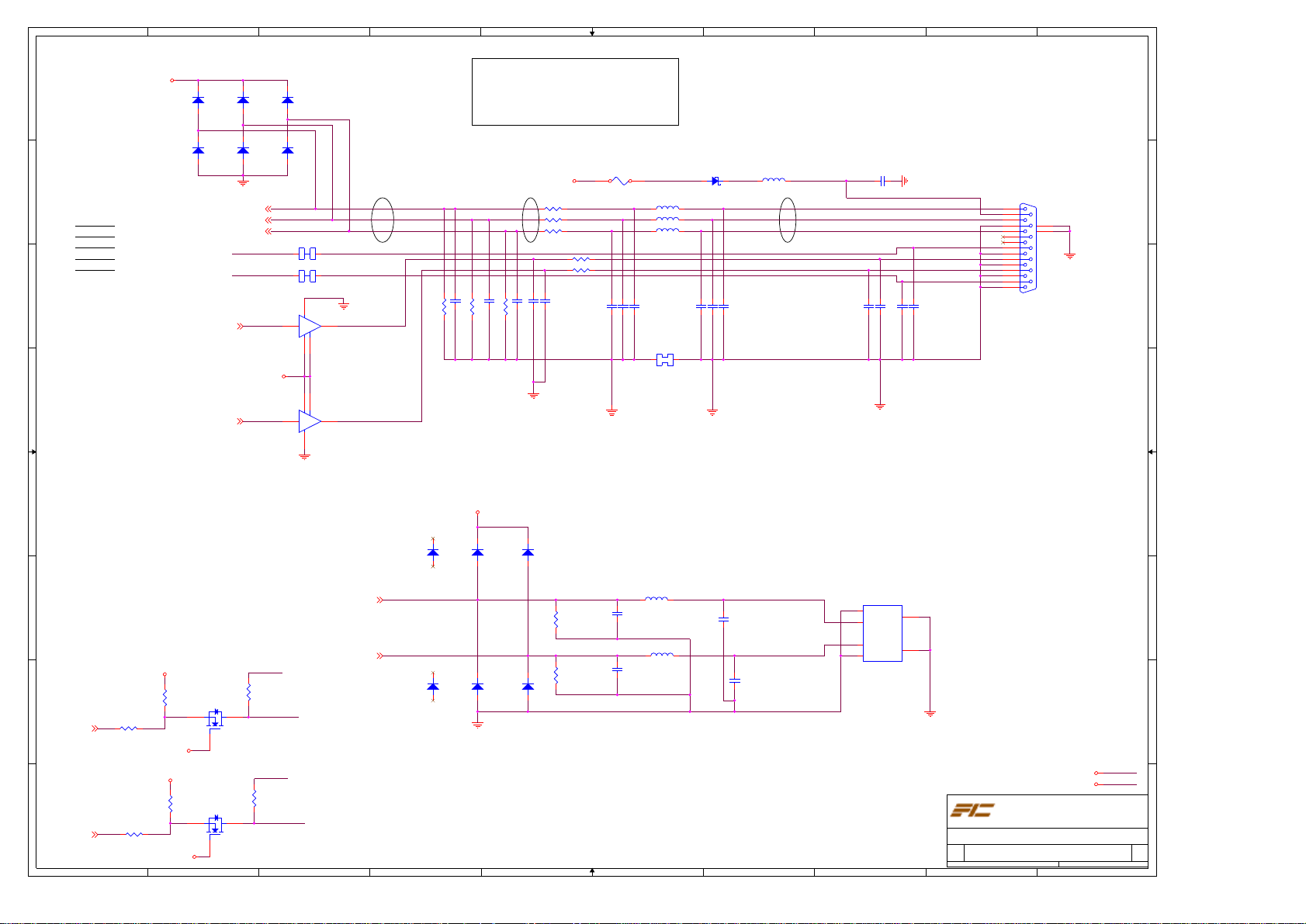

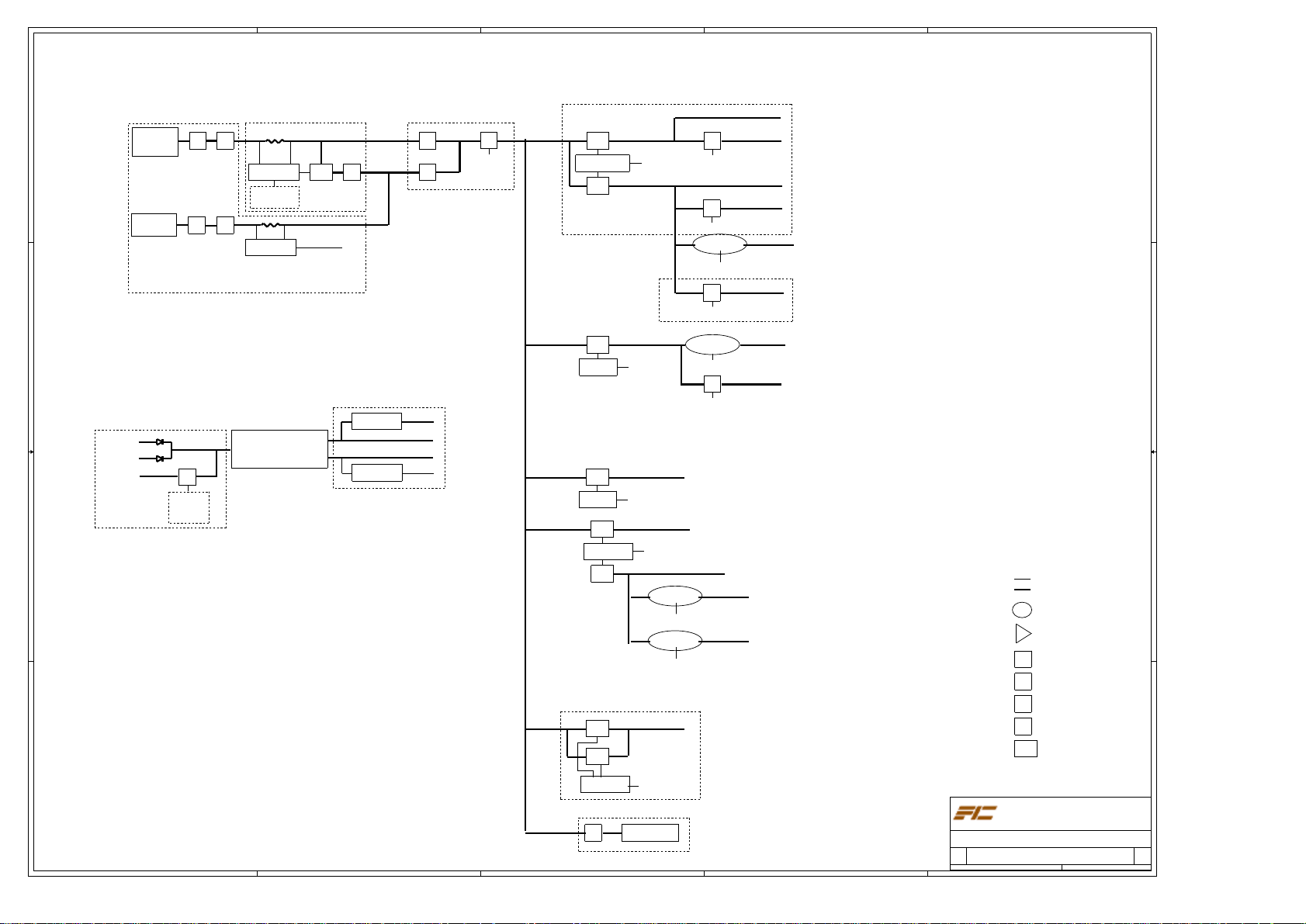

8. Layout Guideline :

Crestline DDRII Layout Guidelines

DDRII Signal Groups

Group Signal Name

D D

Data

SA_DQ[63..0]/SB_DQ[63..0]

SA_DM[7..0]/SB_DM[7..0]

SA_DQS[7..0]/SA_DQS#[7..0]

SB_DQS[7..0]/SB_DQS#[7..0]

SA_MA[13..0]/SB_MA[13..0]Address

SA_BS[2..0]/SB_BS[2..0]

SA_RAS#/SB_RAS#

SA_CAS#/SB_CAS#

SA_WE#/SB_WE#

SM_CS#[3..0]Control

SM_CKE[3..0]

SM_ODT[3..0]

Clock SM_CK[3..0]

SM_CK#[3..0]

SA_RCVENOUT#/SB_RCVENOUT#FeedBack

SA_RCVENIN#/SB_RCVENIN#

CLK group : SM_CK[3..0],SM_CK#[3..0]

4/4/12 7/4/16 8/5/15

GMCH

C C

Topology

Reference Plane

Single Ended Trace Impedance

Differential Mode Impedance

Nominal Trace Width Inner Layer : 7 mils

Nominal CK to CK# Sp acing

(edge to edge)

Minimum Serpentine Spacing Inner Layer : 12 mils

Minimum Spacing to Other DDR2 Inner Layer : 16 mils

Minimum Isolation Spacing to non-DDR2 25 mils

Package Length Range - P1 1000 mils +/- 250 mils

Trace Length Limit - L0 Max = 50 mils (Escape)

Trace Length Limit - L1 Max = 500 mils (Breakout)

Stub Length S1-Stub from via to SO-DIMM Max = 200 mils (Breakin)

MB Length Limits - L0 + L1 + L2 + S1 Min = 500 mils

B B

Maximim Via Count 2 (Per side)

SCK to SCK# Length Matching Match total length to within 5 mils

Clock to Clock Length Match

(Total Length)

Breakout Exceptions (R educe geometries

for GMCH break-out region)

Breakin Exception s (Reduce geometries

for SO-DIMM break-in region)

Feedback group :

SA_RCVENIN#],SA_RCVENOUT#,SB_RCVENIN#],SB_RCVENOUT#

These signals are routed internally on the GMCH package and don't require an y

routing on the MB. As a result, can be left as NC.

A A

4/4

P1P1L0L0L1L1L2L2S1

Escape Breakout Breakin

SLMS SL MS

5

Length Matching and Length Formulas

Signal Group Minimum Length Maximum Length

Control-to-Clock

Command-to-Clock

Strobe-to-Clock

Data-to-Strobe

Clock - 1.0"

Clock - 1.0"

Clock - 0.5"

Strobe - 220mils

SO-DIMM

S1

Differential Pair Point-to-Point

Ground

42 +/- 15%

70 +/- 20%

Outer Layer : 8 mils

Inner Layer : 4 mils

Outer Layer : 5 mils

Outer Layer : 15 mils

Outer Layer : 20 mils

Max = 4000 mils

Max = 4500 milsTotal Length - P1 + L0 + L1 + L2 + S1

Total Length for Channel A : X0

Total Length for Channel B : X1

Match Channel A clocks to X0 +/- 20mils

Match Channel A clocks to X1 +/- 20mils

Inner Layer : 4/12 mils to other DDR2

Outer Layer : 5/15 mils to other DDR2

Max. breakout length is 500 m ils

CK to CK# spacing rule waived at

connector spacing of 15 mils to

other DDR2

Max. breakin length is 2 00 mils

Clock - 0.0"

Clock + 1.0"

Clock + 1.0"

Strobe - 180mils

4

Control group : SM_CKE[3..0],SM_CS#[3..0],SM_ODT[3..0]

8/5/15

7/4/16

GMCH

P1

Topology

Reference Plane

Characteristic Trace Impedance

Nominal Trace Width

Minimum CTRL Trace Spac ing

Minimum Spacing to Other DDR2

Minimum Isolation Spacing to non-DDR2

Package Length P1

Trace Length Limit - L0

Trace Length Limit - L1

Stub Length S1-Stub from via to SO-DIMM

MB Length Limits - L0 + L1 + L2 + S1 From GMCH ball to SO-DIMM pad

Total Length - P1 + L0 + L1 + L2 + S1 From GMCH die to SO-DIMM pad

Parallel Termination Resistor 56 +/- 5%

Maximim Via Count

CTRL to SCK/SCK # Length Matching

(Total Length including package)

Breakout Exceptions (Reduce geometries

for GMCH break-out region)

Command group :

SA_MA[13..0],SB_MA[13..0],SA_BS[2..0],SB_BS[2..0],SA_RAS#,

SB_RAS#,SA_CAS#,SB_CAS#,SA_WE#,SB_WE#

GMCH

P1

Topology

Reference Plane

Characteristic Trace Impedance

Nominal Trace Width

Minimum CMD Bus Trace Spacing

Minimum Spacing to Other DDR2

Minimum Isolation Spacing to non-DDR2

Package Length P1

Trace Length Limit - L0

Trace Length Limit - L1

Stub Length S1-Stub from via to SO-DIMM

MB Length Limits - L0 + L1 + L2 + S1 From GMCH ball to SO-DIMM pad

Total Length - P1 + L0 + L1 + L2 + S1 From GMCH die to SO-DIMM pad

Trace Length L3

Parallel Termination Resistor

Maximim Via Count

CTRL to SCK/SCK # Length Matching

(Total Length including package)

for GMCH break-out region)

4/4/12

Escape

L1

L0

Breakout

SL

MS SL/MS

4/4

L1

Breakout

4/6,5/10

SL/MSMS SL

Escape

L0

L2

L3

SL/MS

S1

MS

SO-DIMM

Point-to-Point with parallel termination

Ground

55 +/- 15%

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 8 mils

Outer Layer : 10 mils

Inner Layer : 12 mils

Outer Layer : 15 mils

25 mils

750 mils +/- 200 mils

Max = 50 mils (Escape)

Max = 500 mils (Breakout)

Max = 200 mils (Breakin)

Min = 500 mils

Max = 4500 mils

Max = 5000 mils

Max = 1500 milsTrace Length L3

3

(CLK-1.0") </= CTRL </= (CLK-0.0")

Inner Layer : 4 mils spacing allowe d

Outer Layer : 5 mils spacing allowed

Max. breakout length is 500 m ils

4/6,5/10

L3

L2

SL/MS

S1

MS

SO-DIMM

Point-to-Point with parallel termination

Ground

55 +/- 15%

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 6 mils

Outer Layer : 10 mils

Inner Layer : 12 mils

Outer Layer : 15 mils

25 mils

750 mils +/- 350 mils

Max = 50 mils (Escape)

Max = 500 mils (Breakout)

Max = 200 mils (Breakin)

Min = 500 mils

Max = 4500 mils

Max = 5000 mils

Max = 1500 mils

56 +/- 5%

3

(CLK-1.0") </= CM D </= (CLK+1.0")

Inner Layer : 4 mils spacing allowe dBreakout Exceptions (R educe geometries

Outer Layer : 5 mils spacing allowed

Max. breakout length is 500 m ils

3

Vtt

Vtt

Data group : SA_DQ[63..0],SB_DQ[63..0],SA_DM[7..0],SB_DM[7..0]

4/6

GMCH

P1 L0

4/4

Escape

L1

L2

Breakout

MS SLSL MS

S1

SO-DIMM

Topology

Reference Plane

Characteri stic Trace Impedance

Nominal Trace Width

Minimum DQ Bus Trace Spacing

Minimum Serpentine Spacing Same as DQ-to-DQ r outing

Minimum Spacing to Other DDR2

Minimum Isolation Spacing to non-DDR2

Package Length P1

Trace Length Limit - L0

Trace Length Limit - L1

Stub Length S1-Stub from via to SO-DIMM

MB Length Limits - L0 + L1 + L2 + S1 From GMCH ball to SO-DIMM pad

Total Length - P1 + L0 + L1 + L2 + S1 From GMCH die to SO-DIMM pad

Trace Length L3

Maximim Via Count

DQ/DM to DQS Length Matching

(Total Length including

Breakout Exceptions (R educe geometries

package)

for GMCH break-out region)

Point-to-Point

Ground

55 +/- 15%

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 6 mils

Outer Layer : 8 mils

Inner Layer : 12 mils

Outer Layer : 15 mils

25 mils

750 mils +/- 350 mils

Max = 50 mils (Escape)

Max = 500 mils (Breakout)

Max = 200 mils (Breakin)

Min = 500 mils

Max = 4500 mils

Max = 5000 mils

Max = 1500 mils

2

Match DQ/DM to [SDQS - 200mils]

+/- 20mils, per byte lane

Inner Layer : 4 mils spacing allowed

Outer Layer : 5 mils spacing allowed

Max. breakout length is 500 mi ls

Data Strobe group : SA_DQS[7..0],SA_DQS[7..0]#,SB_DQS[7..0],SB_DQS[7..0]#

GMCH

P1

P1

Topology

Reference Plane

Single Ended Trace Impedance

Differential Mode Impedance

Nominal Trace Width

Nominal DQS to DQS# Spacing

(edge to edge)

Minimum Serpentine Spacing

Minimum Spacing to Other DDR2

Minimum Isolation Spacing to non-DDR2

Package Length Range - P1

Trace Length Limit - L0

Trace Length Limit - L1

Stub Length S1-Stub from via to SO-DIMM

MB Length Limits - L0 + L1 + L2 + S1 From GMCH ball to SO-DIMM pad

Total Length - P1 + L0 + L1 + L2 + S1 From GMCH die to SO-DIMM pad

Maximim Via Count

DQS to DQS# Length Matching

Clock to Clock Length Match

(Total Length include package)

Breakout Exceptions (R educe geometries

for GMCH break-out region)

Breakin Exceptions (Reduce geometries

for SO-DIMM break-in region)

Escape

L0

L0

4/4/8

L1

L1

Breakout

SL SL MS

4/4/12

L2

L2

SO-DIMM

5/5/10

S1

S1

Breakin

Differential Pair Point-to-Point

Ground

55 +/- 15%

85 +/- 20%

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 12 milsMinimum DQS to DQ Spacin g

Outer Layer : 15 mils

Inner Layer : 8 mils

Outer Layer : 10 mils

Inner Layer : 12 mils

Outer Layer : 15 mils

25 mils

750 mils +/- 350 mils

Max = 50 mils (Escape)

Max = 500 mils (Breakout)

Max = 200 mils (Breakin)

Min = 500 mils

Max = 4500 mils

Max = 5000 mils

2 (Per side)

Match total length to within 5 mils

(CLK-0.5") </= D QS </= (CLK+1.0")

Inner Layer : 8 mils to other DDR2

Outer Layer : 10 mils to other DDR2

Max. breakout length is 500 mi ls

DQS to DQS# spacing rule

waived at connector spacing of

10 mils to other DDR2

Max. breakin length is 2 00 mils

2

Title

Size Document Number Rev

Date: Sheet of

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2) 8751-8751

MR040T>Merom+Crestline GM965+ICH8M

C

DDRII Layout Guideline

1

7 56Monday, July 30, 2007

0.4

檔

Page 8

A

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#[35..3]

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

4 4

3 3

H_A#[35..3]11

H_ADSTB#011

H_REQ#[4..0]11

H_A#[35..3]

H_REQ#[4..0]

H_A#[35..3]11

H_ADSTB#111

H_A20M#21

H_FERR#21

H_IGNNE#21

H_STPCLK#21

H_INTR21

H_NMI21

H_SMI#21

U36A

J4

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

D22

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

Merom Ball-out Rev 1a

ADDR GROUP

0

ADDR GROUP

1

ICH

Rout to TP via and place gnd via w/in 100mils

A#[32-39], APM#[0-1]:Leave escape routing on for future functionality

H_D#[63..0]11

2 2

H_DSTBN#011

H_DSTBP#011

H_DINV#011

H_D#[63..0]11

Zo=55ohm, 0.5" max for GTLREF, Space any other switch

signals away from GTLREF with a minimum of 25mils.

Don't allow the GTLREF routing to create splits or

discontinuities in the reference planes of the FSB

signals

R126 1KΩ 1% 1/16W SMT0402 LR

1.05VDDM

1 1

2KΩ 1% 1/16W SMT0402 LR

A

H_DSTBN#111

H_DSTBP#111

H_DINV#111

12

R121

H_D#[63..0]

H_D#[63..0]

R175 1KΩ 5% 1/16W SMT0402 LR(NU)

C181

0.1uF 10V 10% SMT0402 X5R LR(NU)

Place C181 close to the CPU_TEST4 pin.

Make sure CPU_TEST4 routing is reference to GND

and away from other nossy signale.

CPU_BSEL017

CPU_BSEL117

H_GTLREF

TEST3

TEST5

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

E22

F24

E26

G22

F23

G25

E25

E23

K24

G24

J24

J23

H22

F26

K22

H23

J26

H26

H25

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

AD26

C23

D25

C24

AF26

AF1

A26

B22

B23

C21

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

XDP/ITP SIGNALS

DBR#

THERMAL

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

H CLK

BCLK[0]

BCLK[1]

RESERVED

U36B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

BSEL[0]

BSEL[1]

BSEL[2]

Merom Ball-out Rev 1a

MISC

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

DATA GRP 1

B

DATA GRP 0

B

H_IERR#

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TMS

XDP_TRST#

XDP_DBRESET#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

DATA GRP 2DATA GRP 3

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

H_ADS# 11

H_BNR# 11

H_BPRI# 11

H_DEFER# 11

H_DRDY# 11

H_DBSY# 11

R177 56Ω 5% 1/16W SMT0402 LR

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_BREQ# 11

H_INIT# 21

H_LOCK# 11

H_CPURST# 11

H_RS#0 11

H_RS#1 11

H_RS#2 11

H_TRDY# 11

H_HIT# 11

H_HITM# 11

H_THERMDA 10

H_THERMDC 10 HOT_DOWN# 10,44

PM_THRMTRIP# 12,21

CLK_CPU_BCLK 17

CLK_CPU_BCLK# 17

H_D#[63..0]

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#[63..0]

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

R157 27.4Ω 1% 1/16W SMT0402 LR

COMP0

R155 54.9Ω 1% 1/16W SMT0402 LR SnR188 1KΩ 5% 1/16W SMT0402 LR(NU)

COMP1

R134 27.4Ω 1% 1/16W SMT0402 LR

COMP2

R140 54.9Ω 1% 1/16W SMT0402 LR Sn

COMP3

H_DPRSTP# 12,21,46

H_DPSLP# 21

H_DPWR# 11

H_PWRGD 21

H_CPUSLP# 11

PSI# 46CPU_BS EL217

H_PWRGD rise time :

Max : 15ns

C

Topology : FERR#

1.05VDDM

Topology : PWRGOOD

1.05VDDM

R182

75Ω 1% 1/16W SMT0402 LR

0'' ~ 3''

R183 0Ω 5% 1/16W SMT0402 LR(NU)

H_PROCHOT# 46

Topology : INTR , NMI , A20M# , DPSLP# , IGNNE# , INIT# , SMI# , STPCLK#

Topology : THERMTRIP#

Should be connect to ICH8M and Crestline without T-ing(no stub)

XDP P/U & P/D

XDP_DBRESET#

XDP_TMS

XDP_TDI

XDP_BPM#5

XDP_TCK

XDP_TRST#

R189 1KΩ 5% 1/16W SMT0402 LR(NU)

R122 RES 39Ω 1% 1/16W SMT0402 LR

R127 150Ω 5% 1/16W SMT0402 LR

R124 54.9Ω 1% 1/16W SMT0402 LR Sn(NU)

R118 RES 27Ω 5% 1/16W SMT0402 LR

R119 649Ω 1% 1/10W SMT0603 LR

H_D#[63..0] 11

H_DSTBN#2 11

H_DSTBP#2 11

H_DINV#2 11

H_D#[63..0] 11

Comp0,2 connect with Zo=27.4ohm, make trace

length shorter than 0.5" and width is 18mils.

Comp1,3 connect with Zo=55ohm, make trace

length shorter than 0.5" and width is 5mils

H_DSTBN#3 11

H_DSTBP#3 11

H_DINV#3 11

C

3VDDM

1.05VDDM

D

VCCP=1.05VDDM

ICH8MCPU

VCCP

CPU IMVP6

Rtt

L4

CPU

ICH8M

L1

L1

GMCHL2CPU ICH7m

FSB Common Clock Signal Layout Guide :

ADS# , BNR# , BPRI# , BR0# , DBSY# , DEFER# , DPWR# , DRDY# , HIT# , HITM# , LOCK# ,

RS[2..0]# , TRDY# , RESET#.

Transmission Line Type Total Trace Length Normal Impedance Spacing (mils)

Strip-line(Int. Layer)

Micro-strip(Ext. Layer)

FSB Source Synchronous Data Length Variation and Strobe Matching Requirements :

Signals Name

DATA#[15..0] , DINV0#

DATA#[31..16] , DINV1# +/- 100 mil s

DATA#[47..32] , DINV2#

DATA#[63..48] , DINV3#

FSB Source Synchronous Data Signal Routing Topology#1 :

Signal Name

DINV#[3..0]

DATA#[63..0]

DSTBN#[3..0]

DSTBP#[3..0]

FSB Source Synchronous Address Length Variation and Strobe Matching Requirements :

A#[16..3] , REQ#[4..0]

*** No length matching requirements exist between ADSTB0# and ADSTB1#

FSB Source Synchronous Address Signal Routing :

Signal Name

Address#[31..3]

REQ#[4..0]

ADSTB#[1..0]

VCCP L1

Rtt

L2

0.5" - 12"L1

VCCP

Rtt

L2+L1 L3 Strip-line

L1

Transmission Line

Micro-strip

0.5" - 12"

0.5" - 12" Strip-line

Transmission Line

L1CPU ICH8M

0.5" - 12" Micro-strip

Strip-line

0.5" - 12"

VCCP

L3

RttL1 L4

Rtt

1.0 ~ 6.5 inch 55+/-15%

Signals Matching

+/- 100 mils

+/- 100 mils

Transmission Line Type

Strip-line

Strip-line

Strip-line

Strip-line

Total Trace Length

0.5 ~ 5.5 inch

0.5 ~ 5.5 inch

0.5 ~ 5.5 inch

0.5 ~ 5.5 inch

Signals MatchingSignals Name

+/- 200 mils

Transmission Line Type

Strip-line

Strip-line

Total Trace Length Normal Impedance

0.5 ~ 6.5 inch

0.5 ~ 6.5 inch

0.5 ~ 6.5 inch

D

Rtt Transmission Line

L2

0" - 3.0" Microstrip0.5" - 12"

56 +/-5%

56 +/-5%

L3 L4

0" - 3.0"

0" - 3.0"

Stripline

0" - 3.0"

0" - 3.0"

Rtt Transmission LineL2L1

Micro-strip75 +/-5%0.5" - 6.5"

75 +/-5%0.5" - 6.5"

0" - 3.0"

0.5" - 6.5"

0.5" - 6.5"

Topology : CPUSLP#

GMCH

L1

Topology : RESET#

GMCH

L1

L1 L2

1" - 12"

1" - 6" 0" - 3.0"

1" - 12" 1" - 6"

Processor ITP Signal Default Strapping When ITP-XDP &

ITP700FLEX Dedbug Port Not Used.

Signal Resistor Value Connect To Resistor Placement

TDI

TMS

TRST#

TCK

TDO

Strobes associated with the group Strobe-to-Strobe Complement Matching

DSTBP0#,DSTBN0#

DSTBP1#,DSTBN1#

DSTBP2#,DSTBN2#

DSTBP3#,DSTBN3#

Strobes associated with the group

ADSTB0#+/- 200 mils

ADSTB1#A#[31..17]

1.05VDDM9,11,14,15,17,21,23,50

3VDDM10,12,15,17,18,19,20,21,22,23,24,26,27,28,29,30,31,33,35,37,38,39,42,43,44,46,49,52,53

L3

L1+L3

0" - 3.0"

1" - 12"

0" - 3.0"

1" - 12"

54.9 OHM +/-5%

54.9 OHM +/-5%

649 OHM +/-5%

54.9 OHM +/-5%

OPEN

4 & 8 mils

5 & 10 mils

Normal Impedance

55+/-15%

55+/-15%

55+/-15%

55+/-15%

55+/-15%

55+/-15%

55+/-15%Strip-line

1.05VDDM

3VDDM

VCCP

VCCP

GND

GND

NC

+/- 25 mils+/- 100 mils

+/- 25 mils

+/- 25 mils

+/- 25 mils

Width & Spacing (mils)

Data-to-Data,Strobe-to-strobe Strobe-to-Data

4 & 8 mils

4 & 8 mils

4 & 12 mils

4 & 12 mils

Strobe to Assoc. Address Signal Matching

+/- 200 mils

+/- 200 mils

Width & Spacing (mils)

4 & 8 mils

4 & 8 mils

4 & 8 mils

Title

MR040T>Merom+Crestline GM965+ICH8M

Size Document Number Rev

C

Merom Processor (1/2)

Date: Sheet of

E

Transmission Line

L1CPU

0.5" - 12"

Micro-strip

0.5" - 12"

Strip-line

Transmission LineCPU

L1

1" - 6"

Micro-strip

Strip-line

1" - 6"

Rtt

Rss

24 +/-5%

24 +/-5% 56 +/-5%

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

Transmission LineL4

56 +/-5%

Micro-strip

Strip-line0" - 3.0"

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

N/A

N/A

N/A

4 & 12 mils

4 & 12 mils

Confidential

E

8 56Monday, July 30, 2007

0.4

檔

Page 9

A

hexainf@hotmail.com

B

C

D

E

Place these inside socket cavity on L8

(North side secondary)

VCORE_CPU

4 4

HFM

ICC=41A

3 3

2 2

1 1

C2 08 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR (N U)

C2 11 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR (N U)

C1 75 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR (N U)

C174 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

Place these inside socket cavity on L1

(North side Primary)

C6 71 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR

C6 70 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR

C669 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C672 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

North side secondary

C2 13 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR (N U)

C209 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C210 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C6 67 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR

C668 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C215 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C212 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C214 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

South side secondary

Place these inside socket cavity on

L8 (South side secondary)

C2 58 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR (N U)

C2 56 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR (N U)

C254 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C255 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C257 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

Place these inside socket cavity on L1

(South side Primary)

C6 90 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR

C688 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C687 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C689 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C7 28 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR (N U)

C2 59 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR (N U)

C261 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C727 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C260 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C6 85 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR

C686 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

U36C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Merom Ball-out Rev 1a

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

C250 0.1uF 16V ±10% SM D0603 X7R LR

H_VID0 46

H_VID1 46

H_VID2 46

H_VID3 46

H_VID4 46

H_VID5 46

H_VID6 46

1.05VDDM

C2 41 0. 1u F 16V ± 10% S MD 06 03 X7R LR

C233 0.1uF 16V ±10% SM D0603 X7R LR

C238 0.1uF 16V ±10% SM D0603 X7R LR

C228 0.1uF 16V ±10% SM D0603 X7R LR

C234 0.1uF 16V ±10% SM D0603 X7R LR

VCORE_CPU

ICCP=4.5A,180mils

1/29 EMI

C226

+

P-CAP 220uF 2V ± 20% 9mΩ H=1.9mm SMT7343 V CASE A705V227M002AS SDK(SDK-CAP) LR

Place these inside socket cavity on L8

(North side secondary)

1.5VDDM

ICCA=130mA, 20mils

C3 06 10 uF 6.3V 1 0% S MT 08 05 X5 R C2 01 2X 5R0 J1 06 K TD K LR

C298

0.01uF 16V 10% SMT0402 X7R LR

Place C?

Close To pin

B26

TDK

R117

100Ω 1% 1/16W SMT0402 LR

VCCSENSE 46

R120

100Ω 1% 1/16W SMT0402 LR

VSSSENSE 46

U36D

A4

VSS[082]

VSS[001]

A8

VSS[002]

VSS[083]

A11

VSS[003]

VSS[084]

A14

VSS[004]

VSS[085]

A16

VSS[005]

VSS[086]

A19

VSS[006]

VSS[087]

A23

VSS[007]

VSS[088]

AF2

VSS[008]

VSS[089]

B6

VSS[009]

VSS[090]

B8

VSS[010]

VSS[091]

B11

VSS[011]

VSS[092]

B13

VSS[012]

VSS[093]

B16

VSS[013]

VSS[094]

B19

VSS[014]

VSS[095]

B21

VSS[015]

VSS[096]

B24

VSS[016]

VSS[097]

C5

VSS[017]

VSS[098]

C8

VSS[018]

VSS[099]

C11

VSS[019]

VSS[100]

C14

VSS[020]

VSS[101]

C16

VSS[021]

VSS[102]

C19

VSS[022]

VSS[103]

C2

VSS[023]

VSS[104]

C22

VSS[024]

VSS[105]

C25

VSS[025]

VSS[106]

D1

VSS[026]

VSS[107]

D4

VSS[027]

VSS[108]

D8

VSS[028]

VSS[109]

D11

VSS[029]

VSS[110]

D13

VSS[030]

VSS[111]

D16

VSS[031]

VSS[112]

D19

VSS[032]

VSS[113]

D23

VSS[033]

VSS[114]

D26

VSS[034]

VSS[115]

E3

VSS[035]

VSS[116]

E6

VSS[036]

VSS[117]

E8

VSS[037]

VSS[118]

E11

VSS[038]

VSS[119]

E14

VSS[039]

VSS[120]

E16

VSS[040]

VSS[121]

E19

VSS[041]

VSS[122]

E21

VSS[042]

VSS[123]

E24

VSS[043]

VSS[124]

F5

VSS[044]

VSS[125]

F8

VSS[045]

VSS[126]

F11

VSS[046]

VSS[127]

F13

VSS[047]

VSS[128]

F16

VSS[048]

VSS[129]

F19

VSS[049]

VSS[130]

F2

VSS[050]

VSS[131]

F22

VSS[051]

VSS[132]

F25

VSS[052]

VSS[133]

G4

VSS[053]

VSS[134]

G1

VSS[054]

VSS[135]

G23

VSS[055]

VSS[136]

G26

VSS[056]

VSS[137]

H3

VSS[057]

VSS[138]

H6

VSS[058]

VSS[139]

H21

VSS[059]

VSS[140]

H24

VSS[060]

VSS[141]

J2

VSS[061]

VSS[142]

J5

VSS[062]

VSS[143]

J22

VSS[063]

VSS[144]

J25

VSS[064]

VSS[145]

K1

VSS[065]

VSS[146]

K4

VSS[066]

VSS[147]

K23

VSS[148]

VSS[067]

K26

VSS[068]

VSS[149]

L3

VSS[069]

VSS[150]

L6

VSS[070]

VSS[151]

L21

VSS[071]

VSS[152]

L24

VSS[072]

VSS[153]

M2

VSS[073]

VSS[154]

M5

VSS[074]

VSS[155]

M22

VSS[075]

VSS[156]

M25

VSS[076]

VSS[157]

N1

VSS[077]

VSS[158]

N4

VSS[078]

VSS[159]

N23

VSS[079]

VSS[160]

N26

VSS[080]

VSS[161]

P3 A25

VSS[081] VSS[162]

VSS[163]

Merom Ball-out Rev 1a

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF25

VCORE_CPU46

VCORE_CPU

1.05VDDM

1.05VDDM8,11,14,15,17,21,23,50

1.5VDDM

1.5VDDM14,15,20,21,23,42,43,50

檔

Route VCCSENSE and VSSSENSE traces

at 27.4 ohms with 50mil spacing.

Place PU and PD within 1 inch of CPU

A

B

C

D

Title

Size Document Number Rev

C

Date: Sheet of

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

Confidential

MR040T>Merom+Crestline GM965+ICH8M

Merom Processor (2/2)

E

9 56Monday, July 30, 2007

0.4

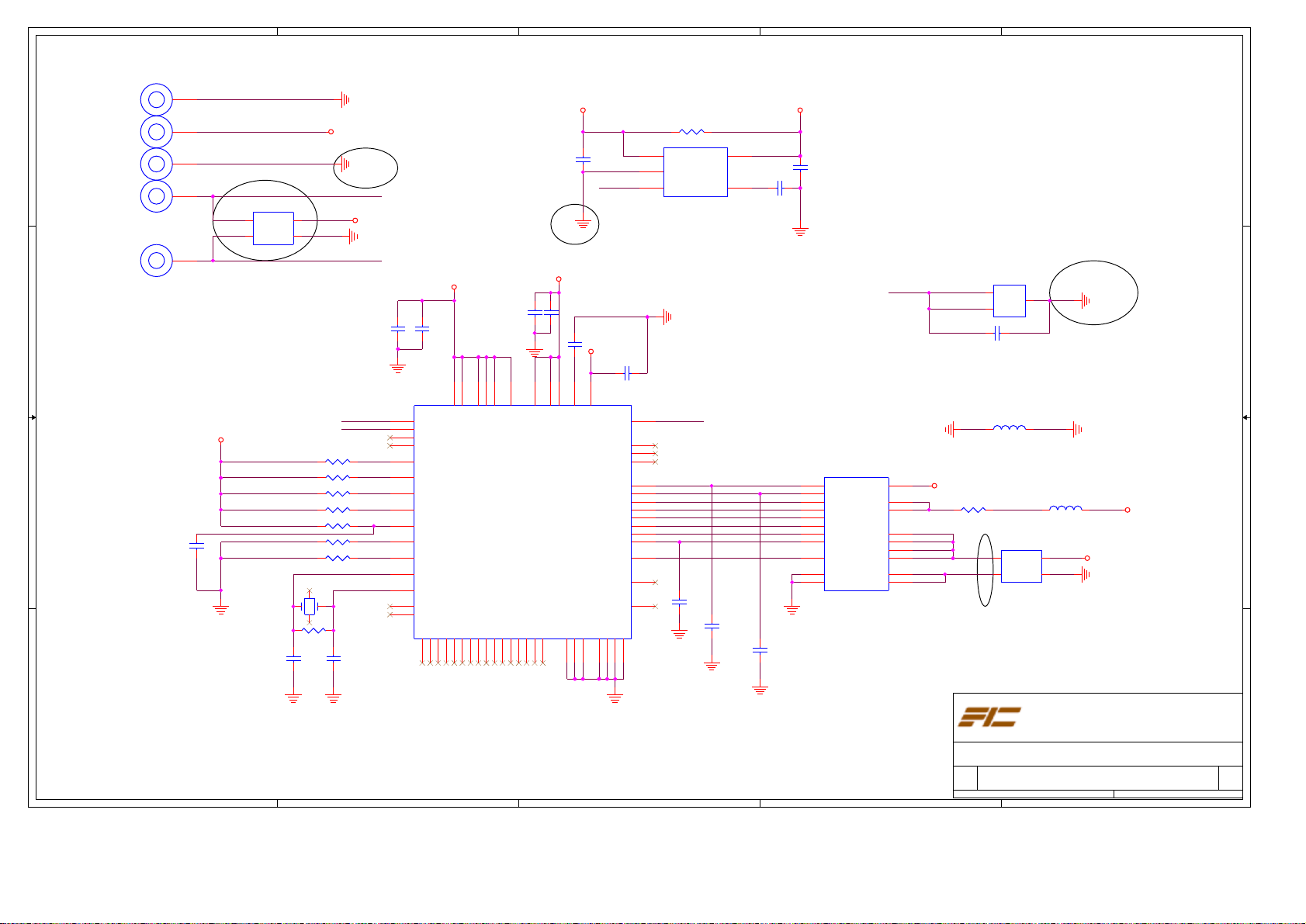

Page 10

8

D D

7

THERMAL SENSOR

6

5

4

1000pF 50V 10% SMT0402 X7R LR

5VDDM

C196

FAN_PWM44

3

Q18

TRANS M-FET-P APM2301AAC-TRL -20V -3A SOT23 3PIN ANPEC LR

DS

G

R123

10KΩ 5% 1/16W SMT0402 LR

R133

1KΩ 5% 1/16W SMT0402 LR

Q19

B

NPN PDTC144EU SOT-323 PHILIPS LR

E C

2

1

30mil

FAN1

DIODE ZENER GLZ6.2B 6.2V 20mA MINI-MELF 2PIN PSI LR

QSMCLK_PMU

QSMDAT_PMU

RP25

3VDDM

4

3

1

2

LNR-IC Temperature Sensor G784P81U 3.0-5.5V MSOP-8 8PIN GMT LR

10mil

10mil

U10

8

7

6

QSMCLK_PMU THRM_VCC

VCC

SCLK

SDATA

ALRT#

THM#GND

HOT_DOWN#8,44

LNR-IC Temperture Sensors MAX6657MSA SO 8PIN MAXIM LR

U55

8

SMBCLK

7

SMBDATA

6

ALERT

OVERT1GND

20mil

THRM_VCC

1

2

D+

3

D-

45

HOT_DOWN#

1

VCC

2

DXP

3

DXN

45

H_THERMDAQSMDAT_PMU

H_THERMDC

HOT_DOWN#

C263

2200pF 50V 10% SMT0402 X7R LR

R171

10KΩ 5% 1/16W SMT0402 LR

R173

100Ω 5% 1/16W SMT0402 LR

C262

0.1uF 16V 80-20% SMT0402 Y5V LR

H_THERMDA

H_THERMDC

3VDDA

H_THERMDA 8

H_THERMDC 8

5VDDM

10 mil

10 mil

C C

10KΩ 5% SMT1010 1/16W 4P2R LR

B B

FAN_SPEED44

D21

P N

10 mil

Minimum

10 mil

CN23

1

1

2

2

345

345

CON HR A1250WV-S-03P SMD 3Pin P=1.25 Wire S/T LR

20-24197-30

GND

THERMDA

THERMDC

GND

Q17

SMCLK_PMU44,47

A A

5VDDM

1/29 EMI

C873

SMDAT_PMU44,47

8

D S

R95

2.2KΩ 5% 1/16W SMT0402 LR

0.1uF 16V 80-20% SMT0603 Y5V LR

D S

G

G

QSMCLK_PMU

TRANS M-FET-N 2N7002 60V 115mA SOT-23 3PIN PSI LR

Q16

QSMDAT_PMU

TRANS M-FET-N 2N7002 60V 115mA SOT-23 3PIN PSI LR

7

3VDDM

3VDDM8,12,15,17,18,19,20,21,22,23,24,26,27,28,29,30,31,33,35,37,38,39,42,43,44,46,49,52,53

3VDDA

3VDDA20,21,22,23,24,26,27,29,33,34,35,42,43,44,47,49,51

5VDDM

5VDDM23,28,29,31,40,41,49

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

6

5

4

3

Date: Sheet of

2

(886-2)8751-8751

MR040T>Merom+Crestline GM965+ICH8M

CPU Thermal

Confidential

10 56Monday, July 30, 2007

1

0.4

檔

Page 11

10

hexainf@hotmail.com

9

8

7

6

5

4

3

2

1

NB 965PM:05-23767-01 (REV. B0)

NB 965GM:05-23768-01 (REV. B0)

H H

H_A#[35..3]

H_REQ#[4..0]

G G

H_D#[63..0]8

H_D#[63..0]

1.05VDDM

R548

RES 221Ω 1% 1/16W SMT0402 RR0510S-2210-FN CYNTEC LR

H_SWING

F F

R546

100Ω 1% 1/16W SMT0402 LR

H_RCOMP

R543

RES 24.9Ω 1% 1/16W SMT0402 LR

C722

0.1uF 10V 10% SMT0402 X5R LR

E E

1.05VDDM

R538

54.9Ω 1% 1/16W SMT0402 LR Sn

H_SCOMP

D D

C C

1.05VDDM

R537

54.9Ω 1% 1/16W SMT0402 LR Sn

H_SCOMP#

H_SWING

H_RCOMP

H_SCOMP

H_CPURST#8

H_CPUSLP#8

H_SCOMP#

1.05VDDM

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

AD12

AC14

AD11

AC11

AE11

AH12

AH13

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

M10

N12

N9

H5

P13

K9

M2

W10

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

AE3

AD9

AC9

AC7

AB2

AD7

AB1

Y3

AC6

AE2

AC5

AG3

AJ9

AH8

AJ14

AE9

AJ5

AH5

AJ6

AE7

AJ7

AJ2

AE5

AJ3

AH2

B3

C2

W1

W2

B6

E5

B9

A9

U37A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRESTLINE_1p0

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

HOST

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#3

J13

H_A#[35..3] 8

H_ADS# 8

H_ADSTB#0 8

H_ADSTB#1 8

H_BNR# 8

H_BPRI# 8

H_BREQ# 8

H_DEFER# 8

H_DBSY# 8

H_DPWR# 8

H_DRDY# 8

H_HIT# 8

H_HITM# 8

H_LOCK# 8

H_TRDY# 8

H_DINV#0 8

H_DINV#1 8

H_DINV#2 8

H_DINV#3 8

H_DSTBN#0 8

H_DSTBN#1 8

H_DSTBN#2 8

H_DSTBN#3 8

H_DSTBP#0 8

H_DSTBP#1 8

H_DSTBP#2 8

H_DSTBP#3 8

H_REQ#[4..0] 8

H_RS#0 8

H_RS#1 8

H_RS#2 8

CLK_MCH_BCLK 17

CLK_MCH_BCLK# 17

R558

1KΩ 1% 1/16W SMT0402 LR

12

B B

R554

SPWR 0 5% 1/16W 0402

R557

2KΩ 1% 1/16W SMT0402 LR

C735

0.1uF 10V 10% SMT0402 X5R LR

A A

10

9

8

7

H_AVREF

H_DVREF

1.05VDDM

1.05VDDM8,9,14,15,17,21,23,50

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

6

5

4

3

Date: Sheet of

(886-2)8751-8751

MR040T>Merom+Crestline GM965+ICH8M

Crestline Host (1/6)

2

Confidential

11 56Monday, July 30, 2007

1

檔

0.4

Page 12

10

H H

SM_RCOMP_VOH

SM_RCOMP_VOL

C164

C163

2.2uF 6.3V 80-20% SMT0603 Y5V LR

0.01uF 16V 10% SMT0402 X7R LR

C653

C655

2.2uF 6.3V 80-20% SMT0603 Y5V LR

0.01uF 16V 10% SMT0402 X7R LR

G G

F F

E E

PM_BMBUSY#22 DFGT_VID_1 52

D D

H_DPRSTP#8,21,46

PM_EXTTS#018

PM_EXTTS#119

DELAY_VR_PWRGOOD24,46

PLT_RST#20

PM_THRMTRIP#8,21

PM_DPRSLPVR22,46

C C

1.8VDDS

R102

1KΩ 1% 1/16W SMT0402 LR

R524

3.01K 1% 1/10W 0603 LR

R522

1KΩ 1% 1/16W SMT0402 LR

M_A_A1418

M_B_A1419

MCH_BSEL017

MCH_BSEL117

MCH_BSEL217

R160

100Ω 5% 1/16W SMT0402 LR

9

MCH_CFG_5

MCH_CFG_9

MCH_CFG_12

MCH_CFG_13

MCH_CFG_16

MCH_CFG_19

MCH_CFG_20

PM_EXTTS#0

PM_EXTTS#1

RST_IN#_MCH

8

U37B

P36

RSVD1

P37

RSVD2

R35

RSVD3

N35

RSVD4

AR12

RSVD5

AR13

RSVD6

AM12

RSVD7

AN13

RSVD8

J12

RSVD9

AR37

RSVD10

AM36

RSVD11

AL36

RSVD12

AM37

RSVD13

D20

RSVD14

H10

RSVD20

B51

RSVD21

BJ20

RSVD22

BK22

RSVD23

BF19

RSVD24

BH20

RSVD25

BK18

RSVD26

BJ18

RSVD27

BF23

RSVD28

BG23

RSVD29

BC23

RSVD30

BD24

RSVD31

BJ29

RSVD32

BE24

RSVD33

BH39

RSVD34

AW20

RSVD35

BK20

RSVD36

C48

RSVD37

D47

RSVD38

B44

RSVD39

C44

RSVD40

A35

RSVD41

B37

RSVD42

B36

RSVD43

B34

RSVD44

C34

RSVD45

P27

CFG_0

N27

CFG_1

N24

CFG_2

C21

CFG_3

C23

CFG_4

F23

CFG_5

N23

CFG_6

G23

CFG_7

J20

CFG_8

C20

CFG_9

R24

CFG_10

L23

CFG_11

J23

CFG_12

E23

CFG_13

E20

CFG_14

K23

CFG_15

M20

CFG_16

M24

CFG_17

L32

CFG_18

N33

CFG_19

L35

CFG_20

G41

PM_BM_BUSY#

L39

PM_DPRSTP#

L36

PM_EXT_TS#_0

J36

PM_EXT_TS#_1

AW49

PWROK

AV20

RSTIN#

N20

THERMTRIP#

G36

DPRSLPVR

BJ51

NC_1

BK51

NC_2

BK50

NC_3

BL50

NC_4

BL49

NC_5

BL3

NC_6

BL2

NC_7

BK1

NC_8

BJ1

NC_9

E1

NC_10

A5

NC_11

C51

NC_12

B50

NC_13

A50

NC_14

A49

NC_15

BK2 R32

NC_16 TEST_2

CRESTLINE_1p0

DDR MUXINGCLKDMI

CFGRSVD

PM

GRAPHICS VIDME

NC

MISC

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF_0

SM_VREF_1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

TEST_1

7

AV29

BB23

BA25

AV23

AW30

BA23

AW25

AW23

BE29

AY32

BD39

BG37

BG20

BK16

BG16

BE13

BH18

BJ15

BJ14

BE16

SM_RCOMP

BL15

BK14

BK31

BL31

AR49

AW4

20miles

B42

C42

H48

H47

K44

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

E35

A39

C38

B39

E36

AM49

AK50

AT43

AN49

AM50

0.1uF 10V 10% SMT0402 X5R LR

H35

K36

G39

G40

A37

R517 RES 20Ω 1% 1/16W SMT0402 LR

SM_RCOMP#

R518 RES 20Ω 1% 1/16W SMT0402 LR

SM_RCOMP_VOH

SM_RCOMP_VOL

R162 10KΩ 1% 1/16W SMT0402 LR(NU)

R190 0Ω 5% 1/16W SMT0402 LR

R158 10KΩ 1% 1/16W SMT0402 LR(NU)

DMI_TXP3

DMI_TXP2

DMI_TXP1

DMI_TXP0

DMI_TXN3

DMI_TXN2

DMI_TXN1

DMI_TXN0

DMI_RXP3

DMI_RXP2

DMI_RXP1

DMI_RXP0

DMI_RXN3

DMI_RXN2

DMI_RXN1

DMI_RXN0

DFGT_VID_0

DFGT_VID_1

DFGT_VID_2

DFGT_VID_3

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_MCH_OE#

R553 0Ω 5% 1/16W SMT0402 LR

R204 20KΩ 1% 1/16W SMT0402 LR

M_CLK_DDR0 18

M_CLK_DDR1 18

M_CLK_DDR3 19

M_CLK_DDR4 19

M_CLK_DDR#0 18

M_CLK_DDR#1 18

M_CLK_DDR#3 19

M_CLK_DDR#4 19

M_CKE0 18

M_CKE1 18

M_CKE3 19

M_CKE4 19

M_CS#0 18

M_CS#1 18

M_CS#2 19

M_CS#3 19

M_ODT0 18

M_ODT1 18

M_ODT2 19

M_ODT3 19

DREFCLK 17

DREFCLK# 17

DREFSSCLK 17

DREFSSCLK# 17

CLK_PCIE_3GPLL 17

CLK_PCIE_3GPLL# 17

DMI_TXP3 20

DMI_TXP2 20

DMI_TXP1 20

DMI_TXP0 20

DMI_TXN3 20

DMI_TXN2 20

DMI_TXN1 20

DMI_TXN0 20

DMI_RXP3 20

DMI_RXP2 20

DMI_RXP1 20

DMI_RXP0 20

DMI_RXN3 20

DMI_RXN2 20

DMI_RXN1 20

DMI_RXN0 20

DFGT_VID_0 52

DFGT_VID_2 52

DFGT_VID_3 52

DFGT_VR_EN 52

CL_CLK0 22

CL_DATA0 22

MPWROK 22,24,44

CL_RST#0 22

C674

CLK_MCH_OE# 17

MCH_ICH_SYNC# 22

6

R? , R?

For Crestline

1.8VDDS

1.25VDDM

1KΩ 1% 1/16W SMT0402 LR

CL_REFCL_REF

80.6 ohmFor Calero

20 ohm

LCD_BRIGHTNESS27,44

1.8VDDS

M_VREF

R1796 150Ω 1% 1/16W SMT0402 LR

R1797 150Ω 1% 1/16W SMT0402 LR

R1798 150Ω 1% 1/16W SMT0402 LR

R535

R532

RES 392Ω 1% 1/16W SMT0402 LR

5

R193 0Ω 5% 1/16W SMT0402 LR(NU)

LVDS_ENABKL44

R1791 SHW 0 5% 1/16W 0402

LVDS_DDC_CLK27

LVDS_DDC_DATA27

LVDS_ENALCD27

R1792

RES 2.4KΩ 1% 1/16W SMT0402 LR

LVDS_TXCLK_LN27

LVDS_TXCLK_LP27

LVDS_TXOUT_L0N27

LVDS_TXOUT_L1N27

LVDS_TXOUT_L2N27

LVDS_TXOUT_L0P27

LVDS_TXOUT_L1P27

LVDS_TXOUT_L2P27

R1793 75Ω 1% 1/16W SMT0402 LR

TV_Y28

TV_C28

R1794 150Ω 1% 1/16W SMT0402 LR

R1795 150Ω 1% 1/16W SMT0402 LR

BLUE28

GREEN28

RED28

Q_VECLK28

Q_VEDAT28

HSYNC28

VSYNC28

4

U37C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

R129100KΩ 5% 1/16W SMT0402 LR

TV_DCONSEL0

TV_DCONSEL1

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

G50

LVDSA_DATA_0

E50

LVDSA_DATA_1

F48

LVDSA_DATA_2

G44

LVDSB_DATA#_0

B47

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LVDSB_DATA_2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

CRESTLINE_1p0

R1789

RES 1.3KΩ 1% 1/16W SMT0402 RR0510S-132-FN CYNTEC LR

3

2

1

1.25VDDM_PEG

R185

RES 24.9Ω 1% 1/16W SMT0402 LR

PEG_COMP

N43

PEG_COMPI

M43

PEG_COMPO

J51

PEG_RX#_0

L51

PEG_RX#_1

N47

PEG_RX#_2

T45

PEG_RX#_3

T50

PEG_RX#_4

U40

PEG_RX#_5

Y44

PEG_RX#_6

Y40

PEG_RX#_7

AB51

PEG_RX#_8

W49

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

N45

U39

U47

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

LVDS

TV VGA

PCI-EXPRESS GRAPHICS

3VDDM

R130 2.2KΩ 5% 1/16W SMT0402 LR

TV_DCONSEL0

R131 2.2KΩ 5% 1/16W SMT0402 LR

TV_DCONSEL1

PM_EXTTS#0

PM_EXTTS#1

CLK_MCH_OE#

RP26

124

3

10KΩ 5% SMT1010 1/16W 4P2R LR

R223 10KΩ 5% 1/16W SMT0402 LR

B B

M_VREF18,19,51

1.25VDDM15,17,23,53

1.8VDDS14,15,18,19,51,53

3VDDM8,10,15,17,18,19,20,21,22,23,24,26,27,28,29,30,31,33,35,37,38,39,42,43,44,46,49,52,53

Confidential

12 56Monday, July 30, 2007

1.25VDDM_PEG

M_VREF

1.25VDDM

1.8VDDS

3VDDM

1

0.4

GMCH Strapping Requirements

3VDDM

MCH_CFG_19

R221 4.02KΩ 1% 1/10W SMT0603 LR

MCH_CFG_20

R222 4.02KΩ 1% 1/10W SMT0603 LR(NU)

MCH_CFG_5

R218 4.02KΩ 1% 1/10W SMT0603 LR(NU)

MCH_CFG_9

R216 4.02KΩ 1% 1/10W SMT0603 LR(NU)

MCH_CFG_12

R220 4.02KΩ 1% 1/10W SMT0603 LR(NU)

MCH_CFG_13

R217 4.02KΩ 1% 1/10W SMT0603 LR(NU)

MCH_CFG_16

A A

R219 4.02KΩ 1% 1/10W SMT0603 LR(NU)

CFG [2:0]

CFG5

CFG9

CFG [12:13]

10

9

011 = 667 MT/s ( 677MHz ) FSB

001 = 533 MT/s ( 533MHz ) FSB

0 = DMI * 2

1 = DMI * 4 ( Default )

0 = Lane Reverse

1 = Normal Operation ( Default )

00 = Clock Gating Disable

01 = XOR Mode Enabled

10 = All Z Mode Enable

11 = Normal Operation ( Default )

8

CFG16

CFG18

(PCIE)

CFG19

CFG20

7

0 = Dynamic ODT Disabled

1 = DMI Lane Reversal Enabled ( Default )

0 = VCC->1.05V ( Default )

1 = VCC->1.5V

0 = Normal ( Default )

1 = Lanes Reversed

0 = Only SDVO or PCIE X1 is operationl ( default )

1 = SDVO or PCIE X1 are operatingsimulaneously via the PEG port.

6

5

(DMI lane)

4

Title

MR040T>Merom+Crestline GM965+ICH8M

Size Document Number Rev

C

Crestline DMI/Graphic (2/6)

3

Date: Sheet of

2

1.25VDDM_PEG15

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

檔

Page 13

10