Fairchild Semiconductor V320MTCX, V320MTC Datasheet

April 1998

Revised October 1998

V320 8-Bit Registered Bus Transceiver

© 1998 Fairchild Semiconductor Corporation DS500149.prf www.fairchildsemi.com

V320

8-Bit Registered Bus Transcei ver

General Description

The V320 is an 8-bit universal bus transceiver designed for

high speed interfa cing with th e VME 320 ba ckplane. It has

output character isti cs op timi ze d for d rivi ng la rge c apa ci tive

loads and features modified input levels (V

IH/VIL

) for

increased noise immunity and reduced input skew. The

V320 functionalit y consists of bus transceiver circuits with

3-STATE, D-type flip-flops, an d control circuitry arranged

for multiplexed t ransmiss ion of d ata direct ly from the inp ut

bus or from the internal r egisters . Data on the A or B bus

will be clocked into the registers as the appropriate clock

pin goes to a high logic lev el. OE

and direction pins a re

provided to control the transceiver function. In the transceiver mode, dat a p re sen t a t the high impedan ce p or t m ay

be store d in ei the r th e A or B re gis t er or in bo t h . Th e s ele c t

controls can multiplex stored and real time (transparent

mode) data. The direction control dete rmines which bus

will receive data when the enable control OE

is active

LOW. In the isolation mode (OE

HIGH) A data may be

stored in the B regis ter and /or B data may be st ored in t he

A register.

Features

■ Independent registers for A and B buses

■ Multiplexed real-time and stored data

■ Guaranteed output skew

■ Guaranteed MOS (Multiple Output Switching) Specifica-

tions

■ Output switching specified for both 50 pF and 250 pF,

and 500 pF loads

■ Guaranteed simultaneous switching noise level (V

OLP

/

V

OLV

) and dynamic threshold performance (V

IHD/VILD

)

■ Glitch free power up/down high impedance for live insertion

■ BiCMOS technology for high drive and lo w power dissipation

■ −40°C to 85°C commercial temperature and V

CC

specifi-

cations

■ Modified specifications across V

CC

and temperature

(V

CC

= 5.0V ±1%, T = 25°C ± 20°C) present more realis-

tic system conditions

■ Available in TSSOP (MTC)

Ordering Code:

Device also available in Tape and Reel. Specify by appe nding suffix letter “X” to the ordering code.

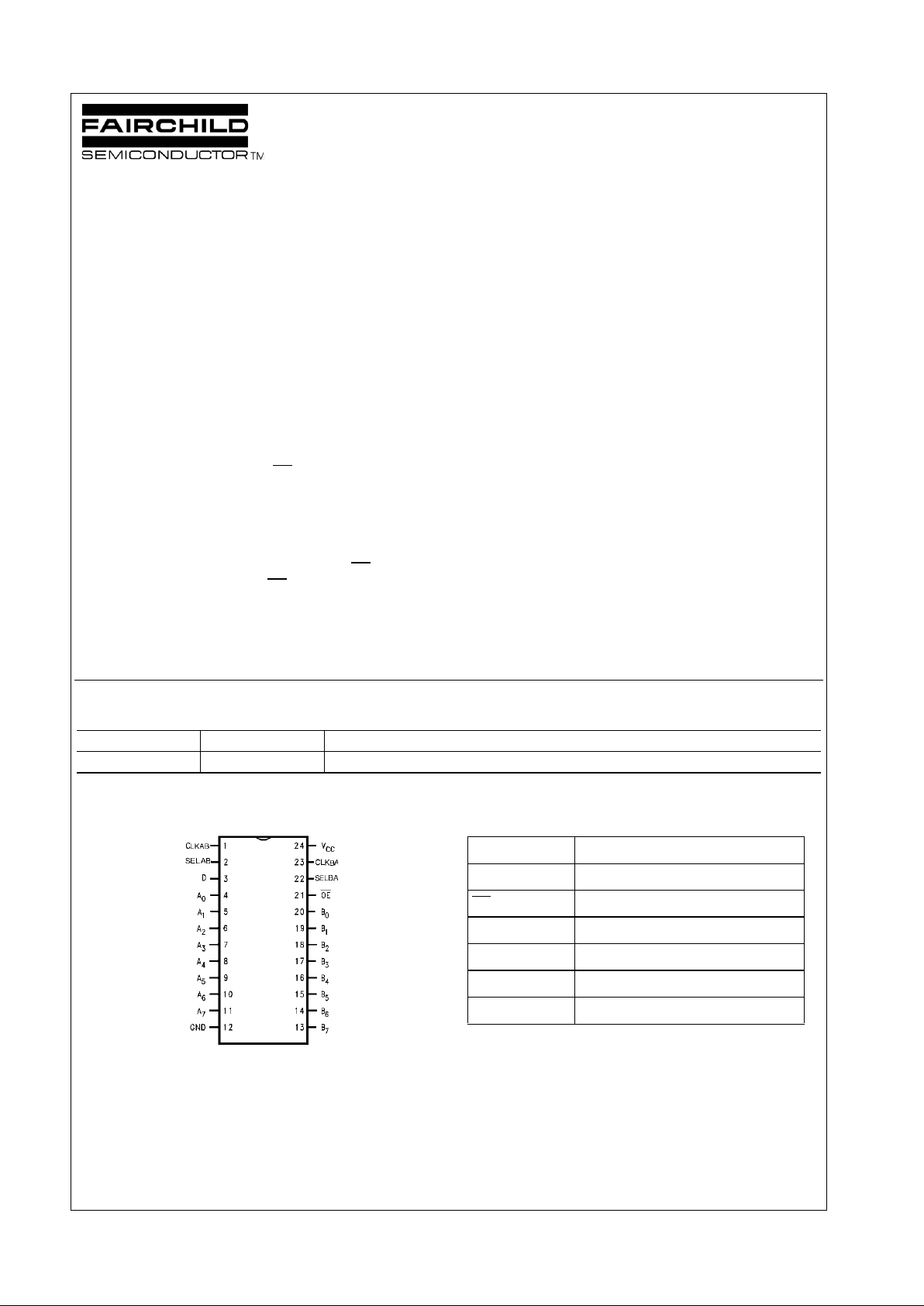

Connection Diagram Pin Descriptions

Order Number Package Number Package Description

V320MTC MTC24 24-Lead Thin Shrink Small Outline Package, JEDEC MO-153, 4.4mm Wide

Pin Names Description

D Direction A-to-B (High) B-to A (Low)

OE

Output Enable (Active LOW)

CLKAB/SELAB A-to-B Clock/Select

CLKBA/SELBA B-to-A Clock/Select

A0–7 A Inputs/Outputs (TTL)

B0–7 B Inputs/Outputs (TTL)

www.fairchildsemi.com 2

V320

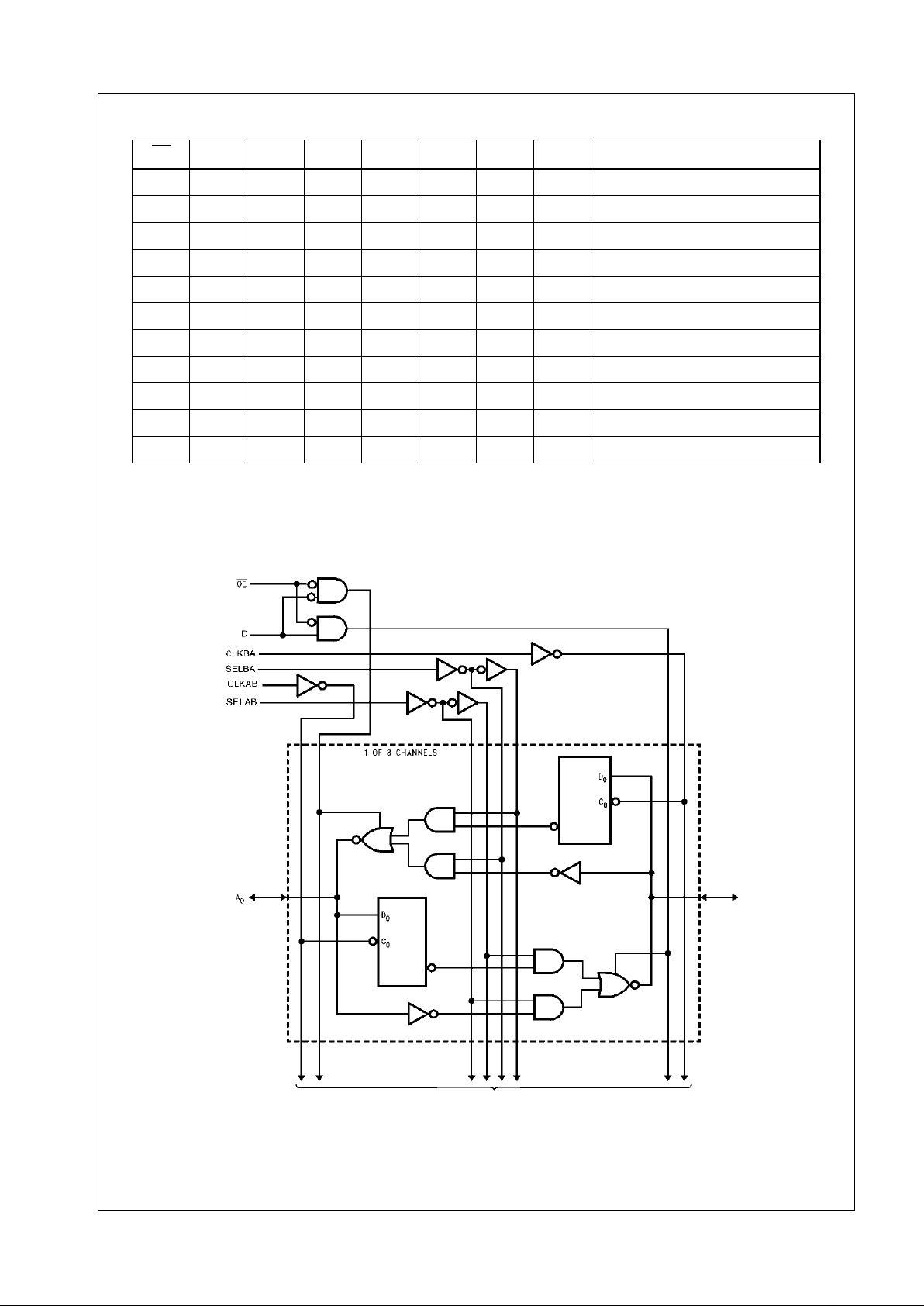

Functional Table

L = Low

H = High

LH = Low to High transition

X = Don’t Care

Logic Diagram

Please note that this diagram is pr ov ided only for the unders t anding of logic opera t ions and should not be us ed to estimate propa gation delays.

OE D SELAB SELBA CLKAB CLKBA

A

0–A7B0–B7

Function

H X X X H or L H or L Isolation

H X X X LH X Input Input CLK A Data into A

HXXXXLH CLK B Data into A Reg.

LHLXXX A to B – Transparent

L H L X LH X CLK A Data into A Reg.

L H H X H or L X Input Output A Reg. to B (Storage)

L H H X LH X CLK A Data into A Reg. and B output

L L X L X X B to A – Transparent

L L X L X LH CLK B Data into B Reg.

L L X H X H or L Output Input B Reg. to A (Storage)

L L X H X LH CLK B Data into B Reg.and A output

3 www.fairchildsemi.com

V320

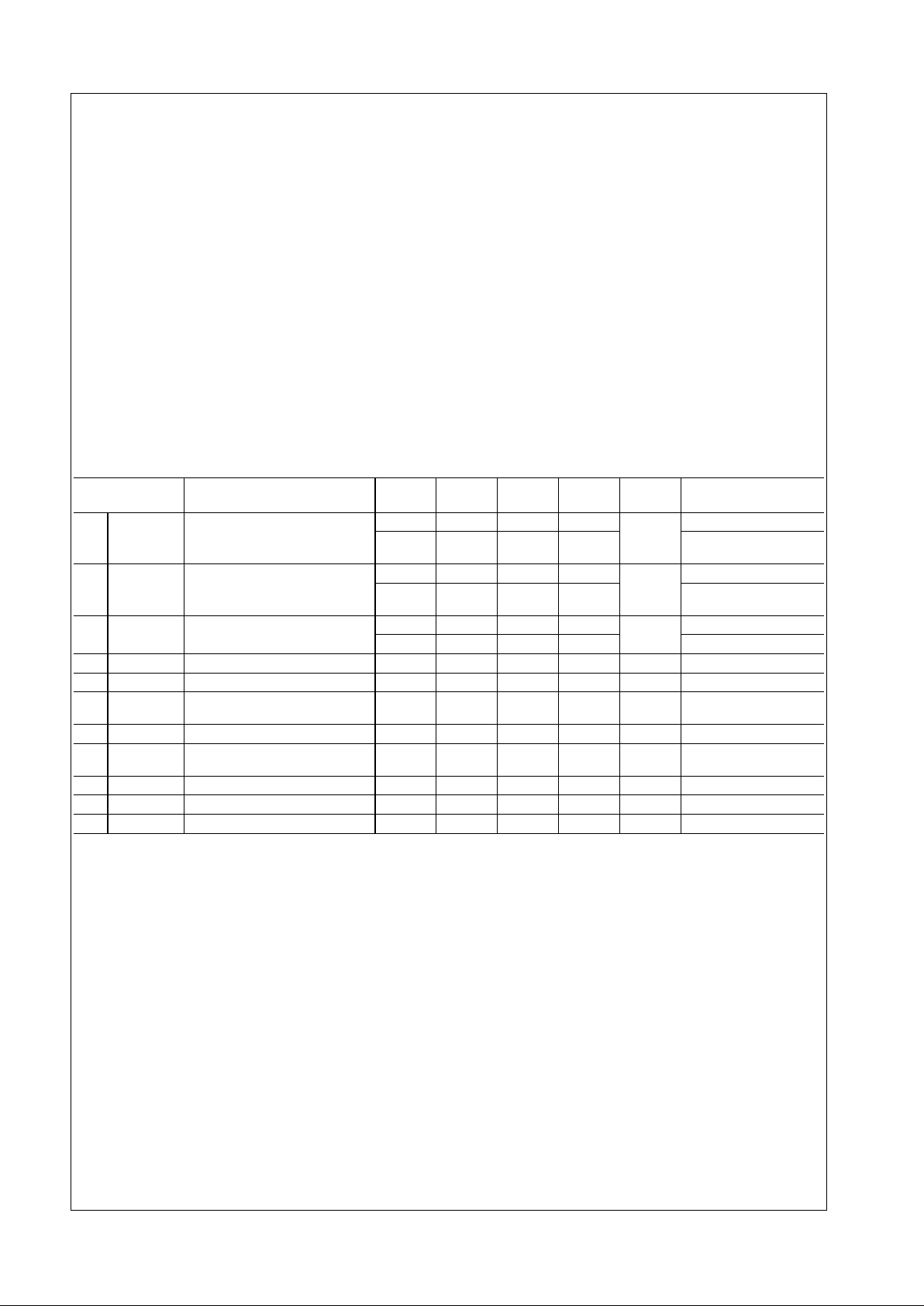

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

Note 1: Absolute maxim um ratings are values be yond which the device

may be damaged or have its useful life impaired. Functional operation

under these conditions is not impli ed.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

DC Electrical Characteristics (4.5V < VCC ≤ 5.5V)

Over Recommended Operating Free-Air Temperature Range (Unless Otherwise Noted)

Note 3: Extended Characteristics (4.95 > VCC > 5.05, T = 25°C ± 20°C)

DC Input Voltage (VI) −0.5V to +7.0V

DC Output Voltage (V

O

)

Outputs 3-STATE −0.5V to +7.0V

Outputs Active (Note 2) −0.5V to V

CC

+0.5V

DC Output Sink Current into

A-port/B-port I

OL

64 mA

DC Output Source Current from

A-port/B-port I

OH

−32 mA

DC Input Diode Current (I

IK

)

V

I

< 0

V

−30 mA to +5.0 mA

ESD Rating typical > 2000V

Storage temperature (T

STG

) −65° C to +15°C

Max I

OL

(Current Applied to a

LOW Output) 2 X I

OL

Spec.

Supply Voltage V

CC

Operating V

CC

4.5V to 5.5V

Minimum Input Edge Rate

Data Input 50 mV/ns

Enable 20 mV/ns

Clock 100 mV/ns

Operating Temperature (T

A

) −40°C to +85°C

Symbol Parameter

V

CC

(V)

Min Typ Max Units Conditions

VIHB-Port/A-Port HIGH Level Input Voltage 4.5–5.5 2.0 V Recognized HIGH Signal

4.95–5.05 1.8

(Note 3)

VILB-Port/A-Port LOW Level Input Vo ltage 4.5–5.5 0.8 V Recognized LOW Signal

4.95–5.05 1.2

(Note 3)

VOHB-Port/A-Port HIGH Level Output Voltage 4.5 2.5 V −3 mA

4.5 2.0 −32 mA

I

OH

B-Port/A-Port High Level Output Current Drive 4.5 −32 mA VOH = 2.0V

VOLB-Port/A-Port LOW Level Output Voltage 4.5 0.55 V 64 mA

I

OL

B-Port/A-Port Low Level Output Current Drive

(Sink)

4.5 64 mA VOL = 0.55V

I

OS

B-Port/A-Port Short Circuit Current 5.5 −100 −275 mA V

OUT

= 0.0V

I

OFF

A-Port and

Control Pins

Power-OFF Leakage Current 0.0 100uA uA V

OUT

= 5.5V, All Others

GND

I

CCH

B-Port/A-Port Quiescent Power Supply Current 5.5 250 uA All Outputs HIGH

I

CCI

B-Port/A-Port B-Port/A-Port 5.5 30 mA All Outputs LOW

I

CCZ

B-Port/A-Port 3-STATE Power Supply Current 5.5 50 uA All Outputs 3-STATE

Loading...

Loading...