Fairchild Semiconductor SPT8100 Datasheet

FEATURES

SPT8100

16-BIT, 5 MSPS CMOS A/D CONVERTER

TECHNICAL DATA

JANUARY 9, 2002

APPLICATIONS

• 16-bit, 5 MSPS CMOS analog-to-digital converter

• On-chip PGA: gain range from 0 to 19.5 dB in se v e n

selectable settings:

0 dB, +2.9 dB, +5.8 dB, +11.8 dB , +14.8 dB , +17.5 dB ,

+19.5 dB

• DLE: ±0.5 LSB , ILE: ±1.25 LSB

• SFDR: 94 dB @ ƒIN = 900 kHz, –8.1 dBFS

• Internal sample-and-hold and voltage reference

• Po wer dissipation: 465 mW at 5 MSPS

• +5 V analog supply and +3.3 to +5.25 V digital output

supply

• 44-lead LQFP plastic package

DESCRIPTION

The SPT8100 is a high-performance, 16-bit analog-todigital converter that operates at a sample rate of up to

5 MSPS. Excellent dynamic performance and high linearity is achieved by a digitally calibrated pipelined architecture fabricated in CMOS process technology.

A low-noise programmable gain amplifier (PGA) is also incorporated on chip. The PGA is digitally programmable in

seven selected settings over a 0 to +19.5 dB range. The

• Data acquisition systems

• IR imaging

• Scanners and digital copiers

• High-end CCD cameras

• Medical imaging

• Wireless communications

• Lab and test equipment

• Automatic test equipment

SPT8100 also features an on-chip internal sample-andhold and internal reference for minimal e xternal circuitry .

It operates from a single +5 V supply. Total power dissipation, including internal reference, is 465 mW. A separate

digital output supply pin is provided for +3.3 V or 5 V logic

output levels. The SPT8100 is available in a 44-lead LQFP

package over the industrial temperature range of –40 °C to

+85 °C.

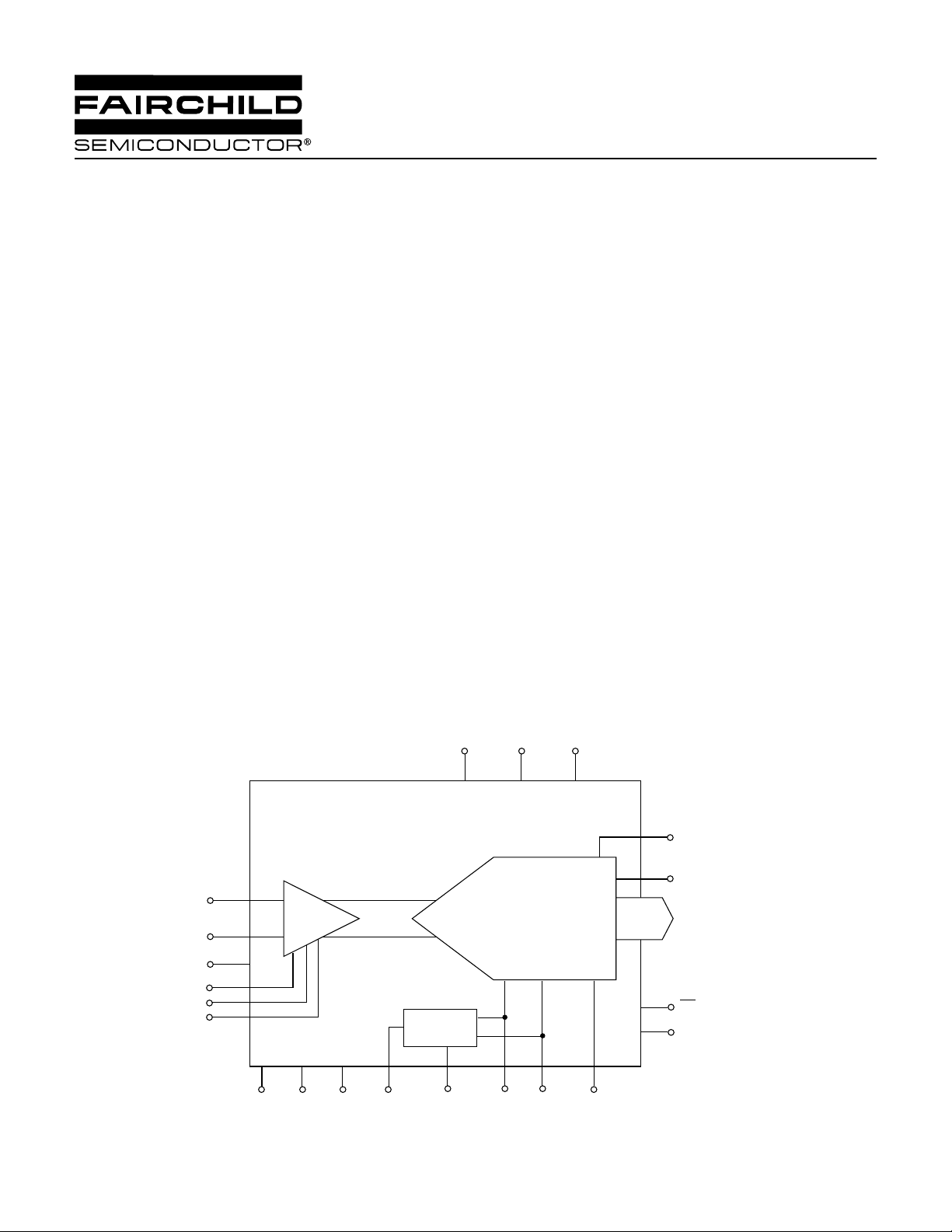

BLOCK DIAGRAM

V

+

IN

V

–

IN

V

CM

GS2 – GS0

(Gain Set)

Low-Noise

AGND

PGA

DD

DV

+5V

AV

+5V

16-bit, 5 MSPS ADC

VREF

OGNDDGND

BIAS

C

(Ext Bias

Capacitor)

BIAS

(Ext Bias

Resistor)

V

R

RTVRB

DD

OV

DD

+3/5 V

CLK

16-bits

OE (Output Enable)

OVR (Over-Range)

D15 – D0

(Data Outputs)

RS (Reset)

RDY (Ready)

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply V oltages

AVDD...................................................................... +6 V

DVDD..................................................................... +6 V

OVDD..................................................................... +6 V

Input V oltages

Analog Input ................................. –0.5 V to VDD +0.5 V

CLK Input ............................................................... V

AVDD – DVDD.................................................. ±100 mV

Delta between AGND, DGND , and OGND...... ±100 mV

Output

Digital Outputs.................................................... 10 mA

T emperature

Operating T emperature........................... –40 to +85 °C

Junction T emperature ...................................... +175 °C

Lead Temperature (soldering 10 seconds) ...... +300 °C

DD

Storage T emperature............................ –65 to +150 °C

Note 1: Operation at any Absolute Maximum Rating is not implied. See

Electrical Specifications for proper nominal applied conditions in

typical applications.

ELECTRICAL SPECIFICATIONS

TA=T

otherwise specified.

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Resolution 15.9 16 Bits

DC Accuracy

Analog Input (into PGA)

MIN

to T

, AVDD=DVDD=+5.0 V, OVDD= 3.3 V, ƒS=5 MSPS, 2.5 VPP input span, Gain=0 dB, R

MAX

=1.43 kΩ, unless

EXT

TEST TEST SPT8100

Integral Linearity Error (ILE) V ±1.25 LSB

Differential Linearity Error (DLE) V ±0.5 LSB

Gain Error

Offset Error

1

2

IV –7.5 +7.5 %FSR

IV –5+5%FSR

Differential Input Voltage Range

+, VIN– V5V

V

IN

PPD

Input Capacitance IV 15 pF

Input Resistance

Input Bandwidth

3

4

PGA Gain = 0 dB IV 5.5 kΩ

PGA Gain = 0 dB V 12 MHz

Input Common Mode Voltage Range V 1.15 2.40 3.65 V

Programmable Gain Amp

Composite Input-Referred ƒ

> 300 kHz

IN

Noise Floor PGA Gain = 0 dB V 1.4 LSB

PGA Gain = 2.9 dB V 1.5 LSB

PGA Gain = 5.8 dB V 1.6 LSB

PGA Gain = 11.8 dB V 2.0 LSB

PGA Gain = 14.8 dB V 2.3 LSB

PGA Gain = 17.5 dB V 2.6 LSB

PGA Gain = 19.5 dB V 2.8 LSB

PGA Range V 19.5 dB

PGA Gain Steps

3

VI 0,2.9,5.8,11.8,14.8,17.5,19.5 dB

PGA Gain Accuracy VI ±0.3 dB

Conversion Characteristics

Maximum Conversion Rate VI 5 MSPS

Pipeline Delay (Latency)

Reset Pulse Time (

RS) IV 3 Clocks

5

IV 5.5 Clocks

Reset Calibration Time FS = 5 MSPS V 150 ms

References and External Bias

– VRB (Internal Ref) VI 2.375 2.5 2.625 V

V

RT

Bias Resistor Range (External) V 800 1430 2500 Ω

Output Voltage IV 2.275 2.40 2.525 V

V

CM

Output Current IV 47 µA

V

CM

V

RT

V

RB

1

Total gain error of PGA and ADC using inter nal references.

2

Total offset error of PGA and ADC relative to mid-scale.

3

See table I for input resistance as a function of PGA gain.

4

Input bandwidth is a frequency to which the fundamental energy drops by 3 dB

5

The input is sampled on the falling edge of the clock and is available on the

output after the rising edge of the clock, 5.5 clock cycles later.

V 3.45 3.65 3.85 V

V 0.95 1.15 1.35 V

RMS

RMS

RMS

RMS

RMS

RMS

RMS

SPT8100

2 1/9/02

ELECTRICAL SPECIFICATIONS

TA=T

otherwise specified.

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

MIN

to T

, AVDD=DVDD=+5.0 V, OVDD= 3.3 V, ƒS=5 MSPS, 2.5 VPP input span, Gain=0 dB, R

MAX

=1.43 kΩ, unless

EXT

TEST TEST SPT8100

1

Effective Number of Bits ADC Input = –1 dBFS

2

ƒIN = 60 kHz IV 12.2 13.0 Bits

= 900 kHz V 12.7 Bits

ƒ

IN

Signal-to-Noise Ratio

(without Harmonics) ADC Input = –1 dBFS

2

ƒIN = 75 kHz IV 78 81 dB

ƒ

= 900 kHz V 80 dB

IN

Harmonic Distortion ADC Input = –0.5 dBFS

= 60 kHz IV –92 –84 dB

ƒ

IN

ƒ

= 900 kHz V –82 dB

IN

Signal-to-Noise and Distortion

(SINAD) ADC Input = –1 dBFS

= 60 kHz IV 75 80 dB

ƒ

IN

= 900 kHz V 78 dB

ƒ

IN

Spurious Free Dynamic Range

3

ƒIN = 60 kHz ADC Input = –0.5 dB IV 85 94 dBc

= 900 kHz V 94 dBc

ƒ

IN

= 2 MHz R

ƒ

IN

ƒIN = 3 MHz R

= 1 kΩ @ 10 MSPS V 83 dBc

EXT

= 1 kΩ @ 10 MSPS V 78 dBc

EXT

Two-Tone Intermodulation

3rd Order Distortion ƒ

=400 kHz, ƒ2=410 kHz

1

ƒ1=890 kHz, ƒ2=900 kHz

4

V –94 dB

5

V –89 dB

Inputs

GS0–GS2 Logic 1 Voltage VI 2.4 V

GS0–GS2 Logic 0 Voltage VI 0.8 V

RS Logic 1 Voltage VI 2.0 V

CLK,

RS Logic 0 Voltage VI 0.8 V

CLK,

Maximum Input Current Low VI –10 +10 µA

Maximum Input Current High VI –10 +10 µA

Input Capacitance V 5 pF

Digital Outputs

Logic 1 Voltage I

= –2 mA VI OVDD – 0.5 V

OH

Logic 0 Voltage IOL = 2 mA VI 0.4 V

CLK to Output Delay Time (t

)C

D

= 20 pF IV 30 ns

LOAD

Power Supply Requirements

Voltages OV

AV

DV

Currents I

DD

DD

DD

DD

IV 3.0 3.3 5.25 V

IV 4.75 5.0 5.25 V

IV 4.75 5.0 5.25 V

VI 93 103 mA

Power Dissipation VI 4 65 515 mW

1

Dynamic performance tested at ƒS=4.4 MSPS

2

0 dBFS is 5.0 V peak-to-peak differential

3

ADC Input = –8.1 dBFS, unless otherwise noted

TEST LEVEL CODES

All electrical characteristics are subject

to the following conditions:

All parameters having min/max specifications are guaranteed. The Test Level

column indicates the specific device

testing actually performed during

production and Quality Assurance

inspection. Any blank section in the data

column indicates that the specification is

not tested at the specified condition.

TEST LEVEL TEST PROCEDURE

I 100% production tested at the specified temperature.

II 100% production tested at TA = +25 °C, and sample tested at the

III QA sample tested only at the specified temperatures.

IV Parameter is guaranteed (but not tested) by design and characteriza-

V Parameter is a typical value for information pur poses only.

VI 100% production tested at TA = +25 °C. Parameter is guaranteed

4

Test Conditions: PGA setting of 5.8 dB; Analog Input at ADC = –0.7 dB

5

Test Conditions: PGA setting of 0 dB; Analog Input at ADC = –1.9 dB

specified temperatures.

tion data.

over specified temperature range.

SPT8100

3 1/9/02

Loading...

Loading...