Fairchild Semiconductor SPT7853 Datasheet

SPT7853

TRIPLE 10-BIT, 30 MSPS A/D CONVERTER

FEATURES

• Three 10-bit, 30 MSPS ADCs on one chip

• SINAD of 54.5 dB @ ƒ

• Channel-to-channel cross talk: –66 dB typical

• Channel-to-channel gain matching of <0.1 dB

• Single 2X sample rate clock

• Total power dissipation: 580 mW (typical)

• Tri-state +3 V to +5 V digital outputs CMOS-compatible

• Single +5 V power supply

= 3.58 MHz

IN

GENERAL DESCRIPTION

The SPT7853 has three 10-bit analog-to-digital converters

on one CMOS chip, each with a sample rate of 30 MSPS.

This device is ideal for professional-level video decoding to

4:2:2/4:4:4 CCIR-601 standard specifications for component digital video, including YCrCb and RGB decoding, professional video equipment, video frame grabbers, medical

imaging, flat panel display and projection applications.

The SPT7853 offers significant advantages over discrete

single-channel A/D implementations. Board area, package

count, system cost and power dissipation can greatly be

reduced by using a single SPT7853 device. In addition,

APPLICATIONS

• CCIR-601 (4:2:2/4:4:4) digital component video

• RGB video decoding

• Medical imaging

• Flat panel displays

• PC projectors

several performance advantages exist, including low channel-to-channel cross-talk noise and well matched channelto-channel gain specifications. The three analog-to-digital

converters are driven from a common 2X sample rate

CMOS clock.

The SPT7853 typically consumes only 580 mW of total

power from a single +5 V supply. Digital outputs can operate

with +3 V or +5 V logic and are tri-state capable. The

SPT7853 is offered in a small 52-pin thin quad flat pack

(TQFP) package and operates over the 0 to +70 °C commercial temperature range.

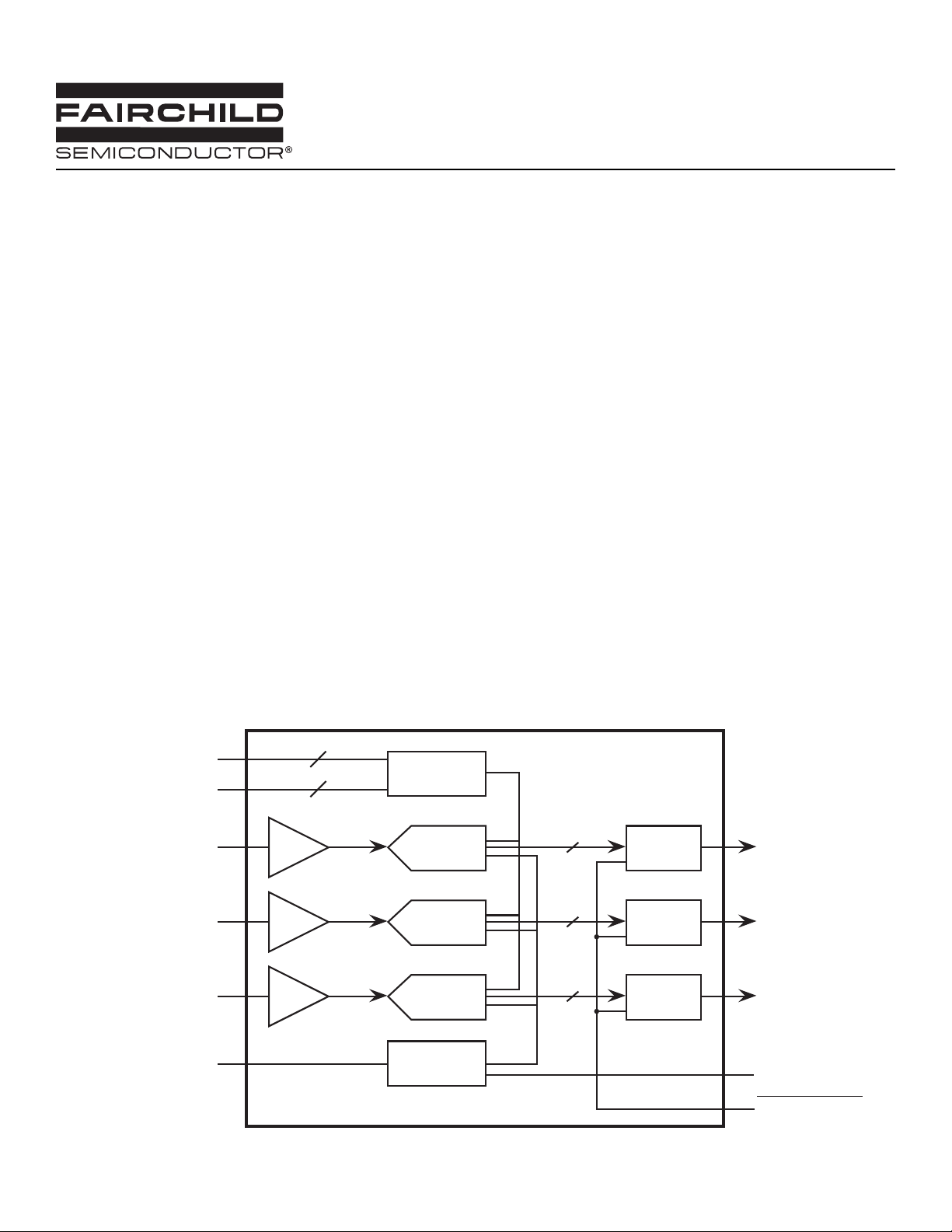

BLOCK DIAGRAM

V

Force/Sense

RH

VRL Force/Sense

V

A

IN

VINB

VINC

Clock

T/H

T/H

T/H

2

2

Reference

Ladder

ADC

A

ADC

B

ADC

C

10

10

10

Output

Buffer

Output

Buffer

Output

Buffer

DA0–9

DB0–9

DC0–9

Timing

Generation

DAV

Output Enable

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages

V

.................................................................................................... +6 V

DD

OV

................................................................................................. +6 V

DD

Temperature

Analog Inputs..................................–0.5 V to VDD +0.5 V

V

................................................–0.5 V to VDD +0.5 V

REF

Clock Input...................................... –0.5 V to VDD +0.5 V

Note: 1. Operation at any Absolute Maximum Rating is not implied and operation beyond the ratings may cause damage to the device.

See Electrical Specifications for proper nominal applied conditions in typical applications.

Output Currents

Digital Outputs .......................................................10 mA

Temperature

Operating Temperature ................................ 0 to + 70 °C

Junction Temperature ......................................... +150 °C

Lead, Soldering (10 seconds)............................. +300 °C

Storage .................................................... –65 to +150 °C

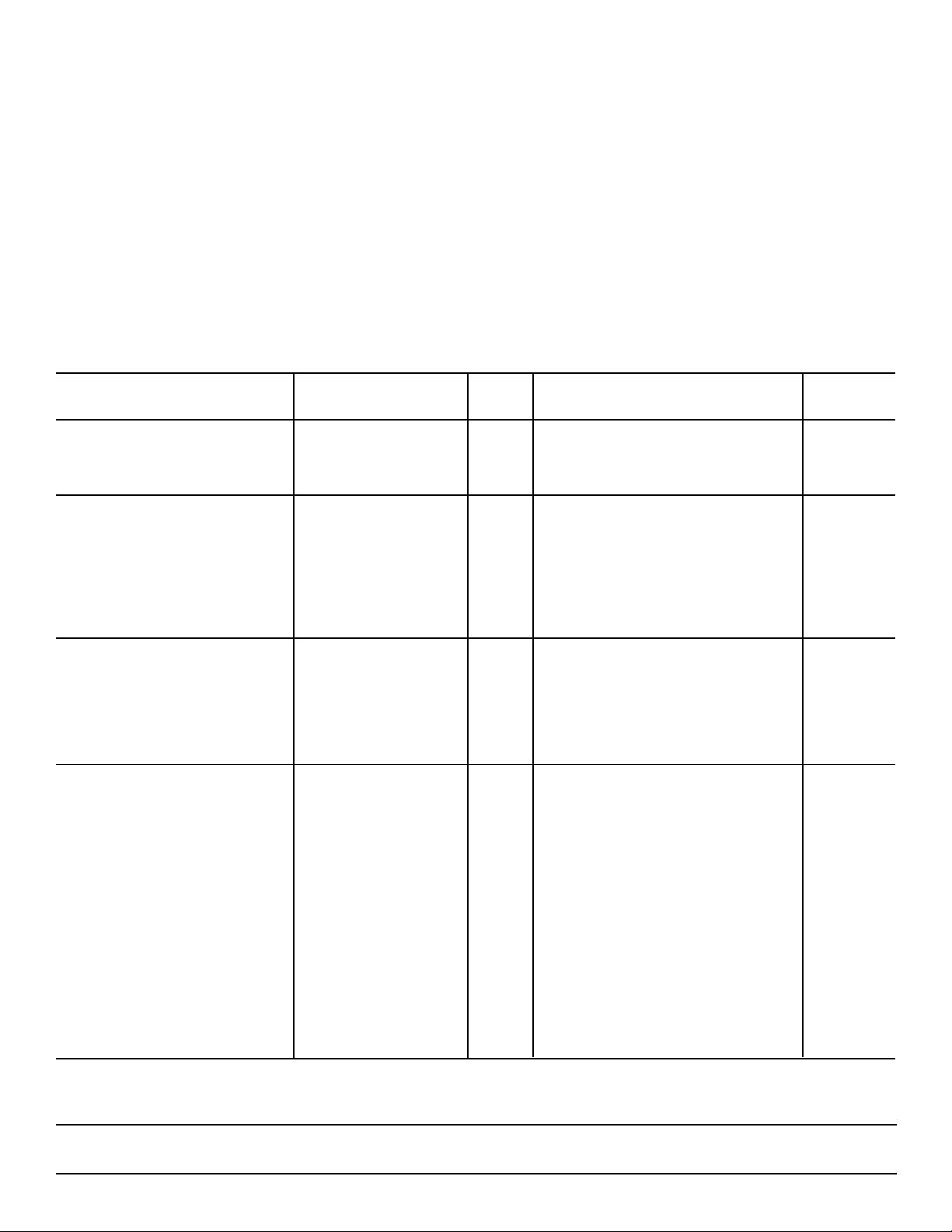

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC Performance

Analog Input

Timing Characteristics

Dynamic Performance

to T

MIN

, VDD=OVDD=+5.0 V, VIN=0 to 4 V, ƒS=30 MSPS, ƒ

MAX

=60 MHz, V

CLK

=4.0 V, V

RHS

=0.0 V, unless otherwise specified.

RLS

TEST TEST SPT7853

Resolution 10 Bits

Differential Linearity ƒs = 20 MSPS V ±0.5 LSB

Integral Linearity ƒs = 20 MSPS V ±1.0 LSB

Input Voltage Range

2

IV V

RLS

V

RHS

V

Input Resistance IV 50 kΩ

Input Capacitance V 5 pF

Input Bandwidth (Full Power) V 120 MHz

–Full-Scale Error

+Full-Scale Error

2

2

V ±0.5 %FS

V ±0.25 %FS

Reference Ladder Resistance VI 120 170 220 Ω

Conversion Rate VI 30 MSPS

Clock Duty Cycle Range IV 45 55 %

Clock-to-Sample Rate Relationship IV 2:1

Pipeline Delay (Latency) IV 12 Clock Cycles

Aperture Delay Time V 5 ns

Aperture Jitter Time V 15 ps

Effective Number of Bits

ƒ

= 3.58 MHz @ 25 °C VI 8.3 8.7 Bits

IN

@ 0 to 70 °C V 8.0 Bits

ƒIN = 10.0 MHz @ 25 °C V 7.4 Bits

Signal-to-Noise Ratio

ƒ

= 3.58 MHz @ 25 °CVI5356dB

IN

@ 0 to 70 °C V 51.6 dB

ƒIN = 10.0 MHz @ 25 °C V 48 dB

Total Harmonic Distortion

ƒIN = 3.58 MHz @ 25 °C VI –56 –58 dB

@ 0 to 70 °C V –54.6 dB

ƒIN = 10.0 MHz @ 25 °C V –51 dB

Signal-to-Noise + Distortion Ratio

ƒIN = 3.58 MHz @ 25 °C VI 52 54.5 dB

@ 0 to 70 °C V 49.7 dB

ƒIN = 10.0 MHz @ 25 °C V 46 dB

2

The full-scale range spans the reference ladder sense pins, V

RHS

and V

. Refer to the Voltage Reference section for discussion.

RLS

2 12/14/99

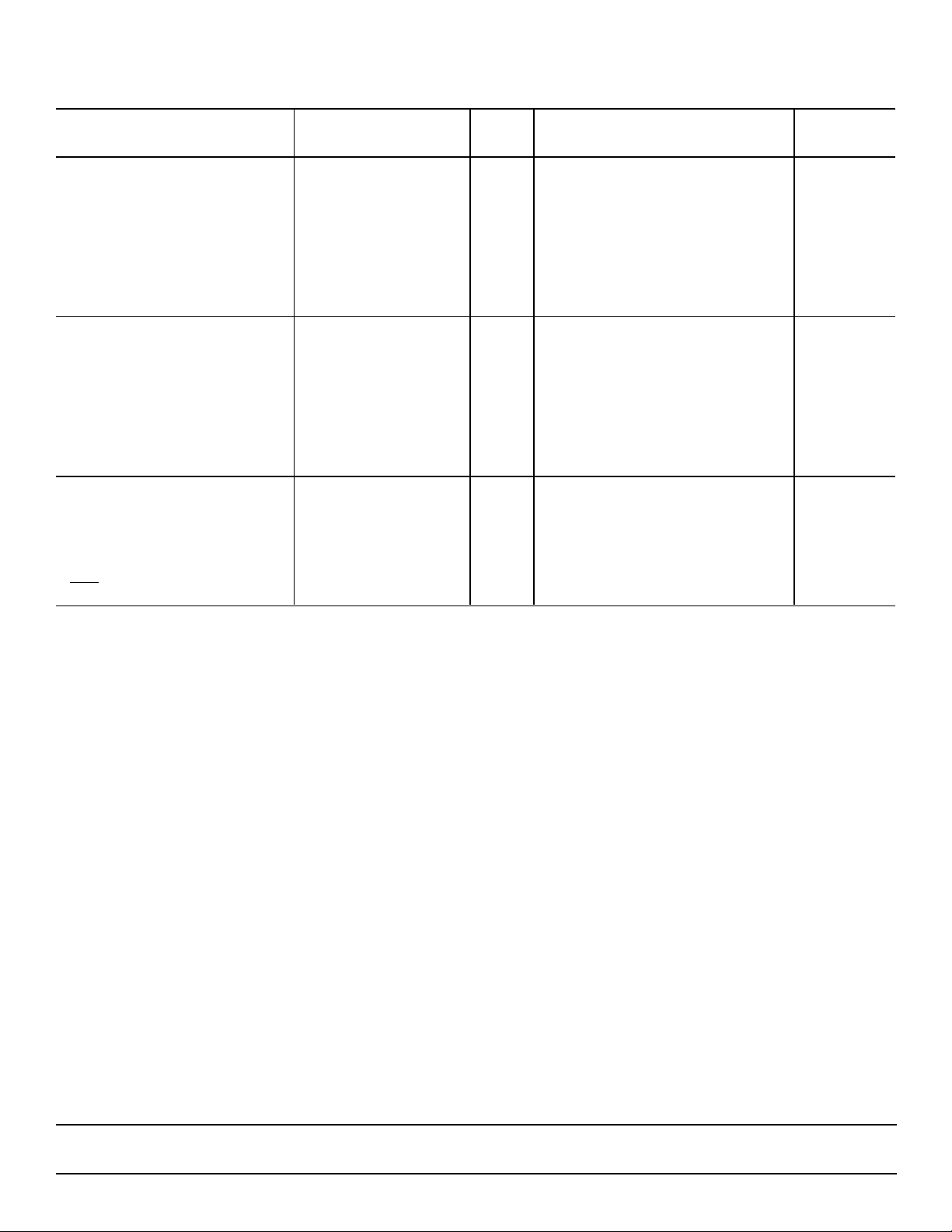

SPT7853

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

Power Supply Requirements

Digital Inputs/Outputs

to T

MIN

Spurious Free Dynamic Range

= 3.58 MHz @ 25 °C V 65 dBc

ƒ

IN

Channel-to-Channel Cross Talk

ƒIN = 3.58 MHz V –66 dB

Channel-to-Channel Gain Matching V ±0.1 dB

Differential Phase V 0.5 Degree

Differential Gain V 0.5 %

V

Supply Voltage IV +4.75 +5.0 +5.25 V

DD

OVDD Supply Voltage IV +2.7 +5.25 V

Supply Current

I

DD

OI

DD

Power Dissipation

Without reference ladder CL = 10 pF V 485 mW

Including reference ladder CL = 10 pF VI 580 750 mW

Digital Input Logic 1 Voltage VI 4.0 V

Digital Input Logic 0 Voltage VI 1.0 V

Digital Output Logic 1 Voltage I

Digital Output Logic 0 Voltage IOL = 800 µA VI 0.4 V

t

RISE/tFALL (CL

OEN to Data Output V 12 ns

, VDD=OVDD=+5.0 V, VIN=0 to 4 V, ƒS=30 MSPS, ƒ

MAX

TEST TEST SPT7853

@ 0 to 70 °C V 56.3 dBc

= 500 µAVIOV

OH

= 10 pF) V 10 ns

=60 MHz, V

CLK

VI 81 105 mA

V911mA

=4.0 V, V

RHS

–0.5 V

DD

=0.0 V, unless otherwise specified.

RLS

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

TEST LEVEL

I

II

III

IV

V

VI

TEST PROCEDURE

100% production tested at the specified temperature.

100% production tested at TA = +25 °C, and sample

tested at the specified temperatures.

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design and

characterization data.

Parameter is a typical value for information purposes

only.

100% production tested at TA = +25 °C. Parameter is

guaranteed over specified temperature range.

SPT7853

3 12/14/99

Loading...

Loading...