Fairchild Semiconductor NM95MS16VBHX, NM95MS16VX, NM95MS16V Datasheet

1

www.fairchildsemi.com

NM95MS16 Plug and Play Front-End Devices for ISA-BUS Systems

July 1998

© 1998 Fairchild Semiconductor Corporation

NM95MS16

Plug and Play Front-End Devices for

ISA-BUS Systems

General Description

The NM95MS16 is the smaller of a family of devices designed to

provide complete Plug and Play Capability for ISA bus systems.

The NM95MS16 includes the necessary state machine logic to

manage the Plug and Play protocol in addition to switches for

steering Interrupt and DMA requests. It also features a built-in 2

kbits of serial EEPROM for storing the resource data specified in

the Plug and Play Standard. In addition, 4 kbits of EEPROM is

available for use by other on-board logic. This device provides a

“truly complete” single-chip solution for implementing Plug and

Play on ISA-Bus Adapter cards. The NM95MS16 supports one

logical device with a flexible choice of DMA/IRQ selection and I/O

Chipselect generation as well as offering 16-bit addressing in

Mode 1.

NM95MS16 is implemented using Fairchild’s Advanced CMOS

process and operates single power supply. The NM95MS16 is

available in a 48-pin TQFP package and 52-pin PLCC package.

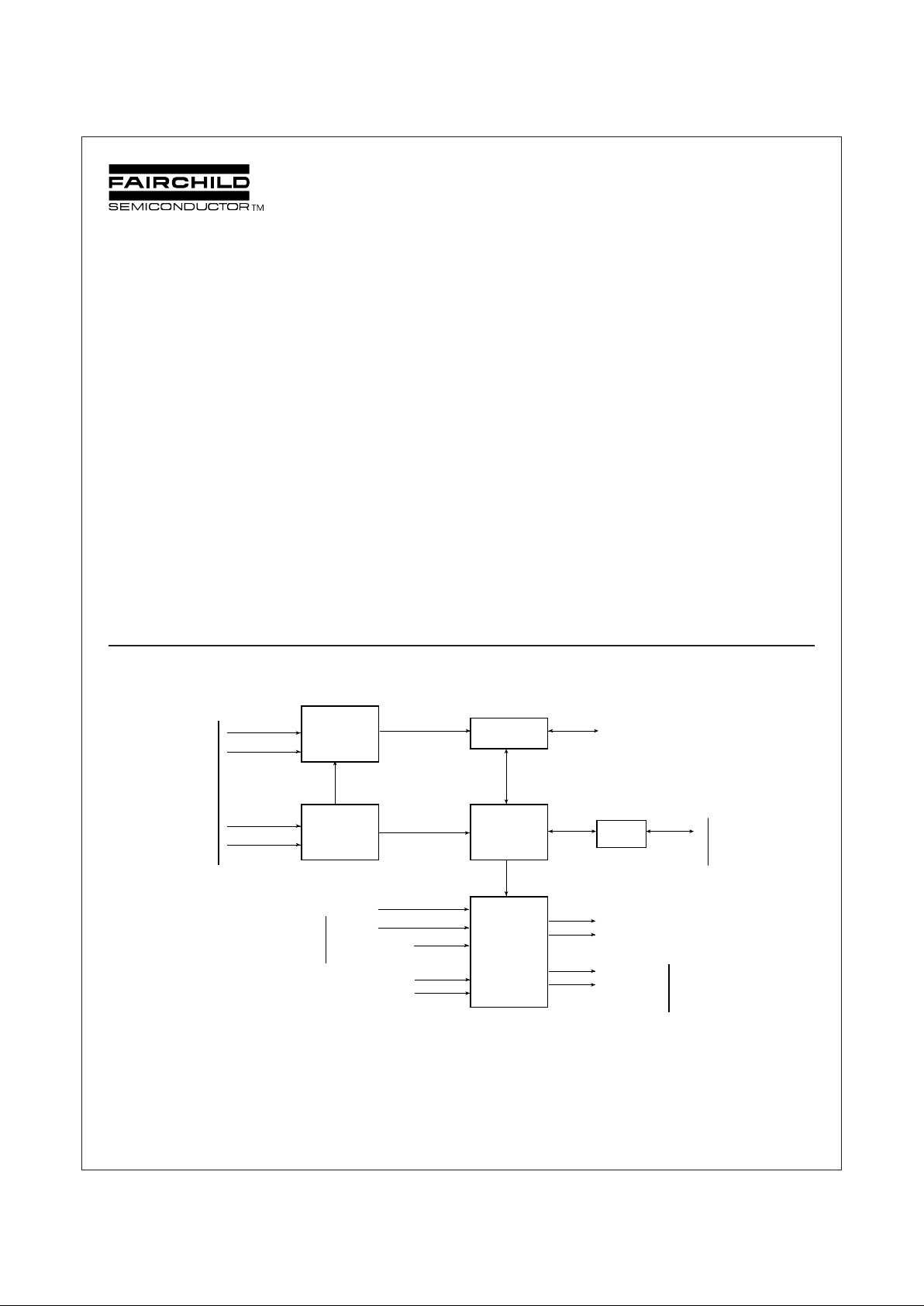

Block Diagram

Features

■ Complete Implementation of Plug and Play Standard

—Direct interface to ISA bus

■ Two modes of operation

—DMA mode

—Extended Interrupt mode (Windows® 95 logo

compatible)

■ 6 or 8 ISA bus interrupt lines and 2 DRQ/DACK lines

supported

■ On-chip EEPROM for resource request table

■ Additional 4 kbits of on-chip EEPROM available for external

access

■ 24 mA Drivers for Data outputs

■ Complete compliance to ISA PnP specification (Ver. 1.0A)

■ 48-Pin TQFP, and 52-Pin PLCC Packages

DS012601-1

Windows® 95 is a registered trademark of Microsoft Corporation.

Osc.

From

ISA

Bus

From

ISA

Bus

To

ISA

Bus

ISA

Bus

Rstdrv

Address

Control

Address

DACKx*

LIRQx

LDRQx

Control

IOCS<0:2>*

Function

Module

Support

Logic

State

Machine

Decoder

& Control

Register

Block

Data

Buffer

SD<0:7>

MICROWIRE Port

EEPROM

LDACKx*

IRQx

DRQx

2

www.fairchildsemi.com

NM95MS16 Plug and Play Front-End Devices for ISA-BUS Systems

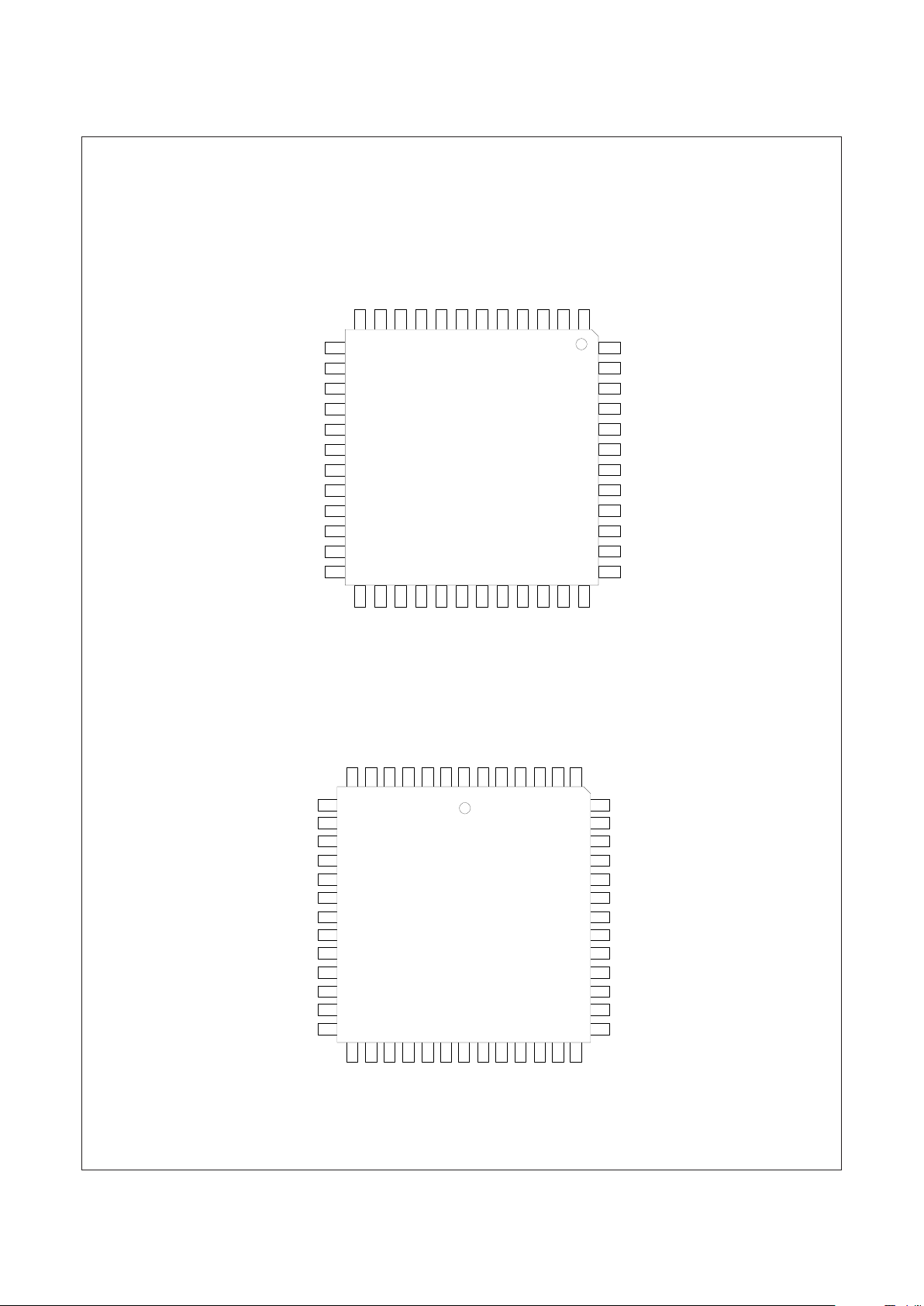

Connection Diagrams

Commercial Temperature Range (0°C to +70°C)

Order Number NM95MS16VBH

Order Number NM95MS16V

SA0

IRQOUT4

IRQOUT3

IRQOUT2

IRQOUT1

IRQOUT0

ISADRQ0/IRQOUT6

ISADRQ1/IRQOUT7

ISADACK0*/SA12

ISADACK1*/SA13

CS

SK

DI

SD7

SD6

SD5

SD4

SD2

SD1

SD0

OSC

AEN

DO

SD3

RSTDRV

IRQOUT5

IRQIN0

IRQIN1/SA14

GND

DRQIN/SA15

V

CC

IOWR*

IORD*

IOCS0*

IOCS1*

DACKOUT*/IOCS2*

SA11

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

GND

12 1234567891011

24

13

14

15

16

17

18

19

20

21

22

23

37

48

47

46

45

44

43

42

41

40

39

38

25 3635343332313029282726

NM95MS16

(TQFP)

1

23

45

6

7

12

9

10

11

13

14

15

16

17

18

19

20

36

48

46

45

44

43

42

41

40

39

38

37

24

22

23

25

33

32

313029

28

27

26

SA0

IRQOUT3

IRQOUT2

IRQOUT1

IRQOUT0

ISADRQ0/IRQOUT6

ISADRQ1/IRQOUT7

ISADACK0*/SA12

ISADACK1*/SA13

CS

SK

SD7

SD6

SD5

SD4

SD2

SD1

SD0

OSC

AEN

DO

SD3

IRQOUT5

IRQIN0

IRQIN1/SA14

GND

DRQIN/ISA15

VCC

IOWR*

IORD*

IOCS0*

IOCS1*

DACKOUT*/IOCS2*

SA11

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

GND

51

52 50 49

35

34

NC

NC

NC

47

21

8

NC

DI

IRQOUT4

RSTDRV

SA1

NM95MS16

(PLCC)

DS012601-2

DS012601-3

3

www.fairchildsemi.com

NM95MS16 Plug and Play Front-End Devices for ISA-BUS Systems

Connection Diagrams (Continued)

Signals Type Description

SA<11:0> I Address inputs from the ISA bus.

IORD* I I/O read strobe from the ISA bus.

IOWR* I I/O write strobe from the ISA bus.

AEN I Address Enable from ISA Bus —used in conjunction with DMA.

SD<7:0> I/O Data bus —lower byte —from/to the ISA bus.

OSC (Note 1) I “OSC” clock from the ISA bus —used for internal state machines.

RSTDRV I Reset input from the ISA bus.

CS I Chip select for Microwire port. There should be a pull down

resistor of 4.7k on CS pin if unused externally, or directly

connected to GND.

SK, DI I Clock and Data input lines for Microwire bus connection to access

a portion (4k) on chip EEPROM.

DO O Data output line for the Microwire interface detailed above.

IRQOUT<5:0> O Connection to ISA bus interrupt request pins. On-chip interrupt

request(s) may be connected to any 6 of the ISA IRQ lines.

IRQIN<1:0> I Interrupt request from on-board logic

DRQin/SA<15> I DMA request from on-board logic, or Address input from ISA bus

depending on mode selected.

DACKOUT* /IOCS2* O DMA Acknowledge for on-board logic or Programmable chipselect

(2) depending on mode selected.

ISADRQ<1:0>/IRQOUT<7:6> O Connection for two ISA bus DMA Request lines, or additional

interrupt request lines depending on the mode selected.

ISADACK<1:0>*/SA<13:12> I DMA Acknowledge from the ISA bus or additional address lines

depending on the mode selected.

IOCS<1:0>* O Programmable chip selects to address on-board peripheral.

IRQIN<1>/SA<14> I Interrupt request from on board logic or Address input from ISA bus

depending on mode selected.

*Signal name with a “*” means its an active low signal.

Note 1: “OSC” clock from ISA Bus is fixed at a standard frequency of 14.318 MHz. NM95MS16 is designed and tested for 14.318 MHz. However NM95MS16 can handle

frequencies up to 24 MHz though it is not 100% tested.

Loading...

Loading...