Fairchild Semiconductor NM34C02LEMT8, NM34C02EM8X, NM34W02LM8, NM34C02ULMT8, NM34C02MT8X Datasheet

...

1

www.fairchildsemi.com

NM34C02 Rev. D.2

NM34C02 2K-Bit Standard 2-Wire Bus Interface

© 1999 Fairchild Semiconductor Corporation

March 1999

NM34C02

2K-Bit Standard 2-Wire Bus Interface

Designed with Permanent Write-Protection for First 128 Bytes for Serial Presence

Detect Application on Memory Modules

General Description

The NM34C02 is 2048 bits of CMOS non-volatile electrically

erasable memory. It is designed to support Serial Presence

Detect circuitry in memory modules. This communications protocol uses CLOCK (SCL) and DATA I/O (SDA) lines to synchronously clock data between the master (for example a microprocessor) and the slave EEPROM device(s).

The contents of the non-volatile memory allows the CPU to

determine the capacity of the module and the electrical characteristics of the memory devices it contains. This will enable "plug and

play" capability as the module is read and PC main memory

resources utilized through the memory controller.

The first 128 bytes of the memory of the NM34C02 can be

permanently Write Protected by writing to the "WRITE PROTECT"

Register. Write Protect implementation details are described

under the section titled Addressing the WP Register.

The NM34C02 is available in a JEDEC standard TSSOP package

for low profile memory modules for systems requiring efficient

space utilization such as in a notebook computer. Two options are

available: L - Low Voltage and LZ - Low Power, allowing the part

to be used in systems where battery life is of primary importance.

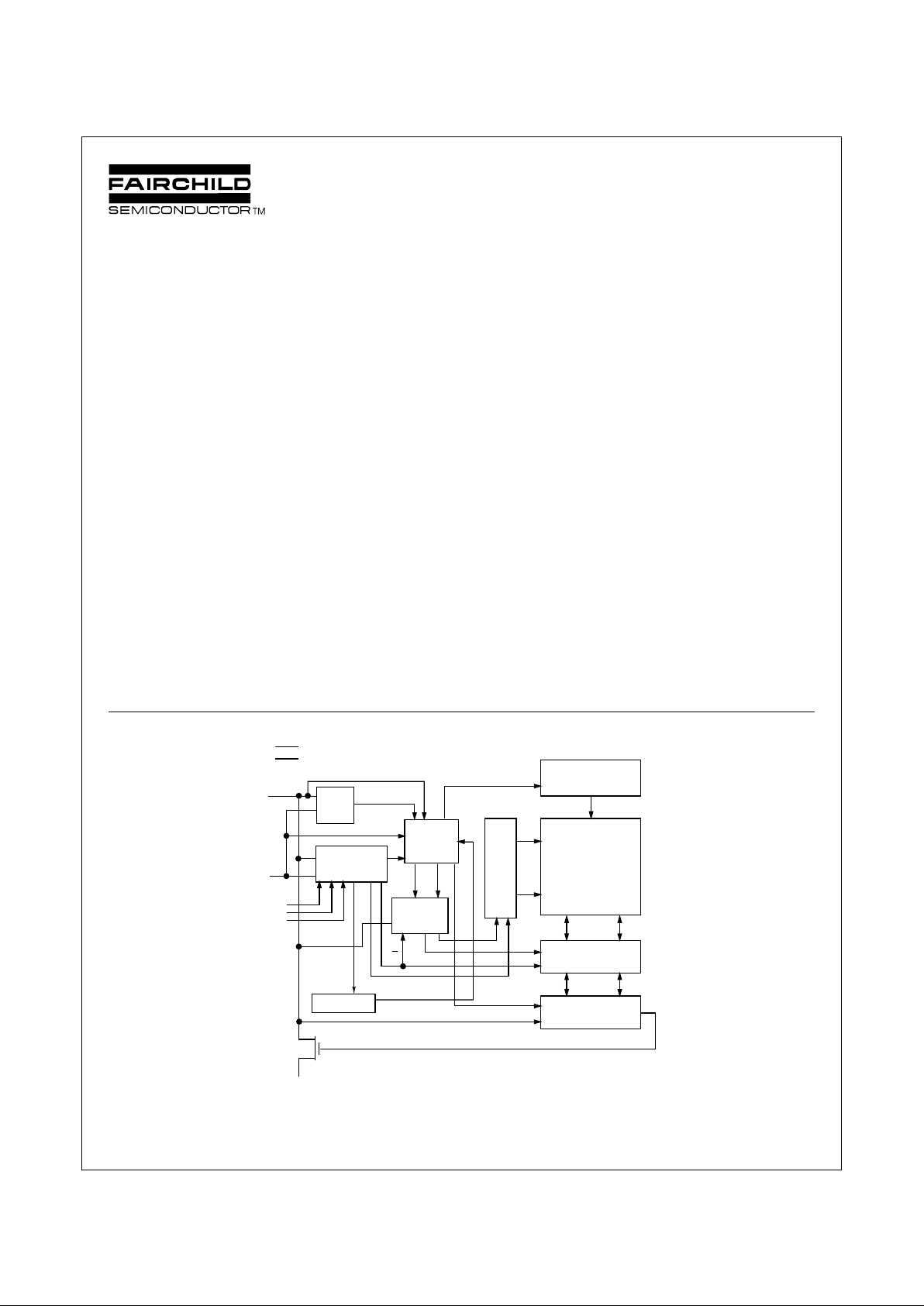

Block Diagram

Features

■ Extended Operating Voltage: 2.7V-5.5V

■ Write-Protection for first 128 bytes

■ 200 µA active current typical

– 10 µA standby current typical

– 1.0 µA standby current typical (L)

– 0.1 µA standby current typical (LZ)

■ IIC compatible interface

– Provides bidirectional data transfer protocol

■ Sixteen byte page write mode

– Minimizes total write time per byte

■ Self timed write cycle

- Typical write cycle time of 6ms

■ Endurance: 1,000,000 data changes

■ Data retention greater than 40 years

■ Packages available: 8-pin TSSOP and 8-pin SO

DS012821-1

H.V. GENERATION

TIMING &CONTROL

E2PROM

ARRAY

16 x 16 x 8

16

YDEC

8

DATA REGISTER

XDEC

CONTROL

LOGIC

WORD

ADDRESS

COUNTER

SLAVE ADDRESS

REGISTER &

COMPARATOR

START

STOP

LOGIC

START CYCLE

16

4

4

CK

D

IN

R/W

LOAD INC

SDA

V

SS

V

CC

D

OUT

A2

A1

A0

Device Address Bits

0/1/2/3

SCL

Write Protect

Register

2

www.fairchildsemi.com

NM34C02 Rev. D.2

NM34C02 2K-Bit Standard 2-Wire Bus Interface

A0

A1

A2

V

SS

V

CC

NC

SCL

SDA

8

7

6

5

1

2

3

4

NM34C02

DS012821-2

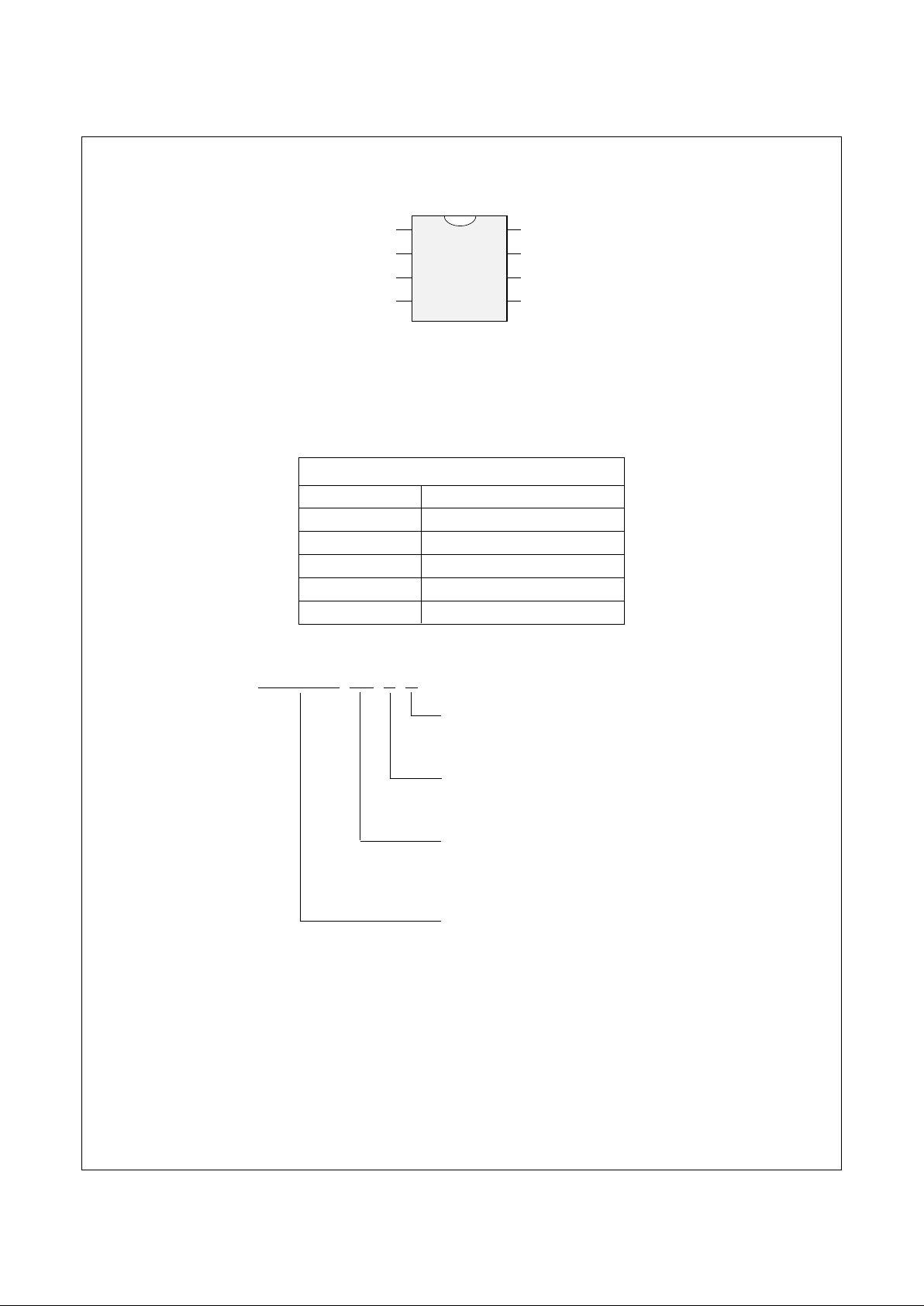

Connection Diagram

SO (M8) and TSSOP (MT8) Package

Top View

See Package Number

M08A and MTC08

Pin Names

A0,A1,A2 Device Address Inputs

V

SS

Ground

SDA Data I/O

SCL Clock Input

NC No Connection

V

CC

Power Supply

Ordering Information

NM34C02 XX X X

Package

M8 = 8 pin SOIC

MT8 = 8 pin TSSOP

Temperature Range

Blank = 0°C to +70°C

E = -40°C to +85°C

Voltage Range

Blank = 4.5V to 5.5V

L = 2.7V to 4.5V

LZ = 2.7V to 4.5V and < 1µA standby current

Device

2K IIC Serial EEPROM

DS012821-21

3

www.fairchildsemi.com

NM34C02 Rev. D.2

NM34C02 2K-Bit Standard 2-Wire Bus Interface

Product Specifications

Absolute Maximum Ratings

Ambient Storage Temperature –65°C to +150°C

All Input or Output Voltages

with Respect to Ground 6.5V to –0.3V

Lead Temperature

(Soldering, 10 seconds) +300°C

ESD Rating 2000V min.

Operating Conditions

Ambient Operating Temperature

NM34C02 0°C to +70°C

NM34C02E -40°C to +85°C

Positive Power Supply

NM34C02 4.5V to 5.5V

NM34C02L 2.7V to 4.5V

NM34C02LZ 2.7V to 4.5V

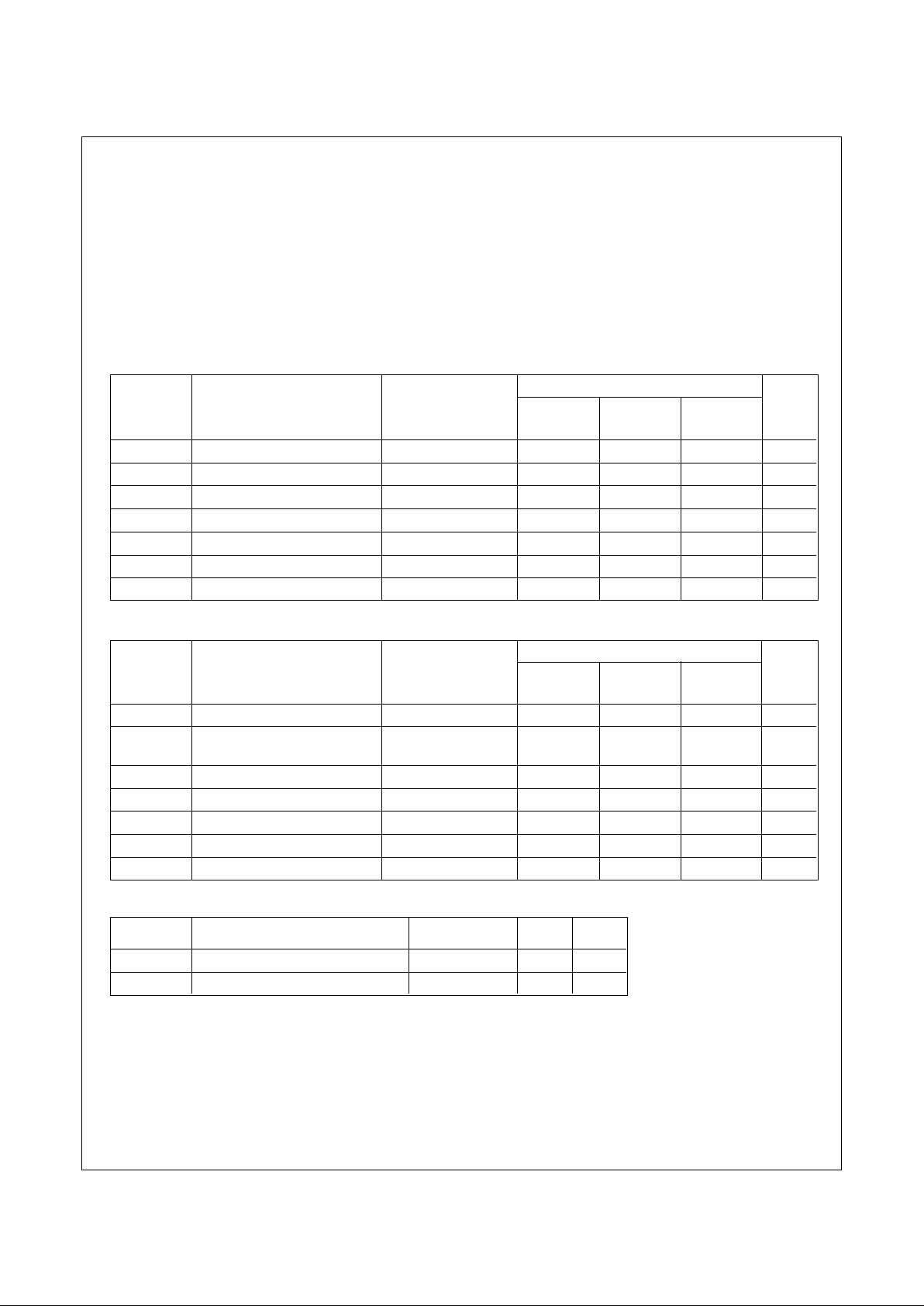

Standard VCC (4.5V to 5.5V) DC Electrical Characteristics

Symbol Parameter Test Conditions Limits Units

Min Typ Max

(Note 1)

I

CCA

Active Power Supply Current f

SCL

= 100 kHz 0.2 1.0 mA

I

SB

Standby Current VIN = GND or V

CC

10 50 µA

I

LI

Input Leakage Current VIN = GND to V

CC

0.1 1 µA

I

LO

Output Leakage Current V

OUT

= GND to V

CC

0.1 1 µA

V

IL

Input Low Voltage –0.3 VCC x 0.3 V

V

IH

Input High Voltage VCC x 0.7 VCC + 0.5 V

V

OL

Output Low Voltage I

OL

= 3 mA 0.4 V

Low VCC (2.7V to 5.5V) DC Electrical Characteristics

Symbol Parameter Test Conditions Limits Units

Min Typ Max

(Note 1)

I

CCA

Active Power Supply Current f

SCL

= 100 kHz 0.2 1.0 mA

I

SB

Standby Current for L VIN = GND or V

CC

110µA

Standby Current for LZ VIN = GND or V

CC

0.1 1 µA

I

LI

Input Leakage Current VIN = GND to V

CC

0.1 1 µA

I

LO

Output Leakage Current V

OUT

= GND to V

CC

0.1 1 µA

V

IL

Input Low Voltage –0.3 V

CC

x 0.3 V

V

IH

Input High Voltage VCC x 0.7 VCC + 0.5 V

V

OL

Output Low Voltage IOL = 3 mA 0.4 V

Capacitance T

A

= +25°C, f = 100/400 KHz, VCC = 5V (Note 2)

Symbol Test Conditions Max Units

C

I/O

Input/Output Capacitance (SDA) V

I/O

= 0V 8 pF

C

IN

Input Capacitance (A0, A1, A2, SCL) VIN = 0V 6 pF

Note 1: Typical values are TA = 25°C and nominal supply voltage (5V).

Note 2: This parameter is periodically sampled and not 100% tested.

4

www.fairchildsemi.com

NM34C02 Rev. D.2

NM34C02 2K-Bit Standard 2-Wire Bus Interface

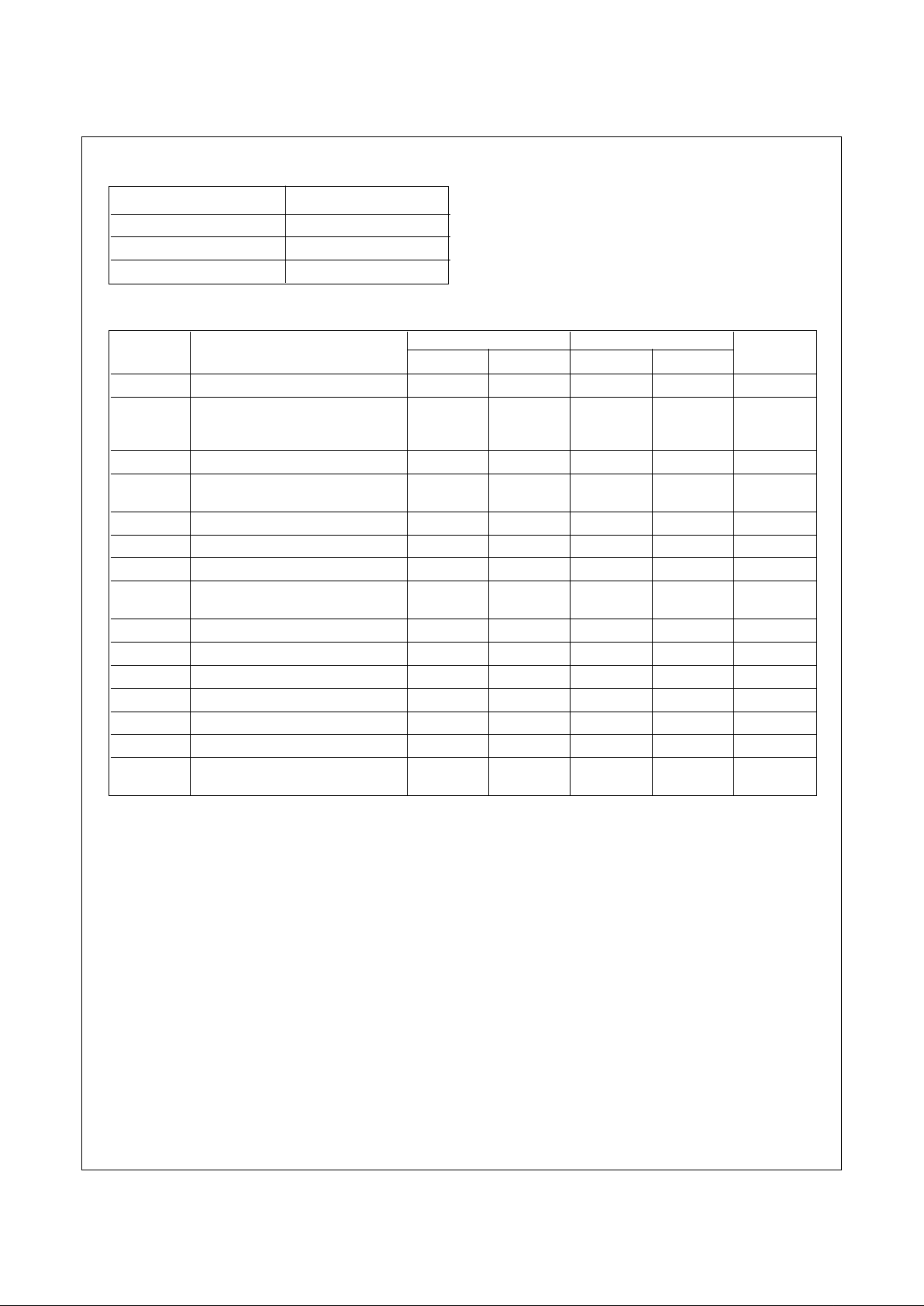

AC Conditions of Test

Input Pulse Levels VCC x 0.1 to VCC x 0.9

Input Rise and Fall Times 10 ns

Input & Output Timing Levels VCC x 0.5

Output Load 1 TTL Gate and CL = 100 pF

Read and Write Cycle Limits (Standard and Low VCC Range 2.7V - 4.5V)

Symbol Parameter 100 KHz 400 KHz Units

Min Max Min Max

f

SCL

SCL Clock Frequency 100 400 KHz

T

I

Noise Suppression Time Constant at

SCL, SDA Inputs (Minimum V

IN

100 50 ns

Pulse width)

t

AA

SCL Low to SDA Data Out Valid 0.3 3.5 0.1 0.9 µs

t

BUF

Time the Bus Must Be Free before 4.7 1.3 µs

a New Transmission Can Start

t

HD:STA

Start Condition Hold Time 4.0 0.6 µs

t

LOW

Clock Low Period 4.7 1.5 µs

t

HIGH

Clock High Period 4.0 0.6 µs

t

SU:STA

Start Condition Setup Time 4.7 0.6 µs

(for a Repeated Start Condition)

t

HD:DAT

Data in Hold Time 0 0 µs

t

SU:DAT

Data in Setup Time 250 100 ns

t

R

SDA and SCL Rise Time 1 0.3 µs

t

F

SDA and SCL Fall Time 300 300 ns

t

SU:STO

Stop Condition Setup Time 4.7 0.6 µs

t

DH

Data Out Hold Time 300 50 ns

t

WR

Write Cycle Time - NM34C02 10 10 ms

(Note 3) - NM34C02L, NM34C02LZ 15 15

Note 3: The write cycle time (tWR) is the time from a valid stop condition of a write sequence to the end of the internal erase/program cycle. During the write cycle, the

NM34C02 bus interface circuits are disabled, SDA is allowed to remain high per the bus-level pull-up resistor, and the device does not respond to its slave address.

Loading...

Loading...