Fairchild Semiconductor NDS9947 Datasheet

February 1996

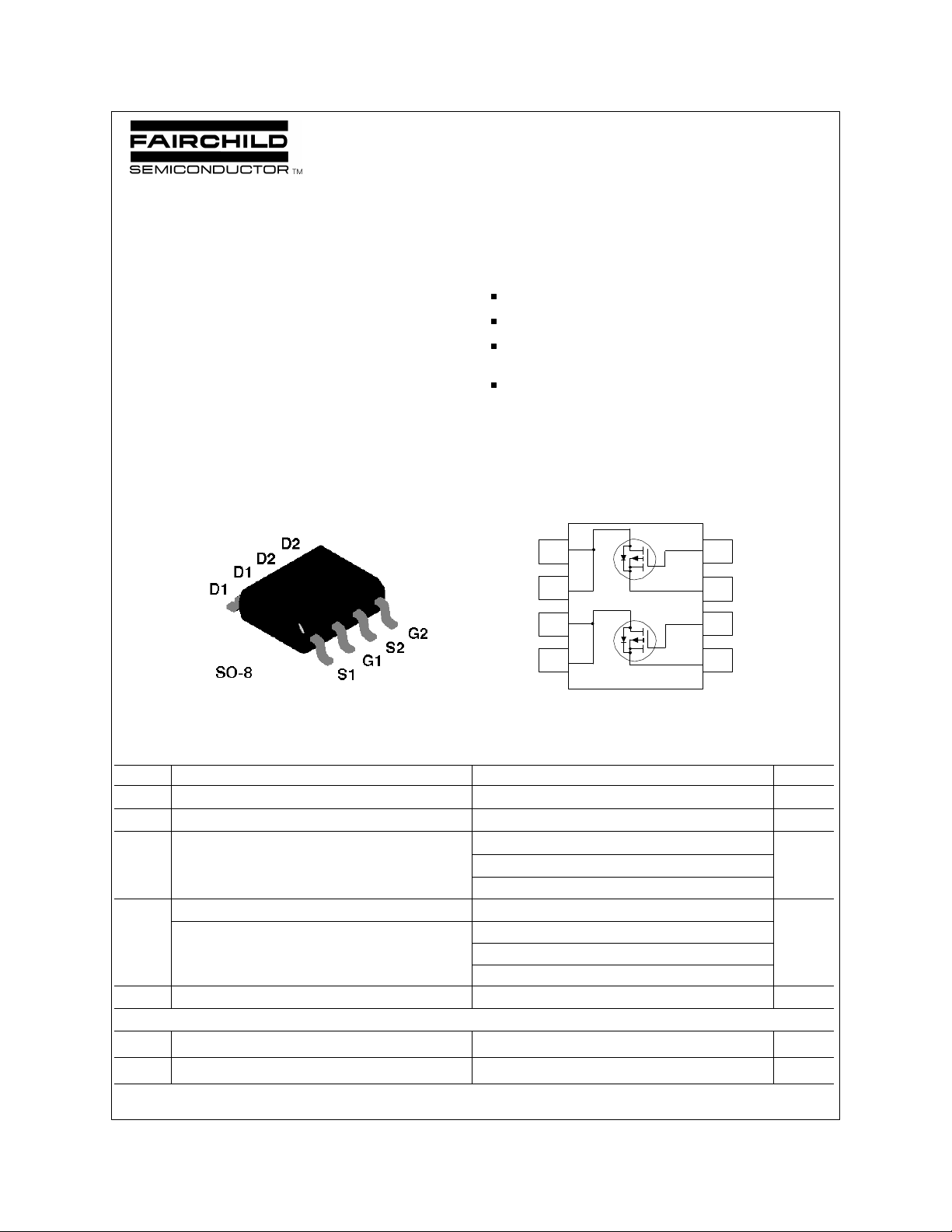

NDS9947

Dual P-Channel Enhancement Mode Field Effect Transistor

General Description Features

These P-Channel enhancement mode power field effect

transistors are produced using Fairchild's proprietary, high cell

density, DMOS technology. This very high density process is

especially tailored to minimize on-state resistance, provide

superior switching performance, and withstand high energy

pulses in the avalanche and commutation modes. These

devices are particularly suited for low voltage applications such

as notebook computer power management and other battery

powered circuits where fast switching, low in-line power loss,

and resistance to transients are needed.

________________________________________________________________________________

-3.5A, -20V. R

High density cell design for extremely low R

= 0.1Ω @ V

DS(ON)

= 10V

GS

DS(ON)

.

High power and current handling capability in a widely used

surface mount package.

Dual MOSFET in surface mount package.

4

3

2

1

Absolute Maximum Ratings T

= 25°C unless otherwise noted

A

5

6

7

8

Symbol Parameter NDS9947 Units

V

DSS

V

GSS

I

D

Drain-Source Voltage -20 V

Gate-Source Voltage ± 20 V

Drain Current - Continuous TA = 25°C (Note 1a)

- Continuous TA = 70°C (Note 1a)

± 3.5 A

± 2.5

- Pulsed TA = 25°C ± 10

P

D

Power Dissipation for Dual Operation 2 W

Power Dissipation for Single Operation (Note 1a) 1.6

(Note 1b) 1

(Note 1c) 0.9

TJ,T

Operating and Storage Temperature Range -55 to 150 °C

STG

THERMAL CHARACTERISTICS

R

θ

R

θ

Thermal Resistance, Junction-to-Ambient (Note 1a) 78 °C/W

JA

Thermal Resistance, Junction-to-Case (Note 1) 40 °C/W

JC

© 1997 Fairchild Semiconductor Corporation

NDS9947.SAM

Electrical Characteristics (T

= 25°C unless otherwise noted)

A

Symbol Parameter Conditions Min Typ Max Units

OFF CHARACTERISTICS

BV

I

DSS

I

GSSF

I

GSSR

DSS

Drain-Source Breakdown Voltage VGS = 0 V, ID = -250 µA -20 V

Zero Gate Voltage Drain Current

VDS = -16 V, V

GS

= 0 V

TJ = 55°C

-1 µA

-10 µA

Gate - Body Leakage, Forward VGS = 20 V, VDS = 0 V 100 nA

Gate - Body Leakage, Reverse

VGS = -20 V, VDS= 0 V

-100 nA

ON CHARACTERISTICS (Note 2)

V

GS(th)

Gate Threshold Voltage VDS = VGS, ID = -250 µA -1 -2.2 -3 V

TJ = 125°C -0.8 -1.9 -2.5

R

DS(ON)

Static Drain-Source On-Resistance

VGS = -10 V, ID = -3.5 A

TJ = 125°C

0.08 0.1

0.11 0.16

Ω

VGS = -4.5 V, ID = -1 A 0.165 0.19

I

g

D(on)

On-State Drain Current

FS

Forward Transconductance VDS = -15 V, ID = -3.5 A 5 S

VGS = -10 V, VDS = -5 V

-14 A

DYNAMIC CHARACTERISTICS

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance 500 pF

VDS = -10 V, VGS = 0 V,

f = 1.0 MHz

Reverse Transfer Capacitance 245 pF

785 pF

SWITCHING CHARACTERISTICS (Note 2)

t

t

t

t

Q

Q

Q

D(on)

r

D(off)

f

g

gs

gd

Turn - On Delay Time VDD = -10 V, ID = -1 A,

V

= -10 V, R

Turn - On Rise Time 17 25 ns

GEN

GEN

= 6 Ω

9 40 ns

Turn - Off Delay Time 26 30 ns

Turn - Off Fall Time 13 20 ns

Total Gate Charge VDS = -10 V,

Gate-Source Charge 6 nC

ID = -3.5 A, VGS = -10 V

19 30 nC

Gate-Drain Charge 12 nC

NDS9947.SAM

Electrical Characteristics (T

= 25°C unless otherwise noted)

A

Symbol Parameter Conditions Min Typ Max Units

DRAIN-SOURCE DIODE CHARACTERISTICS AND MAXIMUM RATINGS

I

S

V

SD

Notes:

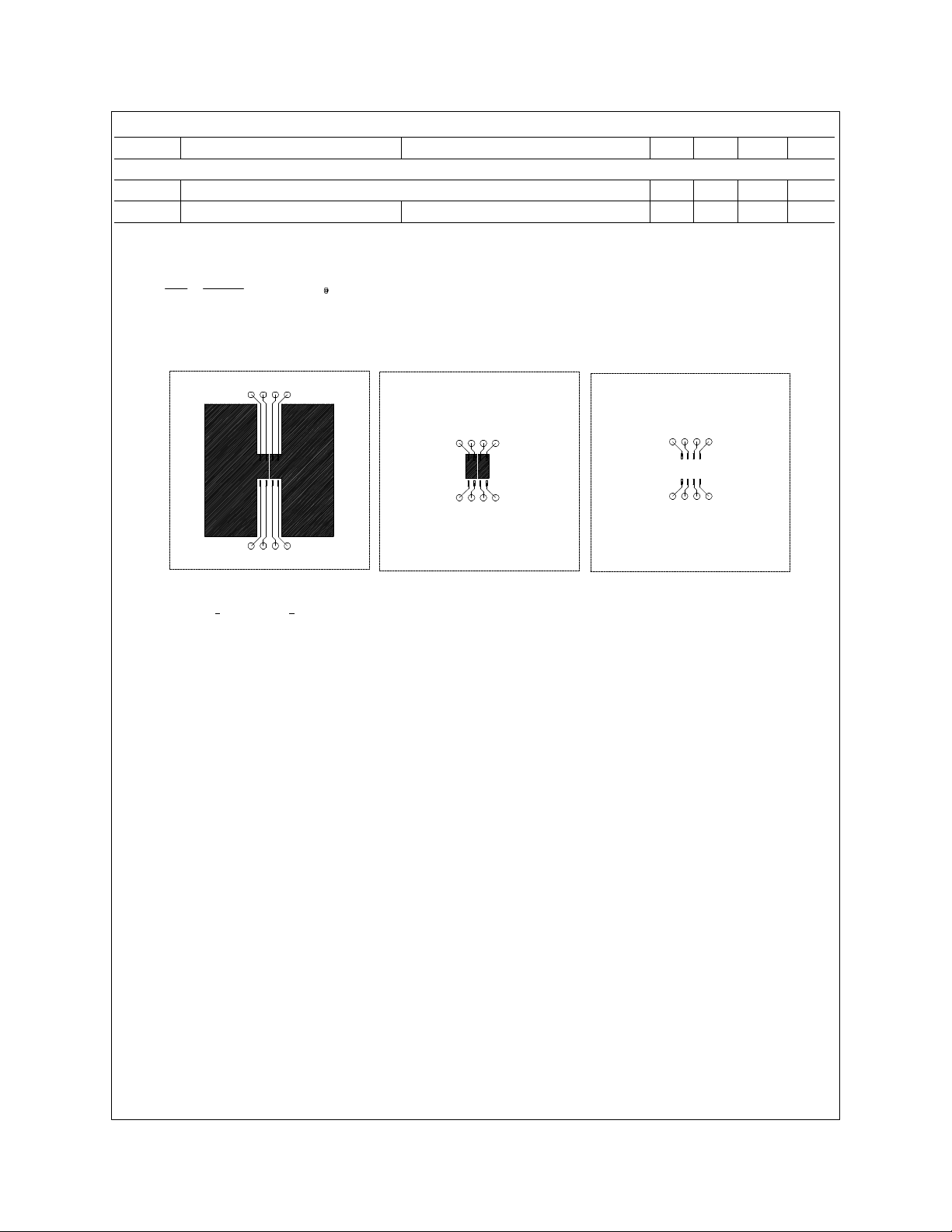

1. R

design while R

P

D

Typical R

Scale 1 : 1 on letter size paper

Maximum Continuous Drain-Source Diode Forward Current -1.7 A

Drain-Source Diode Forward Voltage

is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins. R

JA

θ

(t)

is determined by the user's board design.

CA

θ

T

=

R

θ

a. 78oC/W when mounted on a 0.5 in2 pad of 2oz cpper.

b. 125oC/W when mounted on a 0.02 in2 pad of 2oz cpper.

c. 135oC/W when mounted on a 0.003 in2 pad of 2oz cpper.

T

J−TA

=

(t)

R

θJ A

θ

J C

for single device operation using the board layouts shown below on 4.5"x5" FR-4 PCB in a still air environment:

JA

J−TA

+R

2

= I

(t) × R

DS(O N ) T

D

(t)

θ

CA

J

1a

VGS = 0 V, IS = -1.7 A

1b

(Note 2)

1c

-0.9 -1.2 V

is guaranteed by

JC

θ

2. Pulse Test: Pulse Width < 300µs, Duty Cycle < 2.0%..

NDS9947.SAM

Loading...

Loading...