January 2001

Revised August 2001

FSTUD16450

Configurable 4-Bit to 20-Bit Bus Switch with

-2V Undershoot Protection and Selectable Level Shifting

FSTUD16450 Configurable 4-Bit to 20-Bit Bus Switch with -2V Undershoot Protection and Selectable Level

Shifting

General Description

The Fairchild Universal Bus Switch FSTUD16450 provides

4-bit, 5-bit, 8-bi t, 10-b it, 16- bit, 20 -bit of hig h-s peed CMOS

TTL-compatible bus switch ing. The low On Resistance of

the switch allows inputs to be conn ecte d to ou tpu ts witho ut

adding propagation de lay or generating additi onal ground

bounce noise.

The FSTUD16450 is designed to allow “customer” configuration control of the enable connections. The device is

organized as either a 4-bit, 5-bit, 10-bit or 20-bit bus switch.

8-bit and 16-bit configurations are also achievable (see

Functional Description). The device's bit configuration is

chosen through select pi n logic. (see Truth Table). When

OE

is LOW, Port Ax is connected to Port Bx. When OEx is

x

HIGH, the switch is OPEN.

The A and B Ports are “und ershoo t hardened ” with UHC

protection to support an extended range to 2.0V below

ground. Fairchild's integrated “Undershoot Hardened

Circuit” (UHC) senses undershoot at the I/O's, and

responds by preventing vo ltage differentia ls from develo ping and turning on the switch.

Another key device feature is the addition of a level shifting

select pin, “S

standard N-MOS switch. When S

is integrated into the circuit allowing for level shifting

between 5V inputs and 3.3V outputs.

”. When S2 is LOW, the device behaves as a

2

is HIGH, a diode to V

2

Features

■ Undershoot hardened to −2V (A and B Ports)

■ Voltage level shifting

■ 4

Ω switch connection between two ports

■ Minimal propagation delay through the switch

■ Low l

CC

■ Zero bounce in flow-through mode

■ Control inputs compatible with TTL level

■ See Applications Note AN-5008 for details

■ Also packaged in plastic Fine-Pitch Ball Grid Array

(FBGA) (Preliminary)

Applications Note

Select pins S0, S1, S2 are intended to be used as static

user configurable control pins. The AC performance of

these pins has not be en characterized or teste d. Swit ching

of these select pin s during system operation may temporarily disrupt output logic states and/or enable pin controls.

CC

Ordering Code:

Order Number Package Number Package Description

FSTUD16450GX

(Note 1)

FSTUD16450 MT D MTD56 56-Lead Thin S hr in k Sm all Ou t li n e P ack a ge ( TS S OP ), JEDEC MO-153 , 6. 1mm W id e

Devices also availab l e in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

Note 1: BGA package available in Tape and Reel only.

BGA54A

(Preliminary)

54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

[Tape and Reel]

UHC is a trademark of Fairchild Semiconductor Corporation.

© 2001 Fairchild Semiconductor Corporation DS500391 www.fairchildsemi.com

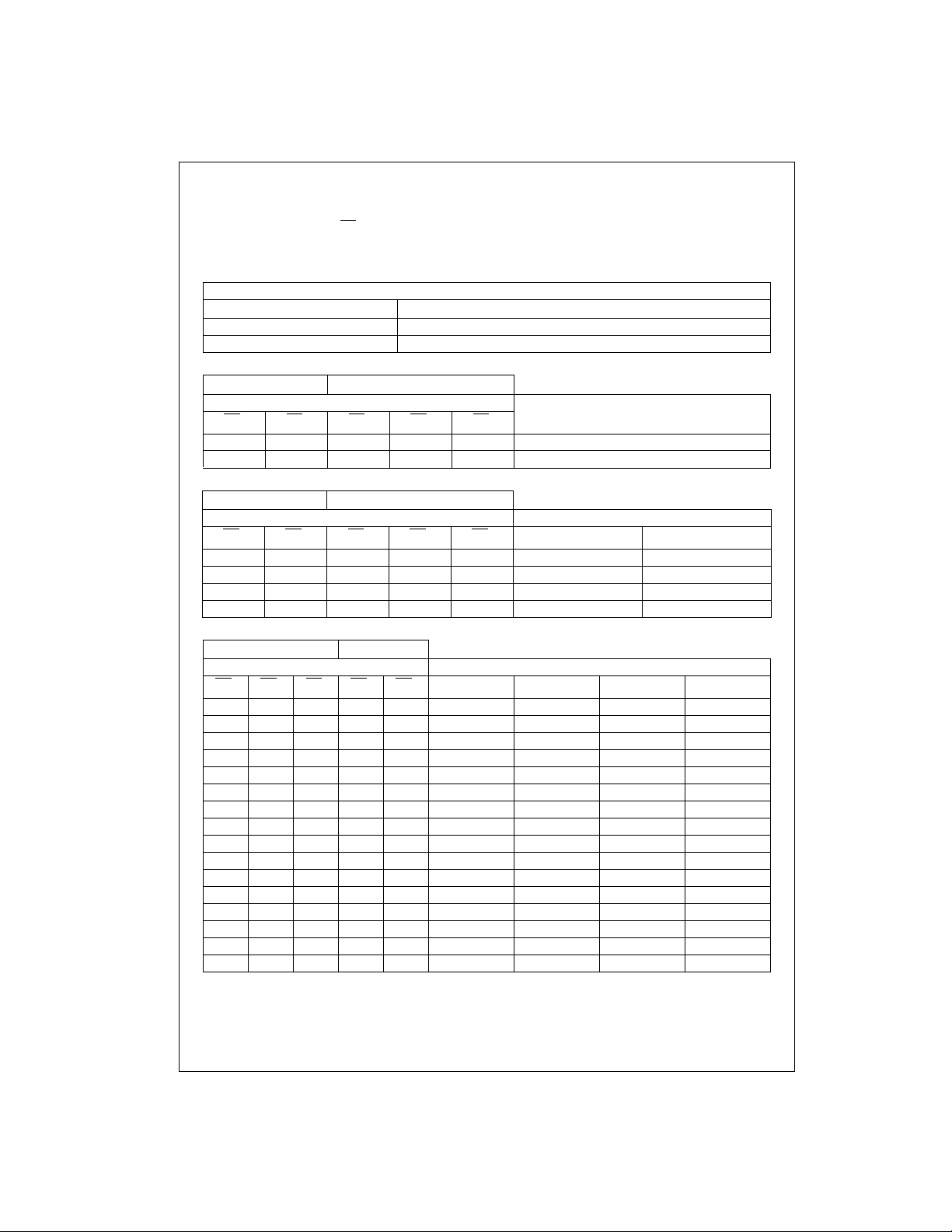

Connection Diagrams

Pin Assignment for TSSOP

FSTUD16450

Pin Descriptions

Pin Name Description

OE

, OE

1

2

Bus Switch Enables

1A, 2A Bus A

1B, 2B Bus B

S

, S

0

1

S

2

Bit Configuration Enables

Level Shifting Diode Enable

NC No Connect

FBGA Pin Assignments

123456

A 1A

B 1A51A41A11B11B41B

C 1A71A6GND OE51B61B

D 1A91A8GND V

E 2A11A

F 2A32A2S

G 2A52A4VCCGND 2B42B

H 2A72A62A102B102B62B

J 2A92A8OE4OE32B82B

1A2OE1OE21B21B

3

CC

10S0VCC1B10

S22B22B

1

1B81B

2B

3

5

7

9

1

3

5

7

9

Pin Assignment for FBGA

(Top Thru View)

www.fairchildsemi.com 2

Logic Diagrams

20-Bit Configuration

(Configuration 1)

FSTUD16450

10-Bit Configuration

(Configuration 2)

5-Bit Configuration

(Configuration 3)

4-Bit Configuration

(Configuration 4)

3 www.fairchildsemi.com

Functional Description

The device can a lso be configured as an 8 and 16-bit devi ce by grounding the u nused pins in Configu rations 2 and 1

respectively. The 8-bit configuration may also be achieved by tying two of the 4-bit enables from configuration together and

tying the remaining enabl e pin (OE

) HIGH.

Truth Tables (X = V

FSTUD16450

(see Functional Description)

Configuration 1

OE

1

LXXXX 1A

HXXXX Z

Configuration 2

OE

1

LXXLX 1A

LXXHX 1A

HXXLX Z 2A

HXXHX Z Z

Configuration 3

OE

OE2OE3OE4OE51A

1

LLLLX1A

LLLHX1A

LLHLX1A

LLHHX1A

LHLLX1A

LHLHX1A

LHHLX1A

LHHHX1A

HLLLX Z 1A

HLLHX Z 1A

HLHLX Z 1A

HLHHX Z 1A

HHL LX Z Z 2A

HHLHX Z Z 2A

HHHLX Z Z Z 2A

HHHHX Z Z Z Z

or GND)

CC

Select Pin

S

2

Mode

L Std. NMOS Switch

H Level Shifting Diode Enabled

= S1 = L

OE

S

0

Inputs

2

OE

3

OE

S

= L, S1 = H

0

OE

4

5

20-Bit Configuration

Inputs/Outputs

= 1B

1-10

10-Bit Configuration

Inputs Inputs/Outputs

OE

2

OE

3

S

= H, S1 = L

0

OE

4

OE

5

1A

1-10

= 1B

= 1B

X

= 1B

X

1-10

X

X

5-Bit Configuration

Inputs Inputs/Outputs

1-5

, 1B

= 1B

x

= 1B

x

= 1B

x

= 1B

x

= 1B

x

= 1B

x

= 1B

x

= 1B

x

1-5

1A

, 1B

6-10

1Ay = 1B

x

1Ay = 1B

x

1Ay = 1B

x

1Ay = 1B

x

x

x

x

x

Z2A

Z2A

ZZ2A

ZZZ

= 1B

y

= 1B

y

= 1B

y

= 1B

y

6-10

y

y

y

y

y

y

y

y

2A

, 2A

1-10

= 2B

2A

1-10

2AX = 2B

1-10

= 2B

1-10

X

1-10

Z

= 2B

X

X

, 2B

1-5

2Ax = 2B

2Ax = 2B

Z2A

1-5

2A

, 2B

6-10

6-10

2Ay = 2B

x

x

Z

= 2B

y

y

y

ZZ

= 2B

x

= 2B

x

2Ax = 2B

2Ax = 2B

Z2A

2Ay = 2B

x

x

x

x

Z

= 2B

y

2Ay = 2B

Z

= 2B

y

y

y

y

y

ZZ

= 2B

x

= 2B

x

2Ay = 2B

x

x

Z

= 2B

y

y

y

www.fairchildsemi.com 4

Loading...

Loading...