Fairchild Semiconductor FJX4008R Datasheet

FJX4008R

FJX4008R

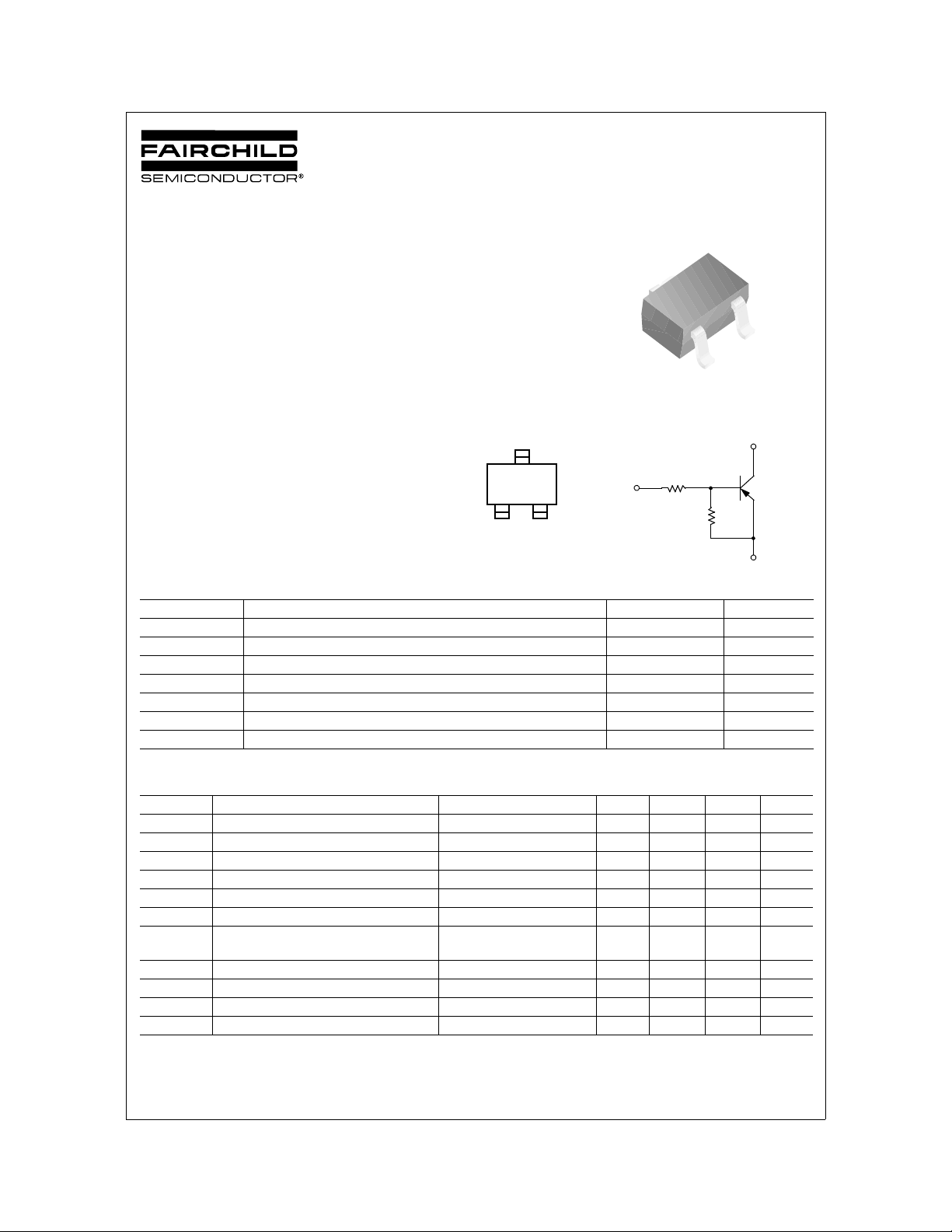

Switching Application (Bias Resistor Built In)

• Switching circuit, Inverter, Interface circuit, Driver Circuit

• Built in bias Resistor (R

• Complement to FJX3008R

=47KΩ, R2=22KΩ)

1

3

1. Base 2. Emitter 3. Collector

Marking

Equivalent Circuit

R1

S58

B

R2

PNP Epitaxial Silicon Transistor

Absolute Maximum Ratings

Symbol Parameter Value Units

V

V

V

I

P

T

T

CBO

CEO

EBO

C

C

J

STG

Collector-Base Voltage -50 V

Collector-Emitter Voltage -50 V

Emitter-Base Voltage -10 V

Collector Current -100 mA

Collector Power Dissipation 200 mW

Junction Temperature 150 °C

Storage Temperature -55 ~ 150 °C

Ta=25°C unless otherwise noted

1

SOT-323

2

C

E

Electrical Characteristics

Ta=25°C unless otherwise noted

Symbol Parameter Tes t Condition Min. Typ. Max. Units

BV

CBO

BV

CEO

I

CBO

h

FE

(sat) Collector-Emitter Saturation Voltage IC= -10mA, IB= -0.5mA -0.3 V

V

CE

f

T

C

ob

Collector-Base Breakdown Voltage IC= -10µA, IE=0 -50 V

Collector-Emitter Breakdown Voltage IC= -100µA, IB=0 -50 V

Collector Cut-off Current VCB= -40V , IE=0 -0.1 µA

DC Current Gain VCE= -5V, IC= -5mA 56

Current Gain Bandwidth Product VCE= -10V , IC= -5mA 200 MHz

Output Capacitance VCB= -10V , IE=0

5.5 pF

f=1.0MHz

V

(off) Input Off Voltage VCE= -5V, IC= -100µA-0.8 V

I

(on) Input On Voltage VCE= -0.3V, IC= -2mA -4 V

V

I

R

1

R

1/R2

©2002 Fairchild Semiconductor Corporation Rev. A3, August 2002

Input Resistor 32 47 62 KΩ

Resistor Ratio 1.9 2.1 2.4

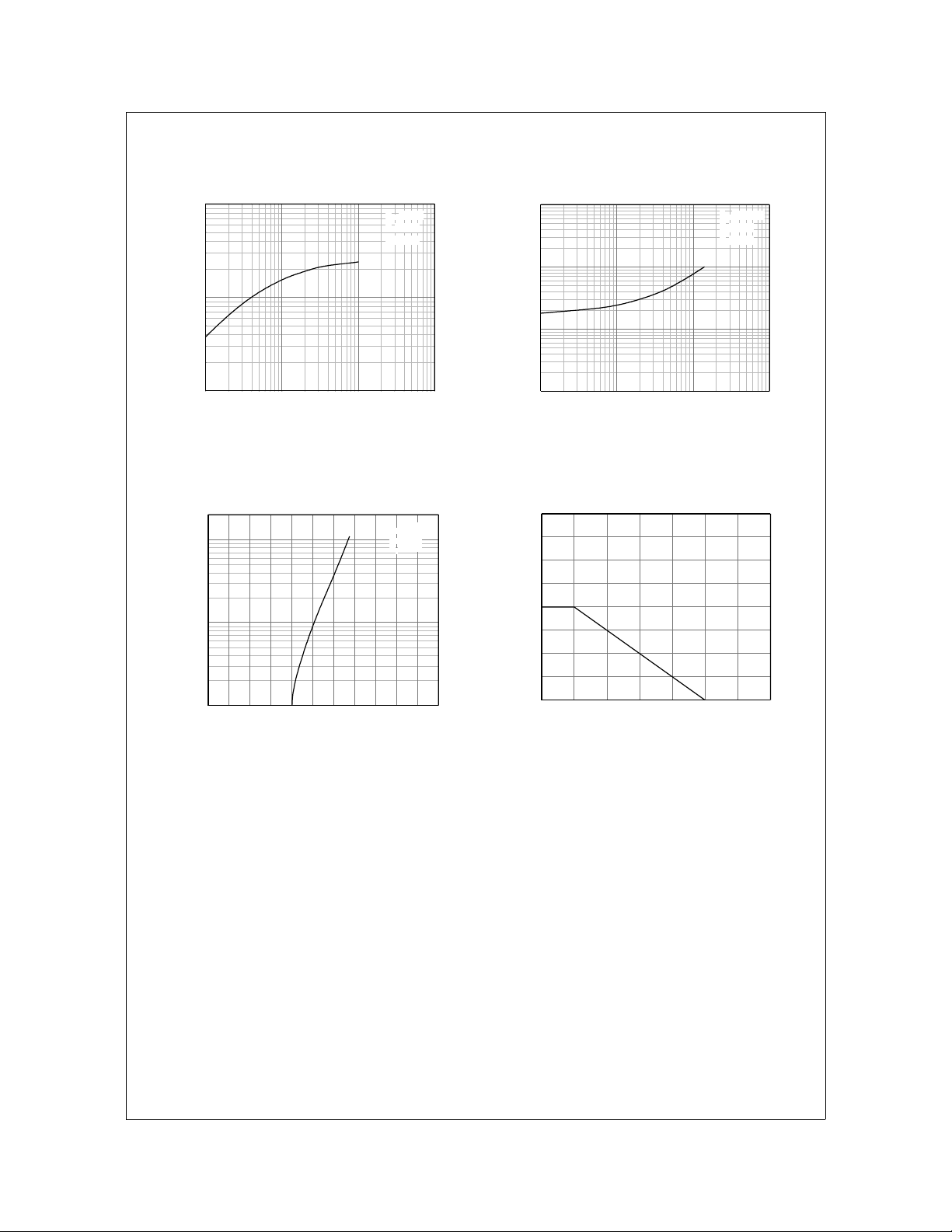

Typical Characteristics

FJX4008R

1000

100

, DC CURRENT GAIN

FE

h

10

-1 -10 -100 -1000

IC[mA], COLLECTOR CURRENT

Figure 1. DC current Gain Figure 2. Input On Voltage

-1000

-100

A], COLLECTOR CURRENT

µ

[

C

I

-10

-0.6 -0.8 -1.0 -1.2 -1.4 -1.6 -1.8 -2.0 -2.2 -2.4 -2.6 -2.8

VI(off)[V], INPUT OFF VOLTAGE

VCE = - 5V

R1 = 47K

R2 = 22K

VCE = - 5V

R1 = 47K

R2 = 22K

-100

-10

-1

(on)[V], INPUT VOLTAGE

I

V

-0.1

-0.1 -1 -10 -100

VCE = - 0.3V

R1 = 47K

R2 = 22K

IC[mA], COLLECTOR CURRENT

400

350

300

250

200

150

100

[mW], POWER DISSIPATION

C

50

P

0

0 255075100125150175

Ta[oC], AMBIENT TEMPERATURE

Figure 3. Input Off Voltage Figure 4. Power Derating

©2002 Fairchild Semiconductor Corporation

Rev. A3, August 2002

Loading...

Loading...