FDS4559

60V Complementary PowerTrench

MOSFET

FDS4559

April 2002

General Description

This complementary MOSFET device is produced using

Fairchild’s advanced PowerTrench process that has

been especially tailored to minimize the on-state

resistance and yet maintain low gate charge for

superior switching performance.

Applications

• DC/DC converter

• Power management

• LCD backlight inverter

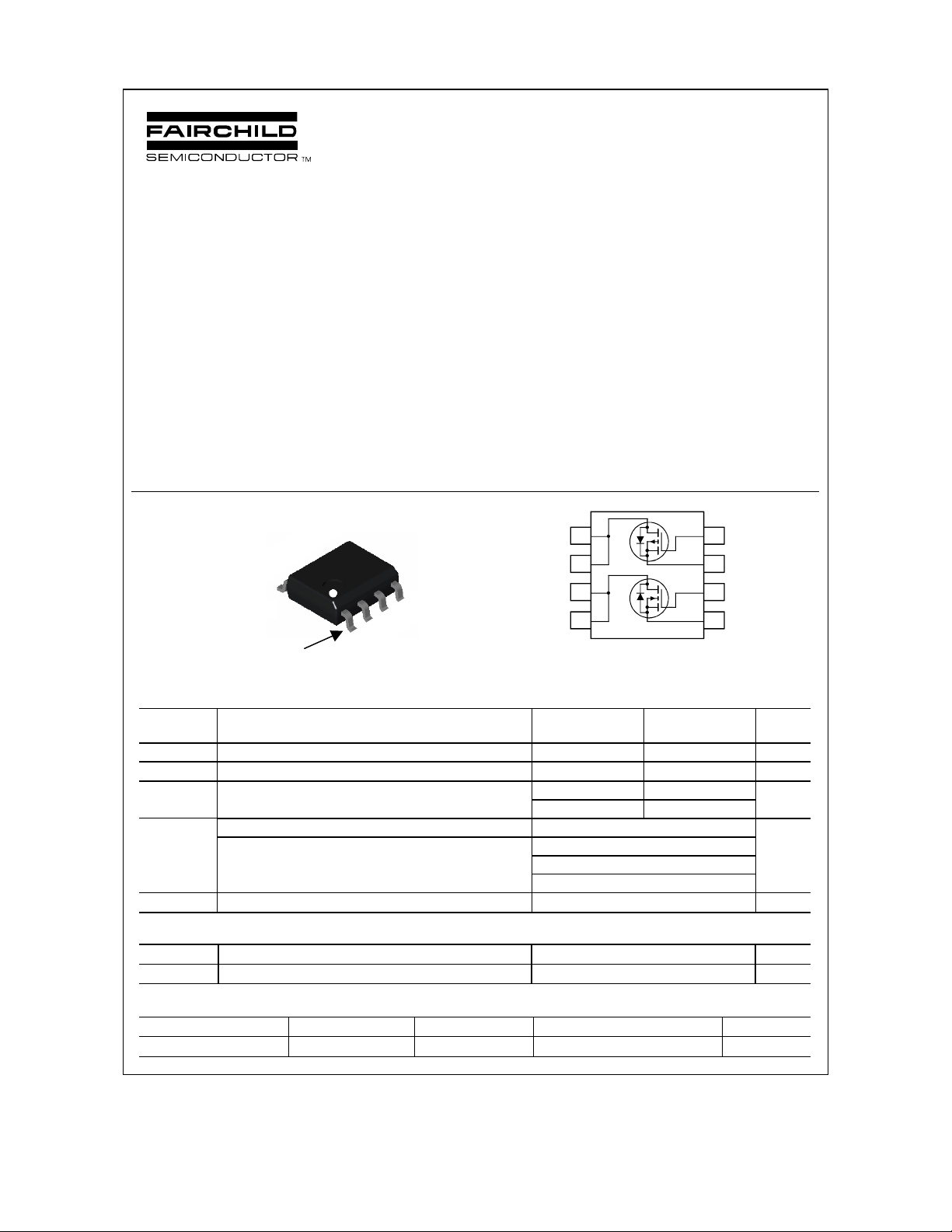

D2

D

D2

D

D1

D

D1

D

SO-8

SO-8

Pin 1

S1

Absolute Maximum Ratings T

G2

S2

G

G1

S

S

S

= 25°C unless otherwise noted

A

Features

• Q1: N-Channel

4.5 A, 60 V R

R

• Q2: P-Channel

–3.5 A, –60 V R

R

Q2

5

6

Q1

7

8

= 55 mΩ @ V

DS(on)

= 75 mΩ @ V

DS(on)

= 105 mΩ @ V

DS(on)

= 135 mΩ @ V

DS(on)

= 10V

GS

= 4.5V

GS

= –10V

GS

= –4.5V

GS

4

3

2

1

Symbol Parameter Q1 Q2 Units

V

Drain-Source Voltage 60 –60 V

DSS

V

Gate-Source Voltage

GSS

ID Drain Current - Continuous (Note 1a) 4.5 –3.5 A

- Pulsed 20 –20

PD Power Dissipation for Dual Operation 2 W

Power Dissipation for Single Operation (Note 1a) 1.6

TJ, T

STG

Operating and Storage Junction Temperature Range -55 to +175

(Note 1b)

(Note 1c)

±20 ±20

1.2

1

V

°C

Thermal Characteristics

R

θJA

R

θJC

Thermal Resistance, Junction-to-Ambient

Thermal Resistance, Junction-to-Case

(Note 1a) 78

(Note 1) 40

Package Marking and Ordering Information

Device Marking Device Reel Size Tape width Quantity

FDS4559 FDS4559 13” 12mm 2500 units

2000 Fairchild Semiconductor Corporation

°C/W

°C/W

FDS4559 Rev C1(W)

FDS4559

Electrical Characteristics T

= 25°C unless otherwise noted

A

Symbol Parameter Test Conditions Type Min Typ Max Units

Drain-Source Avalanche Ratings (Note 1)

W

Single Pulse Drain-Source

DSS

VDD = 30 V, ID = 4.5 A Q1 90 mJ

Avalanche Energy

IAR Maximum Drain-Source

Q1 4.5 A

Avalanche Current

Off Characteristics

BV

Drain-Source Breakdown

DSS

Voltage

∆BVDSS

∆T

I

Zero Gate Voltage Drain

DSS

Breakdown Voltage

Temperature Coefficient

J

Current

I

Gate-Body Leakage VGS = +20 V, VDS = 0 V

GSS

VGS = 0 V, ID = 250 µA

= 0 V, ID = –250 µA

V

GS

= 250 µA, Referenced to 25°C

I

D

= –250 µA, Referenced to 25°C

I

D

VDS = 48 V, VGS = 0 V

= –48 V, VGS = 0 V

V

DS

= +20 V, VDS = 0 V

V

GS

Q2

Q1

Q2

Q1

Q2

Q1

Q2

60

–60

V

58

–49

1

–1

+

+

100

100

mV/°C

Q1

On Characteristics (Note 2)

V

Gate Threshold Volt age VDS = VGS, ID = 250 µA

GS(th)

∆VGS(th)

∆TJ

R

DS(on)

Gate Threshold Voltage

Temperature Coefficient

Static Drain-Source

On-Resistance

= VGS, ID = –250 µA

V

DS

I

= 250 µA, Referenced to 25°C

D

= –250 µA, Referenced to 25°C

I

D

VGS = 10 V, ID = 4.5 A

= 10 V, ID = 4.5 A, TJ = 125°C

V

GS

= 4.5 V, ID = 4 A

V

GS

VGS = –10 V, ID = –3.5 A

= –10 V, ID = –3.5 A, TJ = 125°C

V

GS

= –4.5 V, ID = –3.1 A

V

I

On-State Drain Current VGS = 10 V, VDS = 5 V

D(on)

GS

V

= –10 V, VDS = –5 V

GS

gFS Forward Transconductance VDS = 10 V, ID = 4.5 A

= –5 V, ID = –3 5 A

V

DS

Q1

Q2 1 –1

Q1

Q2

Q1 42

Q2

Q1

Q2

–20

Q1

Q2

2.2

–1.6 3 –3

–5.5 4

mV/°C

55

72

94

55

75

82

20

105

130

190

105

135

A

14 9 S

Dynamic Characteristics

C

Input Capacitance Q1

iss

C

Output Capacitance Q1

oss

C

Reverse Transfer

rss

Capacitance

Q1

= 25 V, VGS = 0 V,

V

DS

f = 1.0 MHz

Q2

= –30 V, VGS = 0 V,

V

DS

f = 1.0 MHz

Q2

Q2

Q1

Q2

650

759

80

90

35

39

pF

pF

pF

Switching Characteristics (Note 2)

t

Turn-On Delay Time

d(on)

tr Turn-On Rise Time

t

Turn-Off Delay Time

d(off)

tf Turn-Off Fall Time

Qg Total Gate Charge

Qgs Gate-Source Charge

Qgd Gate-Drain Charge

Q1

= 30 V, ID = 1 A,

V

DD

= 10V, R

V

GS

GEN

= 6 Ω

Q2

= –30 V, ID = –1 A,

V

DD

= –10 V, R

V

GS

GEN

= 6 Ω

Q1

= 30 V, ID = 4.5 A, VGS = 10 V

V

DS

Q2

= –30 V, ID = –3.5 A, VGS = –10V

V

DS

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

11 7 20

14

8

19

6

12.5

10

19

12

15

18

20

35

34

15

22

18

21

2.4

2.5

2.6

3.0

nC

nC

µA

nA

V

mΩ

ns

ns

ns

ns

nC

FDS4559 Rev C1(W)

V

Electrical Characteristics (continued) T

Symbol

Parameter

Test Conditions

= 25°C unless otherwise noted

A

Type Min Typ Max Units

Drain-Source Diode Characteristics and Maximum Ratings

I

Maximum Continuous Drain-Source Diode Forward Current Q1

S

1.3

Q2

VSD Drain-Source Diode Forward

oltage

Notes:

1. R

is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of

θJA

the drain pins. R

Scale 1 : 1 on letter size paper

2. Pulse Test: Pulse Width < 300µs, Duty Cycle < 2.0%

is guaranteed by design while R

θJC

a) 78°C/W when

mounted on a

0.5 in2 pad of 2 oz

copper

V

= 0 V, IS = 1.3 A (Note 2)

GS

VGS = 0 V, IS = –1.3 A (Note 2)

is determined by the user's board design.

θCA

b) 125°C/W when

mounted on a .02 in2

pad of 2 oz copper

Q1

Q2

0.8

–0.8

c) 135°C/W when mounted on a

minimum pad.

FDS4559

–1.3 A

1.2

–1.2 V

FDS4559 Rev C1(W)

Loading...

Loading...