Fairchild Semiconductor FAN8042 Datasheet

FAN8042

5-CH Motor Driver

www.fairchildsemi.com

FAN8042 Features

• 4-CH balanced transformerless (BTL) driver

• 1-CH (forward reverse) control DC motor driver

• Operating supply voltage (4.5 V ~ 13.2 V)

• Built in thermal shut down circuit (TSD)

• Built in channel mute circuit

• Built in power save mode circuit

• Built in TSD monitor circuit

• Built in 2-OP AMPs

Description

The FAN8042 is a monolithic integrated circuit suitable for

a 5-CH motor driver which drives the tracking actuator,

focus actuator, sled motor, spindle motor, and tray motor of

the CDP/CAR-CD/DVDP systems.

48-QFP-1010E

Typical Application

• Compact disk player

• Video compact disk player

• Car compact disk player

• Digital video disk player

©2001 Fairchild Semiconductor Corporation

Ordering Information

Device Package Operating Temperature

FAN8042 48-QFP-1010E −35°C ~ +85°C

Rev. 1.0.0

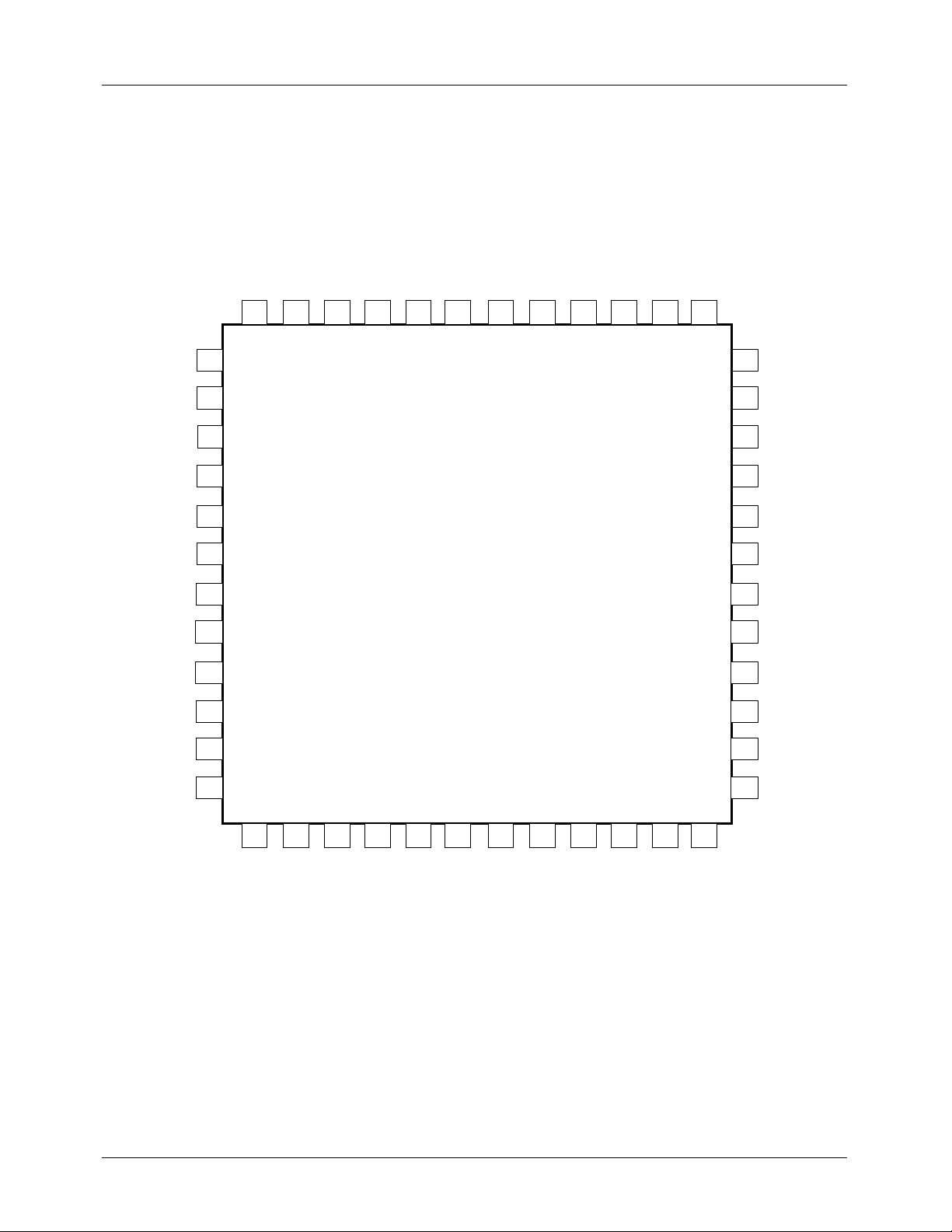

Pin Assignments

IN1+

IN1-

OUT1

IN2+

IN2-

GND

GND

OUT2

IN3+

IN3-

OPOUT1

SVCC

GND

FAN8042

GND

OPIN2+

OPIN2-

OPIN1-

OPIN1+

48 47 46 45 44 43 42 41 40 39 38 37

1

2

3

4

5

6

7

8

9

10

VREF

PS

OPOUT2

PVCC1

36

35

34

33

32

31

30

29

28

27

DO1+

DO1-

DO2+

DO2-

DO3+

GND

GND

DO3-

DO4+

DO4-

OUT3

IN4+

11

12

13 14 15 16 17 18 19 20 21 22 23 24

IN4-

OUT4

CTL

FWD

REV

GND

GND

SGND

MUTE123

MUTE4

TSD-M

26

25

PVCC2

DO5+

DO5-

2

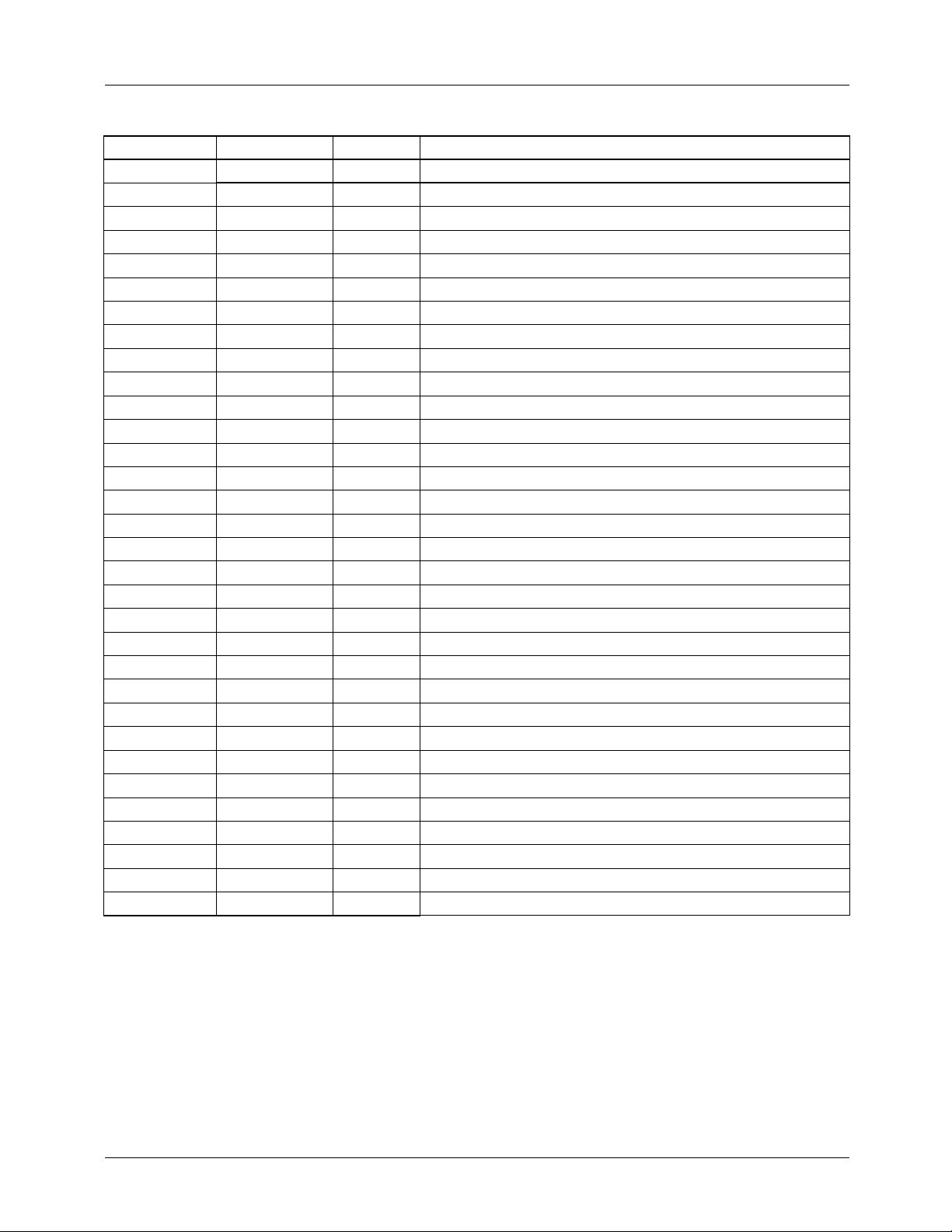

Pin Definitions

Pin Number Pin Name I/O Pin Function Descrition

1IN1+ I CH1 op-amp input (+)

2IN1− I CH1 op-amp input (−)

3 OUT1 O CH1 op-amp output

4IN2+ I CH2 op-amp input (+)

5IN2− I CH2 op-amp input (−)

6 GND - Ground

7 GND - Ground

8 OUT2 O CH2 op-amp output

9 IN3+ I CH3 op-amp input (+)

10 IN3− I CH3 op-amp input (−)

11 OUT3 O CH3 op-amp output

12 IN4+ I CH4 op-amp input (+)

13 IN4− I CH4 op-amp input (−)

14 OUT4 O CH4 op-amp output

15 CTL I CH5 motor speed control

16 FWD I CH5 forward input

17 REV I CH5 reverse input

18 GND - Ground

19 GND - Ground

20 SGND - Signal Ground

21 MUTE123 I Mute for CH1,2,3

22 MUTE4 I Mute for CH4

23 TSD-M O TSD monitor

24 PVCC2 - Power supply voltage 2 (For CH4, CH5)

25 DO5- O CH5 drive output (-)

26 DO5+ O CH5 drive output (+)

27 DO4− O CH4 drive ouptut (−)

28 DO4+ O CH4 drive output (+)

29 DO3− O CH3 drive ouptut (−)

30 GND - Ground

31 GND - Ground

32 DO3+ O CH3 drive output (+)

3

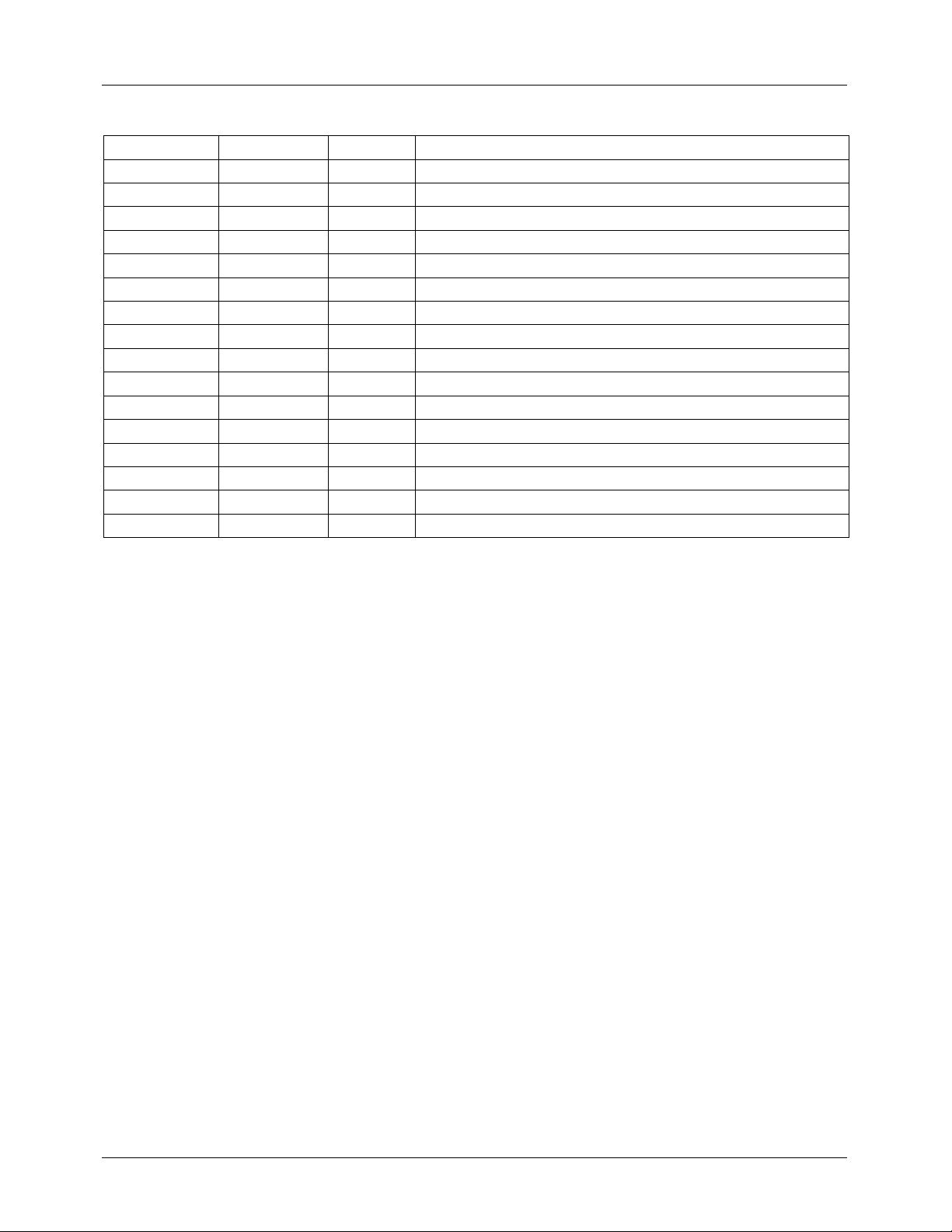

Pin Definitions (Continued)

Pin Number Pin Name I/O Pin Function Descrition

33 DO2− O CH2 drive ouptut (−)

34 DO2+ O CH2 drive output (+)

35 DO1− O CH1 drive ouptut (−)

36 DO1+ O CH1 drive output (+)

37 PVCC1 - Power supply voltage 1 (FOR CH1, CH2, CH3)

38 PS I Power save

39 OPOUT2 O Normal op-amp2 output

40 OPIN2− I Normal op-amp2 input (−)

41 OPIN2+ I Normal op-amp2 input (+)

42 GND - Ground

43 GND - Ground

44 VREF I Bias voltage input

45 SVCC - Signal & OPAMPs supply voltage

46 OPOUT1 O Normal op-amp1 output

47 OPIN1− I Normal op-amp1 input (−)

48 OPIN1+ I Normal op-amp1 input (+)

4

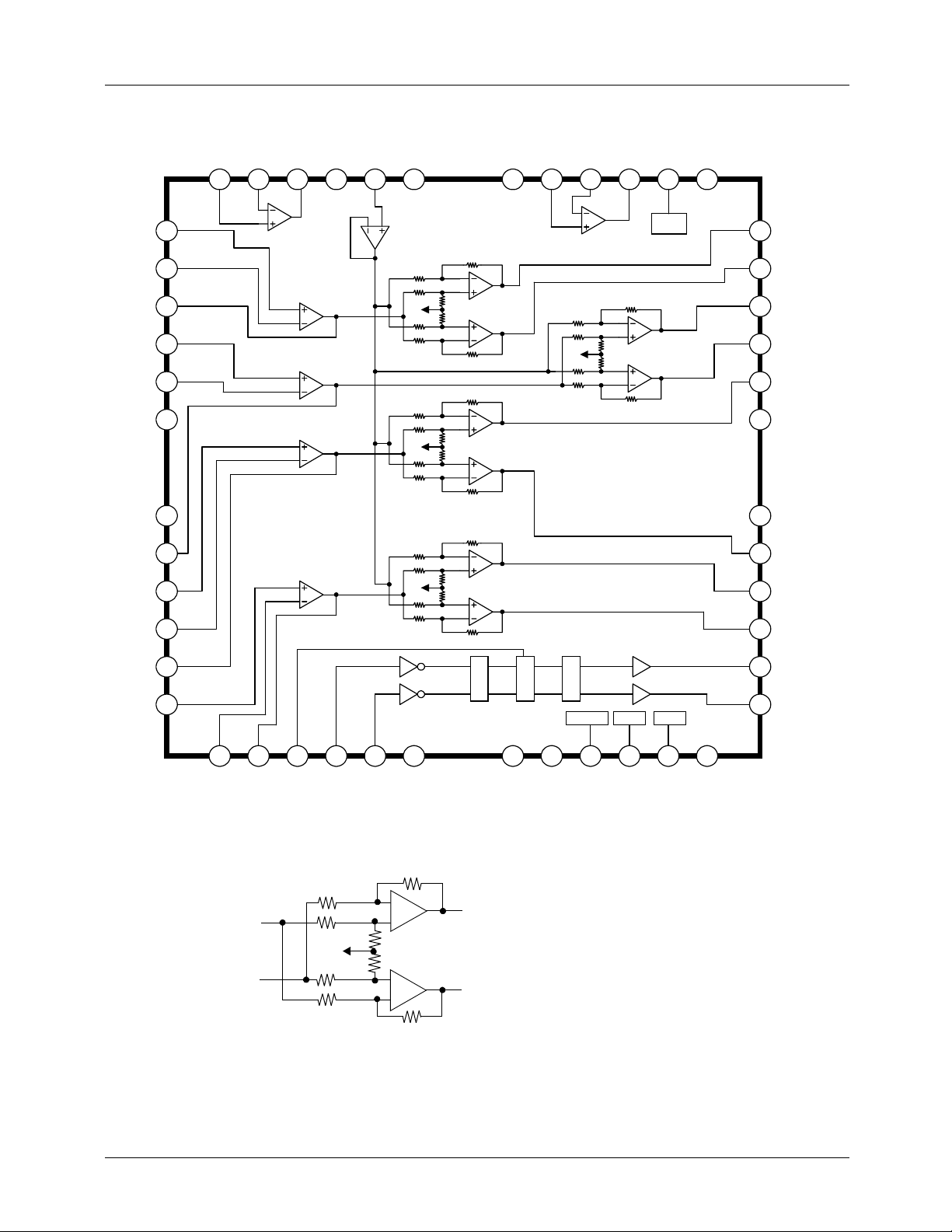

Internal Block Diagram

IN1+

IN1-

OUT1

IN2+

IN2-

GND

GND

OUT2

IN3+

IN3-

OPIN1+ OPIN1- OPOUT1 SVCC VREF OPIN2- OPOUT2 PS PVCC1

GND GND

OPIN2+

42

1

2

10K

10K

3

4

10K

10K

5

6

10K

10K

10K

10K

40K

40K

40K

40K

40K

40K

40K

40K

10K

10K

40K

40K

10K

10K

7

8

10K

10K

9

10K

10

10K

40K

40K

40K

40K

3738394041434445464748

POWER

POWER

POWER POWER

SAVE

SAVE

SAVESAVE

40K

40K

36

DO1+

35

DO1-

DO2+

34

DO2-

33

DO3+

32

GND

31

GND

30

DO3-

29

DO4+

28

27

DO4-

OUT3

11

12

IN4+

OUT4IN4-

Note.

Detailed circuit of the output power amp

From input opamp

Vref

Pref1 is almost PVCC1 / 2

Pref2 is almost PVCC2 / 2

M

S

S

C

W

+

-

MUTE123

MUTE123 MUTE4

MUTE123MUTE123

19

CTL FWD REV GND TSD-M PVCC2

GND SGND MUTE4

D

D

MUTE4 TSD-M

TSD-M

MUTE4MUTE4

TSD-MTSD-M

2423222120181716151413

MUTE123

40K

10K

10K

Pref

10K

−

+

40K

40K

+

−

DO+

DO-

10K

40K

DO5+

26

25

DO5-

5

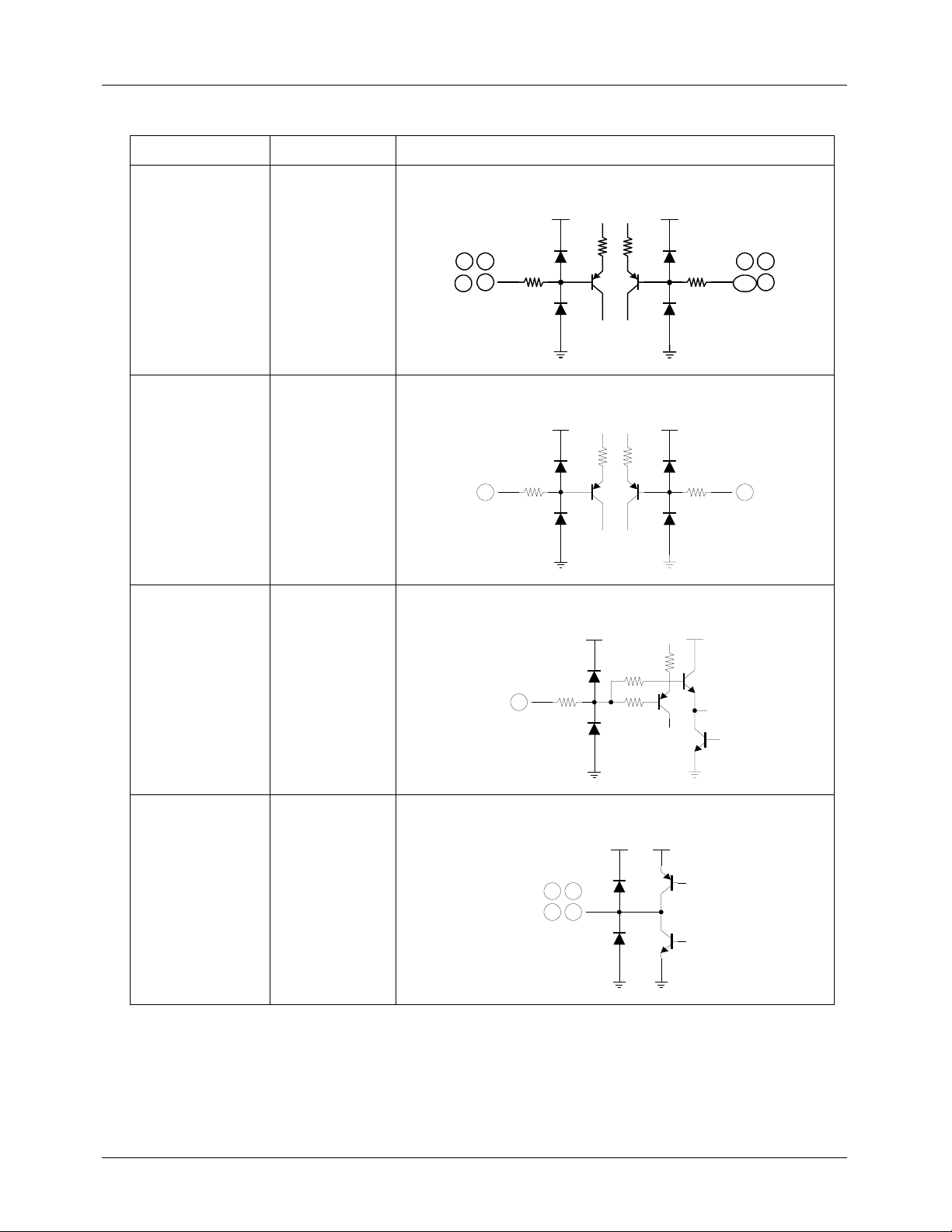

Equivalent Circuits

Description Pin No Internal Circuit

VCC VCC

1,4,9,12,

BTL INPUT

2,5,10,13

OP AMP INPUT 40,41

2K 2K

4 1

12

9 10

VCC

VCC

5K 5K

VCC VCC

5K

1K

5 2

13

41 40

VREF 44

OP AMP

OUTPUT 3,8,11,14

44

1K

VCC VCC

8

3

14

11

6

Loading...

Loading...