Fairchild Semiconductor FAN8037 Datasheet

FAN8037 (KA3037)

7-CH Motor Driver

www.fairchildsemi.com

Features

• 4-CH balanced transformerless (BTL) driver

• 3-CH (forward - reverse) control DC motor driver

• Operating supply voltage (4.5 V ~ 13.2 V)

• Built-in thermal shut down circuit (TSD)

• Built-in all channel mute circuit

• Built-in power save mode circuit

• Built-in stand by mode circuit

• Built-in variable regulator

Description

The FAN8037 is a monolithic integrated circuit suitable for

a 7-ch motor driver which drives the tracking actuator, focus

actuator, sled motor, tray motor, changer motor, panel motor

and, spindle motor of the CDP/CAR-CD systems.

48-QFPH-1414

Target Applicat ion

• Compact disk player (Tray, Changer)

• Video compact disk player (Tray, Changer)

• Car compact disk player (Tray, Changer)

• Mixing with compact disk player and mini disk player

(Tray, Changer, Panel)

©2000 Fairchild Semiconductor International

Ordering Information

Device Package Operating Temp.

FAN8037 48-QFPH-1414 −35°C ~ +85°C

Rev. .1.0.2

May. 2000.

1

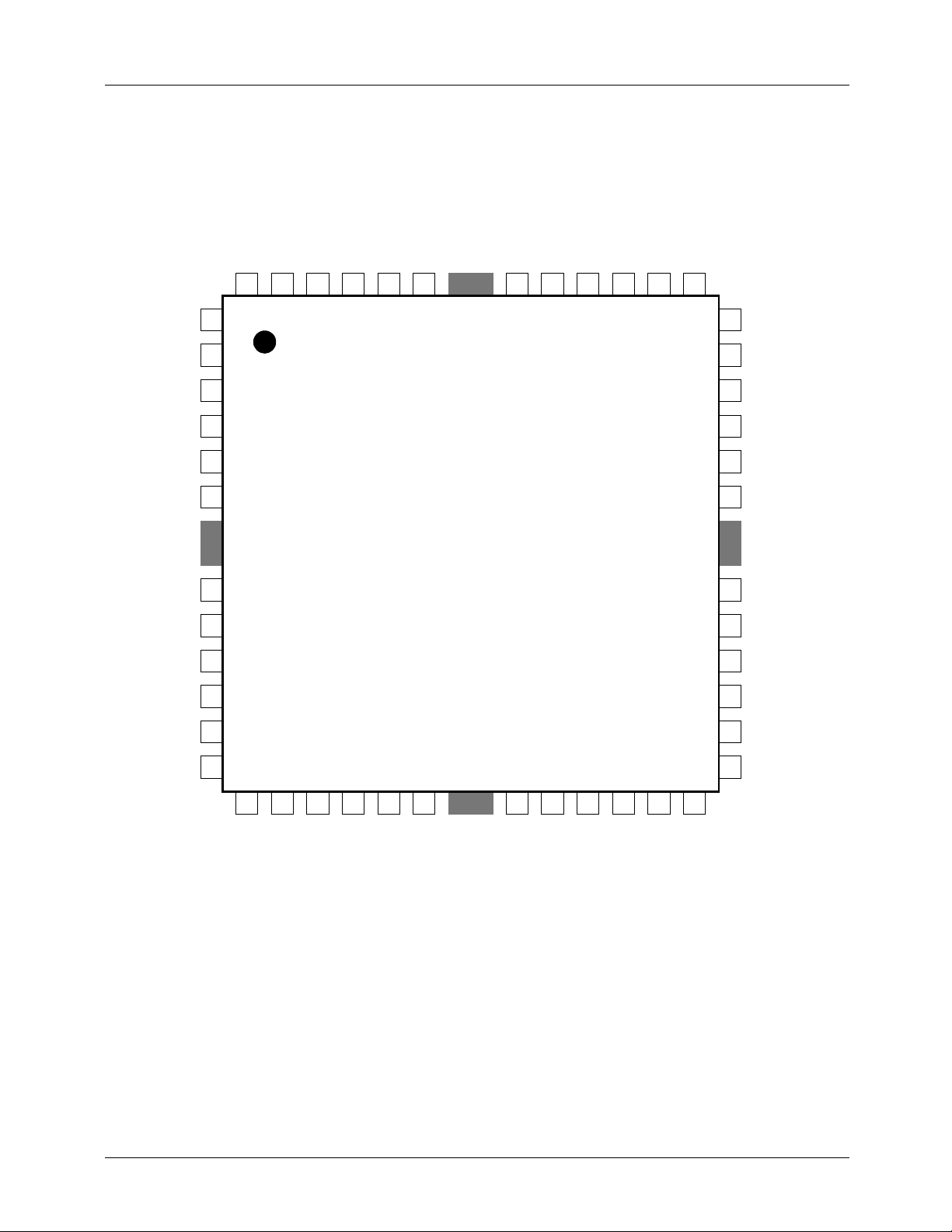

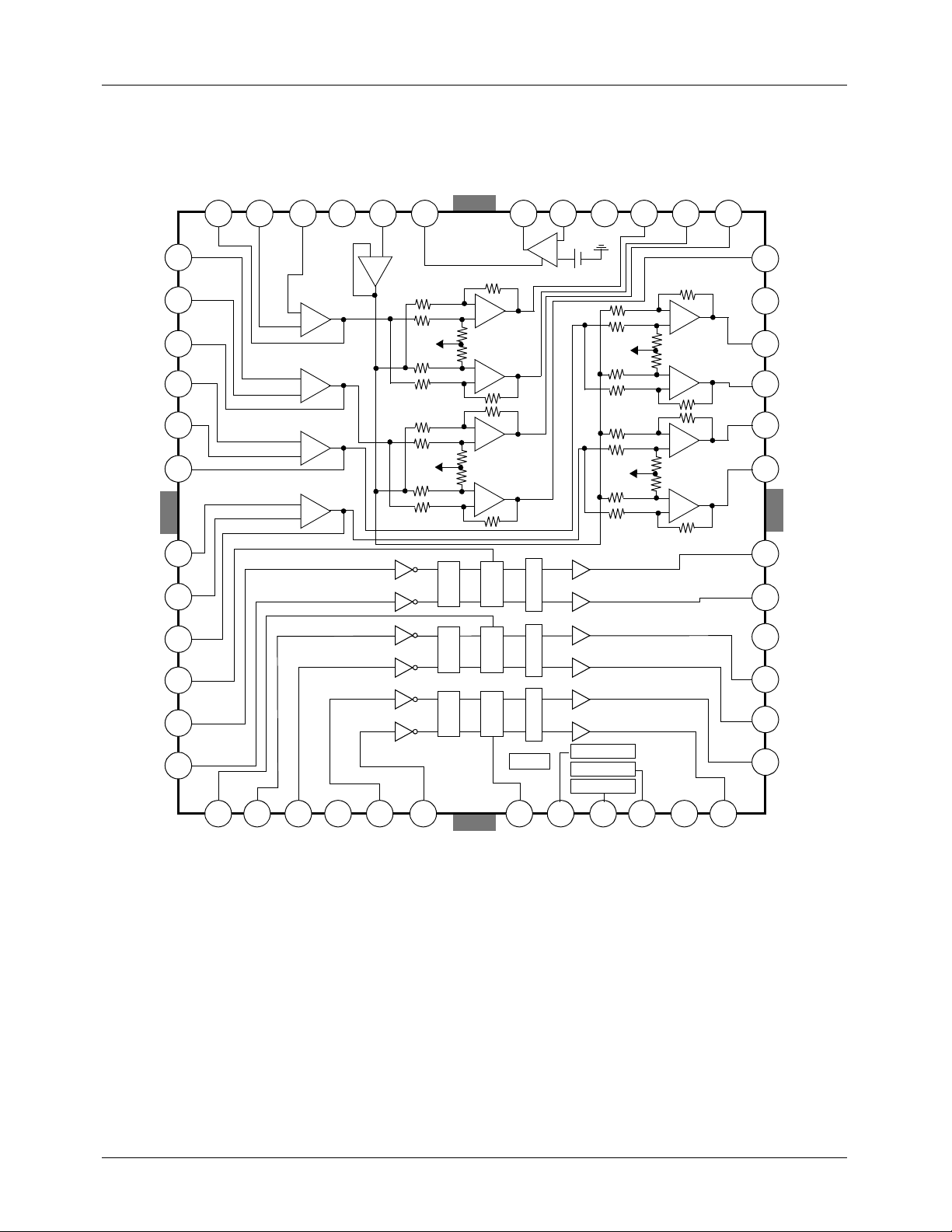

Pin Assignments

OUT1

48 47 46 45 44 43 42 41 40 39 38 37

FAN8037 (KA3037)

IN1.1

SVCC

VREF

IN1.2

RESX

REGX

REGOX

PVCC1

DO1+

DO1−

DO2+

IN2.1

IN2.2

OUT2

IN3.1

IN3.2

OUT3

IN4.1

IN4.2

OUT4

CTL1

FWD1

REV1

1

2

3

4

5

6

DO2−

36

35

PGND1

DO3+

34

DO3−

33

32

DO4+

31

DO4−

FAN8037

7

8

9

10

11

12

30

DO5+

29

DO5−

PGND2

28

DO6+

27

26

DO6−

DO7+

25

13 14 15 16 17 18 19 20 21 22 23 24

SB

CTL2

FWD2

REV2

SGND

FWD3

REV3

CTL3

PS

MUTE

PVCC2

2

DO7−

FAN8037 (KA3037)

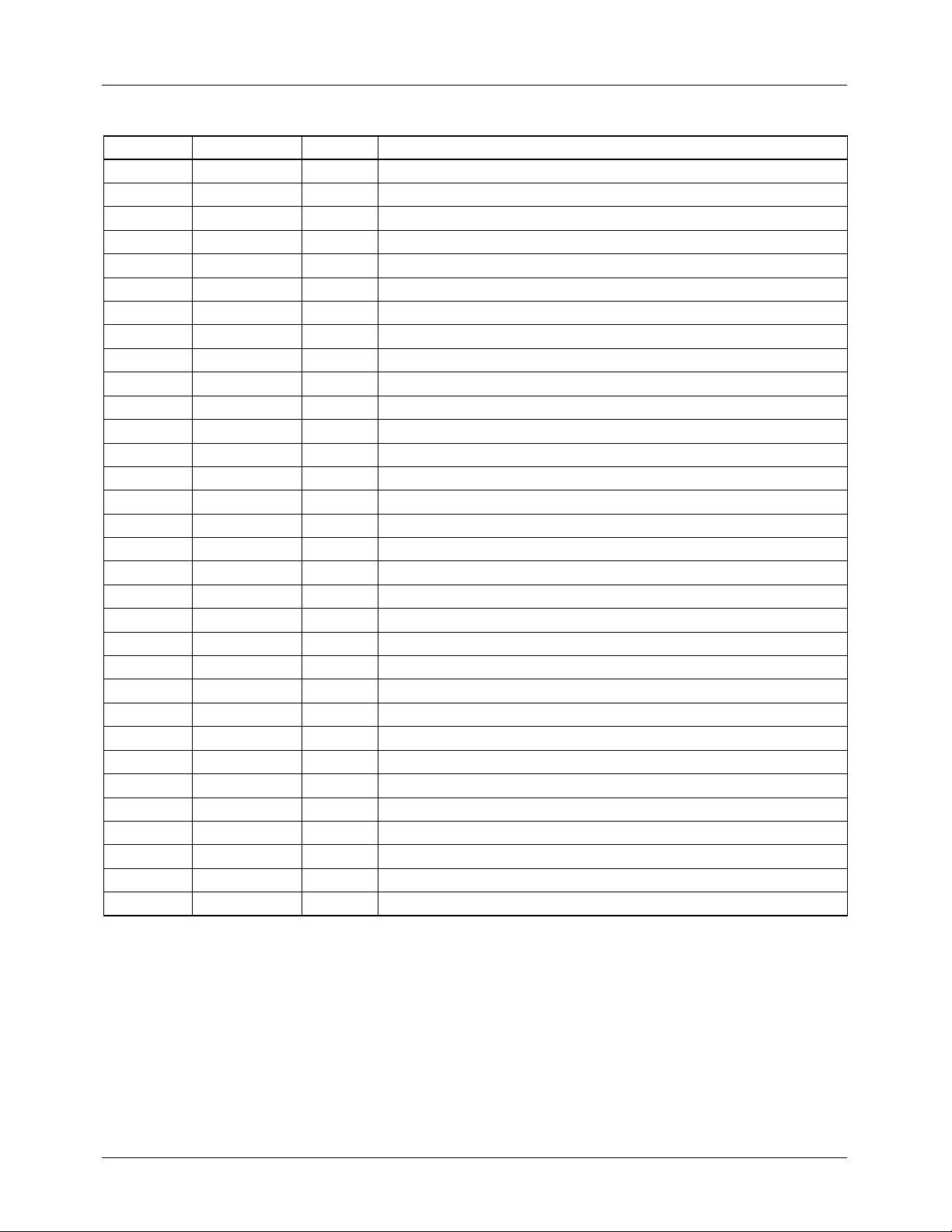

Pin Definitions

Pin Number Pin Name I/O Pin Function Descrition

1 IN2.1 I CH2 op-amp input (+)

2IN2.2 I CH2 op-amp input (−)

3 OUT2 O CH2 op-amp output

4 IN3.1 I CH3 op-amp input (+)

5IN3.2 I CH3 op-amp input (−)

6 OUT3 O CH3 op-amp output

7 IN4.1 I CH4 op-amp input (+)

8IN4.2 I CH4 op-amp input (−)

9 OUT4 O CH4 op-amp output

10 CTL1 I CH5 motor speed control

11 FWD1 I CH5 forward input

12 REV1 I CH5 reverse input

13 CTL2 I CH6 motor speed control

14 FWD2 I CH6 forward input

15 REV2 I CH6 reverse input

16 SGND - Signal groung

17 FWD3 I CH7 forward input

18 REV3 I CH7 reverse input

19 CTL3 I CH7 motor speed control

20 SB I Stand by

21 PS I Power save

22 MUTE I All mute

23 PVCC2 - Power supply voltage (For CH5, CH6, CH7)

24 DO7− O CH7 drive ouptut (−)

25 DO7+ O CH7 drive output (+)

26 DO6− O CH6 drive output (−)

27 DO6+ O CH6 drive output (+)

28 PGND2 - Power ground2 (FOR CH5, CH6, CH7)

29 DO5− O CH5 drive output (−)

30 DO5+ O CH5 drive output (+)

31 DO4− O CH4 drive output (−)

32 DO4+ O CH4 drive output (+)

3

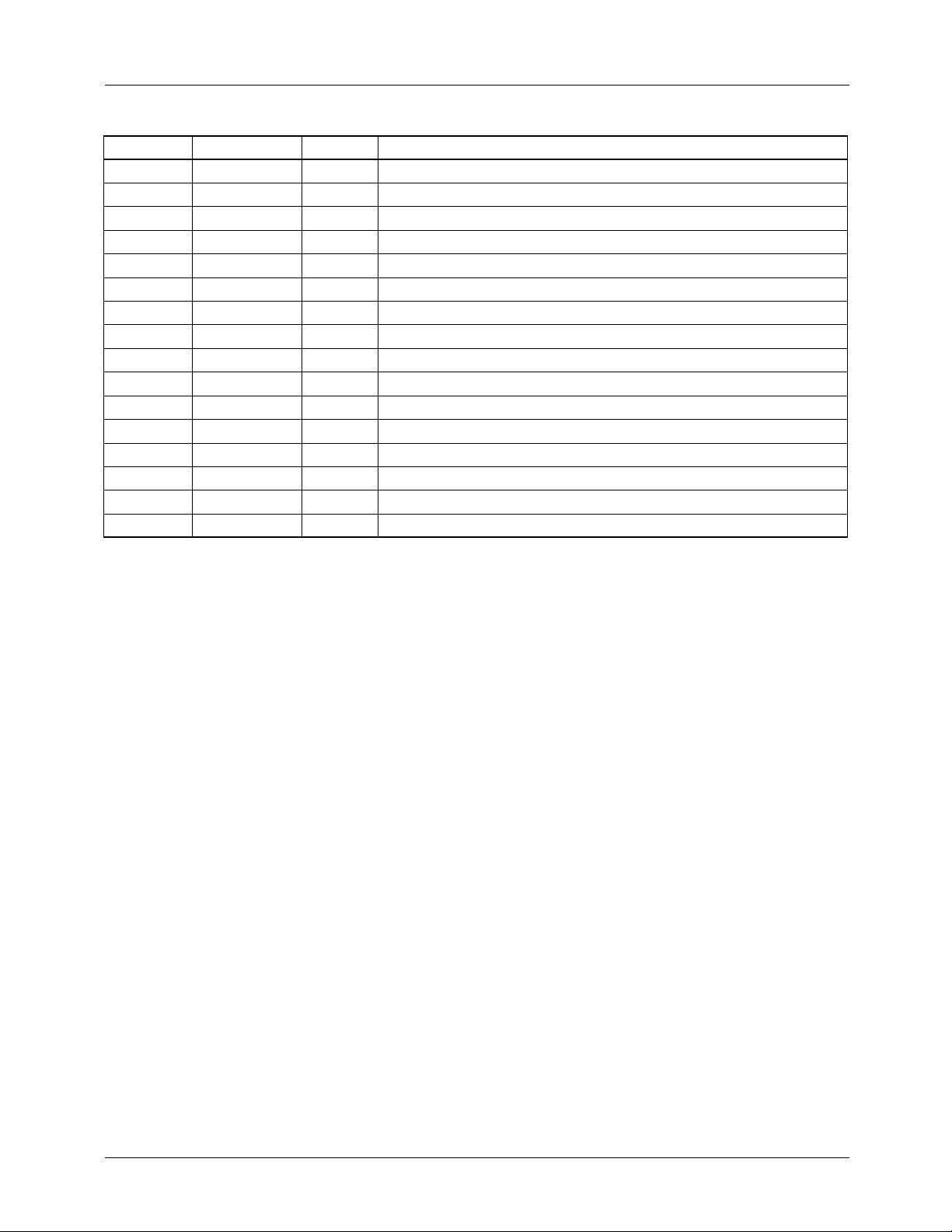

Pin Definitions (Continued)

Pin Number Pin Name I/O Pin Function Descrition

33 DO3− O CH3 drive output (−)

34 DO3+ O CH3 drive output (+)

35 PGND1 - Power ground 1 (FOR CH1, CH2, CH3, CH4)

36 DO2− O CH2 drive output (−)

37 DO2+ O CH2 drive output (+)

38 DO1− O CH1 drive output (−)

39 DO1+ O CH1 drive output (+)

40 PVCC1 - Power supply voltage (FOR CH1, CH2, CH3, CH4)

41 REGOX I Regulator feedback input

42 REGX O Regulator output

43 RESX I Regulator reset input

44 VREF I Bias voltage input

45 SVCC - Signal supply voltage

46 IN1.1 I CH1 op-amp input (+)

47 IN1.2 I CH1 op-amp input (−)

48 OUT1 O CH1 op-amp output

FAN8037 (KA3037)

4

FAN8037 (KA3037)

Internal Block Diagram

1

IN2.1

DO2+DO1−DO1+PVCC1REGOXREGXRESXVREFSVCCIN1.1IN1.2OUT1

373839404142434445464748

+

−

+

−

DO2−

36

IN2.2

OUT2

IN3.1

IN3.2

OUT3

IN4.1

IN4.2

OUT4

CTL1

FWD1

REV1

2

3

4

5

6

7

8

9

10

11

12

+

−

+

−

+

−

+

−

−

+

+

−

−

+

+

−

D

+

M

S

S

W

C

−

D

D

+

M

S

S

W

C

−

D

D

+

M

S

S

W

C

−

D

T.S.D

STAND BY

ALL MUTE

POWER SAVE

−

+

+

−

−

+

+

−

PGND1

35

DO3+

34

33

DO3−

DO4+

32

DO4−

31

DO5+

30

DO5−

29

28

PGND2

DO6+

27

DO6−

26

25

DO7+

13 14 15 16 17 18 19 20 21 22 23 24

CTL2 FWD2 REV2 SGND FWD3 REV3 CTL3 SB PS MUTE PVCC2 DO7−

Notes:

1. SW = Logic switch

2. MSC = Motor speed control

3. D = Output driver

5

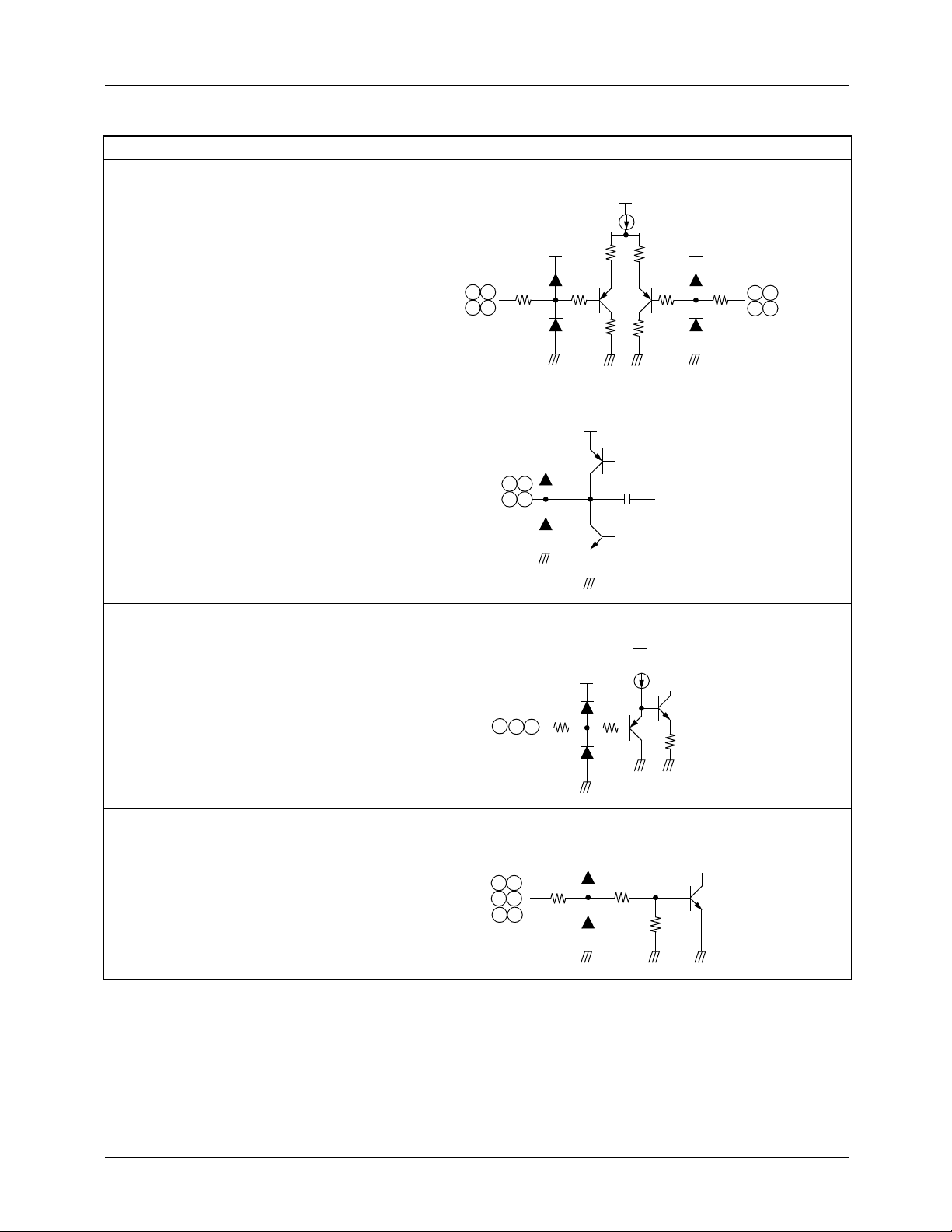

Equivalent Circuits

Description Pin No. Internal circuit

Input

OPIN (+)

OPIN (−)

46,47,1,2

4,5,7,8

SVCC SVCC

FAN8037 (KA3037)

SVCC

Input

48,3,6,9

opout

CTL 10,13,19

46 1

4 7

10

0.05k

48 3

6 9

13 19

SVCC

0.05k

SVCC

SVCC

0.05k

SVCC

1k

47

5 8

2

Logic drive

FWD input

REV input

11,12,

14,15,

17,18

SVCC

11

14 15

17 18

12

0.05k

30k

30k

6

FAN8037 (KA3037)

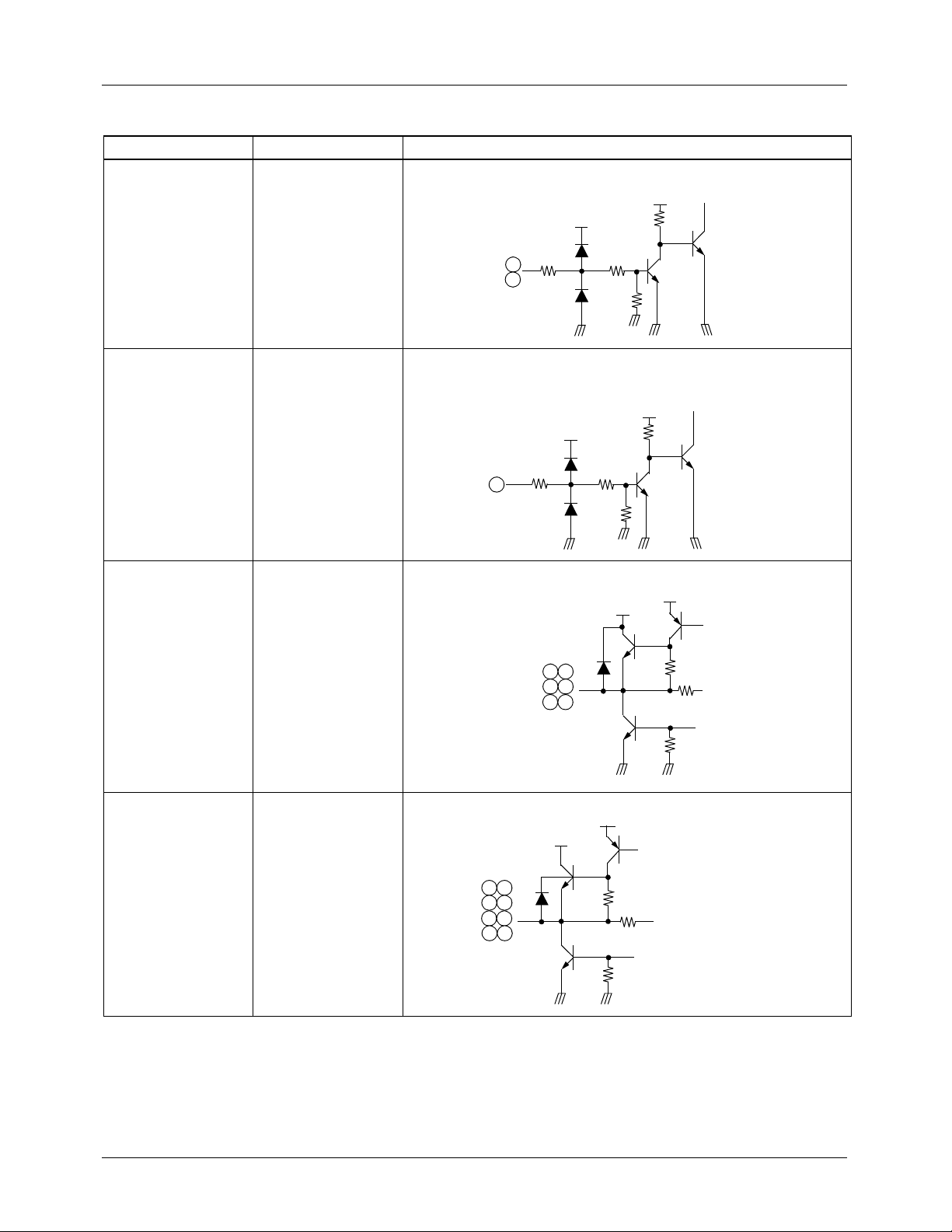

Equivalent Circuits (Continued)

Description Pin No. Internal circuit

Power save

Standby

20,21

SVCC

SVCC

Mute 22

Logic

drive

output

24, 25

26, 27

29,30

SVCC

50k

50k

PVCC2

50k

SVCC

50k

SVCC

30k

1k

0.05k

20

21

0.05k

22

24 25

26 27

29 30

4-CH

drive

output

31, 32

33, 34

36, 37

38, 39

7

31 32

33 34

36 37

38 39

25k

SVCC

PVCC1

20k

20k

25k

Loading...

Loading...