Fairchild Semiconductor 74VHCT138AMTC, 74VHCT138AM, 74VHCT138ACW, 74VHCT138ASJX, 74VHCT138ASJ Datasheet

...

June 1997

Revised April 1999

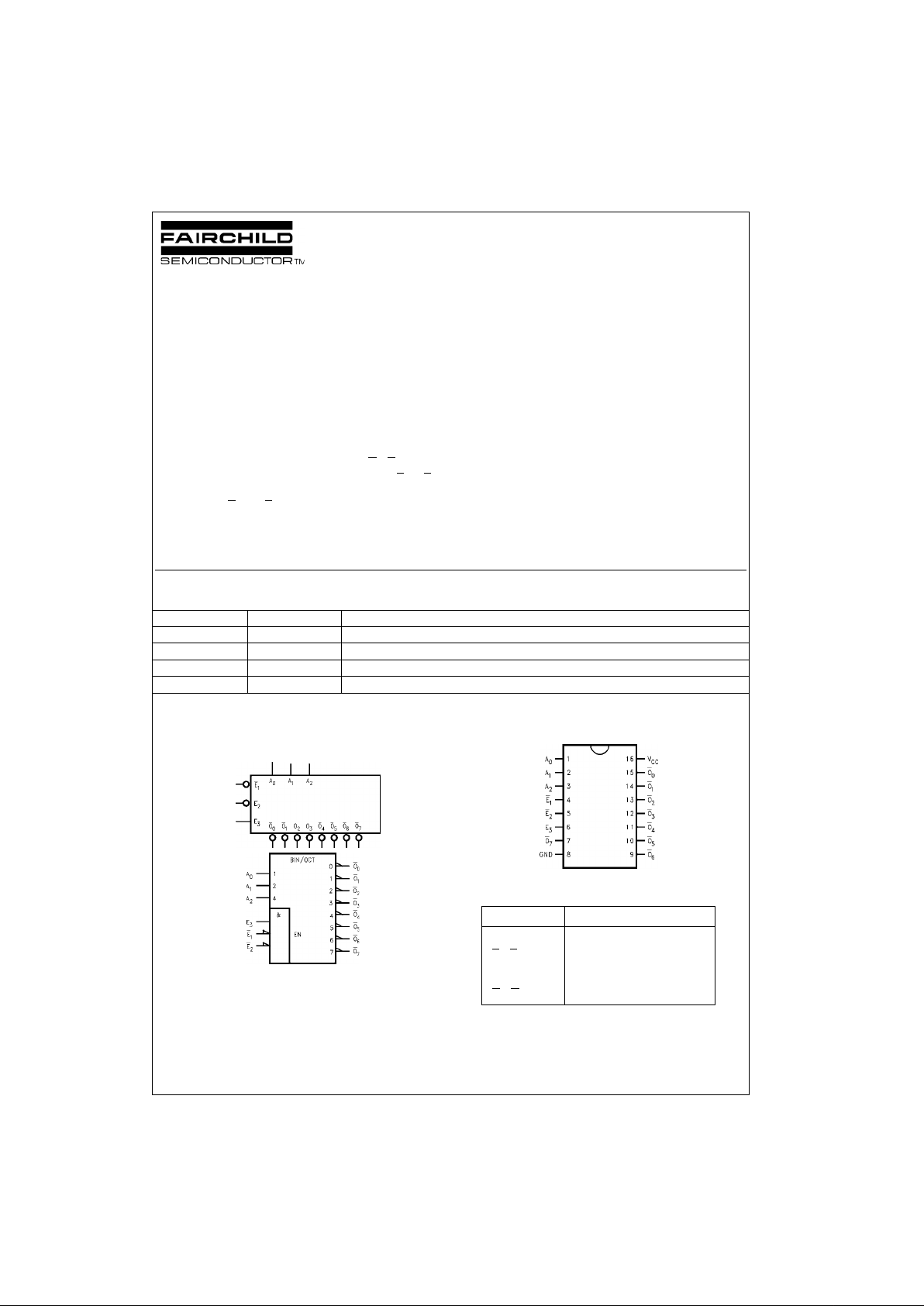

74VHCT138A 3-to-8 Decoder/Demultiplexer

© 1999 Fairchild Semiconductor Corporation DS500014.prf www.fairchildsemi.com

74VHCT138A

3-to-8 Decoder/Demultiplexer

General Description

The VHCT138A is an ad vanced high speed C MOS 3-to-8

DECODER fabricated with silic on gate CMOS technology.

It achieves the high speed operation similar to equivalent

Bipolar Schottky TTL while maintaining the CMOS low

power dissipation.

When the device is enab led, 3 Binary Select inputs ( A

0

, A

1

and A2) determine which one of the outputs (O0–O7) will go

LOW. When enable input E

3

is held LOW or either E1 or E

2

is held HIGH, decoding function is inhib ited and all outputs

go HIGH. E

3

, E1 and E2 inputs are provided to ease cas-

cade connection and for use as an address decoder f or

memory systems. Protection circuit s ensure that 0V to 7V

can be applied to the input pins without r egard to the sup-

ply voltage and to the output pins with V

CC

= 0V. These cir-

cuits prevent device destruction due to m isma tche d s upp l y

and input/output voltages. This device can be used to interface 3V to 5V systems and two supply system s such as

battery backup.

Features

■ High Speed: tPD = 7.6 ns (typ) at VCC = 5V

■ Low power dissipation: I

CC

= 4 µA (max.) at TA = 25°C

■ Power down protection is provided on all inputs and

outputs

■ Pin and function compatible with 74HCT138

Ordering Code:

Surface mount pack ages are also available on Tape and Reel. Specify by appending the s uffix let te r “X” to the ordering code.

Logic Symbols

IEEE/IEC

Connection Diagram

Pin Descriptions

Order Number Package Number Package Description

74VHCT138AM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74VHCT138ASJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74VHCT138AMTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74VHCT138AN N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Pin Names Description

A

0–A2

Address Inputs

E

1–E2

Enable Inputs

E

3

Enable Input

O

0–O7

Outputs

www.fairchildsemi.com 2

74VHCT138A

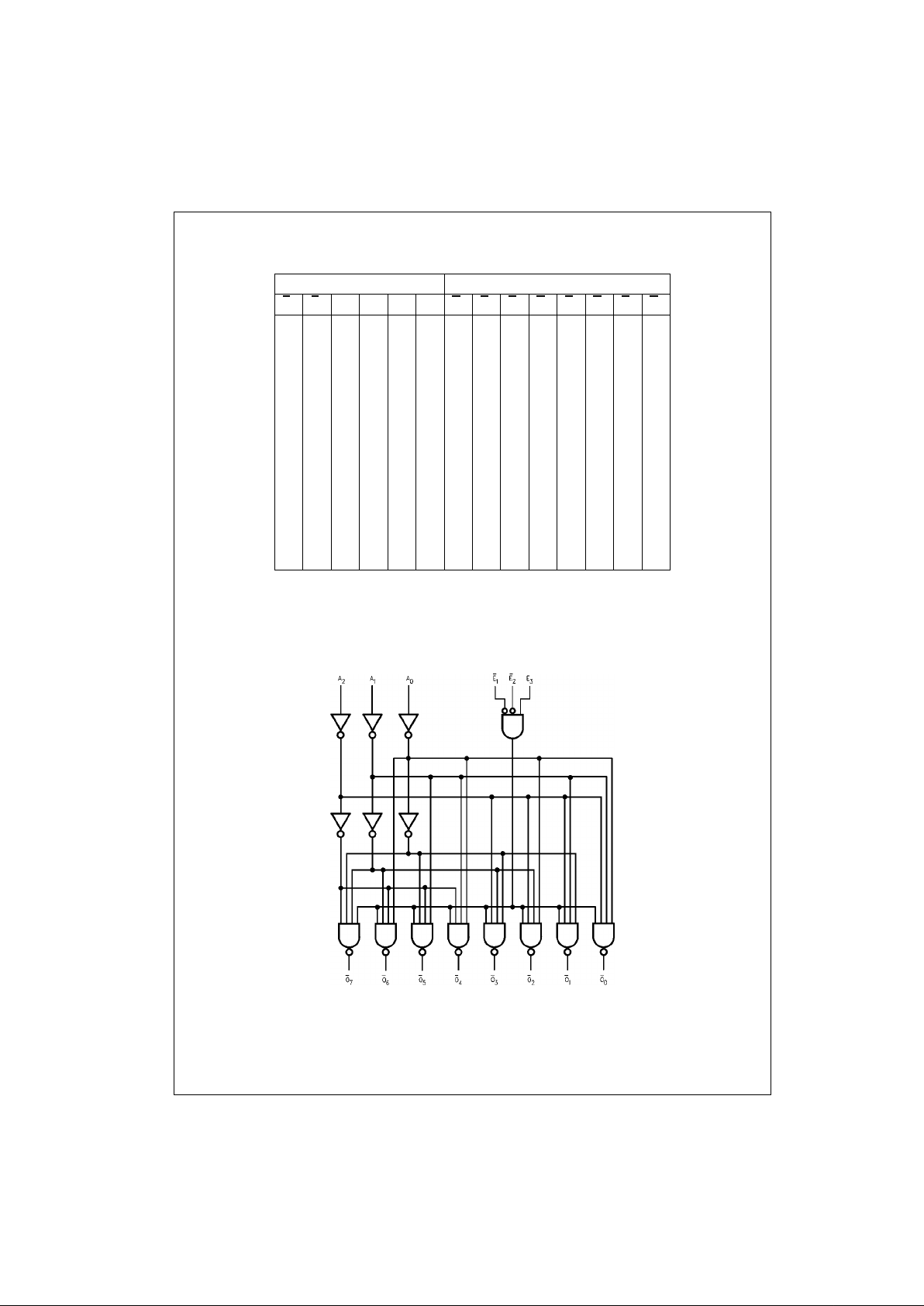

Truth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Logic Diagram

Please note that this diagram is provided on ly fo r th e understanding of logic operations and should not be used to est im at e propagation delays.

Inputs Outputs

E

1E2E3A0A1A2O0O1O2O3O4O5O6O7

HXXXXXHHHHHHHH

XHXXXXHHHHHHHH

XXLXXXHHHHHHHH

LLHLLLLHHHHHHH

LLHHLLHLHHHHHH

LLHLHLHHLHHHHH

LLHHHLHHHLHHHH

LLHLLHHHHHLHHH

LLHHLHHHHHHLHH

LLHLHHHHHHHHLH

LLHHHHHHHHHHHL

Loading...

Loading...