Fairchild Semiconductor 74VHC163SJX, 74VHC163N, 74VHC163SJ, 74VHC163MX, 74VHC163MTCX Datasheet

...

September 1995

Revised April 1999

74VHC163 4-Bit Binary Counter with Synchronous Clear

© 1999 Fairchild Semiconductor Corporation DS012122.prf www.fairchildsemi.com

74VHC163

4-Bit Binary Counter with Synchronous Clear

General Description

The VHC163 is an advanced high-speed CMOS device

fabricated with silicon gate CMOS technology. It achieves

the high-speed operation similar to equivalent Bipolar

Schottky TTL while maintaining the CMOS low power dissipation.

The VHC163 is a high-speed synchronous modulo-16

binary counter. This device is synchronously presettable for

application in prog ramm able divid ers and has two types of

Count Enable inputs plus a Terminal Count output for versatility in forming multistage counters. The CLK input is

active on the rising edge. Both PE

and MR inputs are

active on low logic level. Presetting is synchronous to rising

edge of CLK and the Clea r fun ction of the V HC163 is sy nchronous to CLK. Two enable inputs (ENP and ENT) and

Carry Output are provided to enable easy cascading of

counters, which facilitates easy implementation of n-bit

counters without using external gates.

An input protecti on circuit insures that 0V to 7 V can be

applied to the inp ut pins with out regard to the sup ply voltage. This device can be used to interface 5V to 3V systems

and two supply systems such as battery backup. Th is circuit prevents device destruction due to m ismatched supply

and input voltages.

Features

■ High speed: f

MAX

= 185 MHz (typ) at VCC= 5V

■ Low power dissipation: I

CC

= 4 µA (max) at TA= 25°C

■ Synchronous counting and loading

■ High-speed synchronous expan sion

■ High noise immunity: V

NIH

= V

NIL

= 28% VCC (min)

■ Power down protection is provided on all inputs.

■ Low noise: V

OLP

= 0.8V (max)

■ Pin and function compatible with 74HC163

Ordering Code:

Surface mount pack ages are also available on Tape and Reel. Specify by appending the s uffix let te r “X” to the ordering code .

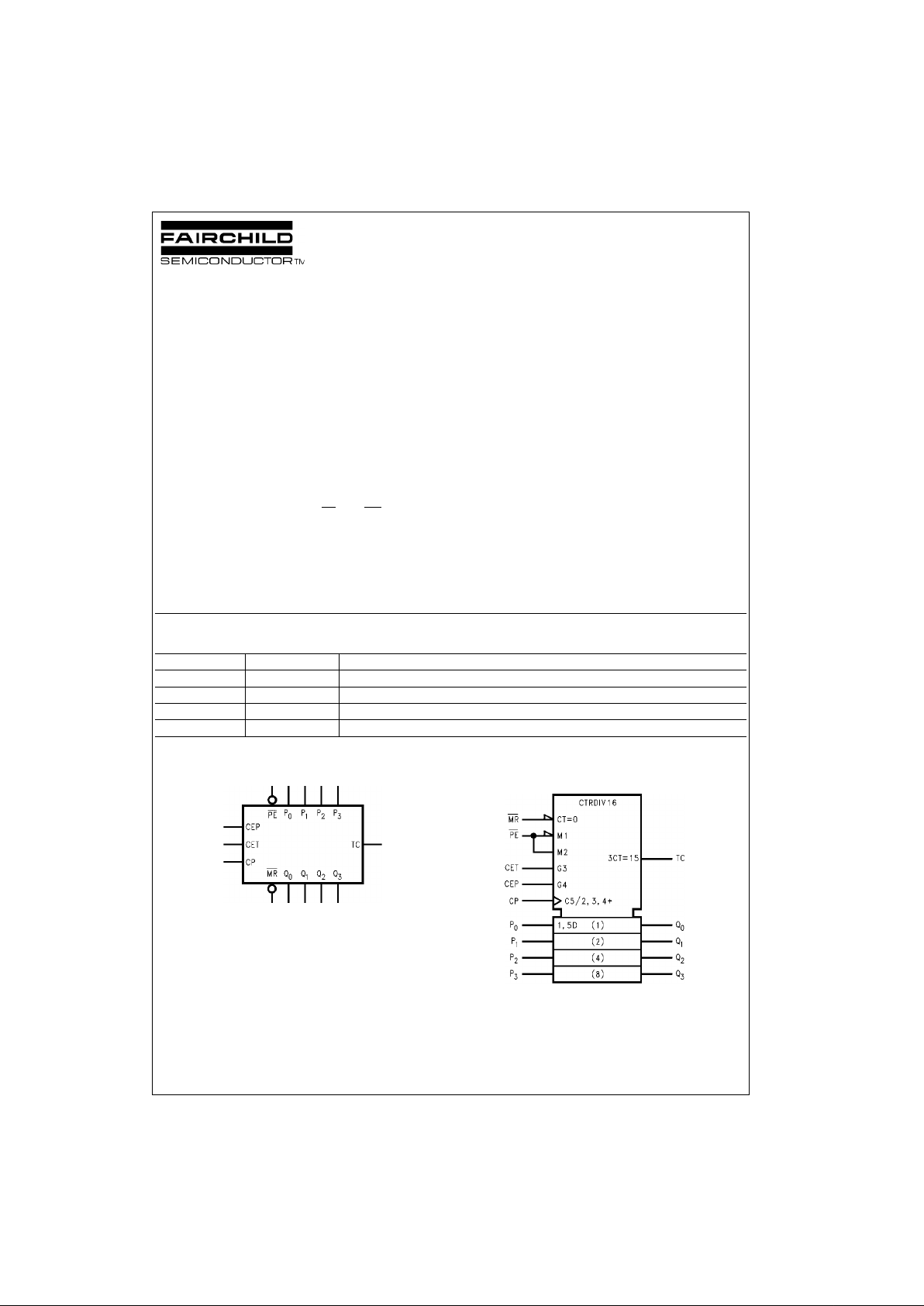

Logic Symbols

IEEE/IEC

Order Number Package Number Package Description

74VHC163M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74VHC163SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74VHC163MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74VHC163N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

74VHC163

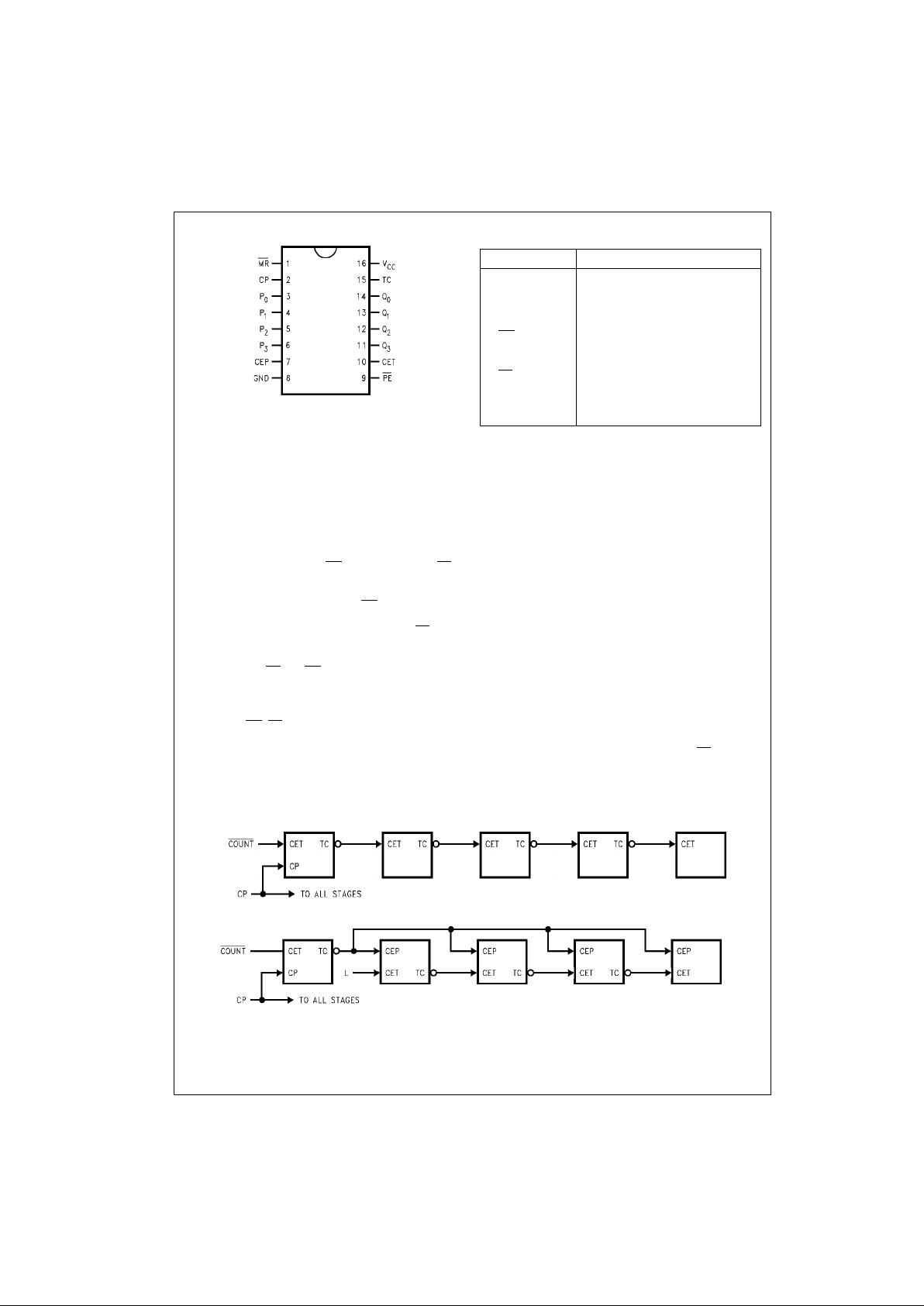

Connection Diagram Pin Descriptions

Functional Description

The VHC163 counts i n modulo-16 bi nary sequenc e. From

state 15 (HHHH) it increments to state 0 (LLLL). The clock

inputs of all flip-flops a re driven in para llel through a clock

buffer. Thus all changes of the Q outputs occur as a result

of, and synchronous with , the LOW-to-HIGH transition of

the CP input signal. The circuits have four fundamental

modes of operation , in order of precedence : synchronous

reset, parallel load, count-up and hold. Four control

inputs—Synchronous Reset (MR

), Parallel Enable (PE),

Count Enable Parallel (CEP) and Count Enable Trickle

(CET)—determine th e mode o f operation , as shown in the

Mode Select Table. A LOW signal on MR

overrides counting and parallel loading and allo ws all outputs to go LOW

on the next rising edge of CP. A LOW signal on PE

overrides counting and allows information on the Parallel Data

(P

n

) inputs to be loaded into the flip-flops on the next rising

edge of CP. With PE

and MR HIGH, CEP and CET permit

counting when both are HIGH. Conversely, a LOW signal

on either CEP or CET inhibi ts counting.

The VHC163 uses D-type edge-triggered flip-flops and

changing the MR

, PE, CEP and CET inputs when the CP is

in either state does not cause errors, provided that the recommended setup and hold times, with respect to the rising

edge of CP, are observed.

The Terminal Count (TC) output is HIGH when CET is

HIGH and counter is in state 15. To implement sync hro-

nous multistage counters, the TC outputs can be used with

the CEP and CET inputs in two different ways.

Figure 1 shows the connections for simple ripple carry, in

which the clock period must be longer than the CP to TC

delay of the first stage, plus the cumulative CET to TC

delays of the intermediate stages, plus the CET to CP

setup time of the last stage. This total delay plus setup time

sets the upper limit o n clock frequency. For faster clock

rates, the carry lookahead connecti ons shown in Figure 2

are recommended. In this sch eme the ripple delay th rough

the intermediate stages commences with the same clock

that causes the first stage to tick over from m ax to min in

the Up mode, or m in to m ax in th e Dow n mo de, to start its

final cycle. Since this final cycle takes 16 clocks to complete, there is plenty of time for the ripple to progress

through the intermediate stages. The critical timing that limits the clock period is th e CP to TC d elay of the fir st stage

plus the CEP to CP setup time of the last stage. T he TC

output is subject t o decoding spikes due to intern al race

conditions and is th erefore not recommen ded for u se as a

clock or asynchronous reset for flip-flops, registers or

counters.

Logic Equations: Count Enable = CEP • CET • PE

TC = Q0 • Q1 • Q 2 • Q3 • CET

FIGURE 1.

FIGURE 2.

Pin Names Description

CEP Count Enable Parallel Input

CET Count Enable Trickle Input

CP Clock Pulse Input

MR

Synchronous Master Reset Input

P

0–P3

Parallel Data Inputs

PE

Parallel Enable Inputs

Q

0–Q3

Flip-Flop Outputs

TC Terminal Count Output

3 www.fairchildsemi.com

74VHC163

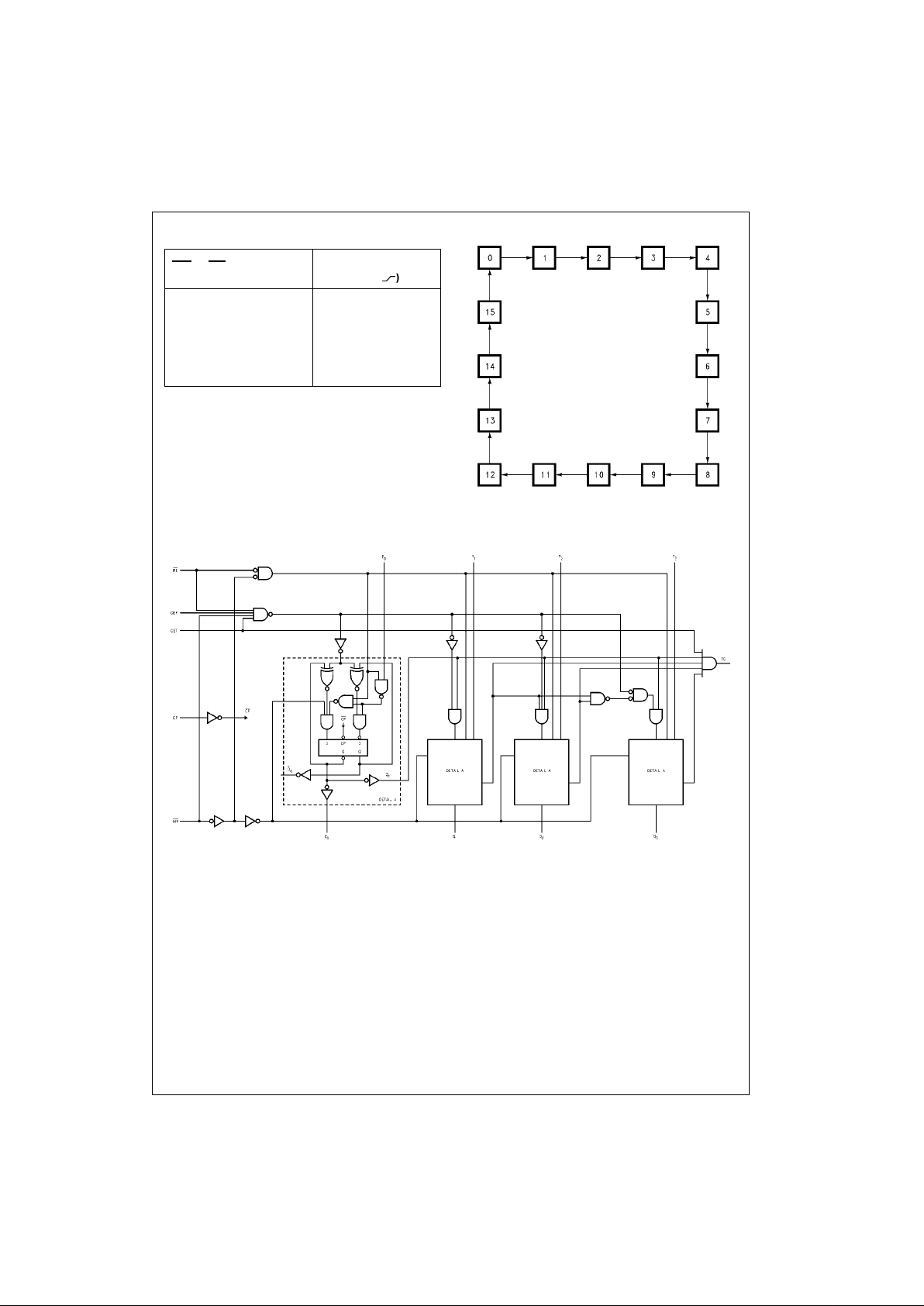

Mode Select Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

State Diagram

Block Diagram

MR PE CET CEP

Action on the Rising

Clock Edge (

)

L X X X Reset (Clear)

H L X X Load (P

n

→ Qn)

H H H H Count (Increment)

H H L X No Change (Hold)

H H X L No Change (Hold)

Loading...

Loading...