Fairchild Semiconductor 74VHC123ASJX, 74VHC123ASJ, 74VHC123AN, 74VHC123AMX, 74VHC123AMTCX Datasheet

...

July 1993

Revised April 1999

74VHC123A Dual Retriggerable Monostable Multivibrator

© 1999 Fairchild Semiconductor Corporation DS011621.prf www.fairchildsemi.com

74VHC123A

Dual Retriggerable Monostable Multivibrator

General Description

The VHC123A is an advanced high speed CMOS

Monostable Multivibrator fabricated with silicon gate CMOS

technology. It achieves the high speed opera tion simil ar to

equivalent Bipolar Schottky TTL while maintaining the

CMOS low power dissipation. Each multivibrator features

both a negative, A, and a po sitive, B, transition triggered

input, either of whi ch can be used as an inhibit in put. Also

included is a clear input that when taken low resets the

one-shot. The VHC123A ca n be triggered on the positive

transition of the clear while A is held low and B is held high.

The output pulse width is determined by the equation:

PW = (R

x

)(Cx); where PW is in seconds, R is in ohms, and

C is in farads.

Limits for R

x

and Cx are:

External capacitor, C

x

No limit

External resistors, R

xVCC

= 2.0V, 5 kΩ min

V

CC

> 3.0V, 1 kΩ min

An input protection circuit ensures that 0 to 7V can be

applied to the inp ut pins with out regard to the sup ply voltage. This device can be used to interface 5V to 3V systems

and two supply systems such as ba ttery back up . This circuit prevents device destruction due to m isma tche d s upp l y

and input voltages.

Features

■ High Speed:

t

PD

= 8.1 ns (typ) at TA = 25°C

■ Low Power Dissipation:

I

CC

= 4 µA (Max) at TA= 25°C

■ Active State: I

CC

= 600 µA (Max) at TA = 25°C

■ High Noise Immunity: V

NIH

= V

NIL

= 28% VCC (min)

■ Power down protection is provided on all inputs

■ Pin and function compatible with 74HC123A

Ordering Code:

Surface mount pack ages are also available on Tape and Reel. Specify by appending the suffix letter “X” to the or dering code.

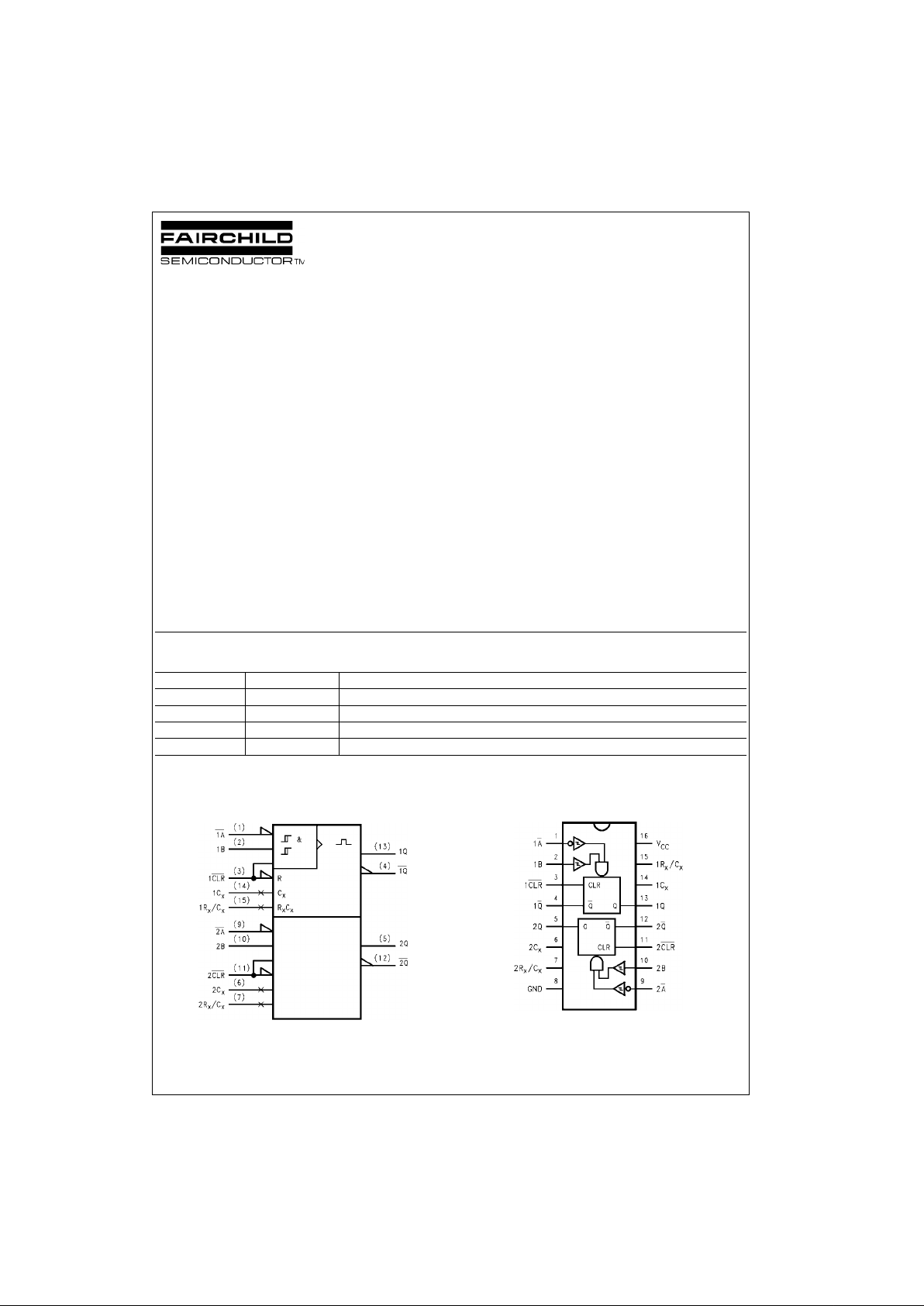

Logic Symbol

IEEE/IEC

Connection Diagram

Order Number Package Number Package Description

74VHC123AM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow

74VHC123ASJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74VHC123AMTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74VHC123AN N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

www.fairchildsemi.com 2

74VHC123A

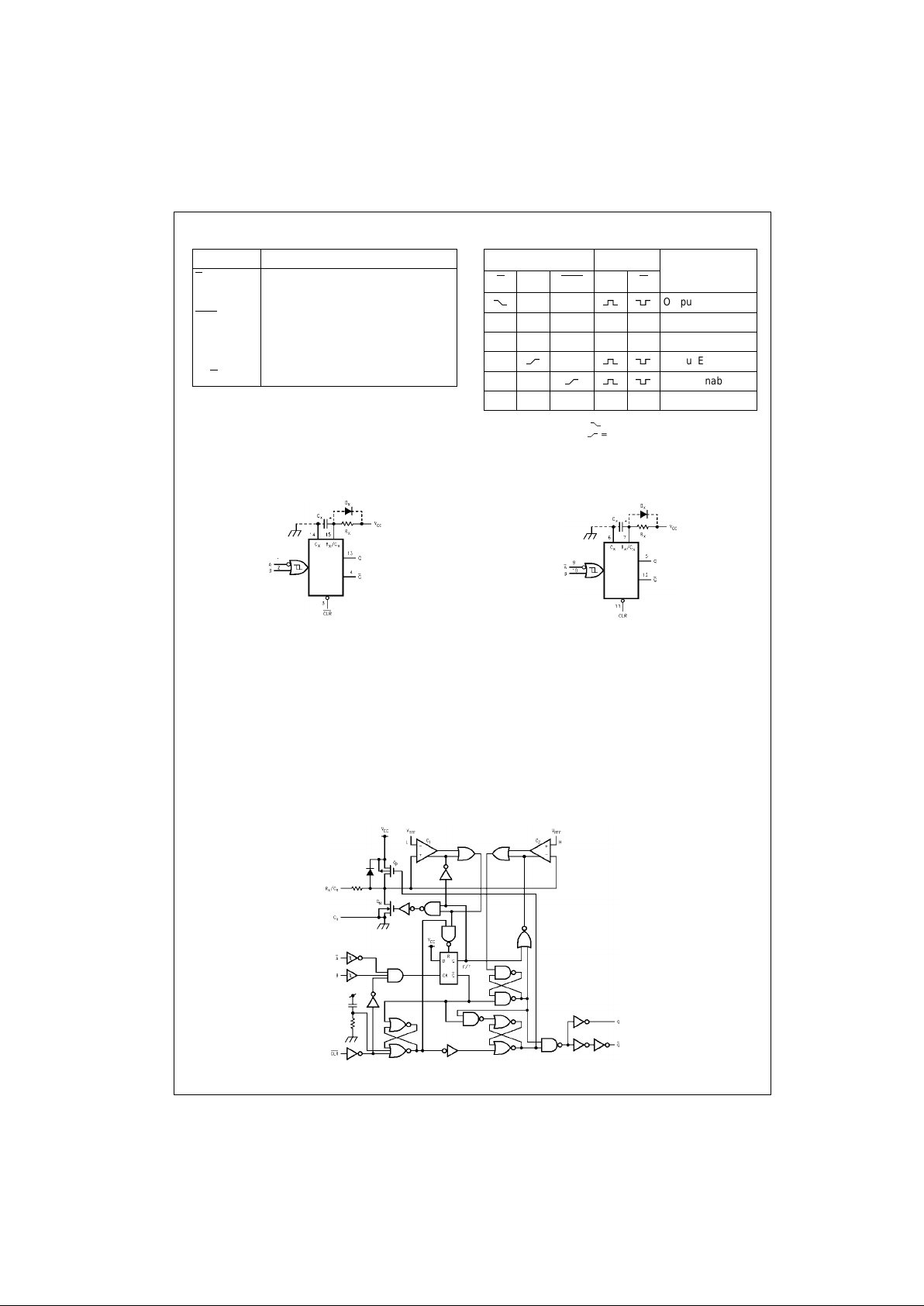

Pin Descriptions Tr uth Table

H = HIGH Voltage Level

= HIGH-to-LOW Tran s iti on

L = LOW Voltage Level

= LOW-to-HIGH Transition

X = Don’t Care

Block Diagrams

Note A: Cx, Rx, Dx are external Capaci to r, Resisto r, and Diode, res pectively.

Note B: External clamping diode, D

x

;

External capacitor is charged to V

CC

level in the wait state, i.e. w hen no trigger is applied.

If the supply voltage is turned off, C

x

discharges mainl y through the int ernal (p arasit ic) diod e. If Cx is sufficiently large a nd VCC drops rapidly, there will be

some possibility o f damag in g the IC throu gh in rus h cu rrent or latch- up . If the ca pac itance of the supp ly volt age fi lter is larg e enough and V

CC

drops slowly,

the in rush current is automatically limite d and damage to the IC is av oided.

The maximum va lue of fo rwar d c urren t t hroug h the par asit ic diode i s ±20 mA. In the case of a large Cx, the limit of fall time of the supply voltage is determined as follows:

t

f

≥ (VCC −0.7) Cx/20 mA

(t

f

is the time between the supply voltage turn off and the supply voltage reaching 0.4 VCC)

In the event a system does not satisfy the above condition, an external clamping diode (D

x

) is needed to protect the IC from rush current.

System Diagram

Pin Names Description

A

Trigger Inputs (Negative Edge)

B Trigger Inputs (Positive Edge)

CLR

Reset Inputs

C

x

External Capacitor

R

x

External Resistor

Q, Q

Outputs

Inputs Outputs Function

A

BCLRQQ

HH

Output Enable

X L H L H Inhibit

H X H L H Inhibit

L

H

Output Enable

LH

Output Enable

XX L LHReset

3 www.fairchildsemi.com

74VHC123A

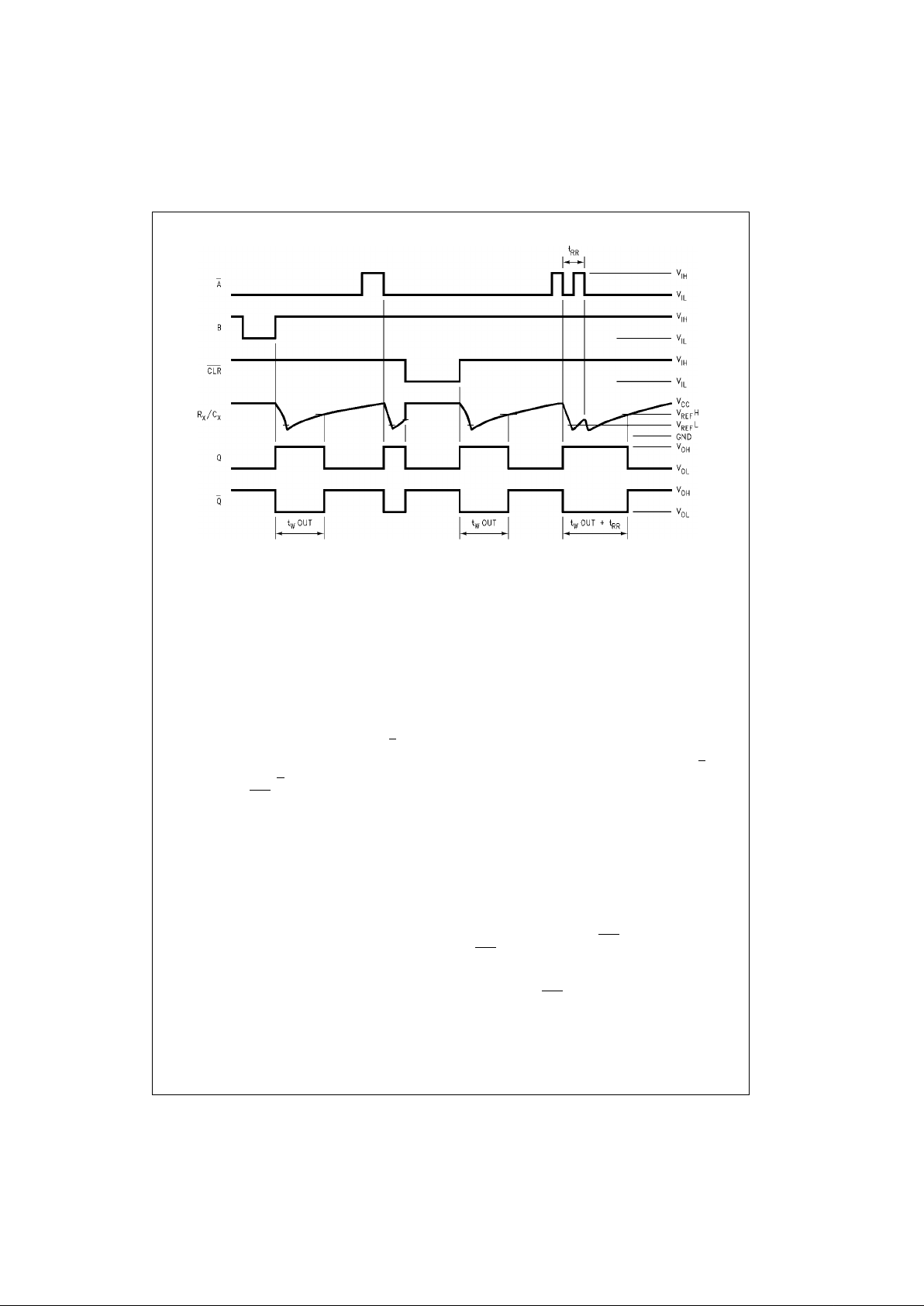

Timing Chart

Functional Description

1. Stand-by State

The external capaci tor (C

x

) is fully charged to V

CC

in

the Stand-by State. That mean s, before trigger ing, the

Q

P

and QN transistors which are connecte d to the Rx/

C

x

node are in the off state. Two comparators that

relate to the timing of the output p ulse, and two r eference voltage supplies turn off. The total supply curre nt

is only leakage current.

2. Trigger Operation

Trigger operation is effective in any of the following

three cases. First, the co ndition where the A

input is

LOW, and B input has a rising signal; second, where

the B input is HIGH, and the A input has a falling signal;

and third, where the A

input is LOW and the B input is

HIGH, and the CLR

input has a rising signal.

After a trigger becomes effecti ve, comparat ors C

1

and

C

2

start operating, and QN is turned on. The external

capacitor discharges thro ugh Q

N

. The voltage level at

the R

x/Cx

node drops. If the Rx/Cx voltage level falls to

the internal referen ce voltage V

ref

L, the output of C

1

becomes LOW. The flip-flop is then reset an d QN turns

off. At that moment C

1

stops but C2 continues operating.

After Q

N

turns off, the voltage at the Rx/Cx node starts

rising at a rate determined by the time constant of

external capacitor C

x

and resistor Rx.

Upon triggering, output Q becomes HIGH, following

some delay time of th e internal F/F and gates. It s tays

HIGH even if the voltage of R

x/Cx

changes from falling

to rising. When R

x/Cx

reaches the internal reference

voltage V

ref

H, the output of C2 becomes LOW, the out-

put Q goes LOW and C

2

stops its operation. That

means, after trigger ing, when the voltage level of the

R

x/Cx

node reaches V

ref

H, the IC returns to its

MONOSTABLE stat e.

With large values of C

x

and Rx, and ignoring the dis-

charge time of the capacitor a nd internal dela ys of the

IC, the width of the outp ut pulse, t

W

(OUT), is as follows:

t

W

(OUT) = 1.0 Cx R

x

3. Retrigger operation (74 V HC12 3A )

When a new trigger is applied to either inpu t A

or B

while in the MONOSTABLE state, it is effective only if

the IC is chargi ng C

x

. The voltage level of the Rx/C

x

node then falls to V

ref

L level again. Therefo re the Q

output stays HIGH if the next tr igger comes in before

the time period set by C

x

and Rx.

If the new trigger is very close to a previous trigger,

such as an occurrence during th e discharge cycle, it

will have no effect.

The minimum time for a tr igge r to be effecti ve 2nd trigger, t

RR

(Min), depends on VCC and Cx.

4. Reset Operation

In normal operation, the CLR

input is held HIGH. If

CLR

is LOW, a trigger has no affect because the Q output is held LOW and the tri gger control F/F is reset.

Also, Q

p

turns on and Cx is charged rapidly to VCC.

This means if CLR

is set LOW, the IC goes into a wait

state.

Loading...

Loading...