Fairchild Semiconductor 74VHC112SJX, 74VHC112SJ, 74VHC112N, 74VHC112MX, 74VHC112MTCX Datasheet

...

September 1995

Revised April 1999

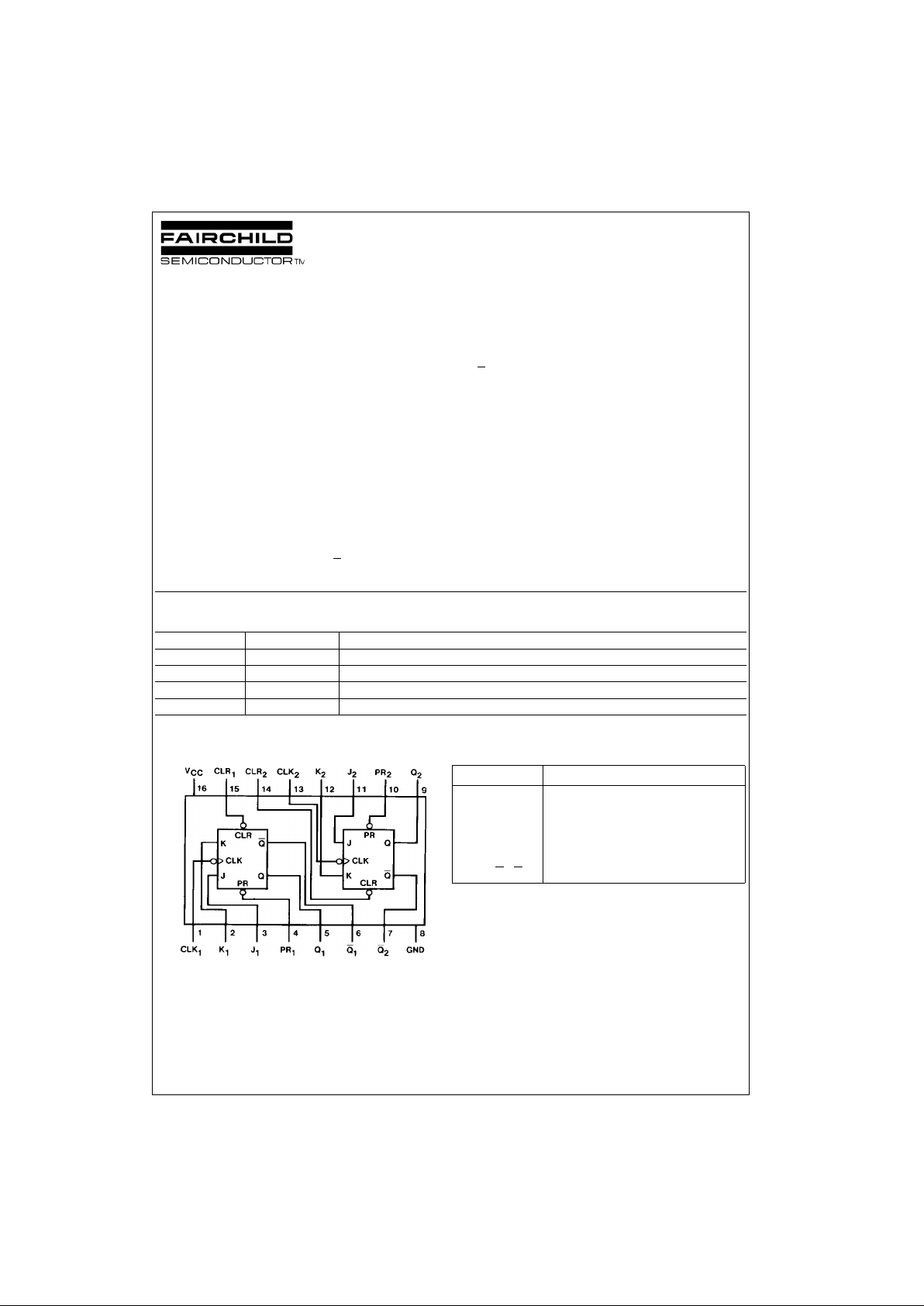

74VHC112 Dual J-K Flip-Flops with Preset and Clear

© 1999 Fairchild Semiconductor Corporation DS012123.prf www.fairchildsemi.com

74VHC112

Dual J-K Flip-Flops with Preset and Clear

General Description

The VHC112 is an advanced high speed CMOS device

fabricated with silicon gate CMOS technology. It achieves

the high-speed operation similar to equivalent Bipolar

Schottky TTL while maintaining the CMOS low power dissipation.

The VHC112 contains two independent, high-speed JK flipflops with Direct Set an d Clear inputs. Synchro nous state

changes are initiated by the falling edge of the clock. Triggering occurs at a voltage level of the clock and is not

directly related to transi tion time. The J and K inputs can

change when the clock is in either state wit hout affecting

the flip-flop, provided tha t th ey ar e in the desir ed state during the recommended s etup and hold tim es relative to the

falling edge of the clock. The LOW signal o n PR or CLR

prevents clocking and forces Q and Q

HIGH, respectively.

Simultaneous LOW signal s on PR and CLR force both Q

and Q

HIGH.

An input protection circuit ensures that 0V to 7V can be

applied to the inp ut pins with out regard to the sup ply voltage. This device can be used to interface 5V to 3V systems

and two supply systems such as battery backup. Th is circuit prevents device destruction due to m ismatched supply

and input voltages.

Features

■ High speed: f

MAX

= 200 MHz (typ) at VCC = 5.0V

■ Low power dissipation: I

CC

= 2 µA (max) at TA = 25°C

■ High noise immunity: V

NIH

= V

NIL

= 28% VCC (min)

■ Power down protection is provided on all inputs

■ Pin and function compatible with 74HC112

Ordering Code:

Surface mount pack ages are also available on Tape and Reel. Specify by appending the s uffix let te r “X” to the ordering code .

Connection Diagram Pin Descriptions

Order Number Package Number Package Description

74VHC112M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74VHC112SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74VHC112MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74VHC112N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Pin Names Description

J

1

, J2, K1, K

2

Data Inputs

CLK

1

, CLK

2

Clock Pulse Inputs (Active Falling Edge)

CLR

1

, CLR

2

Direct Clear Inputs (Active LOW)

PR

1

, PR

2

Direct Preset Inputs (Active LOW)

Q

1

, Q2, Q1, Q2Outputs

www.fairchildsemi.com 2

74VHC112

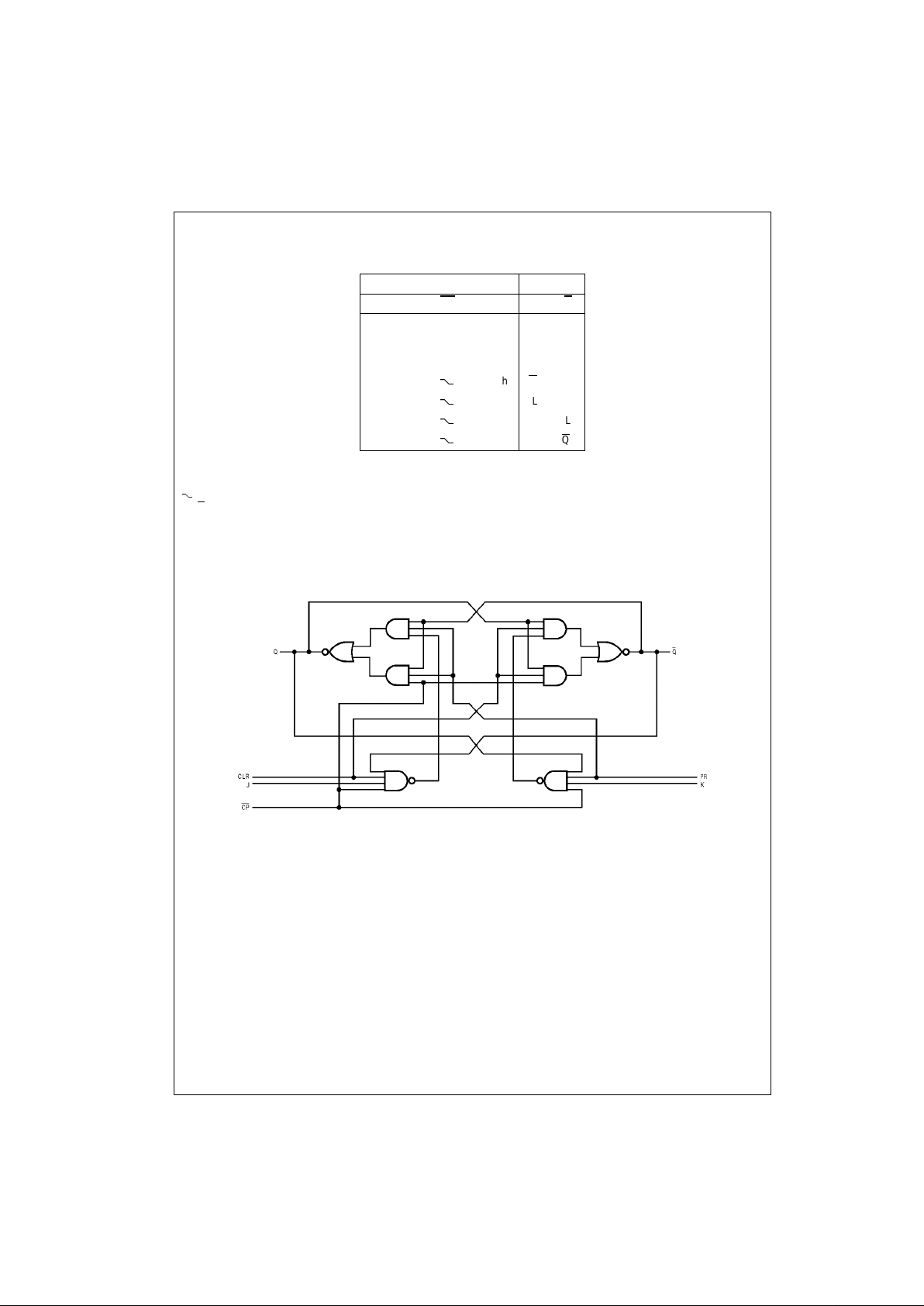

Truth Table

H (h) = HIGH Voltage Level

L (l) = LOW Voltage Level

X = Immaterial

= HIGH-to-LOW C loc k Transit ion

Q

0

(Q0) = Before HIGH-to-LOW Transition of Clock

Lower case letters indicate the state of the ref erenced input or output one setup time prior to the H I GH-to-LOW clock trans it io n.

Logic Diagram

(One Half Shown)

Inputs Outputs

PR CLR CP

JKQ Q

LHXXXHL

HLXXXLH

LLXXXHH

HH

hhQ0Q

0

HH

lhL H

HH

hlH L

HH

llQ0Q

0

3 www.fairchildsemi.com

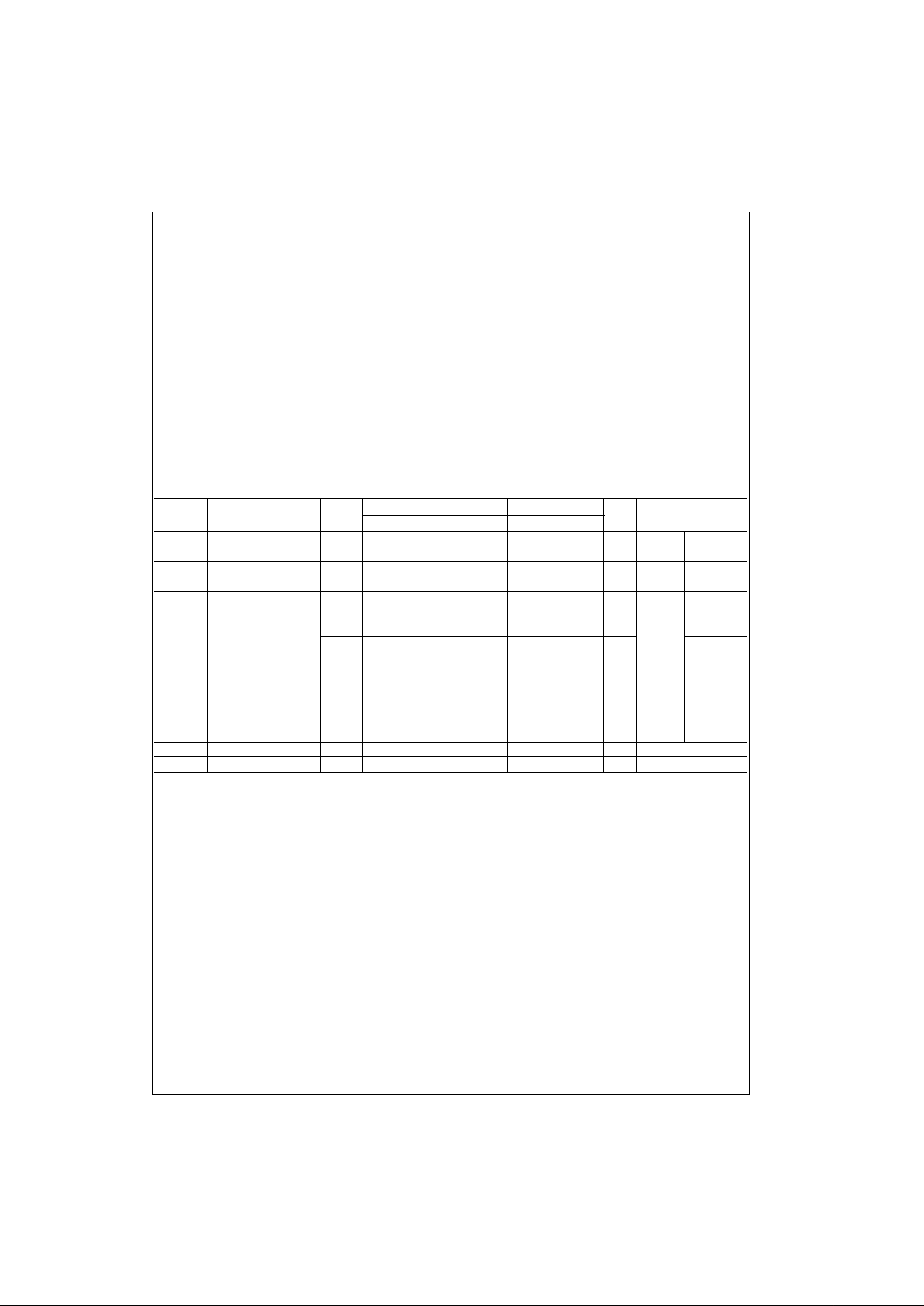

74VHC112

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

(Note 2)

Note 1: Absolute Maximum Ratings are valu es beyond whic h the device

may be damaged or ha ve its useful life impaire d. The datab ook specifications should be met, without exception, to ensure that the system design is

reliable over its p ower supp ly, temperature, and o utput/input loading variables. Fairchild does not recommend operation outside databook specifications.

Note 2: Unused inputs must be held HIGH or LOW. They may not float.

DC Electrical Characteristics

Supply Voltage (VCC) −0.5V to +7.0V

DC Input Voltage (V

IN

) −0.5V to +7.0V

DC Output Voltage (V

OUT

) −0.5V to VCC + 0.5V

Input Diode Current (I

IK

) −20 mA

Output Diode Current (I

OK

) ±20 mA

DC Output Current (I

OUT

) ±25 mA

DC V

CC

/GND Current (ICC) ±50 mA

Storage Temperature (T

STG

) −65°C to +150°C

Lead Temperature (T

L

)

(Solderi ng, 10 seconds) 260°C

Supply Voltage (V

CC

) 2.0V to +5.5V

Input Voltage (V

IN

) 0V to +5.5V

Output Voltage (V

OUT

) 0V to V

CC

Operating Temperature (T

OPR

) −40°C to +85°C

Input Rise and Fall Time (t

r

, tf)

V

CC

= 3.3V ± 0.3V 0 ∼ 100 ns/V

V

CC

= 5.0V ± 0.5V 0 ∼ 20 ns/V

Symbol Parameter

V

CC

(V)

TA = 25°C T

A

= −40°C to +85°C

Units Conditions

Min Typ Max Min Max

V

IH

HIGH Level 2.0 1.50 1.50

V

Input Voltage 3.0 − 5.5 0.7 V

CC

0.7 V

CC

V

IL

LOW Level 2.0 0.50 0.50

V

Input Voltage 3.0 − 5.5 0.3 V

CC

0.3 V

CC

V

OH

HIGH Level 2.0 1.9 2.0 1.9 VIN = VIH IOH = −50 µA

Output Voltage 3.0 2.9 3.0 2.9 V or V

IL

4.5 4.4 4.5 4.4

3.0 2.58 2.48

V

IOH = −4 mA

4.5 3.94 3.80 IOH = −8 mA

V

OL

LOW Level 2.0 0.0 0.1 0.1 VIN = VIH IOL = 50 µA

Output Voltage 3.0 0.0 0.1 0.1 V or V

IL

4.5 0.0 0.1 0.1

3.0 0.36 0.44

V

IOL = 4 mA

4.5 0.36 0.44 IOL = 8 mA

I

IN

Input Leakage Current 0 − 5.5 ±0.1 ±1.0 µA VIN = 5.5V or GND

I

CC

Quiescent Supply Current 5.5 2.0 20.0 µA VIN = VCC or GND

Loading...

Loading...