Fairchild Semiconductor 74VCXH162373MTX, 74VCXH162373MTD Datasheet

January 2000

Revised March 2000

74VCXH162373

Low Voltage 16-Bit Transparent Latch with Bushold

and 26Ω Series Resistors in Outputs

74VCXH162373 Low Voltage 16-Bit Transparent Latch with Bushold

General Description

The VCXH162373 contains sixteen non-inverting latches

with 3-STATE outputs and is intended for bus oriented

applications. The device is byte control led. The flip-flops

appear to be transparent to the data when the Latch enable

(LE) is HIGH. When LE is LOW, the data that meet s the

setup time is latched. Data appea rs on the bus when the

Output Enable (OE

puts are in a high impedance state.

The VCXH162373 data inputs include activ e bushold circuitry, eliminating the need for external pull-up resistors to

hold unused or floating data inputs at a valid logic level.

The VCXH162373 is also de signed with 26Ω series resistors in the outputs. This design reduces line noise in applications such as memory addres s driver, clock drivers and

bus transceivers/transmitters.

The 74VCXH16237 3 is desig ned for lo w voltage (1.65V to

3.6V) V

CC

The 74VCXH162373 is fabricated with an advanced CMOS

technology to achieve high speed operation while maintaining low CMOS power dissipation.

) is LOW. When OE is HIGH, the out-

applications with output compatibility up to 3.6V.

Ordering Code:

Ordering Number

74VCXH162373MTD

74VCXH162373MTX

(Note 1)

Note 1: Use this Order Nu m ber to receive devices in Tape and Reel.

Package

Number

MTD48

MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

[TUBES]

[TAPE a nd REEL]

Features

■ 1.65V–3.6V VCC supply operation

■ 3.6V tolerant control inputs and outputs

■ Bushold on data inputs eliminates the need for external

pull-up/pull-down resistors

■ 26Ω series resistors in outputs

(In to On)

■ t

PD

3.3 ns max for 3.0V to 3.6V V

4.5 ns max for 2.3V to 2.7V V

9.0 ns max for 1.65V to 1.95V V

■ Static Drive (IOH/IOL)

±12 mA @ 3.0V V

±8 mA @ 2.3V V

±3 mA @ 1.65V V

■ Uses patented noise/EMI reduction circuitry

■ Latch-up performance exce eds 300 mA

■ ESD performance:

Human body model > 2000V

Machine model > 200V

Package Description

CC

CC

CC

CC

CC

CC

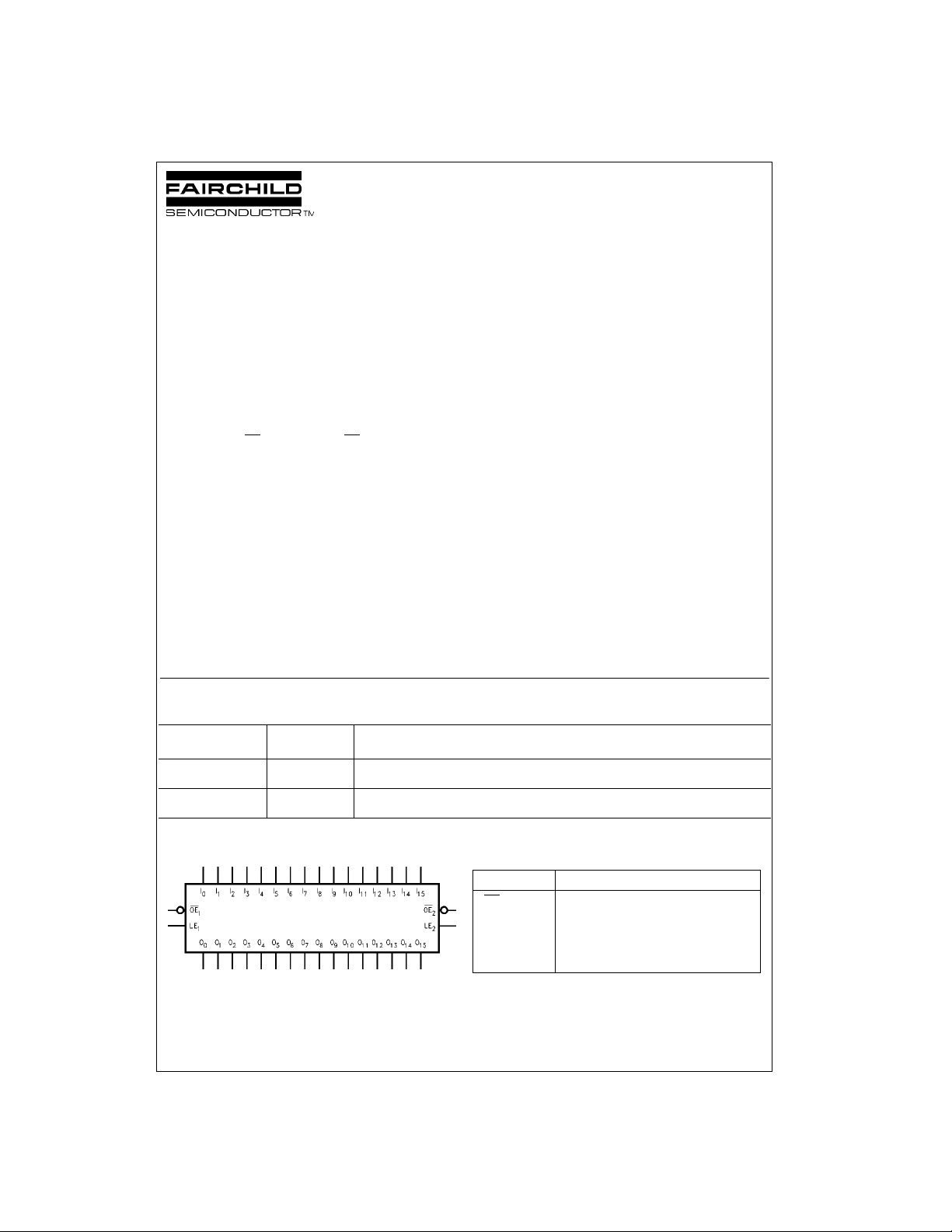

Logic Symbol Pin Descriptions

Pin Names Description

OE

n

LE

n

I

0–I15

O

0–O15

© 2000 Fairchild Semiconductor Corporation DS500227 www.fairchildsemi.com

Output Enable Input (Active LOW)

Latch En able Input

Bushold Inputs

Outputs

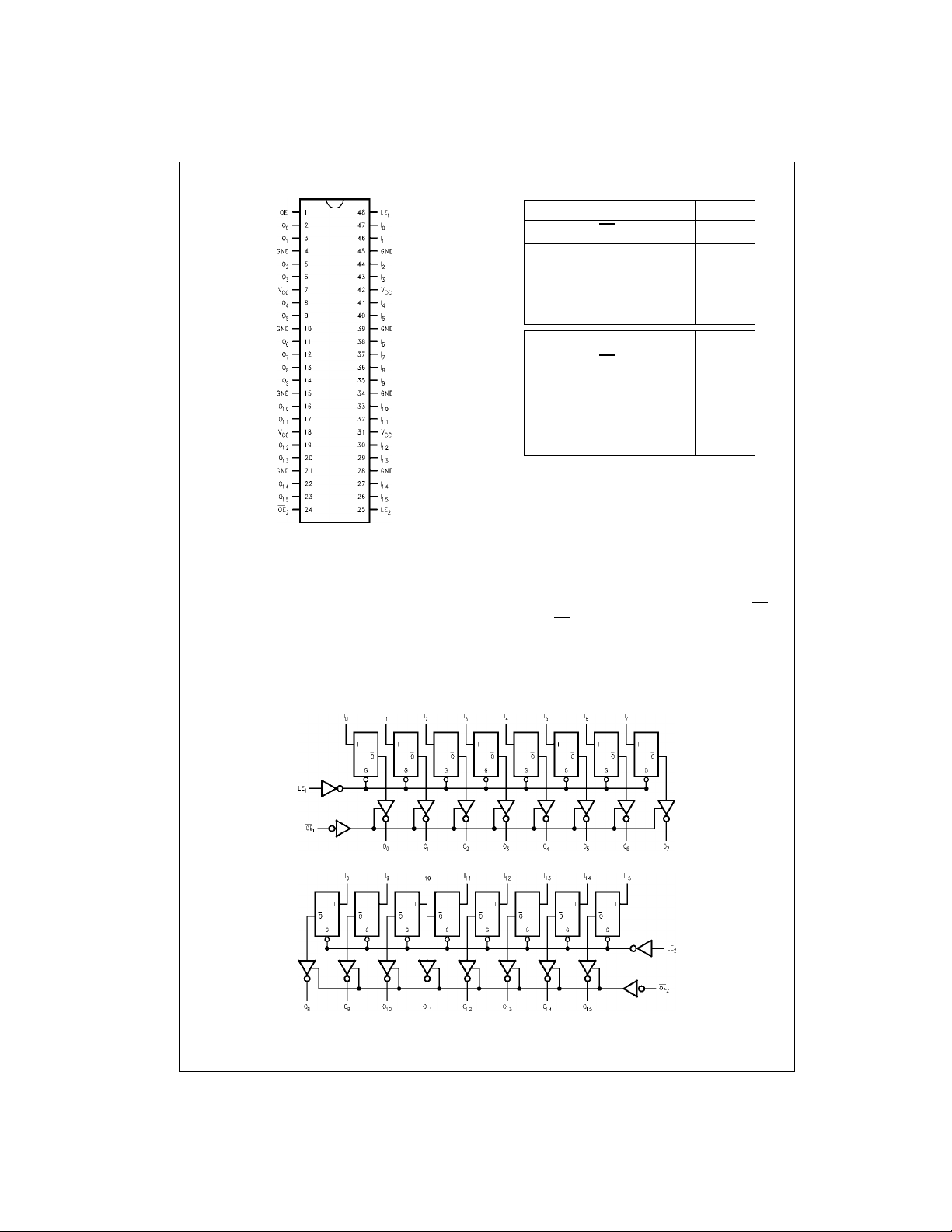

Connection Diagram Truth Tables

74VCXH162373

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial (HIG H or LOW, control inputs may not float )

Z = High Impedance

= Previous O0 before HIGH-to-LOW of Latch Enable

O

0

Functional Description

The 74VCXH162373 contains sixteen edge D-type latches

with 3-STATE outputs. The device is byte controlled with

each byte functioning identically, but independent of the

other. Control pins can be shorted together to obtai n full

16-bit operation. The following description applies to each

byte. When the Latch E nable (LE

enters the latches. In this conditio n the latches are

the I

n

) input is HIGH, data on

n

transparent, i.e., a latc h output will chang e state ea ch tim e

its I input changes. When LE

information that was pr esent on the I inputs a set up time

preceding the HIGH-to-LOW transition on LE

STATE outputs are controlled by the Output Enable (OE

input. When OE

state mode. When OE

in the high impedance mode but this does not interfere with

entering new data into the latches.

Inputs Outputs

LE

OE

1

I0–I

1

O0–O

7

7

XHXZ

HLL L

HLHH

LLXO

0

Inputs Outputs

LE

OE

2

I8–I

2

O8–O

15

15

XHXZ

HLL L

HLHH

LLXO

is LOW, the latches store

n

is LOW the standard outputs are in the 2-

n

is HIGH, the standard outputs a re

n

0

. The 3-

n

)

n

Logic Diagram

Please note that this diagram is provided o nly f or t he understanding of lo gic operations and shou ld not be used to estimate propagation delays.

www.fairchildsemi.com 2

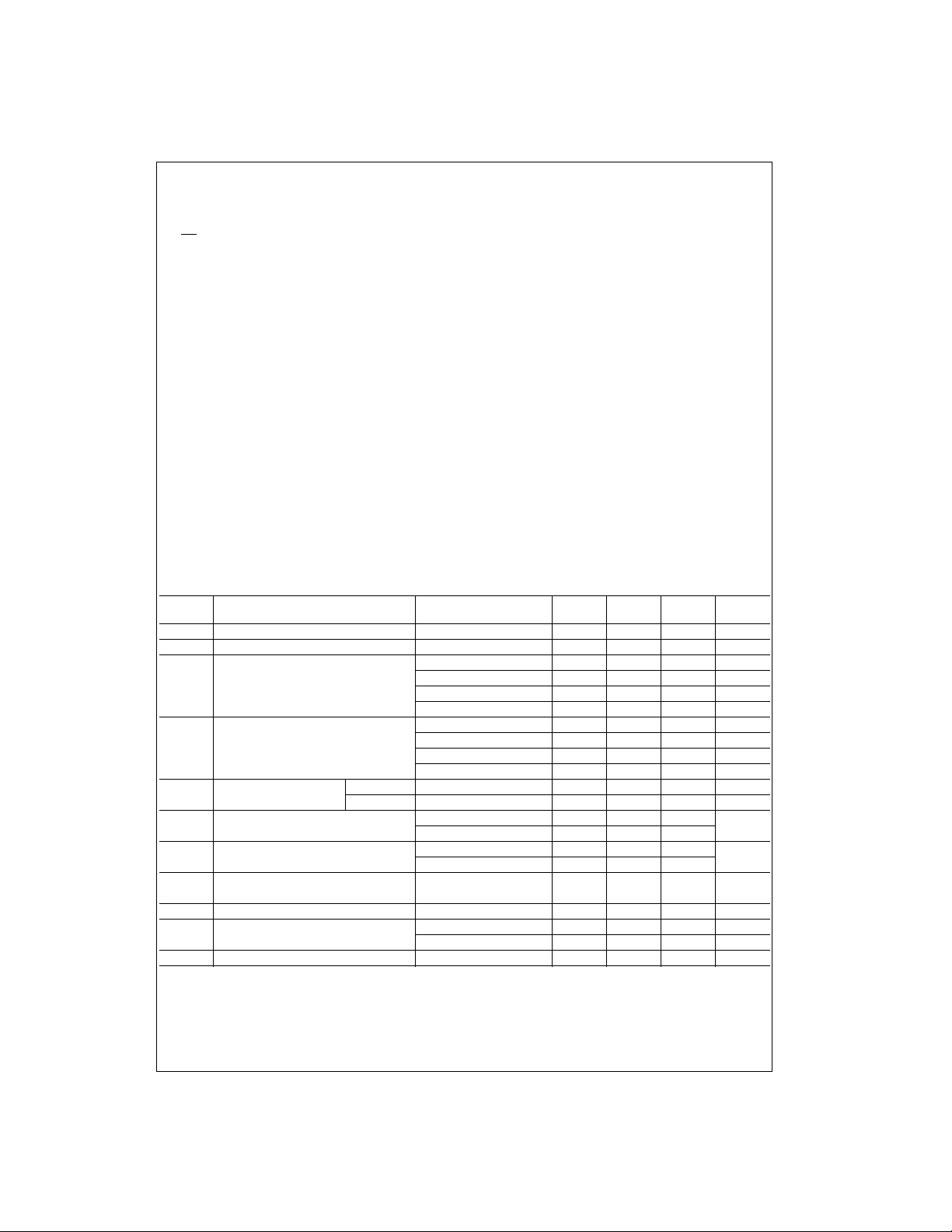

Absolute Maximum Ratings(Note 2) Recommended Operating

Supply Voltage (VCC) −0.5V to +4.6V

DC Input Voltage (V

, LE

OE

n

n

– I

I

0

15

Output Voltage (V

)

I

−0.5V to 4.6V

−0.5V to VCC + 0.5V

)

O

Outputs 3-STATED −0.5V to +4.6V

Outputs Active (Note 3) −0.5V to V

DC Input Diode Current (I

< 0V −50 mA

V

I

DC Output Diode Current (I

< 0V −50 mA

V

O

> V

V

O

CC

)

IK

)

OK

+0.5V

CC

+50 mA

DC Output Source/Sink Current

) ±50 mA

(I

OH/IOL

or GND Current per

DC V

CC

Supply Pin (I

Storage Temperature Range (T

or GND) ±100 mA

CC

) −65°C to +150°C

STG

Conditions

Power Supply

Operating 1.65V to 3.6V

Data Retention Only 1.2V to 3.6V

Input Voltage −0.3V to V

Output Voltage (VO)

Output in Active States 0V to V

Output in “OFF” State 0.0V to 3.6V

Output Current in I

VCC = 3.0V to 3.6V ±12 mA

= 2.3V to 2.7V ±8 mA

V

CC

= 1.65V to 2.3V ±3 mA

V

CC

Free Air Operating Temperature (T

Minimum Input Edge Rate (∆t/∆V)

= 0.8V to 2.0V, VCC = 3.0V 10 ns/V

V

IN

Note 2: The Absolute Maximum Ratings are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the Absolute Maximum Rat-

ings. The “Recommended Operating Conditions” table will define the conditions for actual device operation.

Absolute Maximum Rating must be observed.

Note 3: I

O

Note 4: Floating or unused control inputs must be held HIG H or LOW.

(Note 4)

OH/IOL

) −40°C to +85°C

A

DC Electrical Characteristics (2.7V < VCC ≤ 3.6V)

V

Symbol Parameter Conditions

V

IH

V

IL

V

OH

V

OL

I

I

I

I(HOLD)

I

I(OD)

I

OZ

I

OFF

I

CC

∆I

Note 5: An external driver must source at least the specified current to switch from LOW-to-HIGH.

Note 6: An external dri ve r m us t s ink at least the specified cur rent to switch from HIGH -t o-LOW.

Note 7: Outputs disab led or 3-STATE only.

HIGH Level Input Voltage 2.7–3.6 2.0 V

LOW Level Input Voltage 2.7–3.6 0.8 V

HIGH Level Output Voltage IOH = −100 µA 2.7–3.6 VCC − 0.2 V

LOW Level Output Voltage IOL = 100 µA 2.7–3.6 0.2 V

Input Leakage Current Control Pins 0 ≤ VI ≤ 3.6V 2.7–3.6 ±5.0 µA

Bushold Input Minimum VIN = 0.8V 3.0 75

Drive Hold Current VIN = 2.0V 3.0 −75

Bushold Input Over-Drive (Note 5) 3.6 450

Current to Change State (Note 6) 3.6 −450

3-STATE Output Leakage 0 ≤ VO ≤ 3.6V

Power-OFF Leakage Current 0 ≤ (VO) ≤ 3.6V 0 10 µA

Quiescent Supply Current VI = VCC or GND 2.7–3.6 20 µA

Increase in ICC per Input VIH = VCC −0.6V 2.7–3.6 750 µA

CC

Data Pins VI = VCC or GND 2.7–3.6 ±5.0 µA

IOH = −6 mA 2.7 2.2 V

IOH = −8 mA 3.0 2.4 V

IOH = −12 mA 3.0 2.2 V

IOL = 6 mA 2.7 0.4 V

IOL = 8 mA 3.0 0.55 V

IOL = 12 mA 3.0 0.8 V

VI = VIH or V

VCC ≤ (VO) ≤ 3.6V (Note 7) 2.7–3.6 ±20 µA

IL

CC

(V)

2.7–3.6 ±10 µA

Min Max Units

74VCXH162373

CC

CC

µA

µA

3 www.fairchildsemi.com

Loading...

Loading...