Fairchild Semiconductor 74VCX163245MTDX, 74VCX163245MTD Datasheet

March 2000

Revised March 2000

74VCX163245

Low Voltage 16-Bit Dual Supply Translating Transceiver

with 3-STATE Outputs

74VCX163245 Low Voltage 16-Bit Dual Supply Translating Transceiver with 3-ST ATE Outputs

General Description

The VCX163245 is a dual supply, 16-bit translating transceiver that is designed for 2 way asynchr onous communication between busses at different supply voltages by

providing true sign al tr ans lati on . T he sup ply r ai ls co nsi st of

, which is a higher po tential rail operating at 2.3 to

V

CCA

3.6V and V

1.65 to 2.7V. (V

proper device opera tion). This dual supply design allows

for translation from 1.8V to 2.5V busses to busses at a

higher potential, up to 3.3V.

The Transmit/Receive (T/R

of data flow. Transmit (active-HIGH) enables data from A

Ports to B Ports; Re ceive (activ e-LOW) en ables data from

B Ports to A Ports. The Ou tput Enable (OE

HIGH, disables both A and B Ports by placing them in a

High-Z cond i t io n. Th e A P ort i nt er fa c es wi t h th e higher voltage bus (2.7 − 3.3V); The B Port interfaces with the lower

voltage bus (1.8 − 2.5V). Also the VCX16 3245 is de sign ed

so that the control pins (T/R

The 74VCX163245 is suit able for mixed voltage applications such as notebook compute rs using a 1.8V CPU and

3.3V peripheral components. It is fabricated with an

Advanced CMOS technology to achieve high speed operation while maintaining low CMOS power dissipation.

, which is the lower potential rail operating at

CCB

must be less than or equal to V

CCB

) input determines the direct ion

) input, when

, OEn) are supplied by V

n

CCA

CCB

Features

■ Bidirectional interface between busses ranging from

1.65V to 3.6V

■ Supports Live Insertion and Withdrawal (Note 1)

■ Static Drive (I

±24 mA @ 3.0V V

for

.

±18 mA @ 2.3V V

±6 mA @ 1.65V V

■ Uses patented Quiet Series noise/EMI reduction cir-

cuitry

■ Functionally compatible with 74 series 16245

■ Latchup performance exceeds 300 mA

■ ESD performance:

Human Body Model >2000V

Machine model >200V

Note 1: To ensure the h igh impedance state during power up or power

should be tie d t o V

down, OE

n

value of the res istor is dete rmin ed by the curr ent sou rcing ca pabilit y o f the

driver.

OH/IOL

)

CC

CC

CC

through a pull up resistor. The minimum

CCB

Ordering Code:

Order Number Package Number Package Description

74VCX163245MTD MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Device also available in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

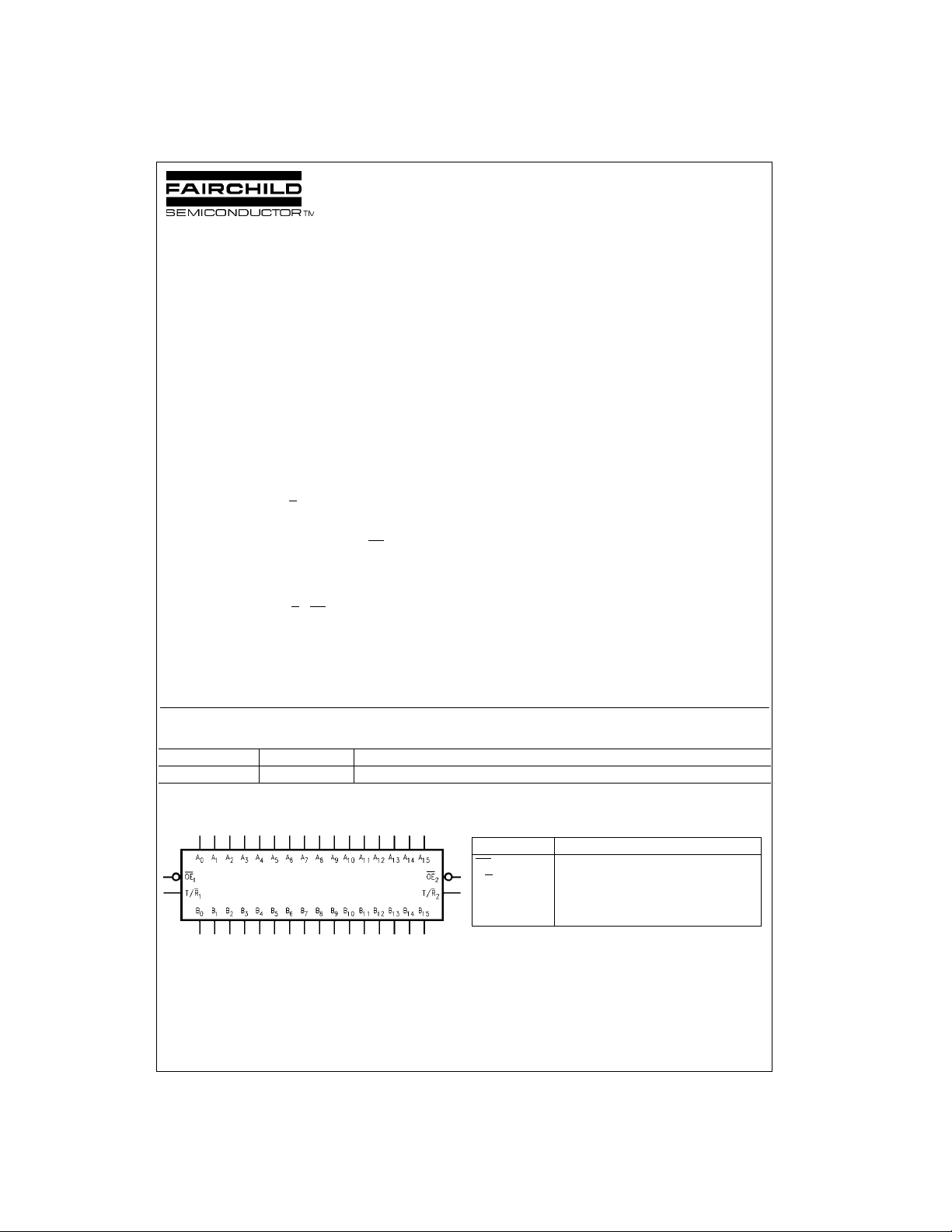

Logic Diagram Pin Descriptions

Pin Names Description

OE

n

T/R

n

A

0–A15

B

0–B15

Quiet Series is a trademark of Fairchild Semiconductor Corporation.

© 2000 Fairchild Semiconductor Corporation ds500168 www.fairchildsemi.com

Output Enable Input (Active LOW)

Transmit/Receive Input

Side A Inputs or 3-STATE Outputs

Side B Inputs or 3-STATE Outputs

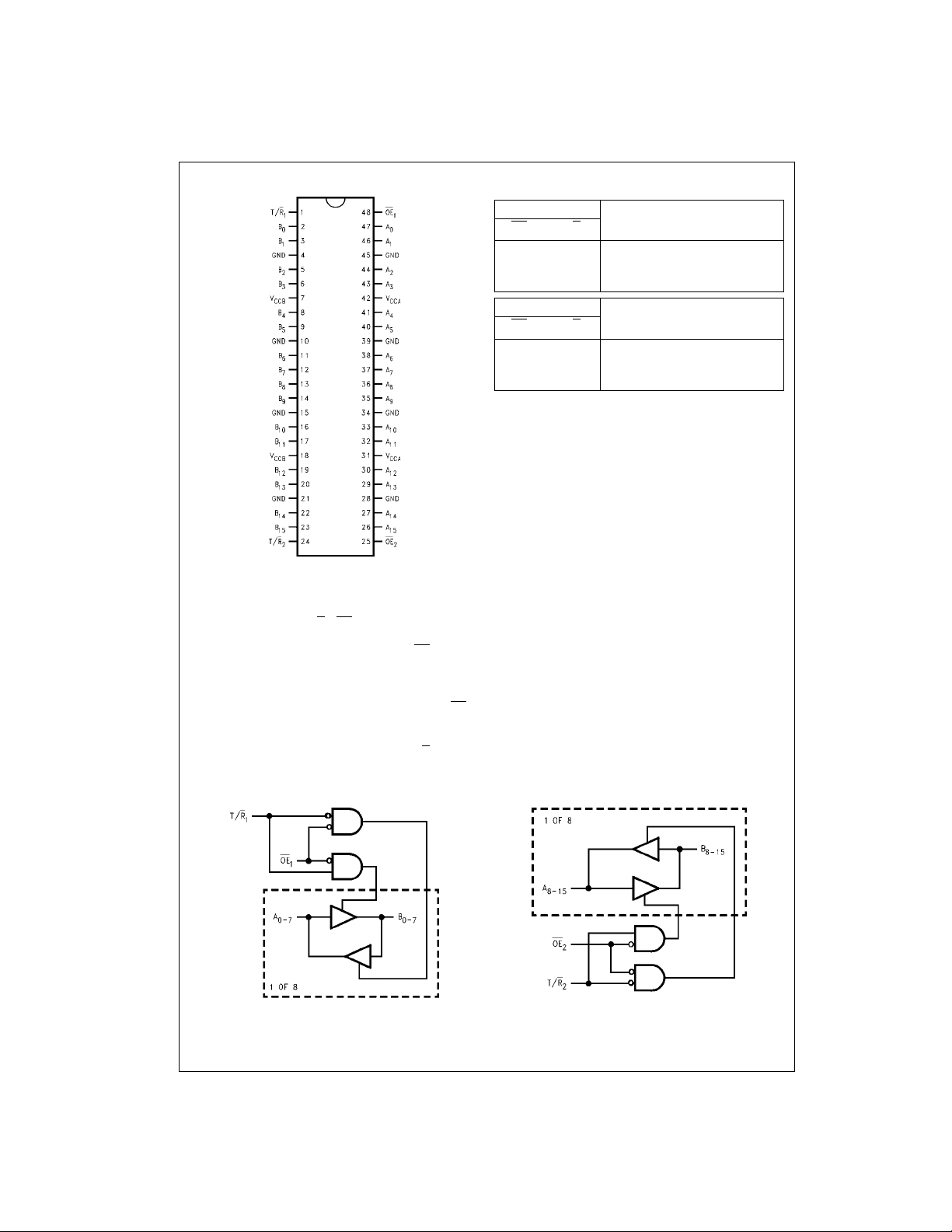

Connection Diagram Truth T ables

Inputs

OE

T/R

1

1

L L Bus B0–B7 Data to Bus A0–A

74VCX163245

L H Bus A0–A7 Data to Bus B0–B

H X HIGH Z State on A0–A7, B0–B

Inputs

OE

T/R

2

2

L L Bus B8–B15 Data to Bus A8–A

L H Bus A8–A15 Data to Bus B8–B

H X HIGH-Z State on A8–A15, B8–B

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial (HIGH or LOW, inputs may not float)

Z = High Impedance

VCX163245 Translator Power Up Sequence Recommendations

To guard against power up problems, some simple guidelines need to b e adhered t o. The VCX16 3245 is de signed

so that the cont rol pin s (T/R

, OEn) are supplied by V

n

Therefore the first recommendation is to begin by powering

up the control side of the device, V

pins should be ramped with or ahead of V

. The OEn control

CCB

CCB

, this will

guard against bus contentions and oscillations as all A Port

and B Port outputs will be disabled. To ensure the high

impedance state during power up or power down, OE

should be tied to V

through a pull up resisto r. The mini-

CCB

mum value of the resistor is determined by the current

sourcing capability of the driver. Second, the T/R

control

n

pins should be placed at logic LOW (0V) level, this will

ensure that the B-sid e b us pi ns are co nfig ure d a s in put s to

help guard against bus conten tion and oscillation s. B-side

.

CCB

Data Inputs should be driven to a valid lo gic level (0V or

V

), this will prevent excessive current draw and oscilla-

CCB

tions. V

V

CCA

proper device oper ation. Upon completion of the se steps

the device can then be config ured for the users desired

n

operation. Following these steps will help to p revent possi-

can then be pow ered up after V

CCA

must be greater than or equal to V

ble damage to the translator device as well as other system

components.

Outputs

Outputs

CCB

to ensure

CCB

7

7

7

15

15

15

, however

Logic Diagrams

Please note that these diagrams are pro v ided only for the underst anding of logic operations and should not be use d to es t im at e propagation delays.

www.fairchildsemi.com 2

Absolute Maximum Ratings(Note 2) Recommended Operating

Supply Voltage

V

CCA

V

CCB

−0.5V to +4.6V

−0.5V to V

CCA

DC Input Voltage (VI) −0.5V to +4.6V

DC Output Voltage (V

)

I/O

Outputs 3-STATE −0.5V to +4.6V

Outputs Active (Note 3)

A

n

B

n

DC Input Diode Current (I

< 0V −50 mA

V

I

DC Output Diode Current (I

< 0V −50 mA

V

O

> V

V

O

CC

)

IK

OK

−0.5V to V

−0.5V to V

)

CCA

CCB

+50 mA

+ 0.5V

+ 0.5V

DC Output Source/Sink Current

) ±50 mA

(I

OH/IOL

or Ground Current ±100 mA

DC V

CC

Supply Pin (I

Storage Temperature (T

or Ground)

CC

) −65°C to +150°C

STG

Conditions

Power Supply (Note 5)

V

CCA

V

CCB

Input Voltage (V

Input/Output Voltage (V

A

n

B

n

Output Current in IOH/I

V

= 3.0V to 3.6V ±24 mA

CCA

= 2.3V to 2.7V ±18 mA

V

CCA

= 2.3V to 2.7V ±18 mA

V

CCB

= 1.65V to 1.95V ±6 mA

V

CCB

Free Air Operating Temperature (T

Minimum Input Edge Rate (∆t/∆V)

= 0.8V to 2.0V, VCC = 3.0V 10 ns/V

V

IN

Note 2: The “Absolute Maximum Ratings ” are those val ues beyond w hich

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommend ed O peratin g Cond itions” t able w ill defin e the condit ions

for actual device operation.

Absolute Maximum Rating must be observed.

Note 3: I

O

Note 4: Unused inputs or I/O pin s mu st be held H IGH or L OW. They ma y

not float.

Note 5: Operation requires: V

(Note 4)

) @ OE, T/R 0V to V

I

OL

CCB

)

I/O

A

≤ V

CCA

2.3V to 3.6V

1.65V to 2.7V

CCB

0V to V

CCA

0V to V

CCB

−40°C to +85°C

74VCX163245

DC Electrical Characteristics (1.65V < V

Symbol Parameter Conditions

V

V

V

V

V

V

V

V

I

I

I

I

∆I

IHA

IHB

ILA

ILB

OHA

OHB

OLA

OLB

I

OZ

OFF

CCA/ICCB

CC

HIGH Level Input Voltage A

LOW Level Input Voltage A

HIGH Level Output Voltage IOH = −100 µA 1.65–1.95 2.3–2.7 V

HIGH Level Output Voltage IOH = −100 µA 1.65–1.95 2.3–2.7 V

Low Level Output Voltage IOL = 100 µA 1.65–1.95 2.3–2.7 0.2

Low Level Output Voltage IOL = 100 µA 1.65–1.95 2.3–2.7 0.2

Input Leakage Current @ OE, T/R 0V ≤ VI ≤ 3.6V 1.65–1.95 2.3–2.7 ±5.0 µA

3-STATE Output Leakage 0V ≤ VO ≤ 3.6V

Power Off Leakage Current 0≤ (VI, VO) ≤ 3.6V 0 0 10 µA

Quiescent Supply Current, An = V

per supply, V

Increase in ICC per Input, Bn, T/R, OE VI = V

Increase in ICC per Input, A

CCA

/ V

n

Bn, T/R, OE 1.65–1.95 2.3–2.7 0.65 x V

n

Bn, T/R, OE 1.65–1.95 2.3–2.7 0.35 x V

IOH = −18 mA 1.65 2.3–2.7 1.7

IOH = −6 mA 1.65–1.95 2.3 1.25

IOL = 18 mA 1.65 2.3–2.7 0.6

IOL = 6 mA 1.65–1.95 2.3 0.3

CCB

CCB

VI = VIH or V

Bn, OE, & T/R = V

V

V

n

VI = V

IL

or GND

CCA

≤ An ≤ 3.6V

CCA

≤ Bn, OE, T/R ≤ 3.6V

CCB

CCB

CCA

CCB

– 0.6V 1.65–1.95 2.3–2.7 750 µA

– 0.6V 1.65–1.95 2.3–2.7 750 µA

≤ 1.95V, 2.3V < V

CCB

V

CCB

(V) (V)

1.65–1.95 2.3–2.7 1.6 V

1.65–1.95 2.3–2.7 0.7 V

1.65–1.95 2.3–2.7 ±10 µAOE = V

or GND

1.65–1.95 2.3–2.7 20 µA

1.65–1.95 2.3–2.7 ±20 µA

≤ 2.7V)

CCA

V

CCA

Min Max Units

V

V

CC

V

V

V

V

CCA

CCB

CC

–0.2

–0.2

3 www.fairchildsemi.com

Loading...

Loading...