Fairchild Semiconductor 74VCX162839MTDX, 74VCX162839MTD Datasheet

© 1999 Fairchild Semiconductor Corporation DS500127 www.fairchildsemi.com

March 1998

Revised July 1999

74VCX162839 Low Voltage 20-Bit Selectable Register/Buffer with 3.6V Tolerant Inputs and Outputs and 26Ω

Series Resistors in the Outputs

74VCX162839

Low Voltage 20-Bit Selectable Register/Buffer with

3.6V Tolerant Inputs and Outputs

and 26Ω Series Resistors in the Outputs

General Description

The VCX162839 contains twen ty non-inverting selectable

buffered or registered pa ths. T he dev ic e can be configured

to operate in a regis tered, or flow throu gh buffer mode by

utilizing the register enable (REGE) and Clock (CP) signals. The device operates in a 20-bit word wide mode. All

outputs can be placed into 3-STATE through use of the OE

pin. These devices ar e ideally sui ted for buffered or registered 168 pin and 200 pin SDRAM DIMM memo ry modules.

The 74VCX162839 is designed for low v oltage (1.65V to

3.6V) V

CC

applications with I/O compatibility up to 3.6V.

The 74VCX162839 i s also designed with 26Ω series resistors in the outputs. This design reduces line noise in applications such as memory address drivers, clock drivers, and

bus transceivers/transmitters.

The 74VCX162839 is fab ricated with an advance d CMOS

technology to achieve high speed operation while maintaining low CMOS power dissipation.

Features

■ Compatible with PC100 and PC133 DIMM module

specifications

■ 1.65V–3.6V V

CC

supply operation

■ 3.6V tolerant inputs and outputs

■ 26Ω series resistors in the outputs

■ t

PD

(CP to On)

4.1 ns max for 3.0V to 3.6V V

CC

5.8 ns max for 2.3V to 2.7V VCC

9.8 ns max for 1.65V to 1.95V V

CC

■ Power-off high impedance inputs and outputs

■ Supports live insertion and withdrawal (Note 1)

■ Static Drive (I

OH/IOL

)

±12 mA @ 3.0V V

CC

±8 mA @ 2.3V V

CC

±3 mA @ 1.65V V

CC

■ Uses patented noise/EMI reduction circuitry

■ Latch-up performance exceeds 300 mA

■ ESD performance:

Human body model > 2000V

Machine model > 200V

Note 1: To ensure the high-impedance state d uring power up or power

down, OE

should be tied to VCC through a pull-up r esistor; the min imum

value of the res istor is d eter mine d by the cu rre nt-sou rcin g ca pa bility of t he

driver.

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending su ffix let te r “X” to the ordering code.

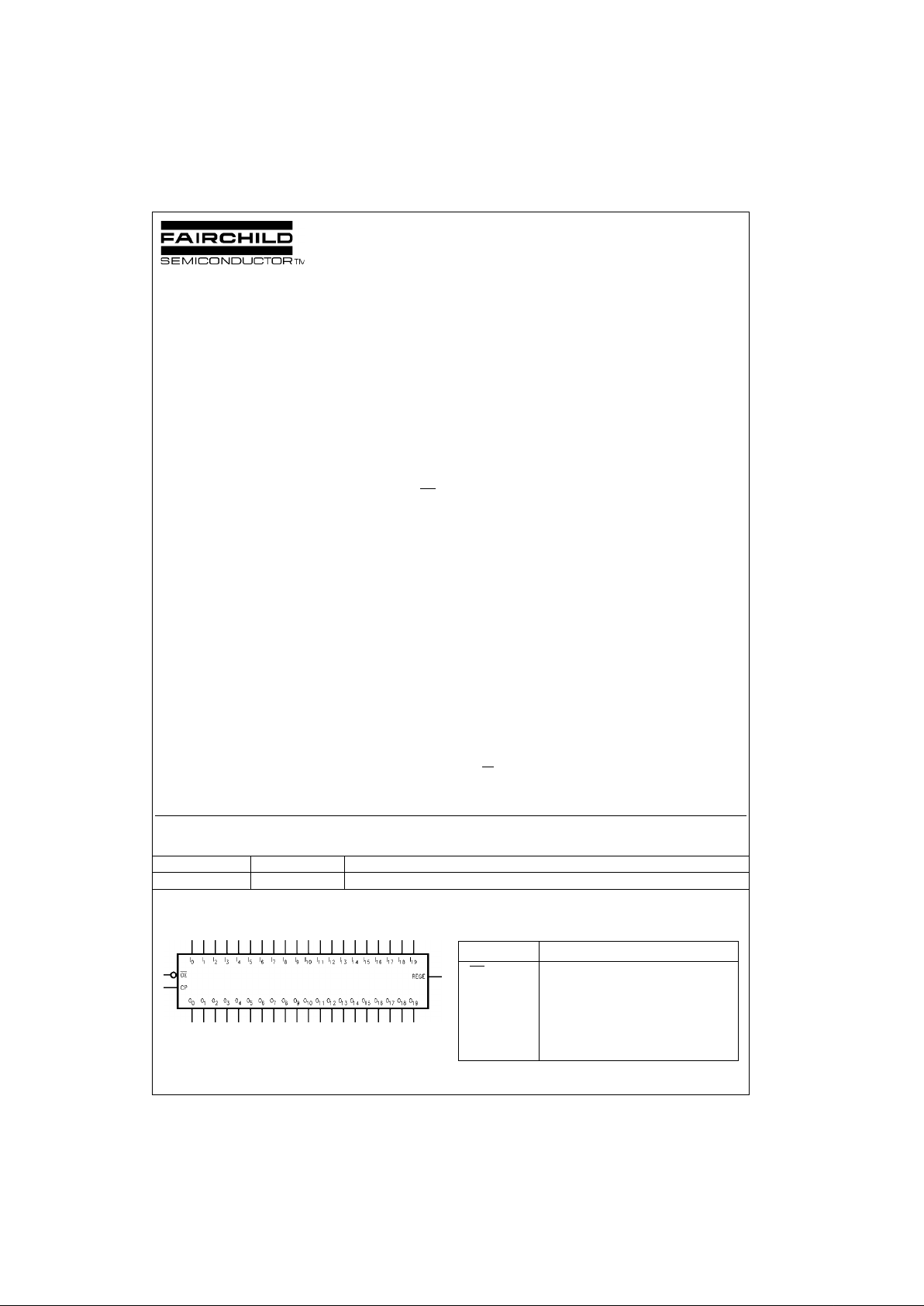

Logic Symbol Pin Descriptions

Order Number Package Number Package Description

74VCX162839MTD MTD56 56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Pin Names Description

OE

Output Enable Input (Active LOW)

I

0–I19

Inputs

O

0–O19

Outputs

CP Clock Pulse Input

REGE Register Enable Input

www.fairchildsemi.com 2

74VCX162839

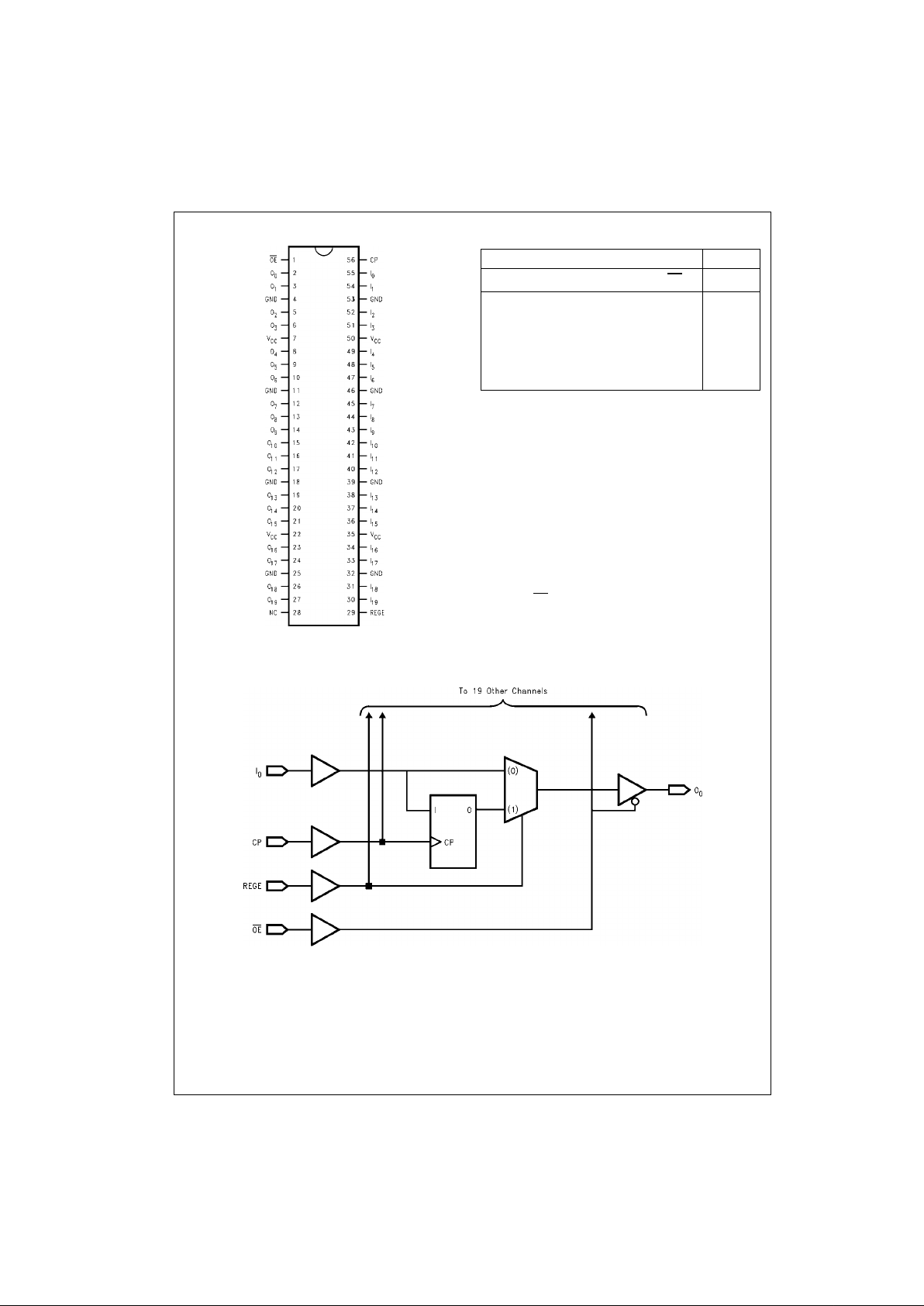

Connection Diagram Tr uth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial (HIGH or LOW, inputs may not float)

Z = High Impedance

Functional Description

The 74VCX162839 consists of twenty selectable noninverting buffers or registers with word wide controls. Mode

functionality is selecte d through operation of the CP and

REGE pin as shown by the truth table. When REGE is held

at a logic “1” the device opera tes as a 20- bit regist er. Data

is transferred from I

n

to On on the rising edge of the CP pin.

When the REGE pin i s held at a logic “ 0” the devi ce operates in a flow through mode an d data propagates direct ly

from the I

n

to the On outputs. All outputs can be 3-stated by

holding the OE

pin at a logic “1.”

Logic Diagram

Inputs Outputs

CP REGE

I

n

OE

O

n

↑ HHL H

↑ HLL L

XLHLH

XLLLL

XXXHZ

3 www.fairchildsemi.com

74VCX162839

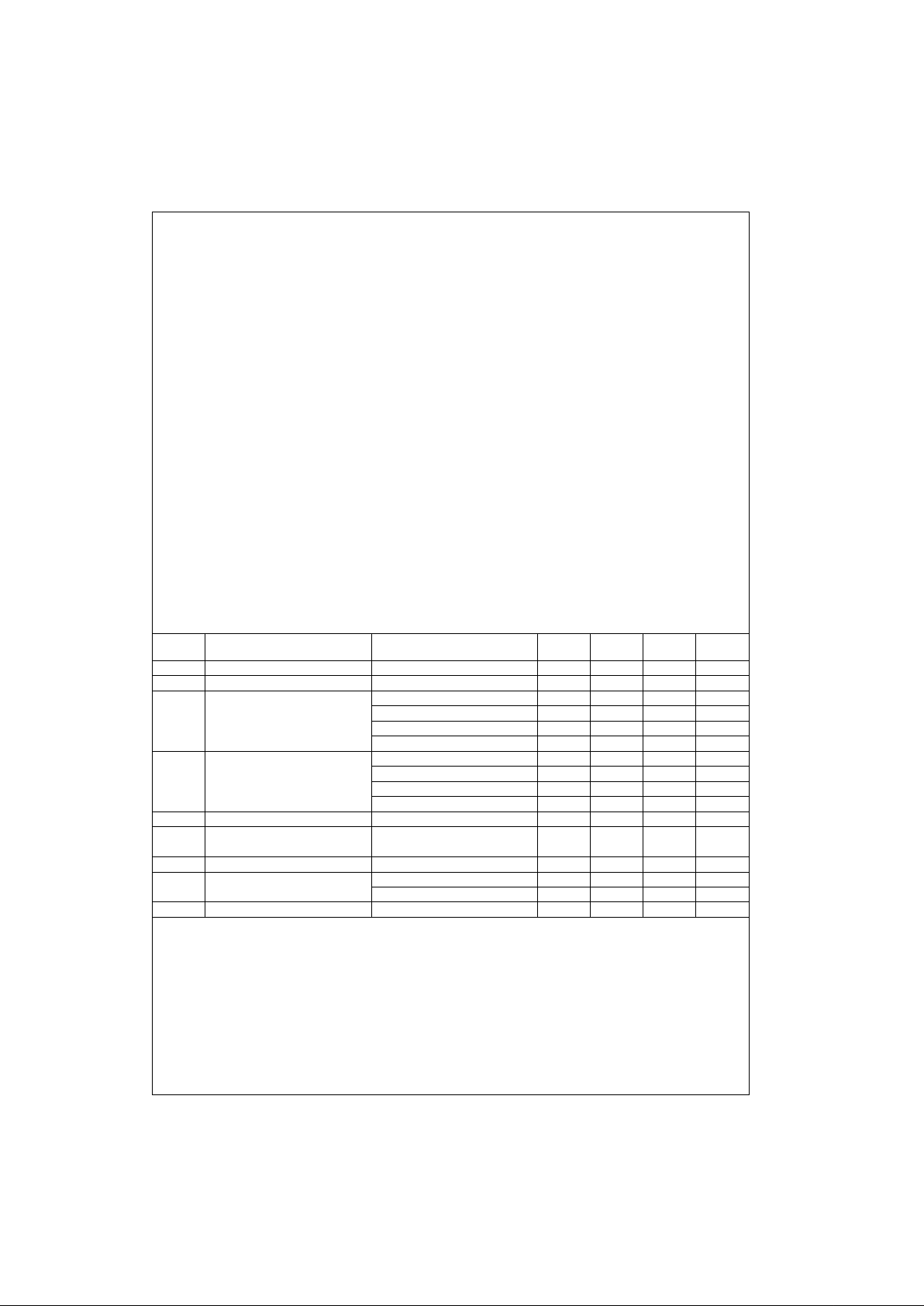

Absolute Maximum Ratings(Note 2) Recommended Operating

Conditions

(Note 4)

Note 2: The Absolute Maximum Ratings are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the Absolute Maximum Rat-

ings. The “Recommended Operating Conditions” table will define the conditions for actual device operation.

Note 3: I

O

Absolute Maximum Rating must be observed.

Note 4: Floating or unused inputs m us t be held HIGH or LOW.

DC Electrical Characteristics (2.7V < VCC ≤ 3.6V)

Note 5: Outputs disab led or 3-STATE only.

Supply Voltage (VCC) −0.5V to +4.6V

DC Input Voltage (V

I

) −0.5V to +4.6V

Output Voltage (V

O

)

Outputs 3-STATE −0.5V to +4.6V

Outputs Active (Note 3) −0.5V to V

CC

+ 0.5V

DC Input Diode Current (I

IK

) VI < 0V −50 mA

DC Output Diode Current (I

OK

)

V

O

< 0V −50 mA

V

O

> V

CC

+50 mA

DC Output Source/Sink Current

(I

OH/IOL

) ±50 mA

DC V

CC

or GND Current per

Supply Pin (I

CC

or GND) ±100 mA

Storage Temperature Range (T

STG

) −65°C to +150°C

Power Supply

Operating 1.65V to 3.6V

Data Retention Only 1.2V to 3.6V

Input Voltage −0.3V to +3.6V

Output Voltage (V

O

)

Output in Active States 0V to V

CC

Output in “OFF” State 0.0V to 3.6V

Output Current in I

OH/IOL

VCC = 3.0V to 3.6V ±12 mA

V

CC

= 2.3V to 2.7V ±8 mA

V

CC

= 1.65V to 2.3V ±3 mA

Free Air Operating Temperature (T

A

) −40°C to +85°C

Minimum Input Edge Rate (∆t/∆V)

V

IN

= 0.8V to 2.0V, VCC = 3.0V 10 ns/V

Symbol Parameter Conditions

V

CC

(V)

Min Max Units

V

IH

HIGH Level Input Voltage 2.7 − 3.6 2.0 V

V

IL

LOW Level Input Voltage 2.7 − 3.6 0.8 V

V

OH

HIGH Level Output Voltage IOH = −100 µA2.7 − 3.6 VCC − 0.2 V

IOH = −6 mA 2.7 2.2 V

IOH = −8 mA 3.0 2.4 V

IOH = −12 mA 3.0 2.2 V

V

OL

LOW Level Output Voltage IOL = 100 µA2.7 − 3.6 0.2 V

IOL = 6 mA 2.7 0.4 V

IOL = 8 mA 3.0 0.55 V

IOL = 12 mA 3.0 0.8 V

I

I

Input Leakage Current 0 ≤ VI ≤ 3.6V 2.7 − 3.6 ±5.0 µA

I

OZ

3-STATE Output Leakage 0 ≤ VO ≤ 3.6V

2.7 − 3.6 ±10 µA

VI = VIH or V

IL

I

OFF

Power-OFF Leakage Current 0 ≤ (VI, VO) ≤ 3.6V 0 10 µA

I

CC

Quiescent Supply Current VI = VCC or GND 2.7 − 3.6 20 µA

VCC ≤ (VI, VO) ≤ 3.6V (Note 5) 2.7 − 3.6 ±20 µA

∆I

CC

Increase in ICC per Input VIH = VCC −0.6V 2.7 − 3.6 750 µA

Loading...

Loading...