Fairchild Semiconductor 74VCX162835MTDX, 74VCX162835MTD Datasheet

© 2000 Fairchild Semiconductor Corporation DS500181 www.fairchildsemi.com

October 1998

Revised April 2000

74VCX162835 Low Voltage 18-Bit Universal Bus Driver with 3.6V Tolerant Inputs/Outputs and 26 Ω Series

Resistors in Outputs

74VCX162835

Low Voltage 18-Bit Universal Bus Driver with

3.6V Tolerant Inputs/Outputs

and 26Ω Series Resistors in Outputs

General Description

The VCX162835 low voltage 18-bit universal bus driver

combines D-type latches and D-type flip-flops to allow data

flow in transparent, latched and clocked modes.

Data flow is controll ed b y ou tpu t-e na bl e (OE

), latch-enable

(LE), and clock (CLK) inputs. The device operates in

Transparent Mode when LE is held HIGH. The device

operates in clocked mode when LE is LOW and CLK is toggled. Data transfer s f rom the In pu ts (I

n

) to Outputs (On) on

a Positive Edge Transition of the Clock. When OE

is LOW,

the output data is enabled. When OE

is HIGH the output

port is in a high impedance state.

The VCX162835 is desig ned with 26Ω series resistors in

the outputs. This design reduces noise in applications such

as memory address drivers, clo ck drivers, and bus transceivers/transmitters.

The 74VCX162835 is designed for low v oltage (1.65V to

3.6V) V

CC

applications with I/O capability up to 3.6V.

The 74VCX162835 is fab ricated with an advance d CMOS

technology to achieve high speed operation while maintaining low CMOS power dissipation.

Features

■ Compatible with PC100 DIMM module specifications

■ 1.65V–3.6V V

CC

specifications provided

■ 3.6V tolerant inputs and outputs

■ 26Ω series resistors in outputs

■ t

PD

(CP to On)

4.2ns max for 3.0V to 3.6V V

CC

5.2ns max for 2.3V to 2.7V V

CC

9.2ns max for 1.65V to 1.95V V

CC

■ Power-down high impedance inputs and outputs

■ Supports live insertion/withdrawal (Note 1)

■ Static Drive (I

OH/IOL

)

±12mA @ 3.0V V

CC

±8 mA @ 2.3V V

CC

±3 mA @ 1.65V V

CC

■ Latchup performance exceeds 300 mA

■ ESD performance:

Human body model > 2000V

Machine model >200V

Note 1: To ensure the high impedance state during power up or power

down, OE

should be tied to VCC through a pulldown resis tor; the minimu m

value of the resistor is dete rmined by the curren t sourcing capability of the

driver.

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending the s uffix let te r “X” to the ordering code.

Order Number Package Num ber Package Description

74VCX162835MTD MTD56 56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

www.fairchildsemi.com 2

74VCX162835

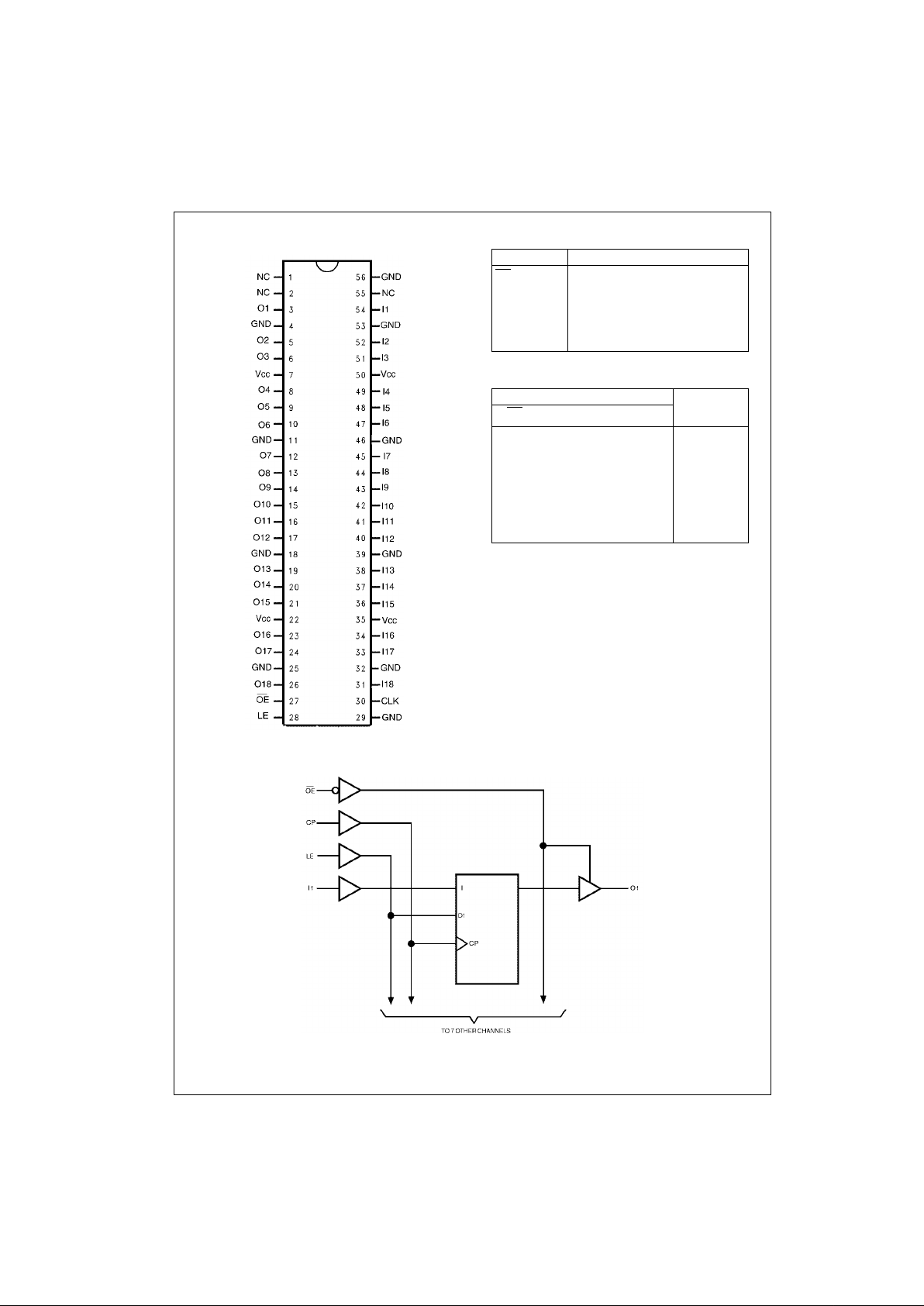

Connection Diagram Pin Descriptions

Function Table

H = HIGH Voltage Level

L = LOW Level Voltage

X = Immaterial (HIGH or LOW, Inputs may not float)

Z = High Impedance

Note 2: Output level be fore the indicated steady-st ate input conditions

were established pr ov ided that CP was HIGH before LE went LOW.

Note 3: Output level be fore the indicated steady-st ate input conditions

were established.

Logic Diagram

Pin Names Description

OE

Output Enable Input (Active LOW)

LE Latch Enable Input

CP Clock Input

I

1

- I

18

Data Inputs

O

1

- O

18

3-STATE Outputs

Inputs Outputs

OE

LE CP I

n

O

n

HXXX Z

LHXL L

LHXH H

LL↑ LL

LL↑ HH

LLHXO

0

(Note 2)

LLLXO

0

(Note 3)

3 www.fairchildsemi.com

74VCX162835

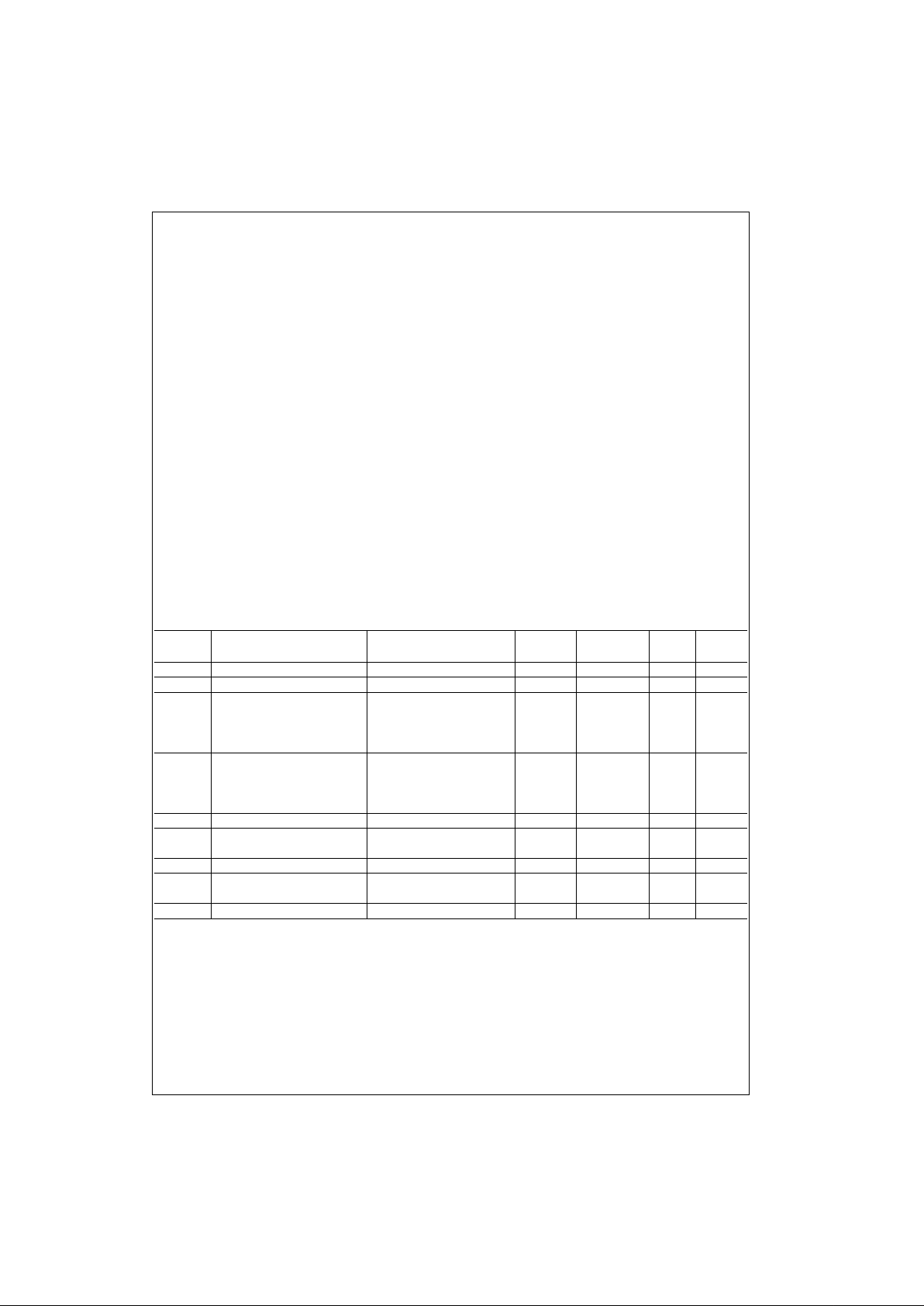

Absolute Maximum Ratings(Note 4) Recommended Operating

Conditions

(Note 6)

Note 4: The “Absolute Maximum Ratings” are those value s beyond which

the safety of the dev ice cannot b e guaranteed . The device sh ould not be

operated at these limit s. The parametric values defi ned in the Electrical

Characteristics tables are not guaranteed at the Absolute Maximum Ratings. The Recommended Operating Con ditions tables will define th e c onditions for actual device operat ion.

Note 5: I

O

Absolute Maximum Rating must be observed.

Note 6: Floating or unused pin (i nputs or I/O's) m ust be held HIGH o r LOW.

DC Electrical Characteristics (2.7V < VCC ≤ 3.6V)

Note 7: Outputs disabled or 3-STATE only.

Supply Voltage (VCC) −0.5V to +4.6V

DC Input Voltage (V

I

) −0.5V to +4.6V

Output Voltage (V

O

)

Outputs 3-STATE −0.5V to +4.6V

Outputs Active (Note 5) −0.5 to V

CC

+ 0.5V

DC Input Diode Current (I

IK

) VI < 0V −50 mA

DC Output Diode Current (I

OK

)

V

O

< 0V −50 mA

V

O

> V

CC

+50 mA

DC Output Source/Sink Current

(I

OH/IOL

) ±50 mA

DC V

CC

or Ground Current per

Supply Pin (I

CC

or Ground) ±100 mA

Storage Temperature Range (T

STG

) −65°C to +150°C

Power Supply

Operating 1.65V to 3.6V

Data Retention Only 1.2V to 3.6V

Input Voltage −0.3V to 3.6V

Output Voltage (V

O

)

Output in Active States 0V to V

CC

Output in 3-STATE 0.0V to 3.6V

Output Current in I

OH/IOL

V

CC

= 3.0V to 3.6V ±12 mA

V

CC

= 2.3V to 2.7V ±8 mA

V

CC

= 1.65V to 2.3V ±3 mA

Free Air Operating Temperature (T

A

) −40°C to +85°C

Minimum Input Edge Rate (∆t/∆V)

V

IN

= 0.8V to 2.0V, VCC = 3.0V 10 ns/V

Symbol Parameter Conditions

V

CC

Min Max Units

(V)

V

IH

HIGH Level Input Voltage 2.7–3.6 2.0 V

V

IL

LOW Level Input Voltage 2.7–3.6 0.8 V

V

OH

HIGH Level Output Voltage IOH = −100 µA2.7–3.6 VCC − 0.2

I

OH

= −6 mA 2.7 2.2

V

I

OH

= −8 mA 3.0 2.4

IOH = −12 mA 3.0 2.2

V

OL

LOW Level Output Voltage IOL = 100 µA2.7–3.6 0.2

I

OL

= 6mA 2.7 0.4

V

IOL = 8 mA 3.0 0.55

I

OL

= 12mA 3.0 0.8

I

I

Input Leakage Current 0V ≤ VI ≤ 3.6V 2.7–3.6 ±5.0 µA

I

OZ

3-STATE Output Leakage 0V ≤ VO ≤ 3.6V

2.7–3.6 ±10 µA

VI = VIH or V

IL

I

OFF

Power Off Leakage Current 0V ≤ (VI, VO) ≤ 3.6V 0 10 µA

I

CC

Quiescent Supply Current VI = VCC or GND 2.7–3.6 20

µA

VCC ≤ (VI, VO) ≤ 3.6V (Note 7) 2.7–3.6 ±20

∆I

CC

Increase in ICC per Input VIH = VCC − 0.6V 2.7–3.6 750 µA

Loading...

Loading...