Fairchild Semiconductor 74LVX4245MTCX, 74LVX4245MTC, 74LVX4245CW, 74LVX4245WMX, 74LVX4245WM Datasheet

...

© 1999 Fairchild Semiconductor Corporation DS011540 www.fairchildsemi.com

January 1993

Revised July 1999

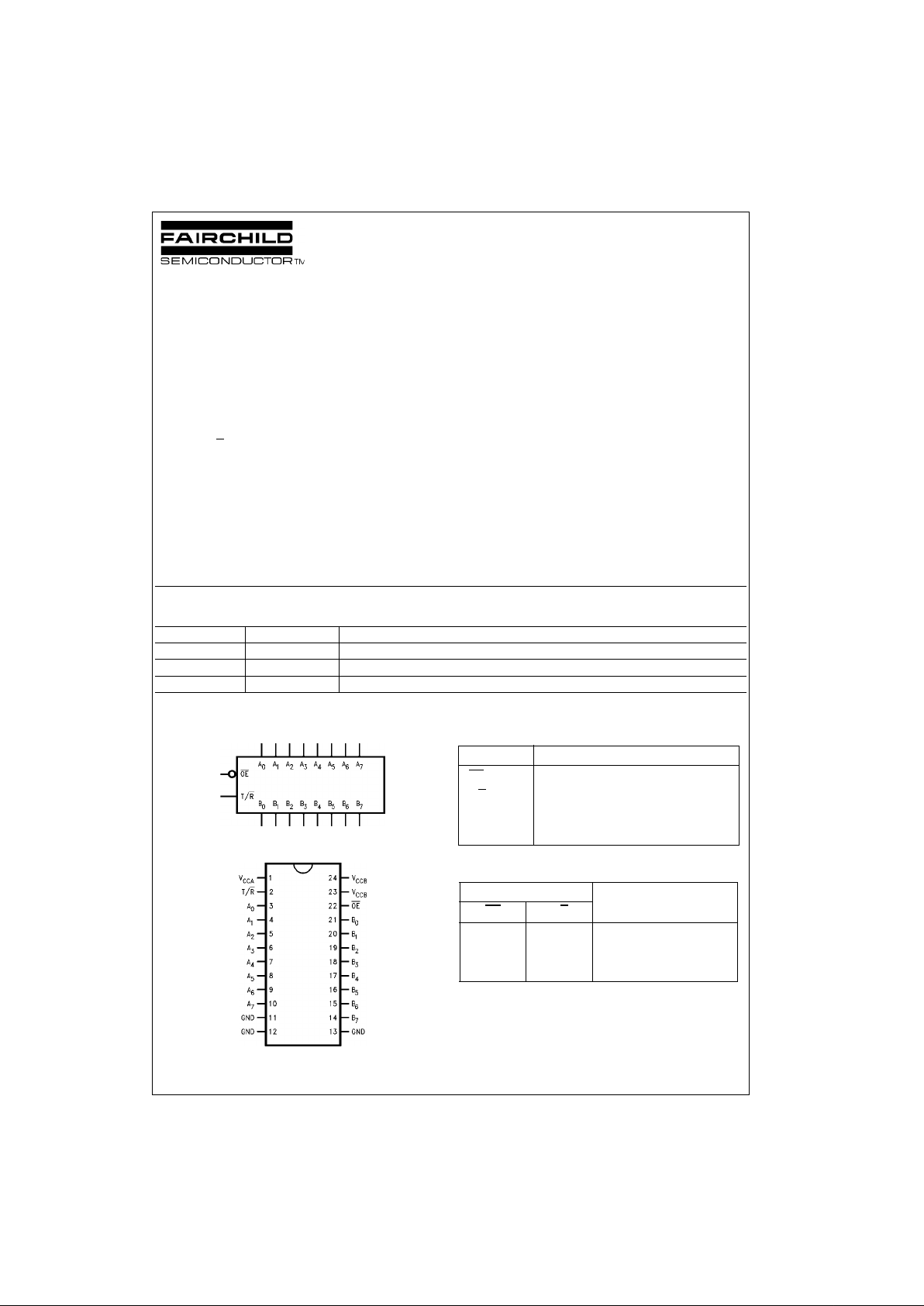

74LVX4245 8-Bit Dual Supply Translating Transceiver with 3-STATE Outputs

74LVX4245

8-Bit Dual Supply Translating Transceiver with 3-STATE

Outputs

General Description

The LVX4245 is a dual-supply, 8-bit tran slating transcei ver

that is designed to interface be tween a 5V bus and a 3V

bus in a mixed 3V/5V sup ply environment. The Transmit/

Receive (T/R

) input determines the direction of da ta flow.

Transmit (active-HIGH) enables data from A Ports to B

Ports; Receive (acti ve-LOW) en ables data from B Ports to

A Ports. The Output Enable input, w hen HIGH, disables

both A and B Ports by placing them in a h igh impedance

condition. The A Port interfaces with the 5V bus; the B Port

interfaces with the 3V bus.

The LVX4245 is suitable for mixed voltage applications

such as laptop com puters using 3. 3V CPU’s and 5V LCD

displays.

Features

■ Bidirectional interface between 5V and 3V buses

■ Control inputs compatible with TTL level

■ 5V data flow at A Port and 3V data flow at B Port

■ Outputs source/sink 24 mA at 5V bus; 12 mA at 3V bus

■ Guaranteed simultaneous switching noise level and

dynamic threshold performance

■ Implements patented EMI reduction circuitry

■ Functionally compatible with the 74 series 245

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

Logic Symbol

Connection Diagram

Pin Descriptions

Truth Ta ble

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Order Number Package Number Package Description

74LVX4245WM M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide

74LVX4245QSC MQA24 24-Lead Quarter Size Outline Package (QSOP), JEDEC MO-137, 0.150” Wide

74LVX4245MTC MTC24 24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Pin Names Description

OE

Output Enable Input

T/R

Transmit/Receive Input

A

0–A7

Side A Inputs or 3-STATE Outputs

B

0–B7

Side B Inputs or 3-STATE Outputs

Inputs Outputs

OE

T/R

L L Bus B Data to Bus A

L H Bus A Data to Bus B

H X HIGH-Z State

www.fairchildsemi.com 2

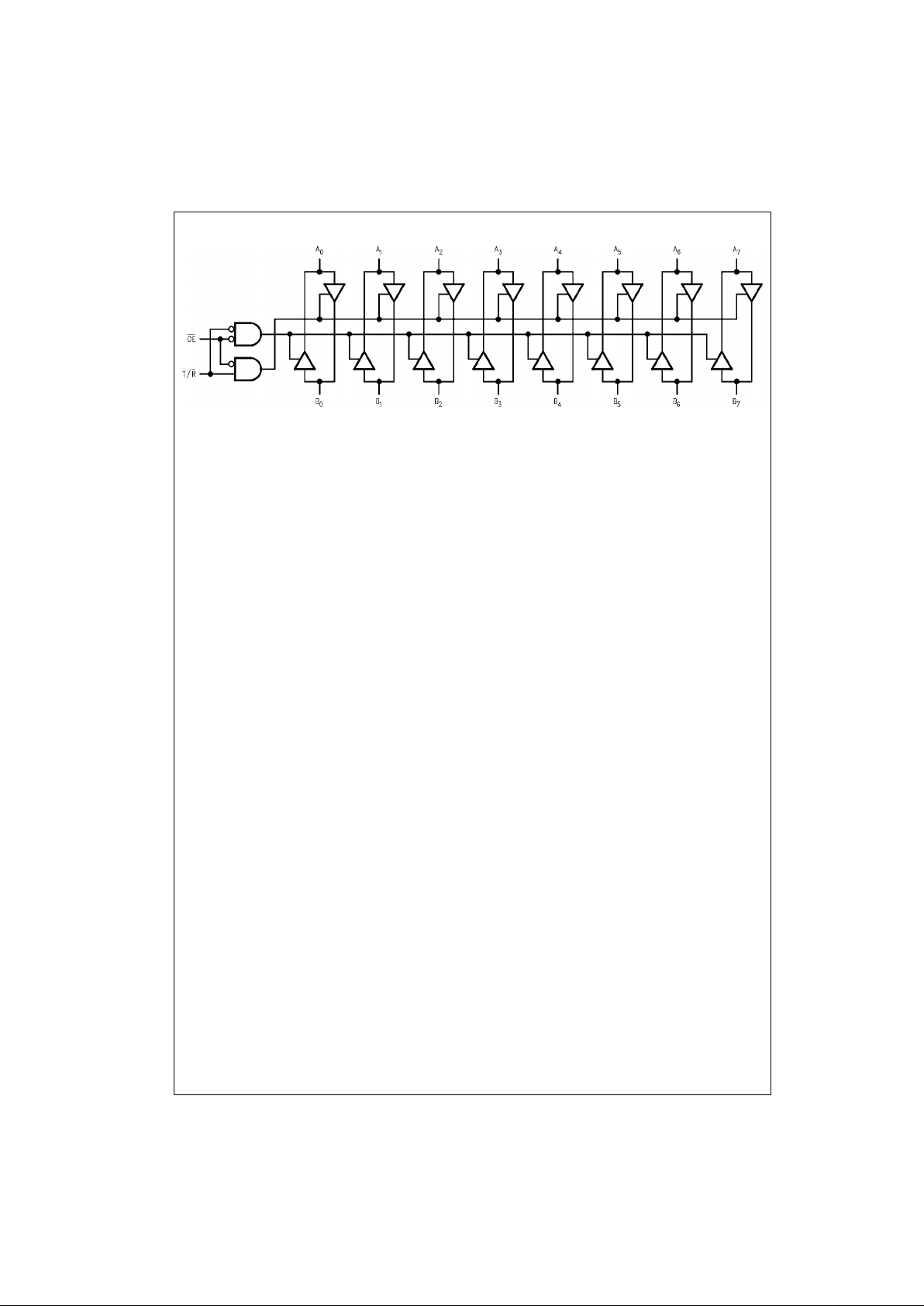

74LVX4245

Logic Diagram

3 www.fairchildsemi.com

74LVX4245

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

(Note 2)

Note 1: The “Absolute Maximum Ratings ” are those val ues beyond w hich

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommend ed O peratin g Cond itions” t able w ill defin e the condition s

for actual device operation.

Note 2: Unused inputs must he held HIGH or LOW. They may not float.

DC Electrical Characteristics

Supply Voltage (V

CCA

, V

CCB

) −0.5V to +7.0V

DC Input Voltage (V

I

) @ OE, T/R −0.5V to V

CCA

+ 0.5V

DC Input/Output Voltage (V

I/O

)

@ A

n

−0.5V to V

CCA

+ 0.5V

@B

n

−0.5V to V

CCB

+ 0.5V

DC Input Diode Current (I

IN

)

@ OE

, T/R ±20 mA

DC Output Diode Current (I

OK

) ±50 mA

DC Output Source or Sink Current

(I

O

) ±50 mA

DC V

CC

or Ground Current

per Output Pin (I

CC

or I

GND

) ±50 mA

and Max Current @ I

CCA

±200 mA

@ I

CCB

±100 mA

Storage Temperature Range

(T

STG

) −65°C to +150°C

DC Latch-Up Source or

Sink Current ±300 mA

Supply Voltage

V

CCA

4.5V to 5.5V

V

CCB

2.7V to 3.6V

Input Voltage (V

I

) @ OE, T/R 0V to V

CCA

Input/Output Voltage (V

I/O

)

@ A

n

0V to V

CCA

@ B

n

0V to V

CCB

Free Air Operating Temperature (TA) −40°C to +85°C

Minimum Input Edge Rate (∆t/∆V) 8 ns/V

V

IN

from 30% to 70% of V

CC

VCC @ 3.0V, 4.5V, 5.5V

Symbol Parameter

V

CCA

(V)

V

CCB

(V)

TA +25°C

TA = −40°C to +85°C

Units Conditions

Typ Guaranteed Limits

V

IHA

Minimum

An, T/R,

5.5 3.3 2.0 2.0

V

V

OUT

≤ 0.1V or

HIGH Level

OE

4.5 3.3 2.0 2.0 ≥ VCC − 0.1V

V

IHB

Input Voltage B

n

5.0 3.6 2.0 2.0

5.0 2.7 2.0 2.0

V

ILA

Maximum

An, T/R,

5.5 3.3 0.8 0.8

V

V

OUT

≤ 0.1V or

LOW Level

OE

4.5 3.3 0.8 0.8 ≥ VCC −0.1V

V

ILB

Input Voltage B

n

5.0 2.7 0.8 0.8

5.0 3.6 0.8 0.8

V

OHA

Minimum HIGH Level 4.5 3.0 4.5 4.4 4.4

V

I

OUT

= −100 µA

Output Voltage 4.5 3.0 4.25 3.86 3.76 IOH = −24 mA

V

OHB

4.5 3.0 2.99 2.9 2.9

V

I

OUT

= −100 µA

4.5 3.0 2.8 2.4 2.4 IOH = −12 mA

4.5 2.7 2.5 2.4 2.4 IOL = −8 mA

V

OLA

Maximum LOW Level 4.5 3.0 0.002 0.1 0.1 V I

OUT

=100 µA

Output Voltage 4.5 3.0 0.18 0.36 0.44 IOL = 24 mA

V

OLB

4.5 3.0 0.002 0.1 0.1 I

OUT

= 100 µA

4.5 3.0 0.1 0.31 0.4 V IOL = 12 mA

4.5 2.7 0.1 0.31 0.4 IOL = 8 mA

I

IN

Maximum Input VI = V

CCA

, GND

Leakage Current 5.5 3.6 ±0.1 ±1.0 µA

@ OE, T/R

I

OZA

Maximum 3-STATE VI = VIL, V

IH

Output Leakage 5.5 3.6 ±0.5 ±5.0

µA

OE = V

CCA

@ A

n

VO = V

CCA

, GND

I

OZB

Maximum 3-STATE VI = VIL, V

IH

Output Leakage 5.5 3.6 ±0.5 ±5.0

µA

OE = V

CCA

@ B

n

VO = V

CCB

, GND

Loading...

Loading...