Fairchild Semiconductor 74LVX374MTC, 74LVX374MSCX, 74LVX374M, 74LVX374SJX, 74LVX374SJ Datasheet

...

October 1993

Revised March 1999

74LVX374 Low Voltage Octal D-Type Flip-Flop with 3-STATE Outputs

© 1999 Fairchild Semiconductor Corporation DS011612.prf www.fairchildsemi.com

74LVX374

Low Voltage Octal D-Type Flip-Flop with

3-STATE Outputs

General Description

The LVX374 is a high-speed, low-power octal D-type flipflop featuring separate D-type inputs for each flip- flop and

3-STATE outputs for bus-oriented applications. A buffered

Clock (CP) and Output Enable (OE

) are common to all flipflops. The inputs tolerate up to 7V allo wing inter face of 5V

systems to 3V systems.

Features

■ Input voltage translation from 5V to 3V

■ Ideal for low power/low noise 3.3V applications

■ Guaranteed simultaneous switching noise level and

dynamic threshold performance

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

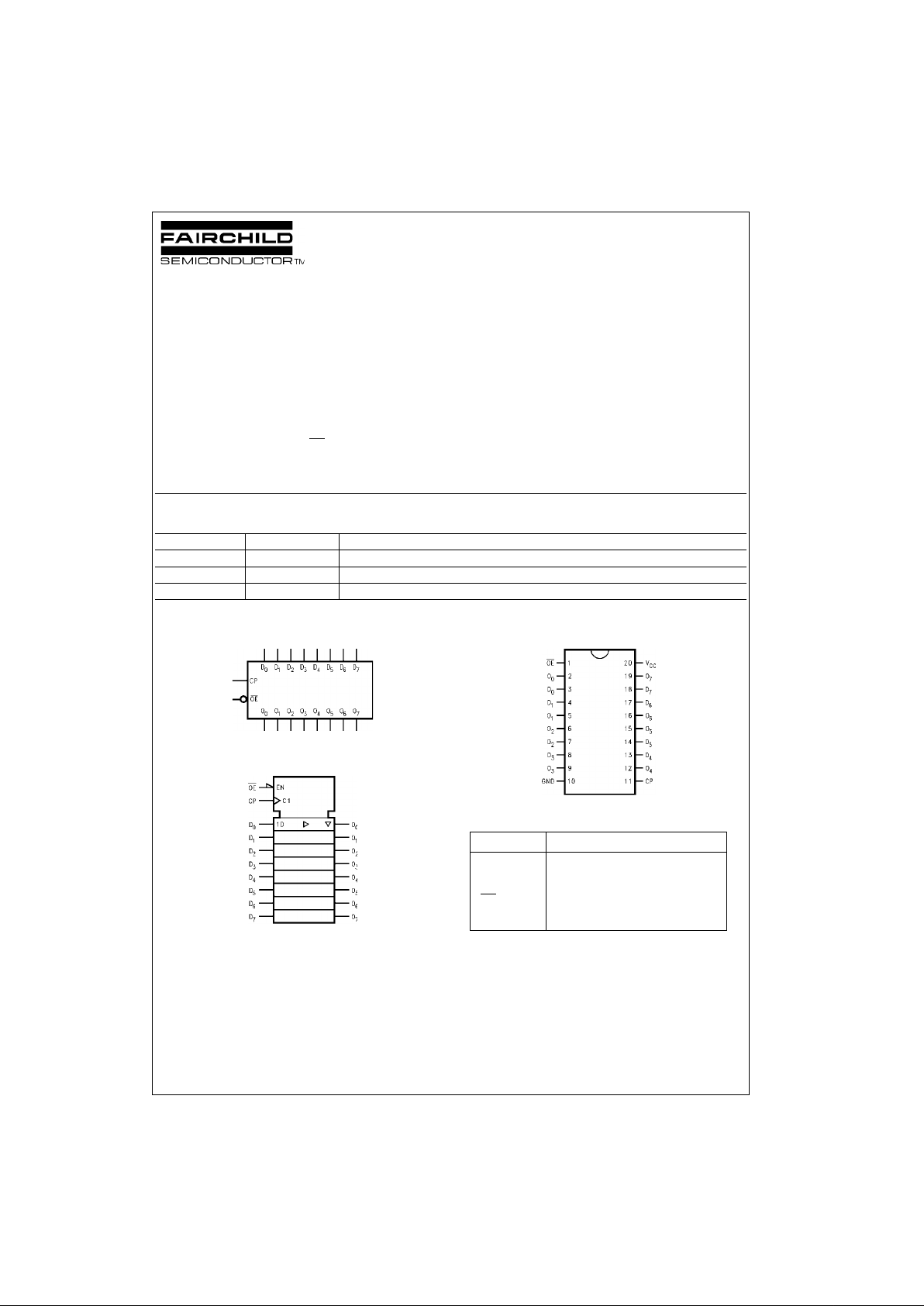

Logic Symbols

IEEE/IEC

Connection Diagram

Pin Descriptions

Order Number Package Number Package Description

74LVX374M M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide

74LVX374SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74LVX374MTC MTC20 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Pin Names Description

D

0–D7

Data Inputs

CP Clock Pulse Input

OE

3-STATE Output Enable Input

O

0–O7

3-STATE Outputs

www.fairchildsemi.com 2

74LVX374

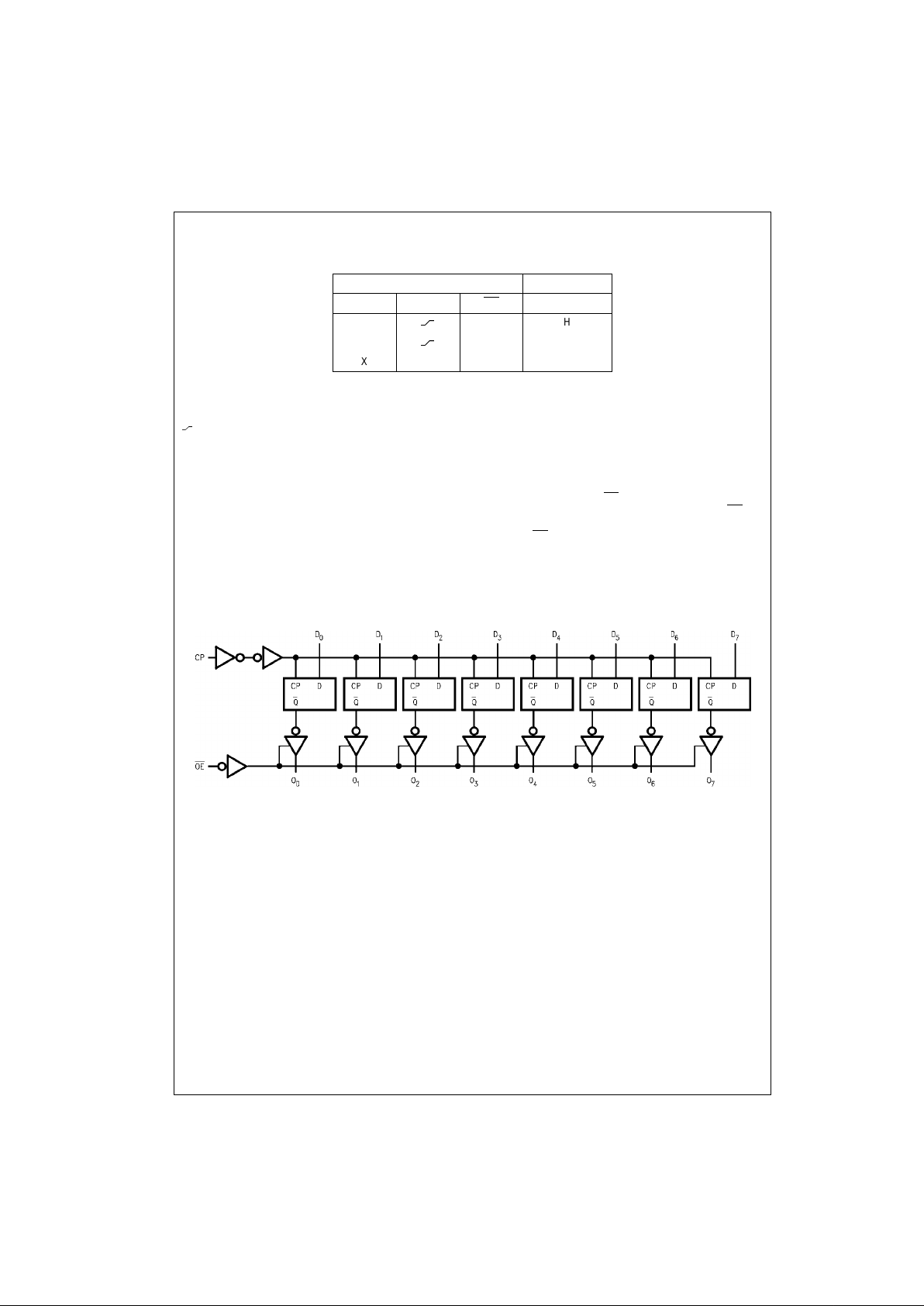

Truth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

= LOW-to-HIGH Transitio n

Functional Description

The LVX374 consists of eight e dge-tr iggere d flip -flops with

individual D-type inputs and 3-STATE true outputs. The

buffered clock and buffered Outp ut Enable are com mon to

all flip-flops. The eight flip-flops will store th e state of their

individual D inputs that meet the setup and hold time

requirements on the LOW-to-HIGH Clock (CP) transition.

With the Output Enable (OE

) LOW, the contents of the

eight flip-flops are available at the outputs. When the OE

is

HIGH, the outputs go to the h igh impedan ce state. Oper ation of the OE

input does not affect the state of the flip-

flops.

Logic Diagram

Please note that this diagram is provided o nly f or t he understanding of lo gic operations and shou ld not be used to estimate propagation delays.

Inputs Outputs

D

n

CP OE O

n

H

LH

L

LL

XXH Z

Loading...

Loading...