Fairchild Semiconductor 74LVX161284MEAX, 74LVX161284MEA, 74LVX161284MTDX, 74LVX161284MTD Datasheet

January 1999

Revised July 2000

74LVX161284

Low Voltage IEEE 161284 Translating Transceiver

74LVX161284 Low Voltage IEEE 161284 Translating Transceiver

General Description

The LVX161284 contains eight bidirectional data buffers

and eleven control/status buffers to implement a full

IEEE 1284 compliant interface. The device supports the

IEEE 1284 standard and is intended to be used in an

Extended Capabiliti es Port mode (E CP). Th e pinout al lows

for easy connection from the Peripheral (A-side) to the

Host (cable side).

Outputs on the cable si de can be configured to be either

open drain or high d rive (

separate power supply pin (V

puts to be driven by a higher supply voltage than the

A-side. The pull-up and pull-down series termination resistance of these outputs o n the cable side is optimized to

drive an external cabl e. In a ddit io n, all i np uts ( exce pt HL H)

and outputs on the cable side contain internal pull-up resistors connected to the V

termination and pull-ups for open drain mode.

Outputs on the Peripheral side are standard low-drive

CMOS outputs designed to interface with 3V logic. The DIR

input controls data flow on the A

pins.

± 14 mA) and are con nected t o a

cable) to allow these out-

CC

cable supply to provide pr oper

CC

1–A8/B1–B8

transceiver

Features

■ Supports IEEE 1284 Level 1 and Level 2 signaling

standards for bidirectional parallel communications

between personal computers and printing peripherals

■ Translation capability allows outputs on the cable side to

interface with 5V signals

■ All inputs have hysteresis to provide noise margin

■ B and Y output resistan ce optimized to drive external

cable

■ B and Y outputs in high impe dance mode dur ing power

down

■ Inputs and outputs on c able side have internal pull-up

resistors

■ Flow-through pin configuration allows easy interface

between the “Peripheral and Host”

■ Replaces the function of two (2) 74ACT1284 devices

Ordering Code

Order Number Package Number Package Descript io n

74LVX161284MEA MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300 Wide

74LVX161284MTD MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering co de.

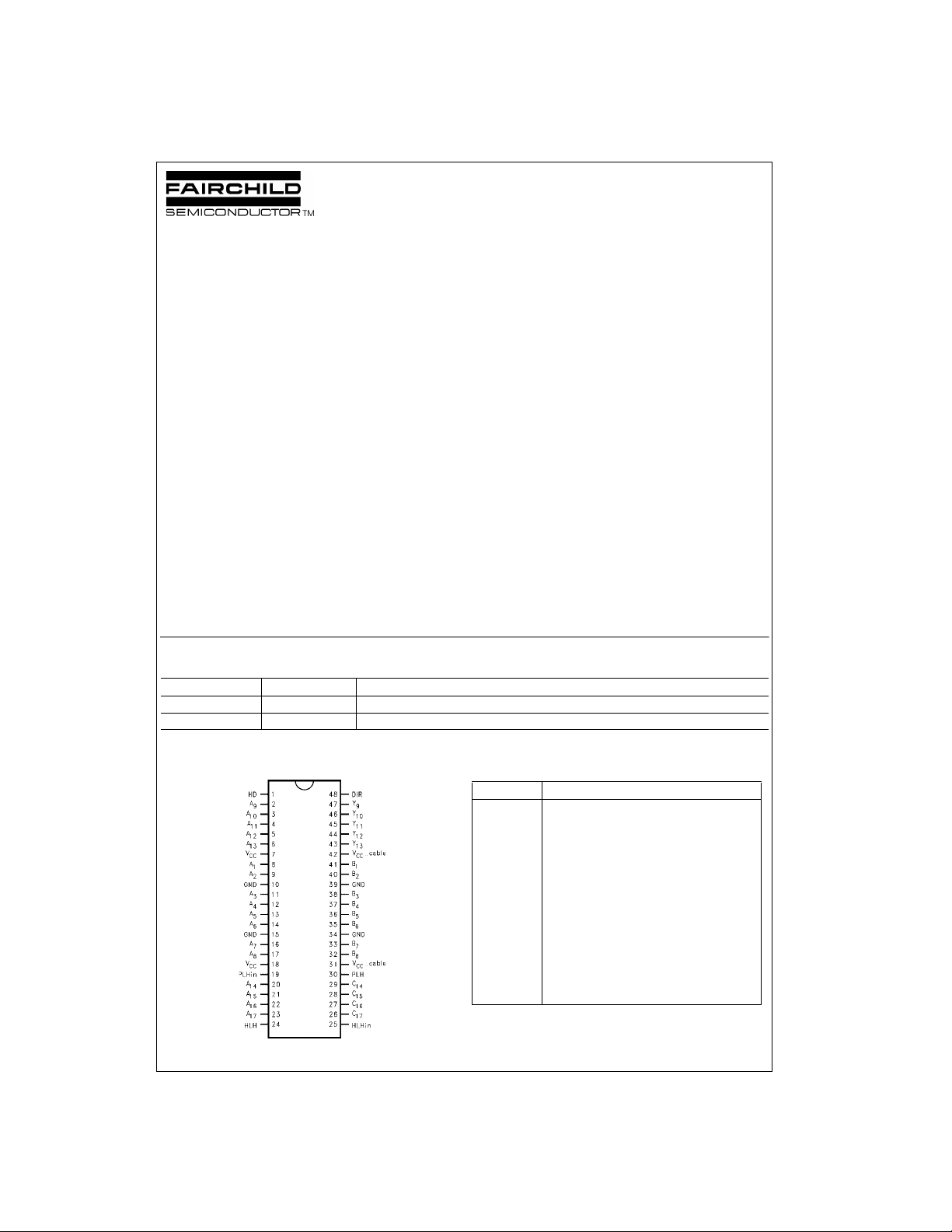

Connection Diagram Pin Descriptions

Pin Names Description

HD High Drive Enable Input (Active HIGH)

DIR Direction Control Input

A

1–A8

B

1–B8

A

9–A13

Y

9–Y13

A

14–A17

C

14–C17

PLH

IN

PLH Peripheral Logic HIGH Output

HLH

IN

HLH Host Logic HIGH Output

Inputs or Outputs

Inputs or Outputs

Inputs

Outputs

Outputs

Inputs

Peripheral Logic HIGH Input

Host Logic HIGH Input

© 2000 Fairchild Semiconductor Corporation DS500202 www.fairchildsemi.com

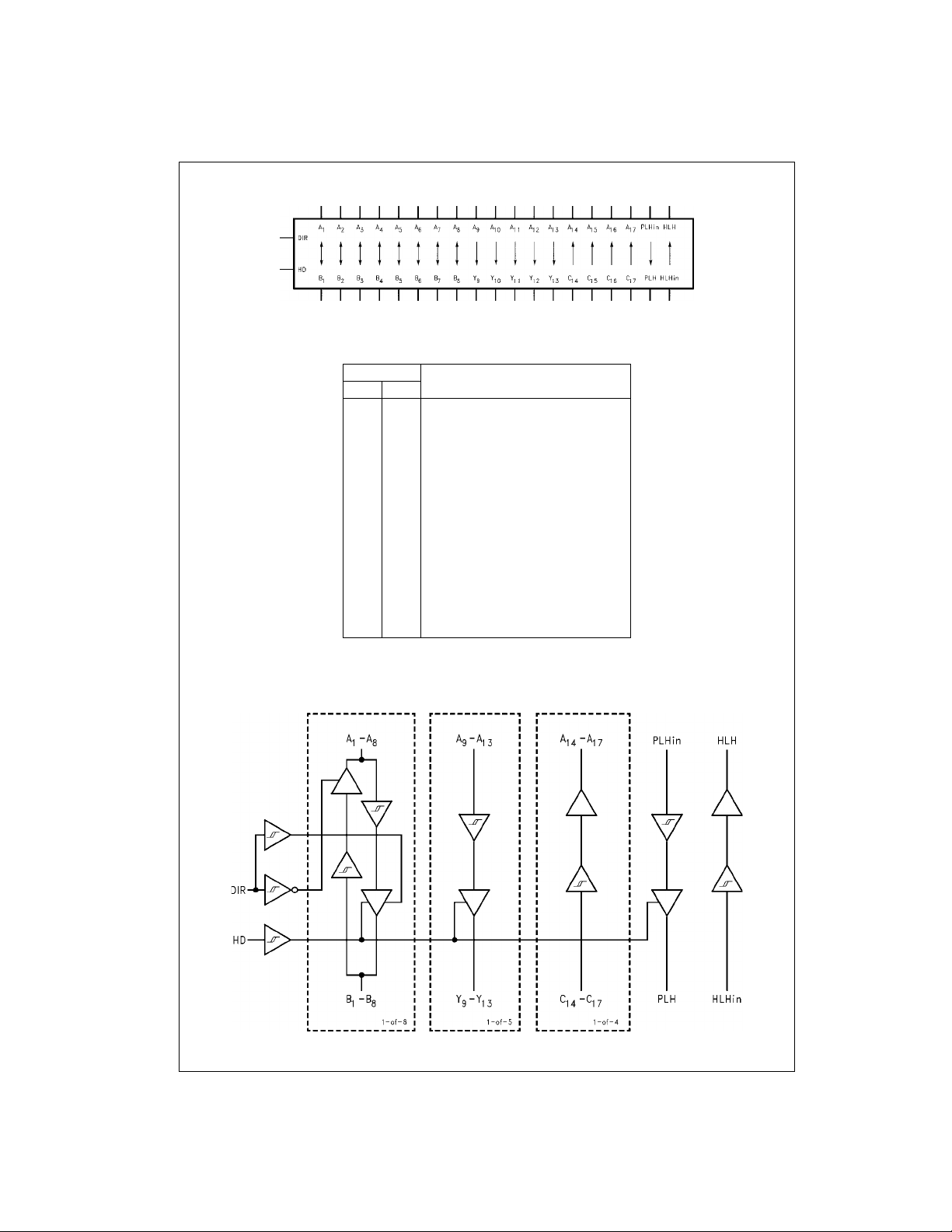

Logic Symbol

74LVX161284

Truth Table

Note 1: Y9–Y13 Open Drain Outputs

Note 2: B

Open Drain Outputs

1–B8

Inputs Outputs

DIR HD

LLB

Data to A1–A8, and

1–B8

A

Data to Y9–Y13 (Note 1)

9–A13

C

Data to A14–A

14–C17

17

PLH Open Drain Mode

LHB

Data to A1–A8, and

1–B8

A

Data to Y9–Y

9–A13

C14–C17 Data to A14–A

13

17

HLA1–A8 Data to B1–B8 (Note 2)

A

Data to Y9–Y13 (Note 1)

9–A13

Data to A14–A

C

14–C17

17

PLH Open Drain Mode

HHA

Data to B1–B

1–A8

8

A9–A13 Data to Y9–Y

C14–C17 Data to A14–A

13

17

Logic Diagram

www.fairchildsemi.com 2

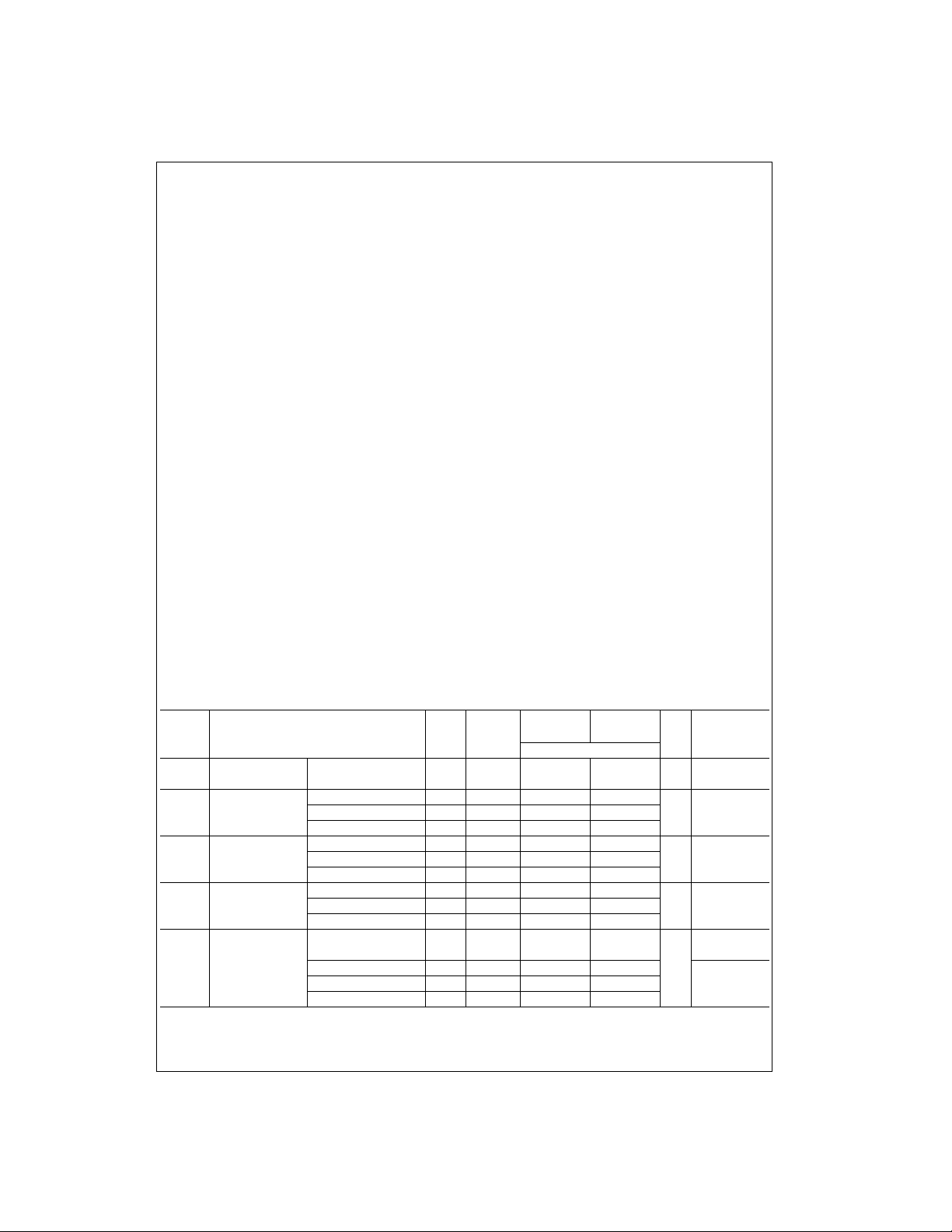

Absolute Maximum Ratings(Note 3) Recommended Operating

Supply Voltage

V

CC

V

CC—Cable

V

CC—Cable

Must Be ≥ V

CC

−0.5V to +4.6V

−0.5V to +7.0V

Input Voltage (VI)—(Note 4)

A

, PLHIN, DIR, HD −0.5V to VCC + 0.5V

1–A13

, C14–C17, HLH

B

1–B8

B

, C14–C17, HLH

1–B8

IN

IN

−0.5V to +5.5V (DC)

−2.0V to +7.0V*

*40 ns Transient

Output Voltage (V

A

, A14–A17, HLH −0.5V to VCC +0.5V

1–A8

B

, Y9–Y13, PLH −0.5V to +5.5V (DC)

1–B8

, Y9–Y13, PLH −2.0V to +7.0V*

B

1–B8

)

O

*40 ns Transient

DC Output Current (I

, HLH ±25 mA

A

1–A8

B

, Y9–Y

1–B8

)

O

13

±50 mA

PLH (Output LOW) 84 mA

PLH (Output HIGH) −50 mA

Input Diode Current (I

DIR, HD, A

9–A13

Output Diode Current (I

A

, A14–A17, HLH ±50 mA

1–A8

B

, Y9–Y13, PLH −50 mA

1–B8

DC Continuous V

Current

Storage Temperature

)—(Note 4)

IK

, PLH, HLH, C14–C

)

OK

or Ground

CC

17

−65°C to +150°C

−20 mA

±200 mA

ESD (HBM) Last Passing Voltage 2000V

Conditions

Supply Voltage

V

CC

V

CC—Cable

DC Input Voltage (V

Open Drain Voltage (VO) 0V to 5.5V

Operating Temperature (T

Note 3: Absolute maximum ratings are values beyond which the device

may be damaged or have its useful lif e impaired. Fairch ild does not recommend operation ou tside the databook sp ec if ic ations.

Note 4: Either voltage lim it or c urrent limit is sufficient to protect inputs.

)0V to V

I

) −40°C to +85°C

A

74LVX161284

3.0V to 3.6V

3.0V to 5.5V

CC

DC Electrical Characteristics

Symbol Parameter

V

V

V

∆V

V

Input Clamp 3.0 3.0 −1.2 −1.2 V Ii= −18 mA

IK

Diode Voltage

Minimum An, Bn, PLHIN, DIR, HD 3.0–3.6 3.0–5.5 2.0 2.0

IH

Input Voltage HLH

Maximum An, Bn, PLHIN, DIR, HD 3.0–3.6 3.0–5.5 0.8 0.8

IL

Input Voltage HLH

Minimum Input An, Bn, PLHIN, DIR, HD 3.3 5.0 0.4 0.4

T

Hysteresis C

Minimum HIGH An, HLH 3.0 3.0 2.8 2.8

OH

Level Output 3.0 3.0 2.4 2.4 IOH = −4 mA

Voltage Bn, Y

n

IN

n

IN

n

HLH

IN

n

Bn, Y

n

PLH 3.15 3.15 3.1 3.1 IOH = −500 µA

= 0°CTA = −40°C

T

V

V

CC

CC—Cable

(V)

3.0–3.6 3.0–5.5 2.3 2.3

3.0–3.6 3.0–5.5 2.6 2.6

3.0–3.6 3.0–5.5 0.8 0.8

3.0–3.6 3.0–5.5 1.6 1.6

3.3 5.0 0.8 0.8 V

3.3 5.0 0.2 0.2 V

3.0 3.0 2.0 2.0 IOH = −14 mA

3.0 4.5 2.23 2.23 IOH = −14 mA

(V)

A

to +70°Cto +85°C

Guaranteed Limits

Units Conditions

VHIGH Level C

VLOW Level C

+

V

–V

T

+

V

–V

T

+

–V

T

IOH = −50 µA

V

3 www.fairchildsemi.com

−

T

−

T

−

T

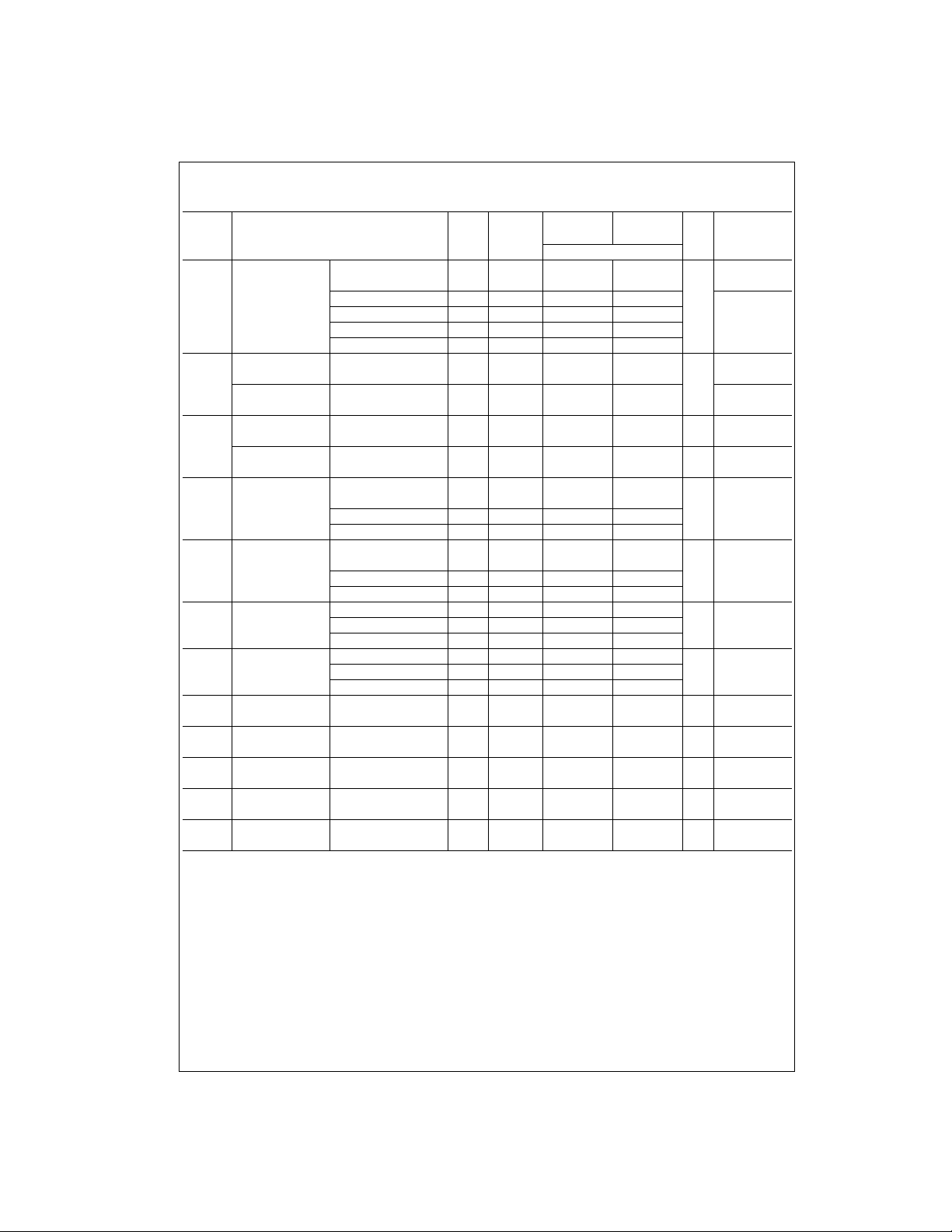

DC Electrical Characteristics (Continued)

V

V

CC

Symbol Parameter

V

74LVX161284

Maximum LOW An, HLH 3.0 3.0 0.2 0.2

OL

Level Output 3.0 3.0 0.4 0.4 I

Voltage Bn, Y

n

, Y

B

n

n

PLH 3.0 3.0 0.85 0.95 I

PLH 3.0 4.5 0.8 0.9 IOL = 84 mA

R

Maximum Output B1–B8, Y9–Y

D

13

Impedance 3.3 5.0 55 55

Minimum Output B

1–B8

, Y9–Y

13

Impedance 3.3 5.0 35 35

R

I

I

I

I

I

IH

IL

OZH

OZL

OFF

Maximum Pull-Up B1–B8, Y9–Y

P

Resistance C

Minimum Pull-Up B1–B8, Y9–Y

Resistance C14–C

13,

14–C17

13

17

Maximum Input A9–A13, PLHIN, 3.6 3.6 1.0 1.0

Current in HD, DIR, HLH

HIGH State C14–C

C14–C

IN

17

17

Maximum Input A9–A13, PLHIN,3.63.6−1.0 −1.0 µAVI = 0.0V

Current in HD, DIR, HLH

LOW State C14–C

C14–C

Maximum Output A1–A

Disable Current B1–B

(HIGH) B1–B

Maximum A1–A

Output Disable B

1–B8

Current (LOW) B1–B

IN

17

17

8

8

8

8

8

Power Down B1–B8, Y9–Y13,

Output Leakage PLH

I

OFF

I

OFF—ICC

I

OFF—ICC2

I

CC

Power Down

Input Leakage

C14–C17, HLH

IN

Power Down

Leakage to V

CC

Power Down Leakage

to V

CC—Cable

Maximum Supply 3.6 3.6 45 45 mA VI = VCC or GND

Current 3.6 5.5 70 70 mA VI = VCC or GND

Note 5: Output impedance is m easured with the outp ut ac tive LOW and active HIGH (HD = HIGH).

Note 6: Power-down le ak age to V

to 5.5V and measuring the resulting I

Note 7: This parameter is guaranteed but not tested, characterized only.

or V

CC

CC

is tested by simultaneously forcing all pins on the cable-side (B1–B8, Y9–Y13, PLH, C14–C17 and HLHIN)

CC—Cable

or I

CC—Cable

.

CC—Cable

(V)

(V)

3.0 3.0 0.8 0.8 IOL = 14 mA

3.0 4.5 0.77 0.77 IOL = 14 mA

3.3 3.3 60 60

3.3 3.3 30 30

3.3 3.3 1650 1650

3.3 5.0 1650 1650

3.3 3.3 1150 1150

3.3 5.0 1150 1150

3.6 3.6 50.0 50.0 VI = 3.6V

3.6 5.5 100 100 VI = 5.5V

3.6 3.6 −3.5 −3.5 mA VI = 0.0V

3.6 5.5 −5.0 −5.0 mA VI = 0.0V

3.6 3.6 20 20 µAVO = 3.6V

3.6 3.6 50 50 µAVO = 3.6V

3.6 5.5 100 100 µAVO = 5.5V

3.6 3.6 −20 −20 µAVO = 0.0V

3.6 3.6 −3.5 −3.5 mA

3.6 5.5 −5.0 −5.0 mA

0.0 0.0 100 100 µAV

0.0 0.0 100 100 µAVI = 5.5V

0.0 0.0 250 250 µA (Note 6)

0.0 0.0 250 250 µA (Note 6)

T

= 0°CTA = −40°C

A

to +70°Cto +85°C

Guaranteed Limits

Units Conditions

IOL = 50 µA

= 4 mA

OL

V

= 84 mA

OL

(Note 5)(Note 7)

Ω

(Note 5)(Note 7)

Ω

Ω

VI = 3.6V

µA

= 5.5V

O

www.fairchildsemi.com 4

Loading...

Loading...