Fairchild Semiconductor 74LVQ74SC, 74LVQ74SJX, 74LVQ74SJ, 74LVQ74SCX Datasheet

74LVQ74

Low Voltage Dual D-Type Positive Edge-Triggered

Flip-Flop

General Description

The LVQ74 is a dual D-type flip-flop with Asynchronous

Clear and Set inputs and complementary (Q, Q) outputs. Information at the input is transferred to the outputs on the

positive edge of the clock pulse. Clocktriggeringoccursat a

voltage level of the clock pulse and is not directly related to

the transition time of the positive-going pulse. After the Clock

Pulse input threshold voltage has been passed, the Data input is locked out and information present will not be transferred to the outputs until the next rising edge of the Clock

Pulse input.

Asynchronous Inputs:

LOW input to S

D

(Set) sets Q to HIGH level

LOW input to CD(Clear) sets Q to LOW level

Clear and Set are independent of clock

Simultaneous LOW on C

D

and SDmakes both Q and Q

HIGH

Features

n Ideal for low power/low noise 3.3V applications

n Guaranteed simultaneous switching noise level and

dynamic threshold performance

n Guaranteed pin-to-pin skew AC performance

n Guaranteed incident wave switching into 75Ω

Ordering Code:

Order Number Package Number Package Description

74LVQ74SC M14A 14-Lead (0.150" Wide) Molded Small Outline Integrated Circuit, SOIC JEDEC

74LVQ74SJ M14D 14-Lead Molded Small Outline Package, SOIC EIAJ

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

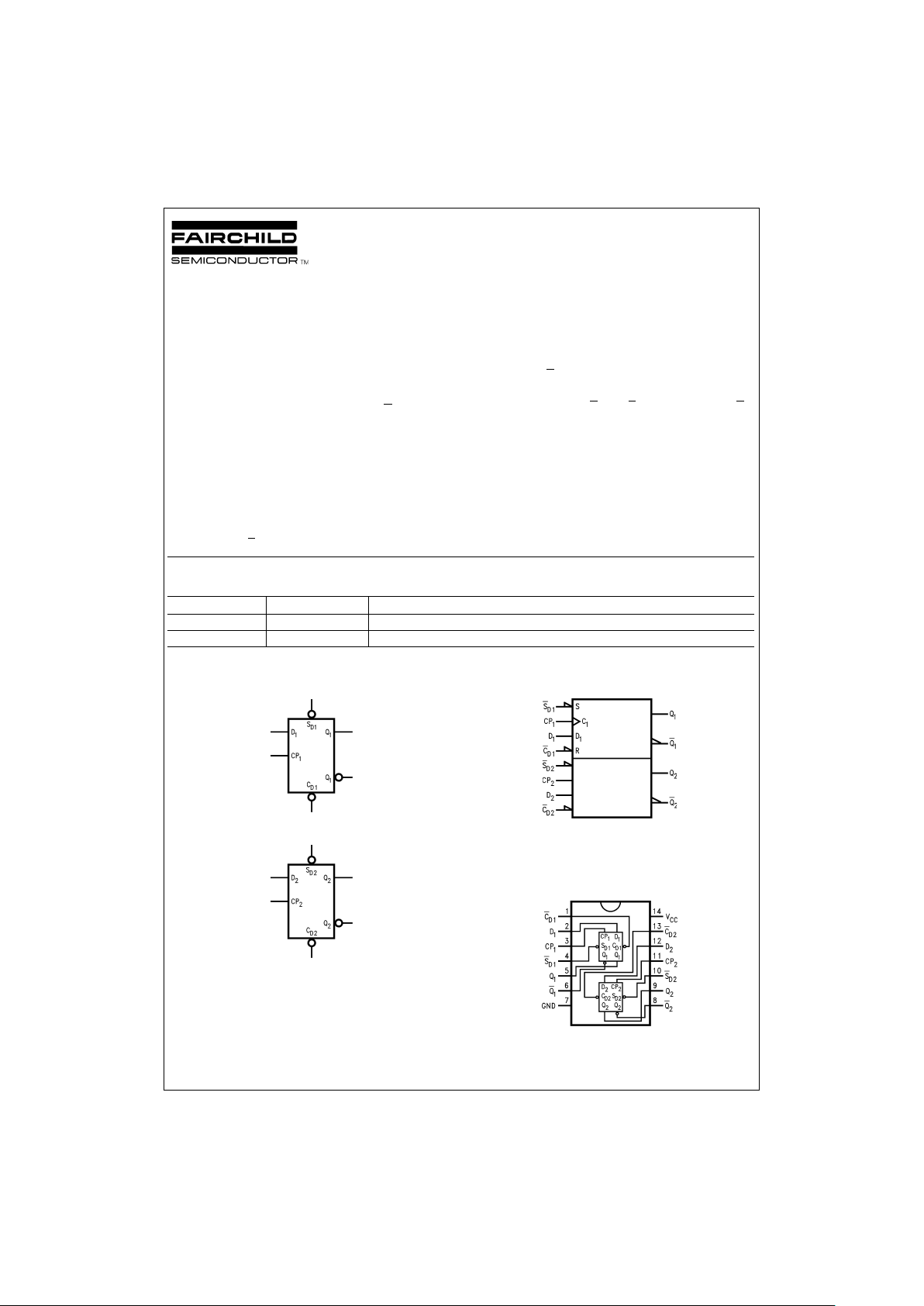

Logic Symbols

Connection Diagram

DS011347-1

DS011347-2

IEEE/IEC

DS011347-3

Pin Assignment

for SOIC JEDEC and EIAJ

DS011347-4

May 1998

74LVQ74 Low Voltage Dual D-Type Positive Edge-Triggered Flip-Flop

© 1998 Fairchild Semiconductor Corporation DS011347 www.fairchildsemi.com

Pin Descriptions

Pin Names Description

D

1,D2

Data Inputs

CP

1

,CP

2

Clock Pulse Inputs

C

D1,CD2

Direct Clear Inputs

S

D1,SD2

Direct Set Inputs

Q

1,Q1,Q2,Q2

Outputs

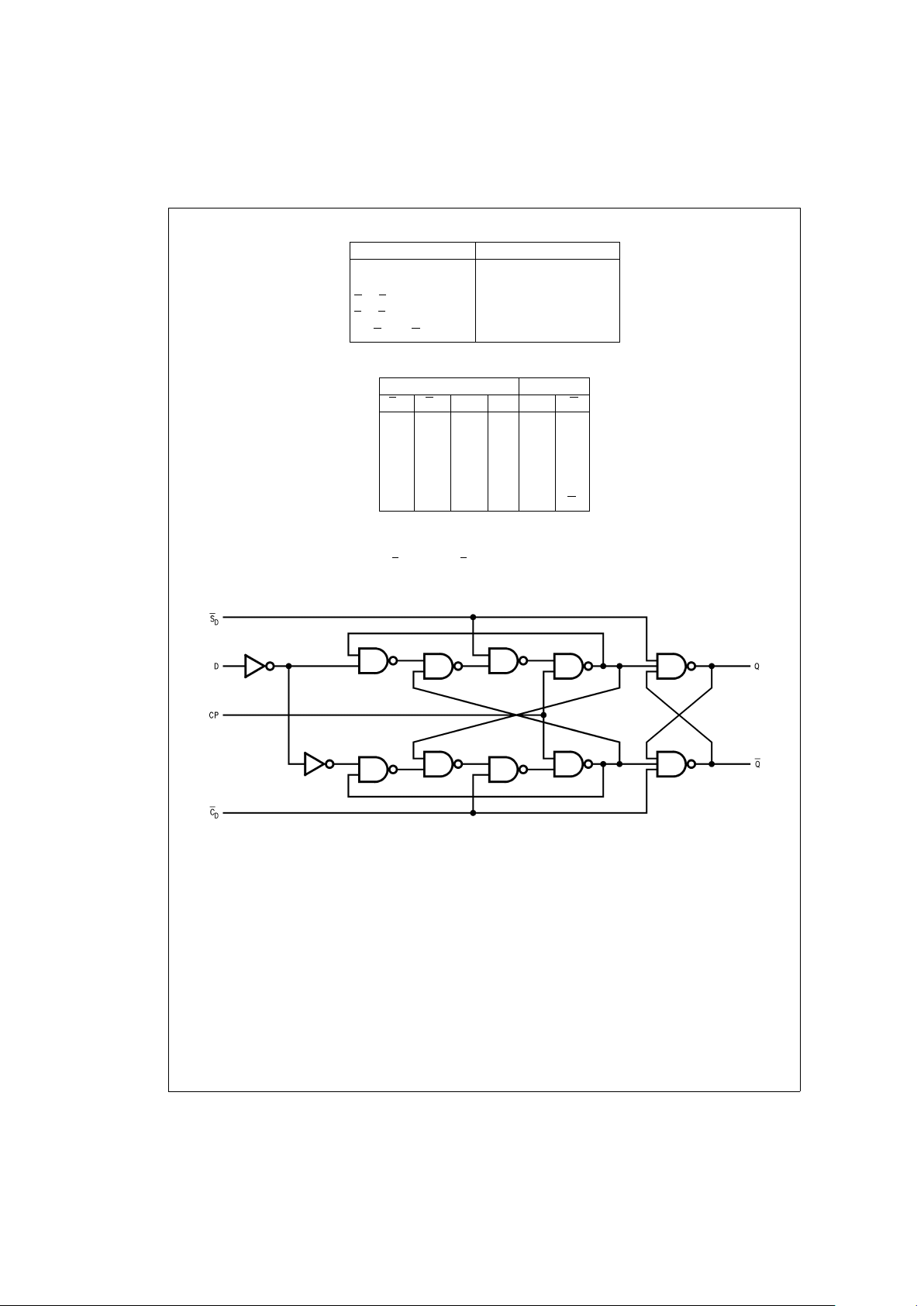

Truth Table

Inputs Outputs

S

D

CDCP D Q Q

LHXXHL

HLXXLH

LLXXHH

HH

N

HH L

HH

N

LLH

HHLXQ

0

Q

0

H=HIGH Voltage Level

L=LOW Voltage Level

X=Immaterial

N

=

LOW-to-HIGH Clock Transition

Q

0(Q0

)=Previous Q(Q) before LOW-to-HIGH Transition of Clock

Logic Diagram

DS011347-6

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com 2

Loading...

Loading...