Fairchild Semiconductor 74LVQ374SCX, 74LVQ374SC, 74LVQ374QSCX, 74LVQ374QSC, 74LVQ374MSAX Datasheet

...

74LVQ374

Low Voltage Octal D-Type Flip-Flop with 3-STATE

Outputs

General Description

The LVQ374isahigh-speed,low-poweroctalD-typeflip-flop

featuring separate D-type inputs for each flip-flop and

3-STATE outputs for bus-oriented applications. A buffered

Clock (CP) and Output Enable (OE) are common to all

flip-flops.

Features

n Ideal for low power/low noise 3.3V applications

n Implements patented EMI reduction circuitry

n Available in SOIC JEDEC, SOIC EIAJ and QSOP

packages

n Guaranteed simultaneous switching noise level and

dynamic threshold performance

n Improved latch-up immunity

n Guaranteed incident wave switching into 75Ω

n 4 kV minimum ESD immunity

n Buffered positive edge-triggered clock

n 3-STATE outputs drive bus lines or buffer memory

address registers

Ordering Code:

Order Number Package Number Package Description

74LVQ374SC M20B 20-Lead (0.300" Wide) Molded Small Outline Package, SOIC JEDEC

74LVQ374SJ M20D 20-Lead Molded Shrink Small Outline Package, SOIC EIAJ

74LVQ374QSC MQA20 20-Lead (0.150" Wide) Molded Shrink Small Outline Package, SOIC JEDEC

Devices also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

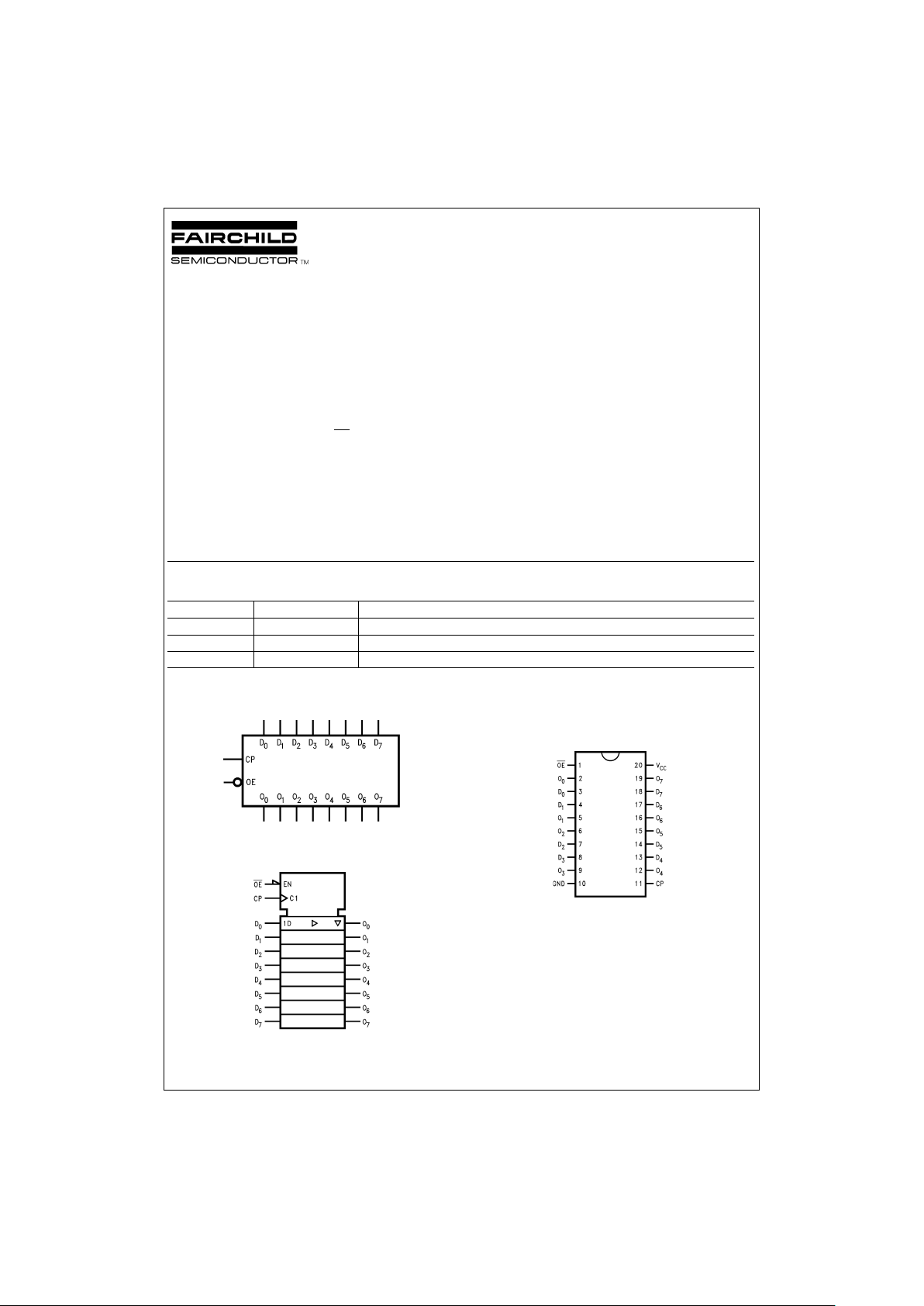

Logic Symbols Connection Diagram

DS011360-1

IEEE/IEC

DS011360-2

Pin Assignment for

SOIC and QSOP

DS011360-3

May 1998

74LVQ374 Low Voltage Octal D-Type Flip-Flop with 3-STATE Outputs

© 1998 Fairchild Semiconductor Corporation DS011360 www.fairchildsemi.com

Pin Descriptions

Pin Names Description

D

0–D7

Data Inputs

CP Clock Pulse Input

OE

3-STATE Output Enable Input

O

0–O7

3-STATE Outputs

Truth Table

Inputs Outputs

D

n

CP OE O

n

H

N

LH

L

N

LL

XXH Z

H=HIGH Voltage Level

L=LOW Voltage Level

X=Immaterial

Z=High Impedance

N

=

LOW-to-HIGH Transition

Functional Description

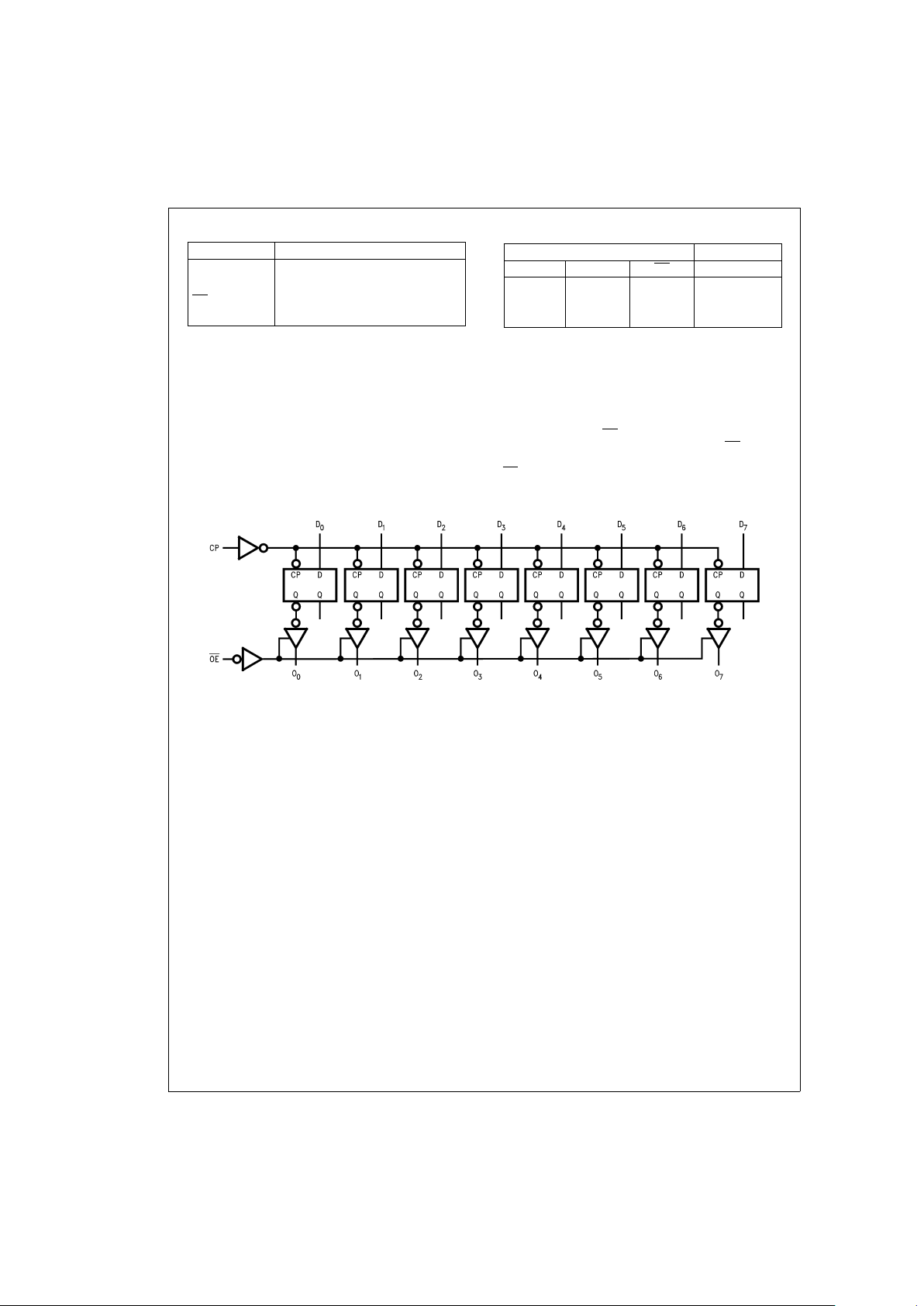

The LVQ374 consists of eight edge-triggered flip-flops with

individual D-type inputs and 3-STATE true outputs. The buffered clock and buffered Output Enable are common to all

flip-flops. The eight flip-flops will store the state of their individual D-type inputs that meet the setup and hold time re-

quirements on the LOW-to-HIGH Clock (CP) transition. With

the Output Enable (OE) LOW, the contents of the eight

flip-flops are available at the outputs. When the OE is HIGH,

the outputs go to the high impedance state. Operation of the

OE input does not affect the state of the flip-flops.

Logic Diagram

DS011360-5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com 2

Loading...

Loading...