Fairchild Semiconductor 74LVQ138SJX, 74LVQ138SJ, 74LVQ138SCX, 74LVQ138SC Datasheet

74LVQ138

Low Voltage 1-of-8 Decoder/Demultiplexer

74LVQ138 Low Voltage 1-of-8 Decoder/Demultiplexer

May 1998

General Description

The LVQ138 is a high-speed 1-of-8 decoder/demultiplexer.

This device is ideally suited for high-speed bipolar memory

chip select address decoding. The multiple input enables allow parallel expansion to a 1-of-24 decoder using just three

LVQ138devices or a 1-of-32 decoder using four LVQ138 devices and one inverter.

Features

n Ideal for low power/low noise 3.3V applications

n Guaranteed simultaneous switching noise level and

dynamic threshold performance

n Improved latch-up immunity

n Guaranteed incident wave switching into 75Ω

n 4 kV minimum ESD immunity

n Demultiplexing capability

n Multiple input enable for each expansion

n Active LOW mutually exclusive outputs

Ordering Code:

Order Number Package Number Package Description

74LVQ138SC M16A 16-Lead (0.150" Wide) Small Outline Integrated Circuit, SOIC JEDEC

74LVQ138SJ M16D 16-Lead Molded Small Outline Package, SOIC EIAJ

Devices also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

Logic Symbols Connection Diagram

Pin Assignment

for SOIC JEDEC and EIAJ

DS011350-1

IEEE/IEC

DS011350-2

Pin Descriptions

Pin Names Description

Address Inputs

Enable Inputs

Enable Input

Outputs

DS011350-4

A

E

E

O

0–A2

1–E2

3

0–O7

© 1998 Fairchild Semiconductor Corporation DS011350 www.fairchildsemi.com

Functional Description

The LVQ138 high-speed 1-of-8 decoder/demultiplexer accepts three binary weighted inputs (A

enabled, provides eight mutually exclusive active-LOW outputs (O

active-LOW (E1,E2) and one active-HIGH (E3). All outputs

). The LVQ138features three Enable inputs, two

0–O7

will be HIGH unless E1and E2are LOW and E3is HIGH.

This multiple enable function allows easy parallel expansion

0,A1,A2

) and, when

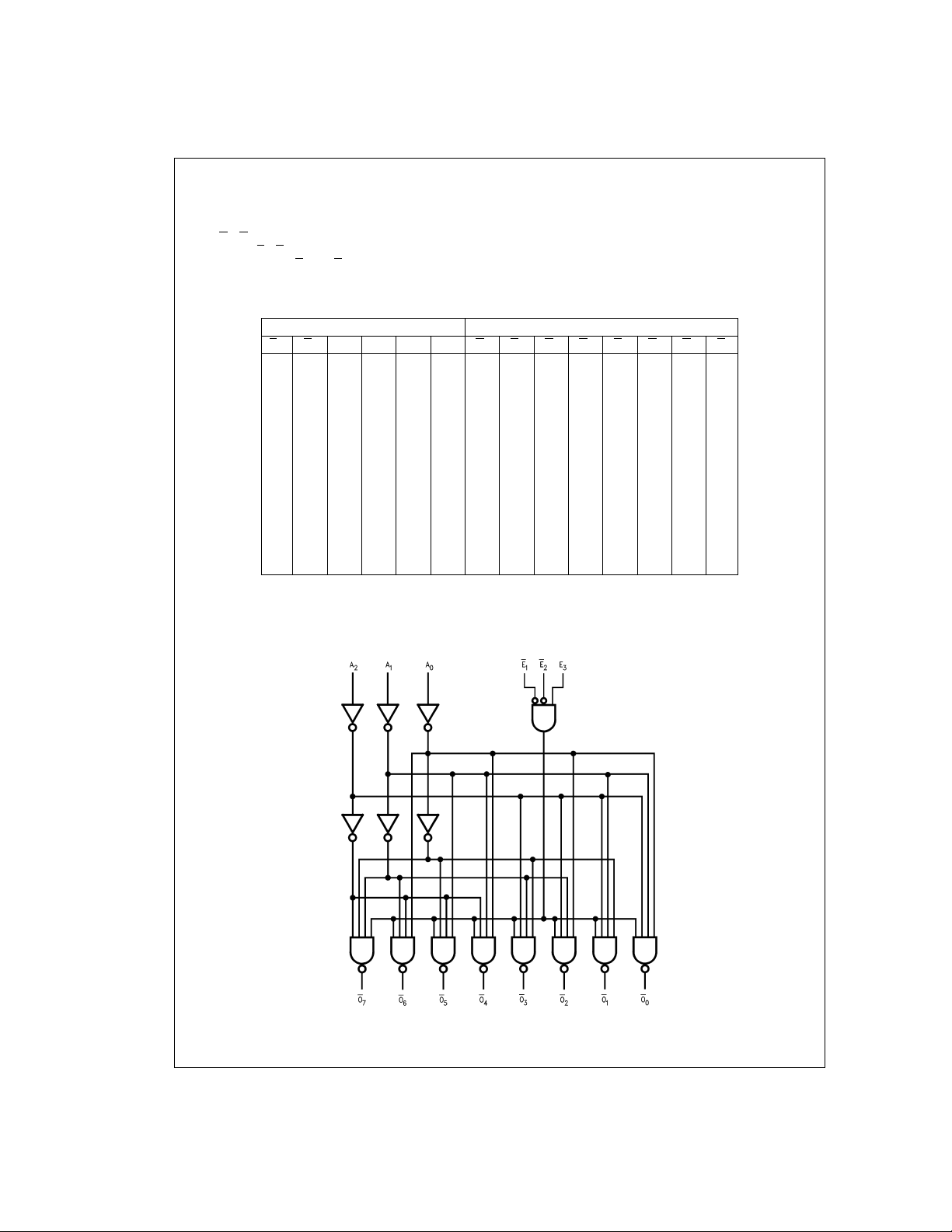

Truth Table

Inputs Outputs

E2E3A0A1A2O0O1O2O3O4O5O6O

E

1

HXXXXXHHHHHHHH

XHXXXXHHHHHHHH

XXLXXXHHHHHHHH

LLHLLLLHHHHHHH

LLHHLLHLHHHHHH

LLHLHLHHLHHHHH

LLHHHLHHHLHHHH

LLHLLHHHHHLHHH

LLHHLHHHHHHLHH

LLHLHHHHHHHHLH

LLHHHHHHHHHHHL

H=HIGH Voltage Level

L=LOW Voltage Level

X=Immaterial

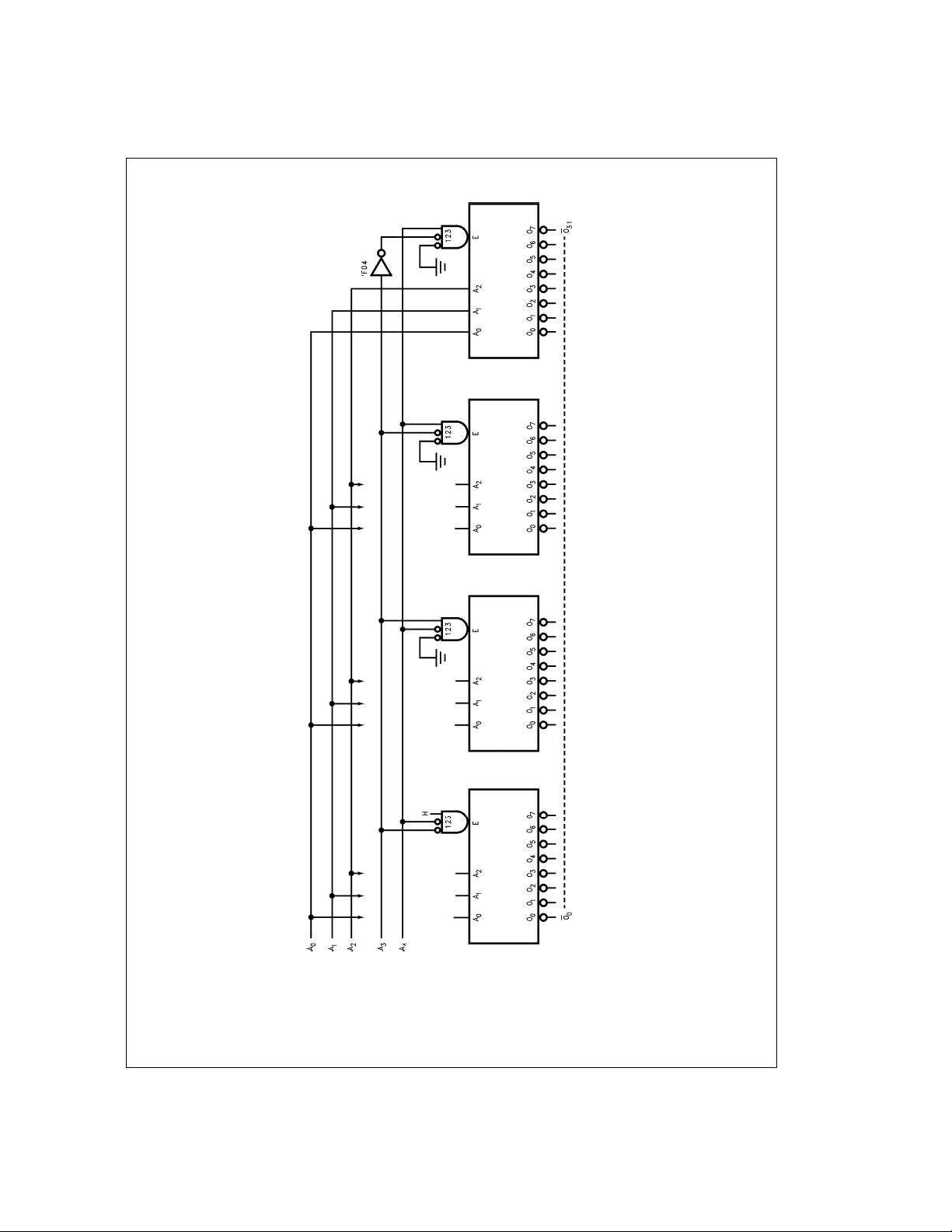

of the device to a 1-of-32 (5 lines to 32 lines) decoder with

just four LVQ138 devices and one inverter (see

Figure 1

The LVQ138 can be used as an 8-output demultiplexer by

using one of the active LOW Enable inputs as the data input

and the other Enable inputs as strobes. The Enable inputs

which are not used must be permanently tied to their appropriate active-HIGH or active-LOW state.

7

).

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com 2

DS011350-5

Logic Diagram

DS011350-6

FIGURE 1. Expansion to 1-of-32 Decoding

3 www.fairchildsemi.com

Loading...

Loading...