Fairchild Semiconductor 74LVQ00SC, 74LVQ00SJX, 74LVQ00SJ, 74LVQ00SCX Datasheet

74LVQ00

Low Voltage Quad 2-Input NAND Gate

November 1997

74LVQ00 Low Voltage Quad 2-Input NAND Gate

LVQ00

General Description

The LVQ00 contains four 2-input NAND gates.

Features

n Ideal for low power/low noise 3.3V applications

n Guaranteed simultaneous switching noise level and

dynamic threshold performance

n Guaranteed pin-to-pin skew AC performance

n Guaranteed incident wave switching into 75Ω

Ordering Code: See

Order Number Package Number Package Description

74LVQ00SC M14A 14-Lead (0.150" Wide) Molded Small Outline Integrated Circuit, SOIC JEDEC

74LVQ00SJ M14D 14-Lead Small Outline Package, SOIC EIAJ

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

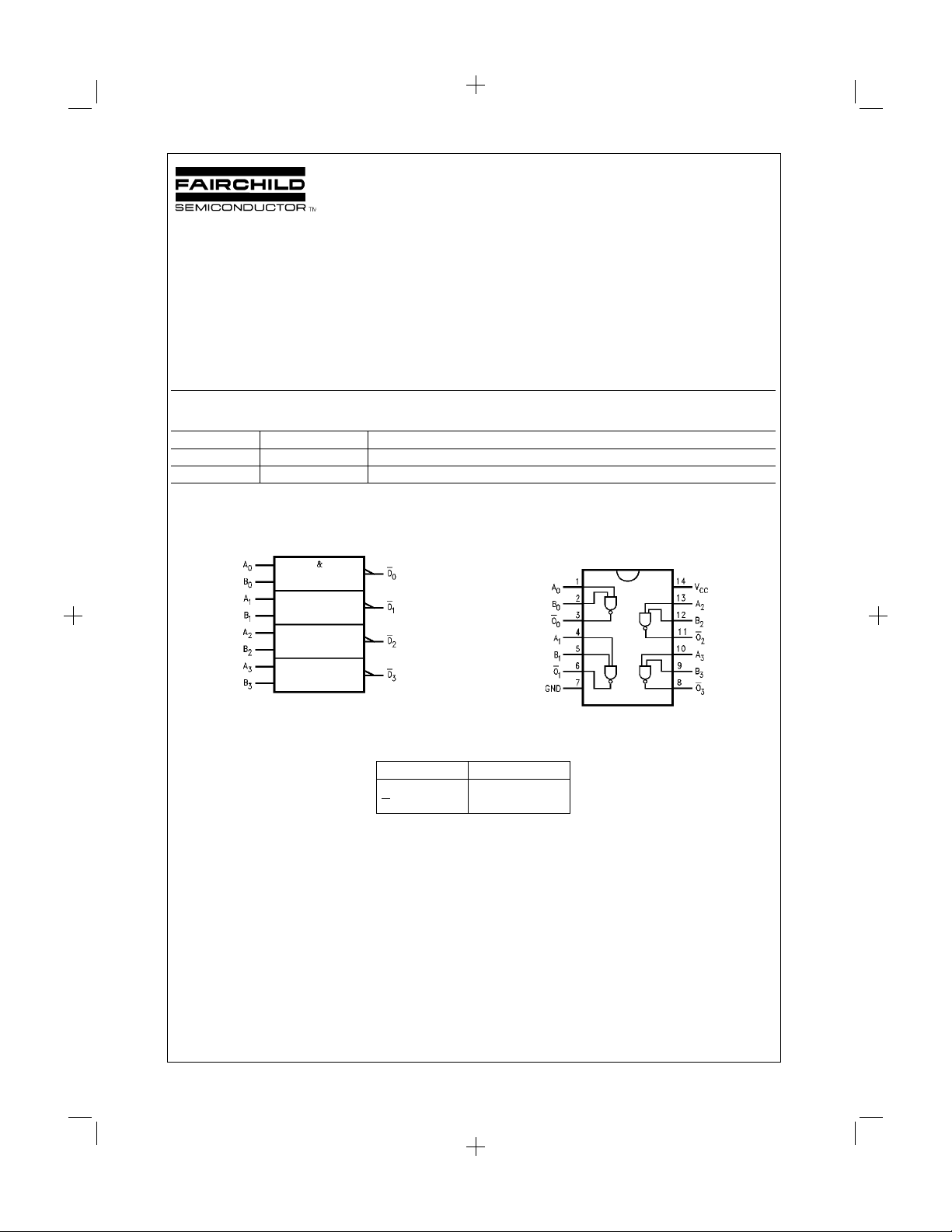

Logic Symbol Connection Diagram

IEEE/IEC

DS011341-1

Pin Assignment for

for SOIC JEDEC and EIAJ

DS011341-2

Pin Descriptions

Pin Names Description

A

O

n,Bn

n

Inputs

Outputs

© 1997 Fairchild Semiconductor Corporation DS011341 www.fairchildsemi.com

PrintDate=1997/11/10 PrintTime=09:36:39 23554 ds011341 Rev. No. 4 cmserv

Proof 1

1

Absolute Maximum Ratings (Note 1)

Supply Voltage (V

DC Input Diode Current (I

=

−0.5V −20 mA

V

I

=

V

V

I

CC

DC Input Voltage (V

DC Output Diode Current (I

=

−0.5V −20 mA

V

O

=

V

V

O

CC

DC Output Voltage (V

DC Output Source

or Sink Current (I

or Ground Current

DC V

CC

or I

(I

CC

GND

Storage Temperature (T

DC Latch-Up Source or

Sink Current

) −0.5V to +7.0V

CC

)

IK

+ 0.5V +20 mA

) −0.5V to VCC+ 0.5V

I

)

OK

+ 0.5V +20 mA

) −0.5V to VCC+ 0.5V

O

)

O

)

) −65˚C to +150˚C

STG

±

±

200 mA

±

100 mA

50 mA

Recommended Operating

Conditions

Supply Voltage (V

LVQ 2.0V to 3.6V

Input Voltage (V

Output Voltage (VO) 0VtoV

Operating Temperature (TA)

74LVQ −40˚C to +85˚C

Minimum Input Edge Rate (∆V/∆t)

from 0.8V to 2.0V

V

IN

@

3.0V 125 mV/ns

V

CC

Note 1: The “Absolute Maximum Ratings” are those values beyond which

the safety of the device cannot be guaranteed.The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The

“Recommended Operating Conditions” table will define the conditions for actual device operation.

Note 2: Unused inputs must be held HIGH or LOW. They may not float.

(Note 2)

)

CC

) 0VtoV

I

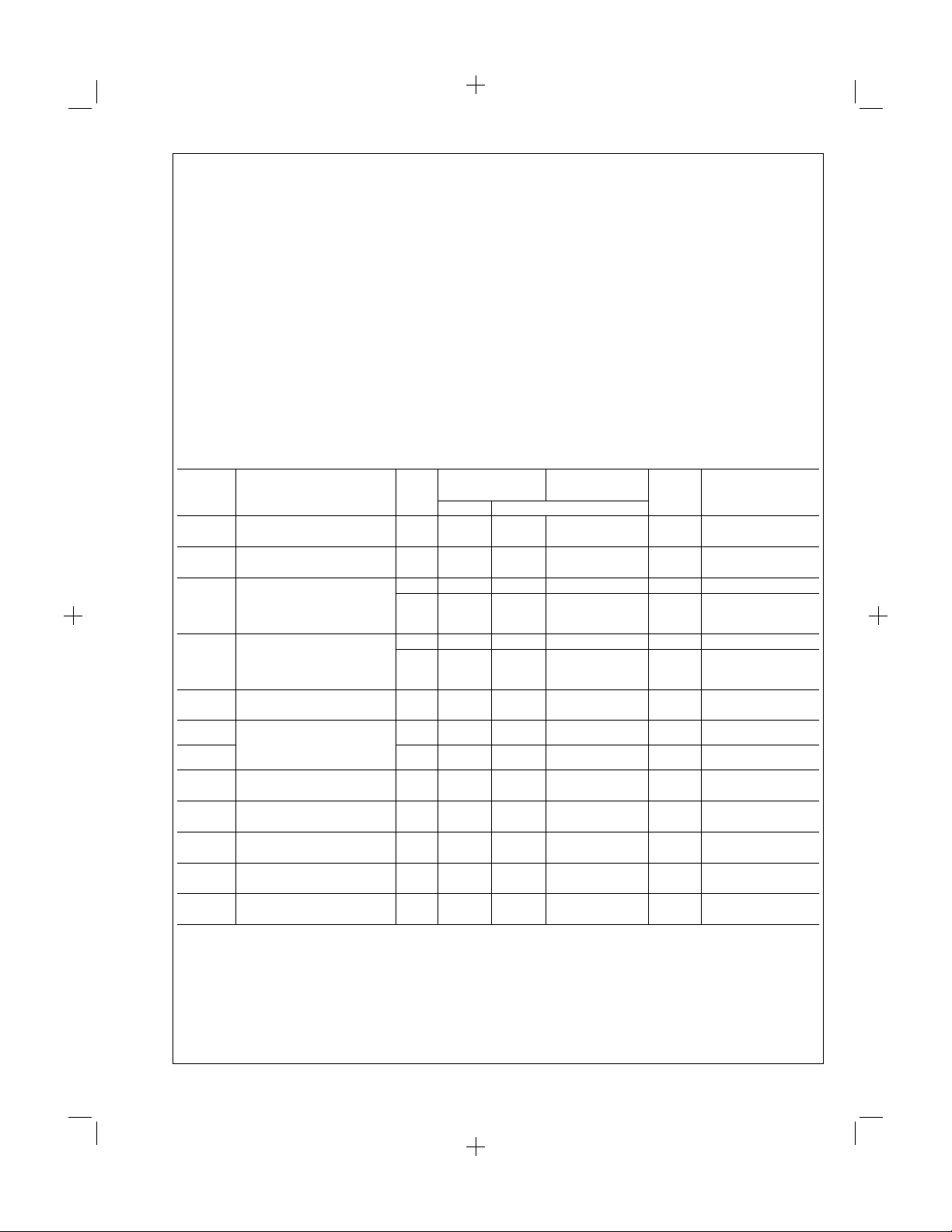

DC Electrical Characteristics

Symbol Parameter V

CC

=

T

+25˚C T

A

(V) −40˚C to +85˚C

Typ Guaranteed Limits

V

IH

Minimum High Level 3.0 1.5 2.0 2.0 V V

Input Voltage or V

V

IL

Maximum Low Level 3.0 1.5 0.8 0.8 V V

Input Voltage or V

V

OH

V

OL

I

IN

Minimum High Level

Output Voltage

Maximum Low Level

Output Voltage

Maximum Input 3.6

3.0 2.99 2.9 2.9 V I

3.0 2.58 2.48 V V

3.0 0.002 0.1 0.1 V I

3.0 0.36 0.44 V V

±

0.1

Leakage Current

I

I

I

OLD

OHD

CC

Minimum Dynamic

Output Current

(Note 4)

Maximum Quiescent 3.6 2.0 20.0 µA V

3.6 36 mA V

3.6 −25 mA V

Supply Current or GND

V

OLP

V

OLV

V

IHD

Quiet Output 3.3 0.6 1.0 V (Notes 6, 7)

Maximum Dynamic V

OL

Quiet Output 3.3 −0.5 −1.0 V (Notes 6, 7)

Minimum Dynamic V

OL

Maximum High Level 3.3 1.5 2.0 V (Notes 6, 8)

Dynamic Input Voltage

V

ILD

Maximum Low Level 3.3 1.5 0.8 V (Notes 6, 8)

Dynamic Input Voltage

Note 3: All outputs loaded; thresholds on input associated with output under test.

Note 4: Maximum test duration 2.0 ms, one output loaded at a time.

Note 5: Incident wave switching on transmission lines with impedances as low as 75Ω for commercial temperature range is guaranteed for 74LVQ.

Note 6: Worst case package.

Note 7: Max number of outputs defined as (n). Data inputs are driven 0V to 3.3V; one output at GND.

Note 8: Max number of Data Inputs (n) switching. (n − 1) inputs switching 0V to 3.3V. Input-under-test switching: 3.3V to threshold (V

f=1 MHz.

=

A

±

1.0 µA V

Units Conditions

OUT

CC

OUT

CC

=

OUT

=

IN

=

I

OH

(Note 3)

=

OUT

=

IN

=

I

OL

(Note 3)

=

V

I

OLD

(Note 5)

OHD

5)

=

IN

), 0V to threshold (V

ILD

=

0.1V

− 0.1V

=

0.1V

− 0.1V

−50 µA

or V

V

IL

IH

−12 mA

50 µA

or V

V

IL

IH

12 mA

, GND

CC

=

0.8V Max

=

2.0V Min (Note

V

CC

CC

CC

),

IHD

www.fairchildsemi.com 2

PrintDate=1997/11/10 PrintTime=09:36:41 23554 ds011341 Rev. No. 4 cmserv Proof 2

Loading...

Loading...