© 1999 Fairchild Semiconductor Corporation DS009556 www.fairchildsemi.com

April 1988

Revised August 1999

74F545 Octal Bidirectional Transceiver with 3-STATE Outputs

74F545

Octal Bidirectional Transceiver with 3-STATE Outputs

General Description

The 74F545 is an 8-bit, 3-STATE, high-speed transceiver. It

provides bidirectiona l drive for bus-oriented microp rocessor and digital communicat ions systems. Straight throu gh

bidirectional transceivers are featured, with 24 mA bus

drive capability on the A Ports and 64 mA bus drive capability on the B Ports.

One input, Transmit/Receive (T/R

) determines the direction

of logic signals through the bidirectional transceiver. Transmit enables data from A-t o-B Ports; Recei ve enables da ta

from B-to-A Ports. The Output Enable input disables both A

and B Ports by placing them in a 3-STATE condition.

Features

■ Higher drive than 8304

■ 8-bit bidirectional data flow reduces system package

count

■ 3-STATE inputs/outputs for interfaci ng with bus-orien ted

systems

■ 24 mA and 64 mA bus drive capability on A and B Ports,

respectively

■ Transmit/Receive and Output Enable simplify control

logic

■ Guarante ed 4000V minimum ESD protection

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

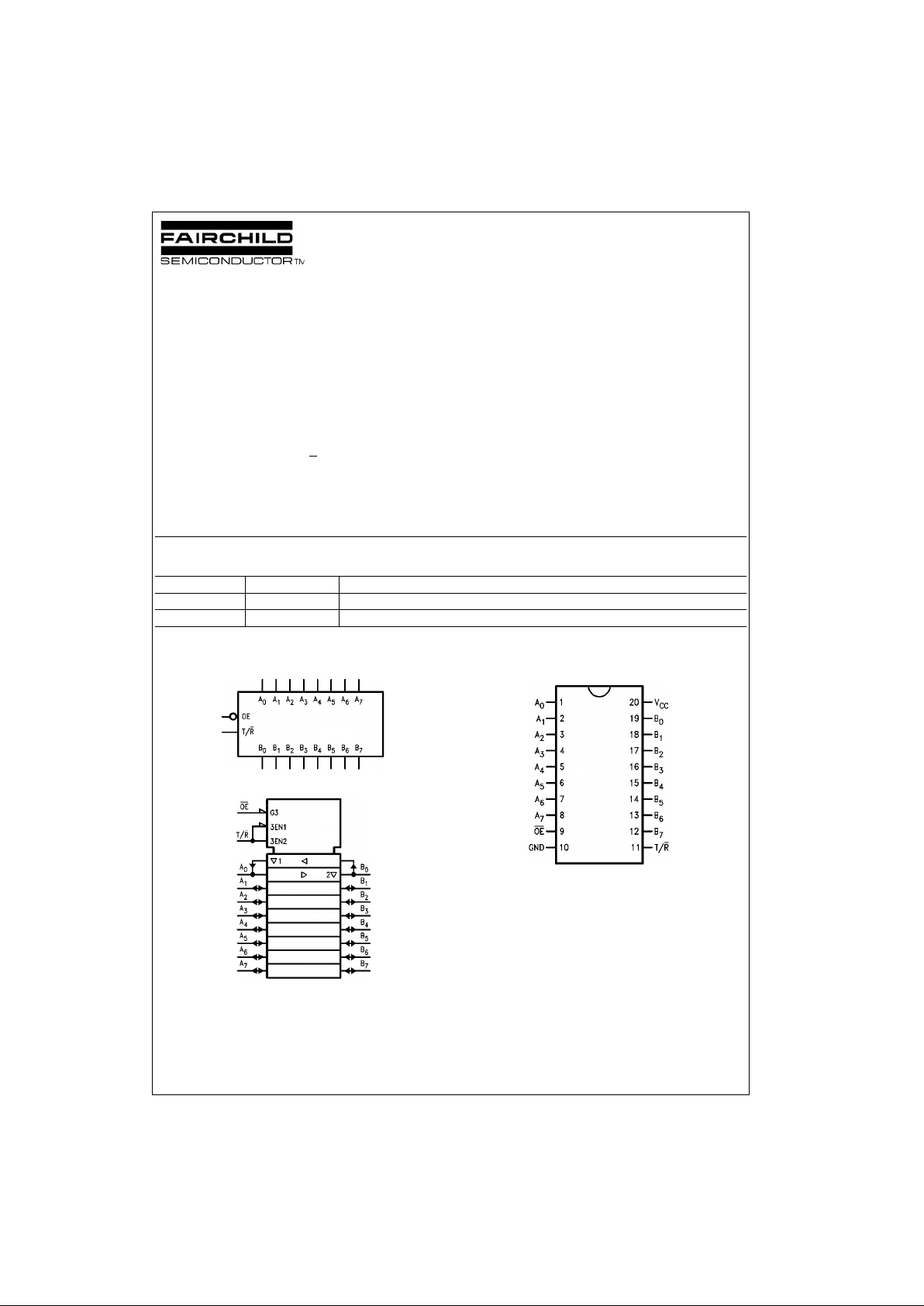

Logic Symbols

IEEE/IEC

Connection Diagram

Order Number Package Number Package Description

74F545SC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

74F545PC N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

74F545

Unit Loading/Fan Out

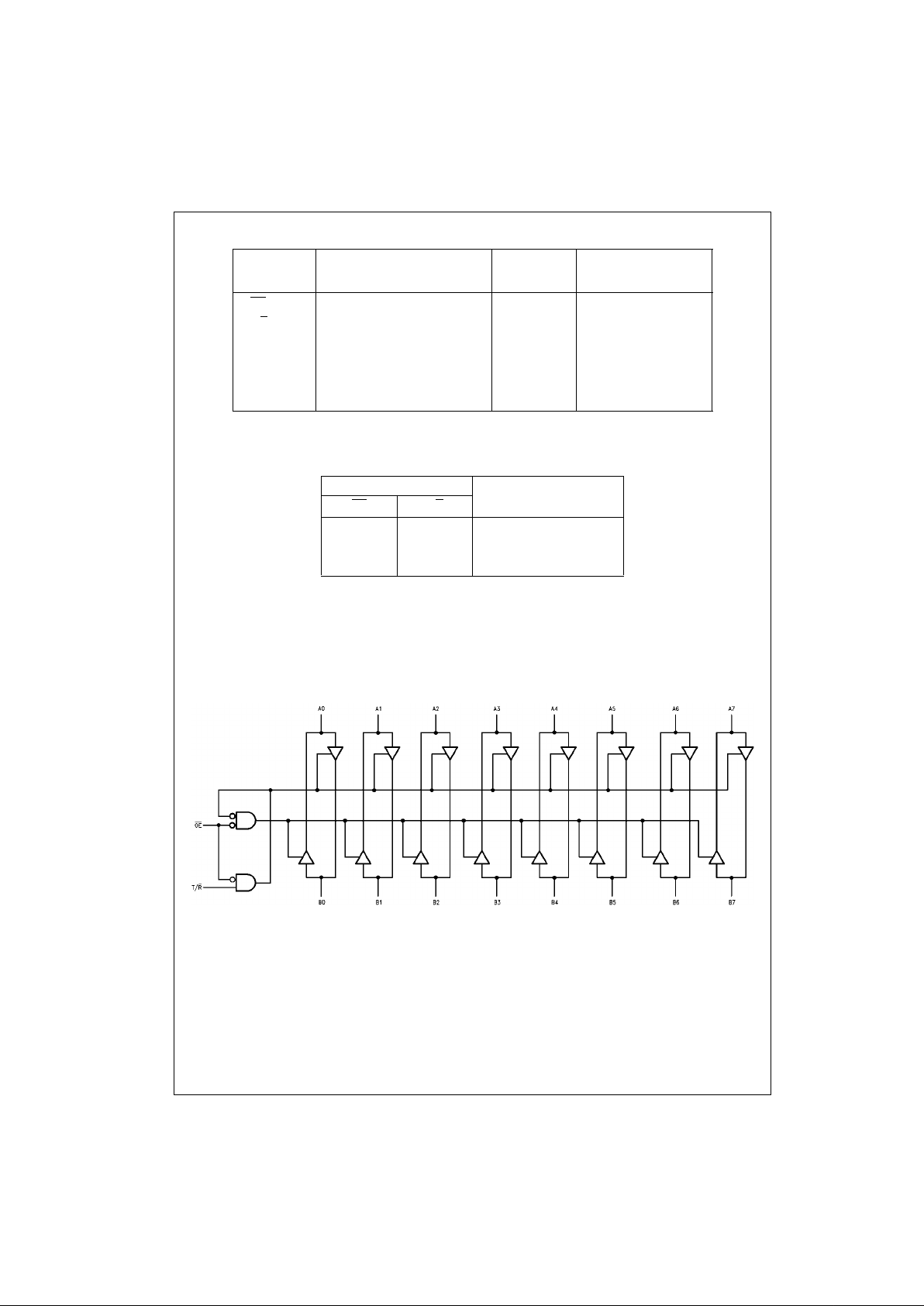

Truth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

Logic Diagram

Please note that this diagram is provided o nly f or t he understanding of lo gic operations and should not be used to estimate propagation delays.

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

OE Output Enable Input (Active LOW) 1.0/2.0 20 µA/−1.2 mA

T/R

Transmit/Receive Input 1.0/2.0 20 µA/−1.2 mA

A

0–A7

Side A 3-STATE Inputs or 3.5/1.083 70 µA/−650 µA

3-STATE Outputs 150/40 (33.3) −3 mA/24 mA (20 mA)

B

0–B7

Side B 3-STATE Inputs or 3.5/1.083 70 µA/−650 µA

3-STATE Outputs 600/106.6 (80) −12 mA/64 mA (48 mA)

Inputs Outputs

OE

T/R

L L Bus B Data to Bus A

L H Bus A Data to Bus B

HXHigh Z

Loading...

Loading...