Fairchild Semiconductor 74F538SJ, 74F538SCX, 74F538SC, 74F538PC Datasheet

© 1999 Fairchild Semiconductor Corporation DS009551 www.fairchildsemi.com

April 1988

Revised August 1999

74F538 1-of-8 Decoder with 3-STATE Outputs

74F538

1-of-8 Decoder with 3-STATE Outputs

General Description

The 74F538 decoder/dem ultiplexer acce pts three Address

(A

0–A2

) input signals and decodes them to select one of

eight mutually exclusive outputs. A polarity control input (P)

determines whether th e outputs are active LOW or active

HIGH. A HIGH Signal on eith er of the active LOW Outp ut

Enable (OE

) inputs forces all output s to the high impedance state. Two active HIGH and two act ive LOW input

enables are available for easy e xpan sion to 1-o f 32 decoding with four packages, o r for data de mul tiplexin g to 1 -of-8

or 1-of-16 destinations.

Features

■ Output polarity control

■ Data demultiplexing capability

■ Multiple enables for expansion

■ 3-STATE outputs

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

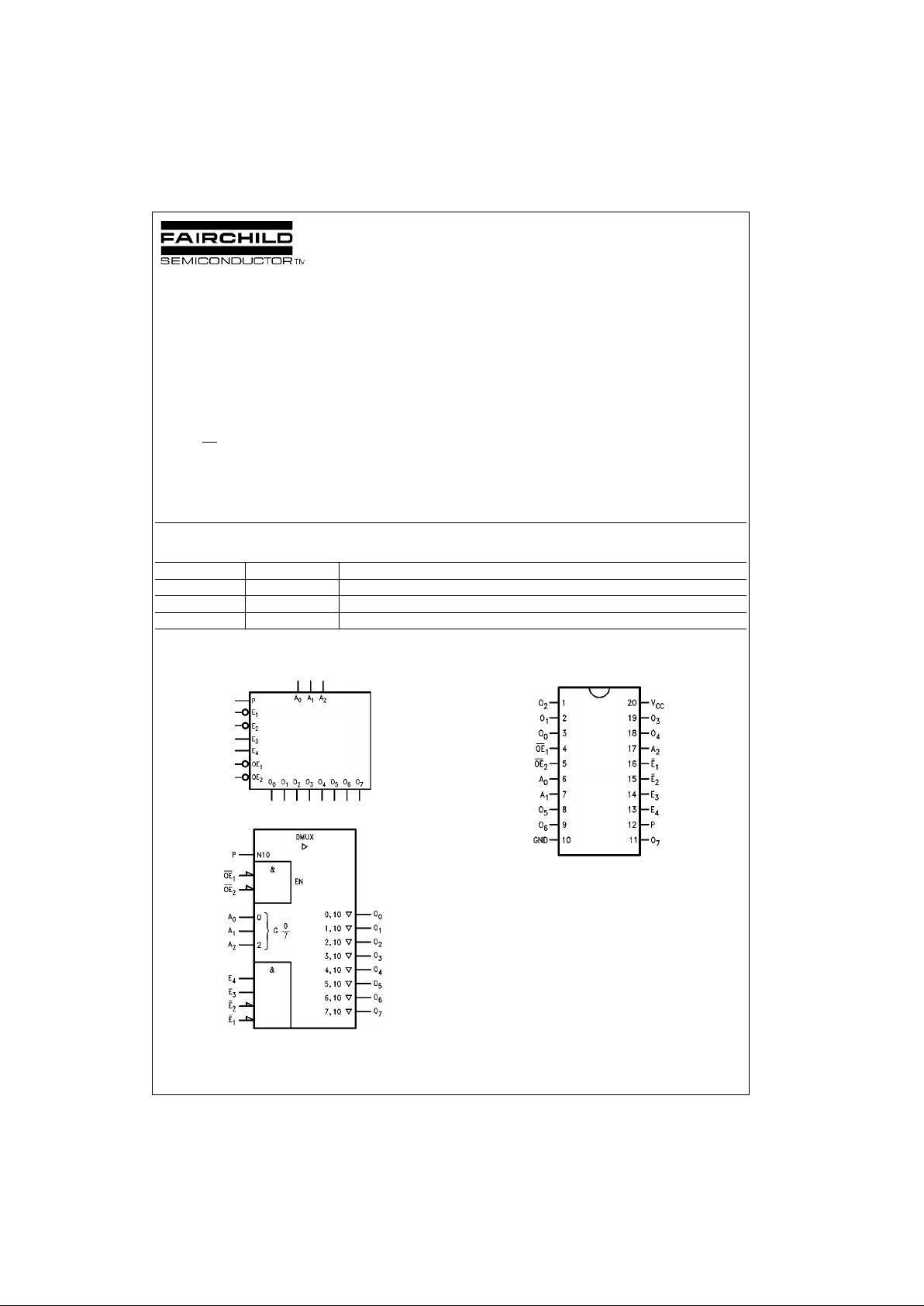

Logic Symbols

IEEE/IEC

Connection Diagram

Order Number Package Number Package Description

74F538SC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

74F538SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F538PC N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

74F538

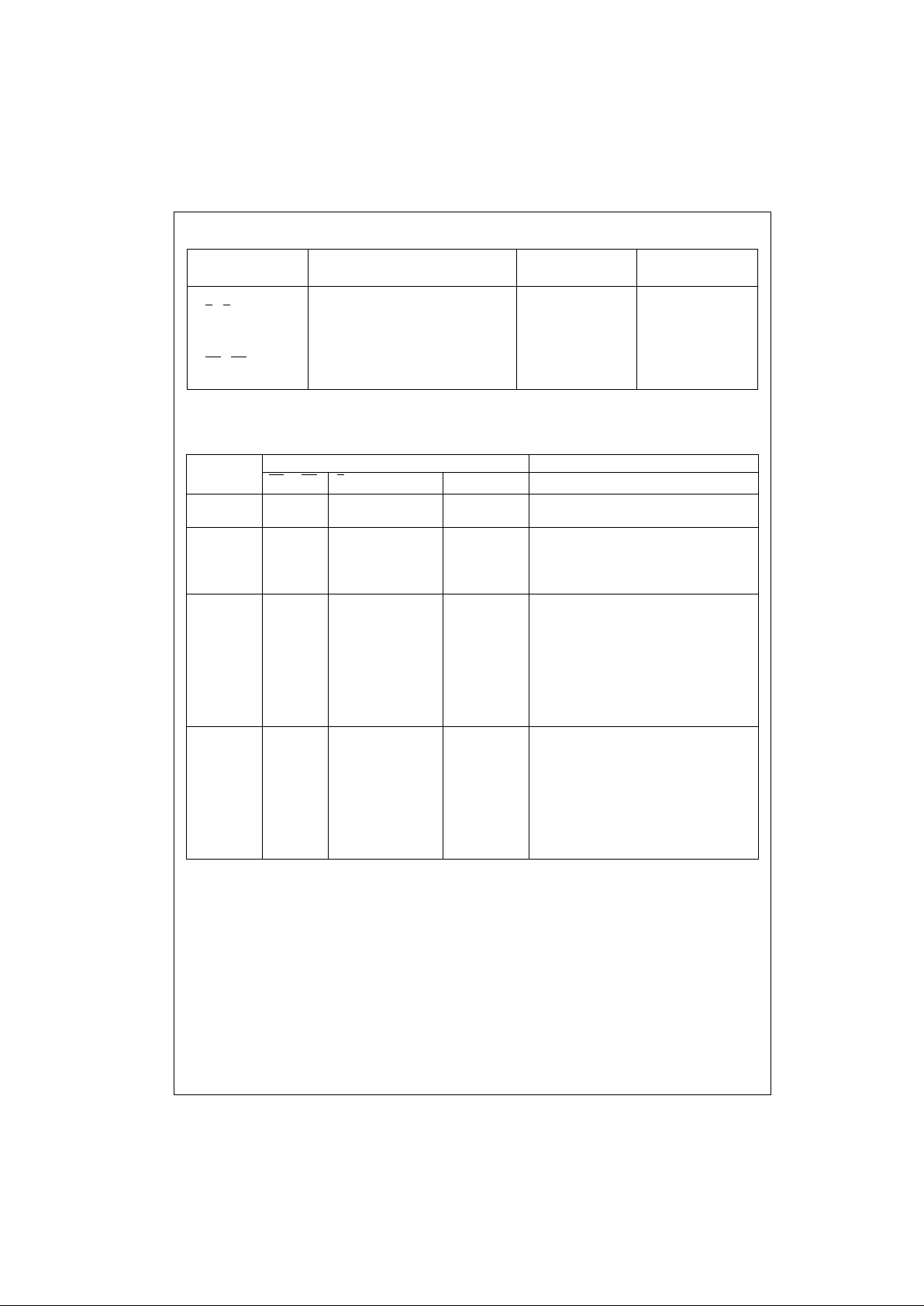

Unit Loading/Fan Out

Truth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

A0–A

2

Address Inputs 1.0/1.0 20 µA/−0.6 mA

E

1

, E

2

Enable Inputs (Active LOW) 1.0/1.0 20 µA/−0.6 mA

E

3

, E

4

Enable Inputs (Active HIGH) 1.0/1.0 20 µA/−0.6 mA

P Polarity Control Input 1.0/1.0 20 µA/−0.6 mA

OE

1

, OE

2

Output Enable Inputs (Active LOW) 1.0/1.0 20 µA/−0.6 mA

O

0–O7

3-STATE Outputs 150/40 (33.3) −3 mA/24 mA (20 mA)

Function

Inputs Outputs

OE

1OE2E1E2E3E4A2A1A0O0O1O2O3O4O5O6O7

High H X XXXXXXXZZZZZZZZ

Impedance X HXXXXXXXZZZZZZZZ

Disable L L HXXXXXX

L L XHXXXXX Outputs Equal P Input

L L XXLXXXX

L L XXXLXXX

Active HIGH L LLLHHLLLHLLLLLLL

Output L L LLHHLLHLHLLLLLL

(P = L) L LLLHHLHLLLHLLLLL

L L LLHHLHHLLLHLLLL

L L LLHHHLLLLLLHLLL

L L LLHH HLHLLLLLHLL

L L LLHHHHLLLLLL LHL

L L LLHHHHHLLLLLLLH

Active LOW L L L LHHL LL LHHHHHHH

Output L L L LHHL LHHLHHHHHH

(P = H) L L LLHHL HLHHLHHHHH

L L L LHHLHHHHHLHHHH

L L LL HHHLLHHHHLHHH

L L L LHHHLHHHHHHLHH

L L L LHHHHLHHHHH HLH

L L L LHHHH HHH HHHHHL

3 www.fairchildsemi.com

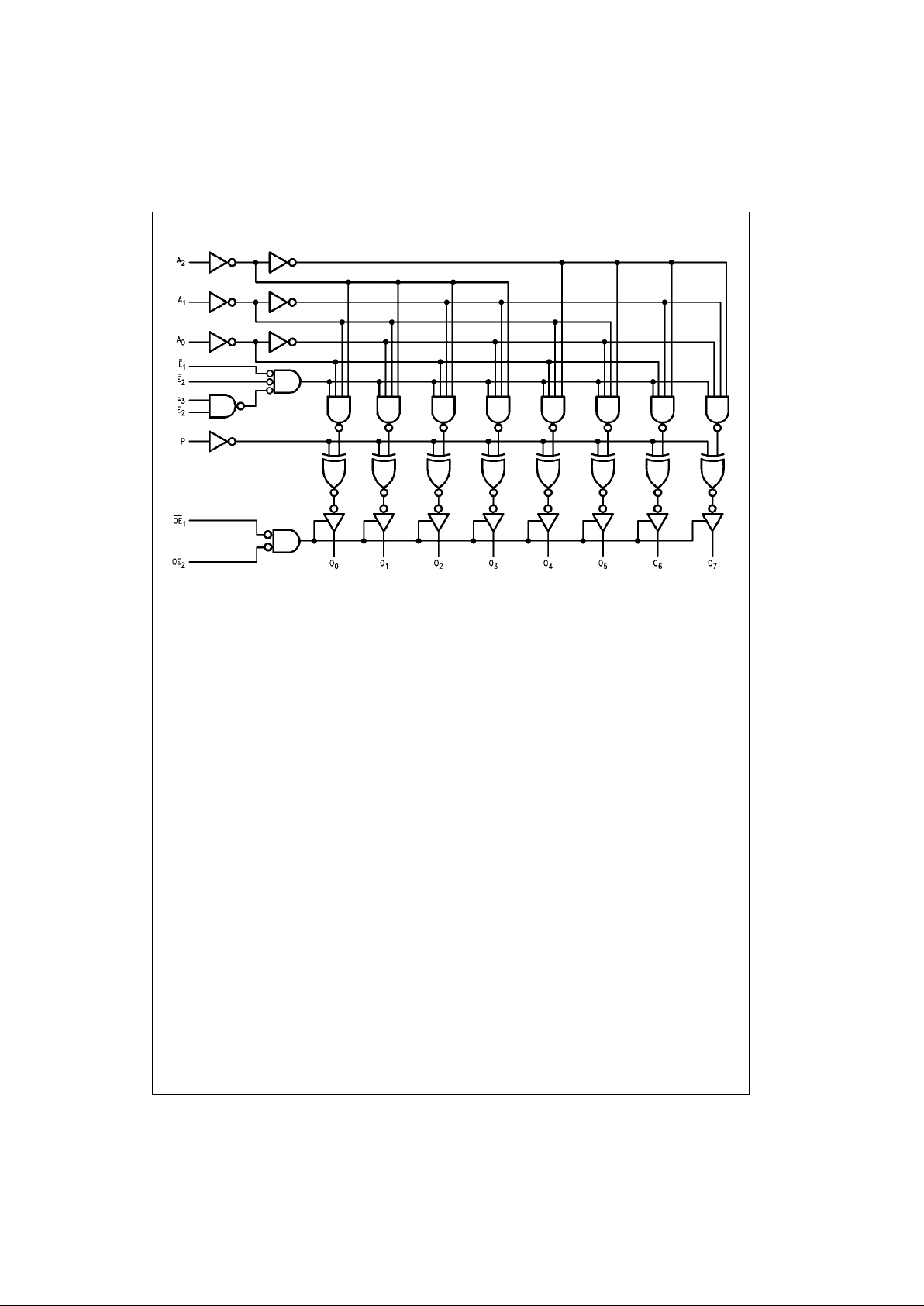

74F538

Logic Diagram

Please note that this d iagram is provided only f or t he understanding of lo gic operations and should not be used to estimat e propagation delays.

Loading...

Loading...