Fairchild Semiconductor 74F378SJX, 74F378SJ, 74F378SCX, 74F378SC, 74F378PC Datasheet

© 1999 Fairchild Semiconductor Corporation DS009526 www.fairchildsemi.com

April 1988

Revised August 1999

74F378 Parallel D-Type Register with Enable

74F378

Parallel D-Type Register with Enable

General Description

The 74F378 is a 6-bit register with a buffered common

Enable. This device is si mila r to the 74F174, but wi th com mon Enable rather than common Master Reset.

Features

■ 6-bit high-speed parallel register

■ Positive edge-triggered D-type inputs

■ Fully buffered common clock and enable inputs

■ Input clamp diodes limit high-s peed termination effects

■ Full TTL and CMOS compatible

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

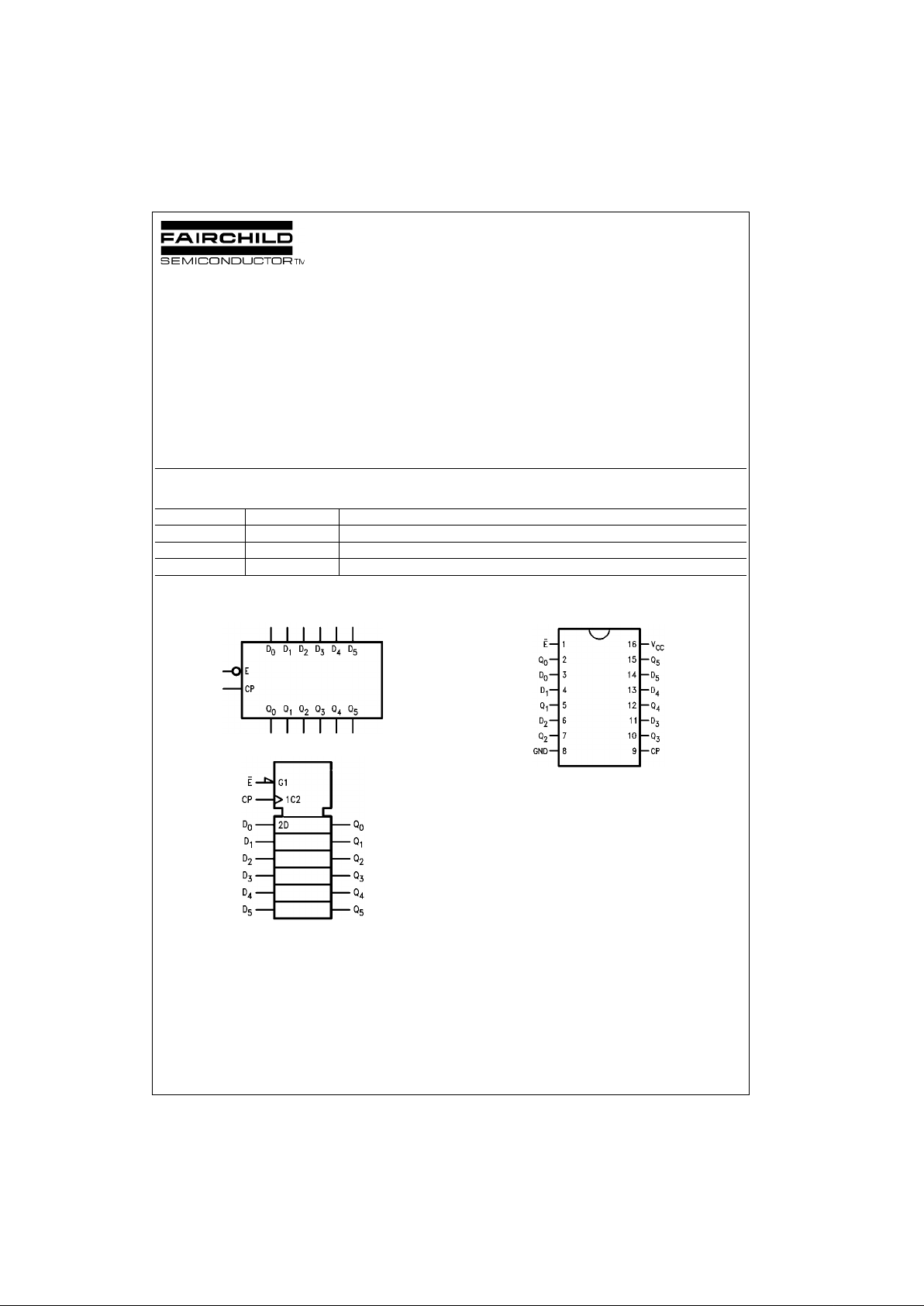

Logic Symbols

IEEE/IEC

Connection Diagram

Order Number Package Number Package Description

74F378SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F378SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F378PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

74F378

Unit Loading/Fan Out

Functional Description

The 74F378 consists of six edge-triggere d D- typ e f lip -flo ps

with individual D inputs and Q inputs. The Clock (CP ) and

Enable (E

) inputs are common to all flip-flops.

When the E

input is LOW, new data is entered into the register on the LOW-to-HIGH tra nsitio n o f th e CP in put. When

the E

input is HIGH the register will r etain the prese nt da ta

independent of the CP input.

Tr uth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

= LOW-to-HIGH Clock Transition

Logic Diagram

Please note that this diagram is provided o nly f or t he understanding of lo gic operations and should not be used to estimate propagation delays.

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

E Enable Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

D

0–D5

Data Inputs 1.0/1.0 20 µA/−0.6 mA

CP Clock Pulse Input (Active Rising Edge) 1.0/1.0 20 µA/−0.6 mA

Q

0–Q5

Outputs 50/33.3 −1 mA/20 mA

Inputs Output

E

CP D

n

Q

n

H

X No Change

L

HH

L

LL

Loading...

Loading...