Fairchild Semiconductor 74F368SJ, 74F368SCX, 74F368SC, 74F368PC Datasheet

© 1999 Fairchild Semiconductor Corporation DS009521 www.fairchildsemi.com

April 1988

Revised August 1999

74F366•74F368 Hex Inverter Buffer with 3-STATE Outputs

74F366•74F368

Hex Inverter Buffer with 3-STATE Outputs

Features

■ 3-STATE buffer outputs sink 64 mA

■ High-speed

■ Bus-oriented

■ High impedance npn base inputs for reduced loading

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

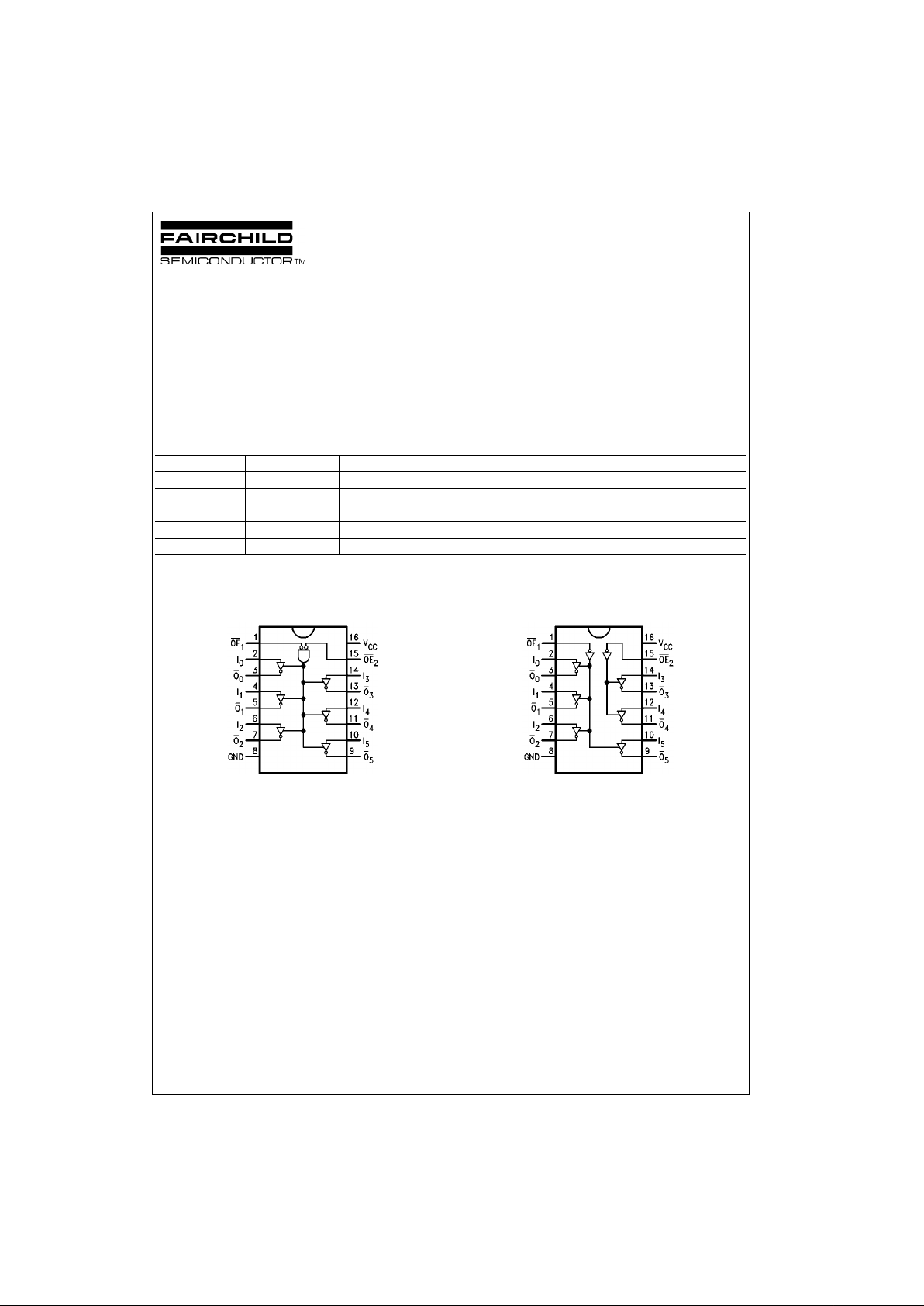

Connection Diagrams

74F366 74F368

Order Number Package Number Package Description

74F366SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F366PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

74F368SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F368SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F368PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

74F366•74F368

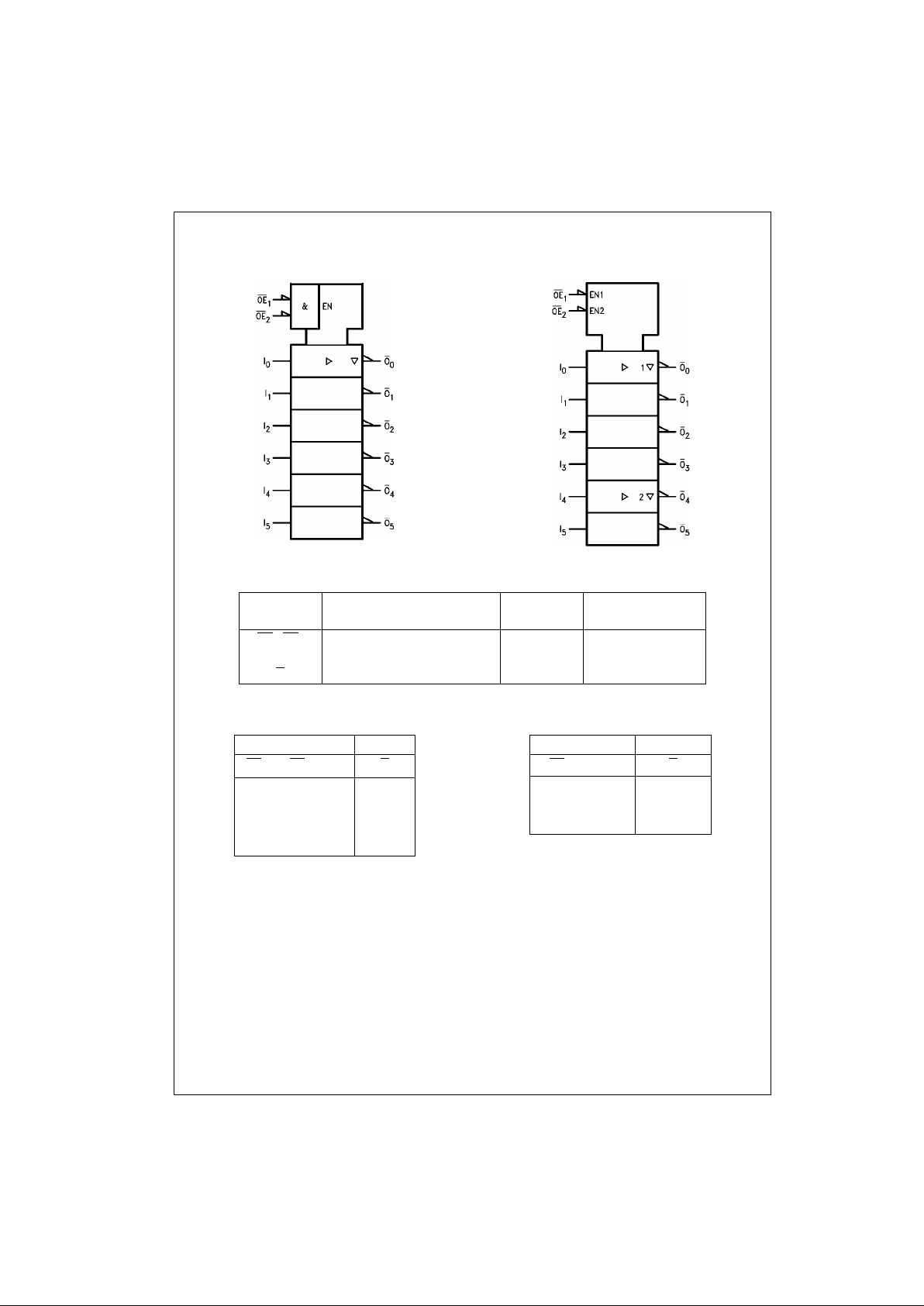

Logic Symbols

IEEE/IEC

74F366

IEEE/IEC

74F368

Unit Loading/Fan Out

Function Tables

74F366 74F368

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

OE1, OE

2

Output Enable Input (Active LOW) 1.0/0.033 20 µA/−20 µA

I

n

Input 1.0/0.033 20 µA/−20 µA

O

n

, O

n

Outputs 600/106.6 (80) −12 mA/64 m A (48 mA)

Inputs Output

OE

1

OE

2

IO

LLLH

LLHL

XHX Z

HXX Z

Inputs Output

OE

IO

LL H

LH L

HX Z

L = LOW Voltage Level X = Immaterial

H

= HIGH Voltage Level Z = High Impedance

Loading...

Loading...