Fairchild Semiconductor 74F269SPC, 74F269SCX, 74F269SC, 74F269CW Datasheet

© 1999 Fairchild Semiconductor Corporation DS009510 www.fairchildsemi.com

April 1988

Revised August 1999

74F269 8-Bit Bidirectional Binary Counter

74F269

8-Bit Bidirectional Binary Counter

General Description

The 74F269 is a fully synchronous 8-stage up/down

counter featuring a preset capability for programmable

operation, carry lookah ead for easy cascading a nd a U/D

input to control the di re ction of c oun ti ng . Al l stat e cha ng es,

whether in counting or para llel loadi ng, are initiated by the

rising edge of the clock.

Features

■ Synchronous counting and loading

■ Built-in lookahead carry capability

■ Count frequency 100 MHz

■ Supply current 113 mA typ

■ 300 mil slimline package

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

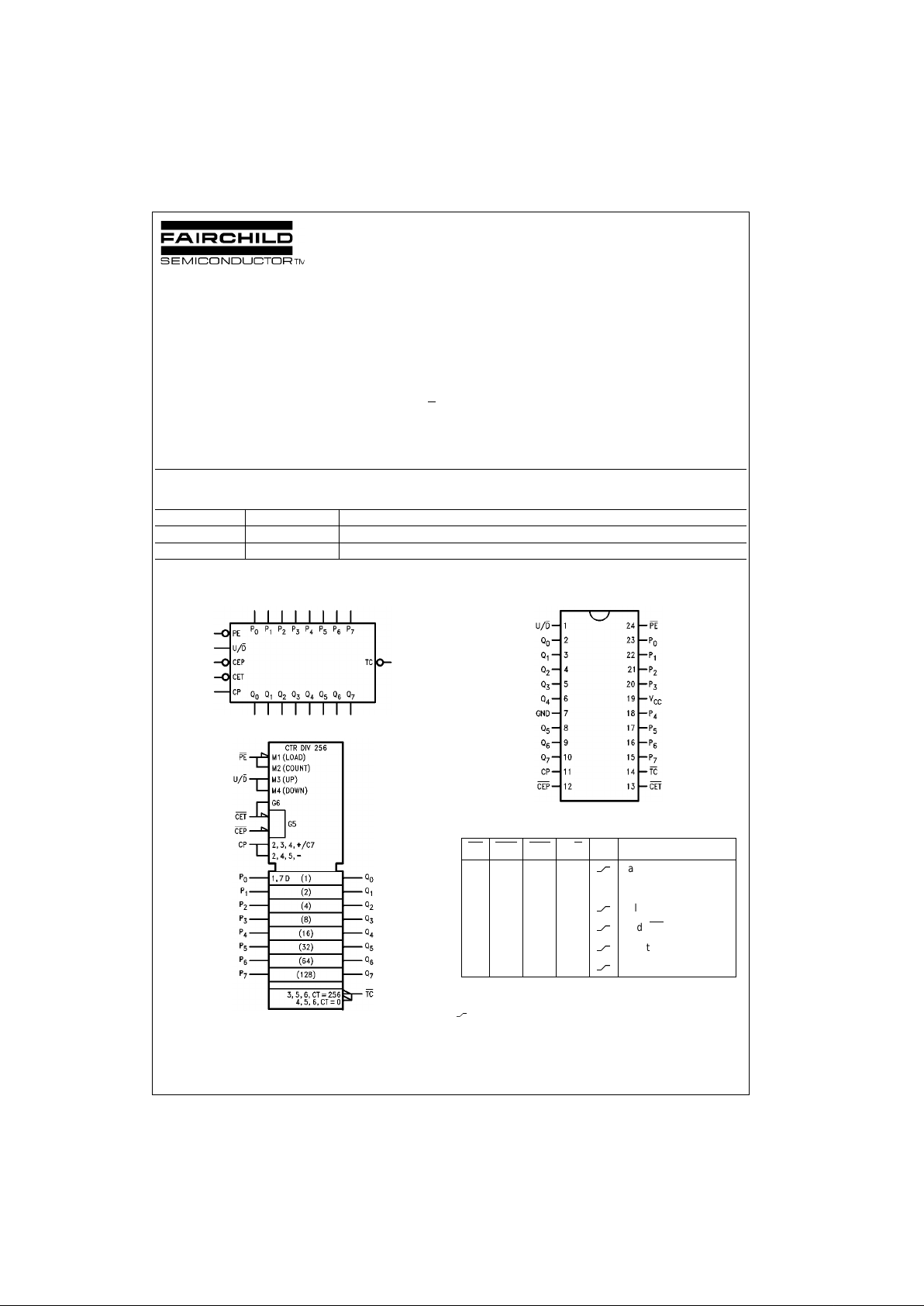

Logic Symbols

IEEE/IEC

Connection Diagram

Function Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

= Transition LOW-to-HIGH

Order Number Package Number Package Description

74F269SC M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

74F269SPC N24C 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

PE CEP CET U/D CP Function

LXXX

Parallel Load All

Flip-Flops

HH X X

Hold

HXH X

Hold (TC Held HIGH)

HL L H

Count Up

HLLL

Count Down

www.fairchildsemi.com 2

74F269

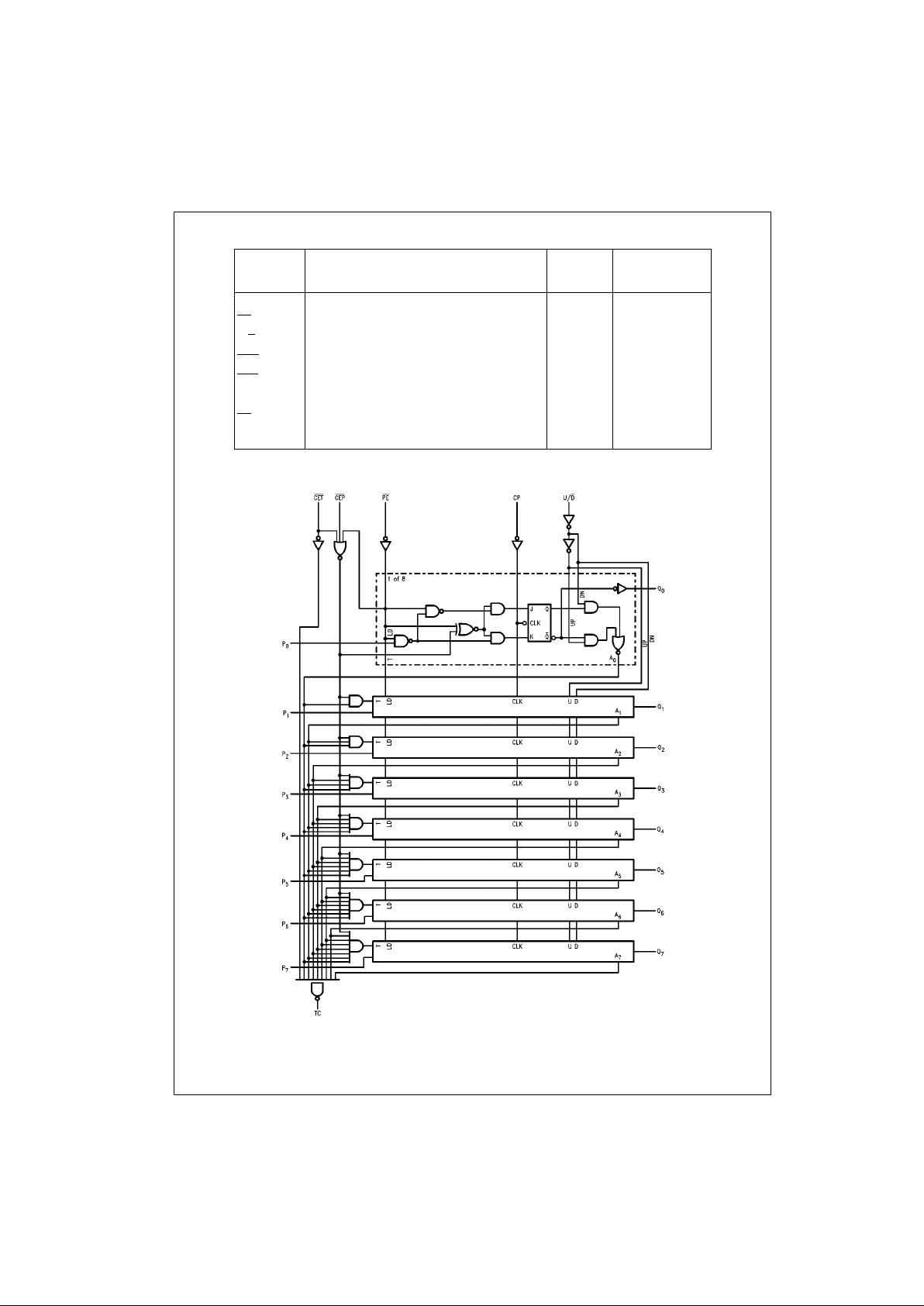

Unit Loading/Fan Out

Logic Diagram

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

P0–P

7

Parallel Data Inputs 1.0/1.0 20 µA/−0.6 mA

PE

Parallel Enable Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

U/D

Up-Down Count Control Input 1.0/1.0 20 µA/−0.6 mA

CEP

Count Enable Parallel Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

CET

Count Enable Trickle Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

CP Clock Input 1.0/1.0 20 µA/−0.6 mA

TC

Terminal Count Output (Active LOW) 5.0/33.3 −1 mA/20 mA

Q

0–Q7

Flip-Flop Outputs 50/33.3 −1 mA/20 mA

Loading...

Loading...