© 2000 Fairchild Semiconductor Corporation DS009498 www.fairchildsemi.com

April 1988

Revised March 2000

74F194 4-Bit Bidirectional Universal Shi ft Register

74F194

4-Bit Bidirectional Universal Shift Register

General Description

The 74F194 is a high-speed 4-bit bidirectional universal

shift register. As a high-speed, multif unctional, sequential

building bl oc k, i t is us ef ul in a w id e va r i ety o f ap pl i cat i o ns. I t

may be used in seri al-s eria l, sh ift left, shif t r i ght , se rial- parallel, parallel-serial, and parallel-parallel data register

transfers.

Features

■ Typical shift frequency of 150 MHz

■ Asynchronous master reset

■ Hold (do nothing) mode

■ Fully synchronous serial or parallel data transfers

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

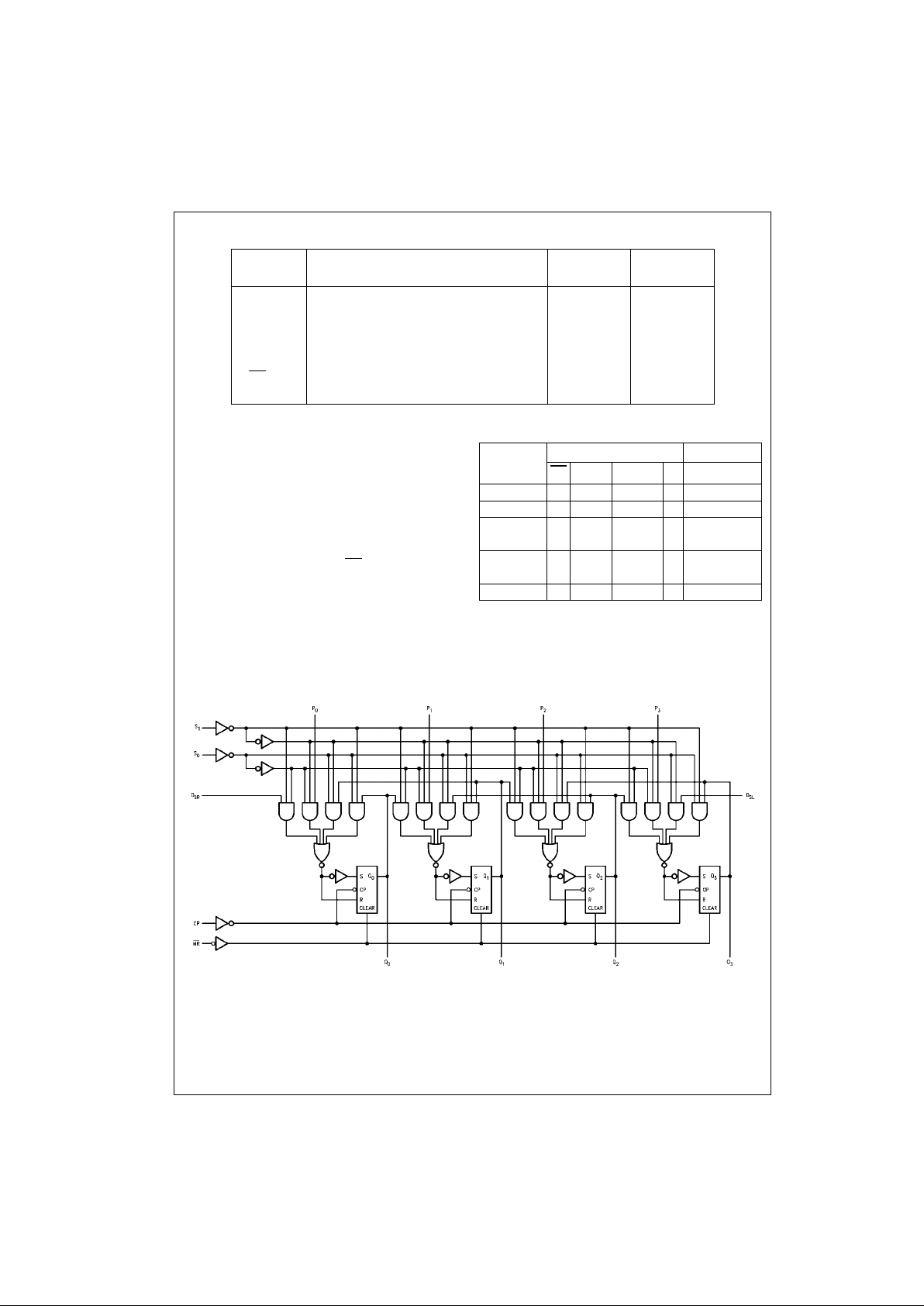

Logic Symbols

IEEE/IEC

Connection Diagram

Order Number Package Number Package Description

74F194SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F194SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F194PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

74F194

Unit Loading/Fan Out

Functional Description

The 74F194 conta ins four edge-trigge red D-type flip-flo ps

and the necessary inter stage logic to synchronously perform shift right, shift left, parallel load and hold operations.

Signals applied to the Selec t (S

0

, S1) inputs determine the

type of operation, as shown in the Mode S elect Table. Signals on the Select, Parallel data (P

0–P3

) and Serial data

(D

SR

, DSL) inputs can change when the clock is in either

state, provided only th at the r ecomm ended s etup an d hol d

times, with respect to the clock rising edge, a re observed.

A LOW signal on Master Reset (MR

) overrides all other

inputs and forces the outputs LOW.

Mode Select Table

H (h) = HIGH Voltage Level

L (l) = LOW Voltage Level

pn (qn) = Lower case letters indicate the state of the referenc ed input (or

output) one setup tim e prior to the LOW-to-HIGH c loc k t ransition.

X = Immaterial

Logic Diagram

Please note that this diagram is provided o nly f or t he understanding of lo gic operations and should not be used to estimate propagation delays.

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

S0, S

1

Mode Control Inputs 1.0/1.0 20 µA/−0.6 mA

P

0–P3

Parallel Data Inputs 1.0/1.0 20 µA/−0.6 mA

D

SR

Serial Data Input (Shift Right) 1.0/1.0 20 µA/−0.6 mA

D

SL

Serial Data Input (Shift Left) 1.0/1.0 20 µA/−0.6 mA

CP Clock Pulse Input (Active Rising Edge) 1.0/1.0 20 µA/−0.6 mA

MR

Asynchronous Master Reset Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

Q

0–Q3

Parallel Outputs 50/33.3 −1 mA/20 mA

Operating Inputs Outputs

Mode MR

S1S0DSRDSLPnQ0Q1Q2Q

3

Reset L X X X X X L L L L

Hold H l l X X X q

0q1q2q3

Shift Left H h l X l X q1q2q3L

Hhl X hXq

1q2q3

H

Shift Right H l h l X X L q

0q1q2

Hlhh XXHq0q1q

2

Parallel Load H h h X X pnp0p1p2p

3

3 www.fairchildsemi.com

74F194

Absolute Maximum Ratings(Note 1) Recomm ended Operating

Conditions

Note 1: Absolute maximum ratings are values beyon d which the device

may be damaged or have its useful life impaired . Functional operation

under these condit ions is not implied.

Note 2: Either voltage limit or curren t limit is sufficient to protect in puts.

DC Electrical Characteristics

Storage Temperature −65°C to +150°C

Ambient Temperature under Bias −55°C to +125°C

Junction Temperature under Bias −55°C to +150°C

V

CC

Pin Potential to Ground Pin −0.5V to +7.0V

Input Voltage (Note 2) −0.5V to +7.0V

Input Current (Note 2) −30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with V

CC

= 0V)

Standard Output −0.5V to V

CC

3-STATE Output −0.5V to +5.5V

Current Applied to Output

in LOW State (Max) t wice the rated I

OL

(mA)

Free Air Ambi ent Temperature 0°C to +70°C

Supply Voltage +4.5V to +5.5V

Symbol Parameter Min Typ Max Units

V

CC

Conditions

V

IH

Input HIGH Voltage 2.0 V Recognized as a HIGH Signal

V

IL

Input LOW Voltage 0.8 V Recognized as a LOW Signal

V

CD

Input Clamp Diode Voltage −1.2 V Min IIN = −18 mA

V

OH

Output HIGH 10% V

CC

2.5

VMin

IOH = −1 mA

Voltage 5% V

CC

2.7 IOH = −1 mA

V

OL

Output LOW 10% V

CC

0.5 IOL = 20 mA

Voltage

I

IH

Input HIGH

5.0 µAMaxVIN = 2.7V

Current

I

BVI

Input HIGH Current

7.0 µAMaxVIN = 7.0V

Breakdown Test

I

CEX

Output HIGH

50 µAMaxV

OUT

= V

CC

Leakage Current

V

ID

Input Leakage

4.75 V 0.0

IID = 1.9 µA

Test All Other Pins Grounded

I

OD

Output Leakage

3.75 µA0.0

V

IOD

= 150 mV

Circuit Current All Other Pins Grounded

I

IL

Input LOW Current −0.6 mA Max VIN = 0.5V

I

OS

Output Short-Circuit Current −60 −150 mA Max V

OUT

= 0V

I

CC

Power Supply Current 33 46 mA Max

Loading...

Loading...