Fairchild Semiconductor 74ACT2708PC, 74ACT2708CW Datasheet

February 1989

Revised January 1999

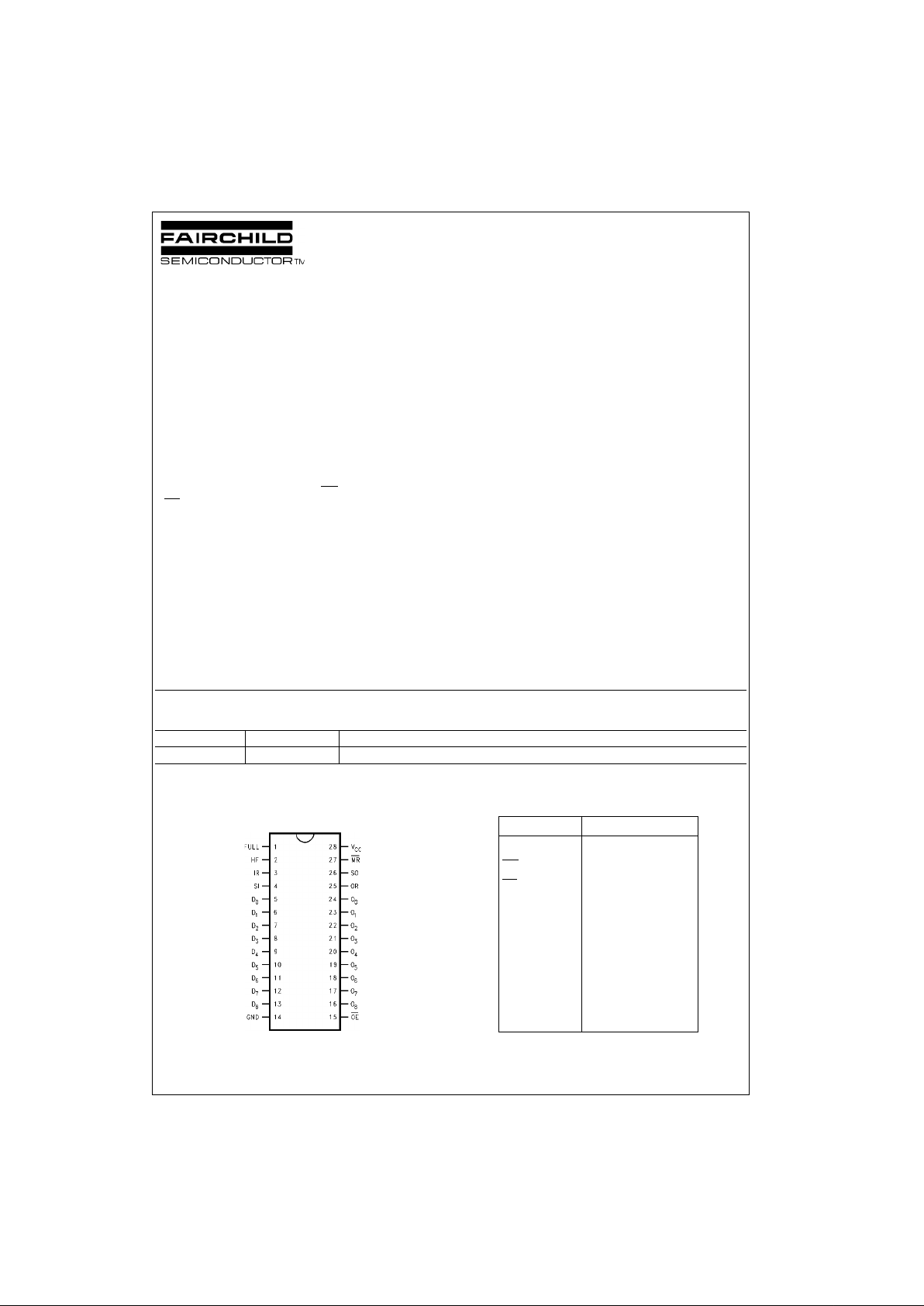

74ACT2708 64 x 9 First-In, First-Out Memory

© 1999 Fairchild Semiconductor Corporation DS010144.prf www.fairchildsemi.com

74ACT2708

64 x 9 First-In, First-Out Memory

General Description

The ACT2708 is an exp andable first-in, first-out memor y

organized as 64 words by 9 bits. An 85 MHz shift-in and 60

MHz shift-out typical data rate makes it ideal for high-speed

applications. It uses a dual port RAM architecture with

pointer logic to achi eve the high speed with ne gligible fallthrough time.

Separate Shift-In (SI) and Shift -Ou t (S O) clocks cont rol t he

use of synchronous or asynchr onous write or re ad. Other

controls include a Mas ter Reset (MR

) and Output Enable

(OE

) for initializing the internal registers and allowing the

data outputs to be 3-S TATE. Input Ready (I R) and Output

Ready (OR) signal when the FIFO is ready for I/O operations. The status flags HF and FULL indicate when the

FIFO is full, empty or half full.

The FIFO can be expanded to provide different word

lengths by tying off unused data inputs.

Features

■ 64-words by 9-bit dual port RAM organization

■ 85 MHz shift-in, 60 MHz shift-out data rate, typical

■ Expandable in word width only

■ TTL-compatible inputs

■ Asynchronous or synchronous operation

■ Asynchronous master reset

■ Outputs source/sink 8 mA

■ 3-STATE outputs

■ Full ESD protection

■ Input and output pi ns directly in line for easy boar d lay-

out

■ TRW 1030 work-alike operation

Applications

• High-speed disk or tape controllers

• A/D output buffers

• High-speed graphics pixel buffer

• Video time base correction

• Digital filtering

Ordering Code:

Device also available in Tape and Reel. Specify by appendin g s uf f ix let te r “X” to the ordering cod e.

Connection Diagram

Pin Assignment for DIP

Pin Descriptions

FACT is a tra demark of Fairchild Semico nductor Corporation.

Order Number Package Number Package Description

74ACT2708PC N28B 28-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600” Wide

Pin Names Description

D

0–D8

Data Inputs

MR

Master Reset

OE

Output Enable Input

SI Shift-In

SO Shift-Out

IR Input Ready

OR Output Ready

HF Half Full Flag

FULL Full Flag

O

0–O8

Data Outputs

www.fairchildsemi.com 2

74ACT2708

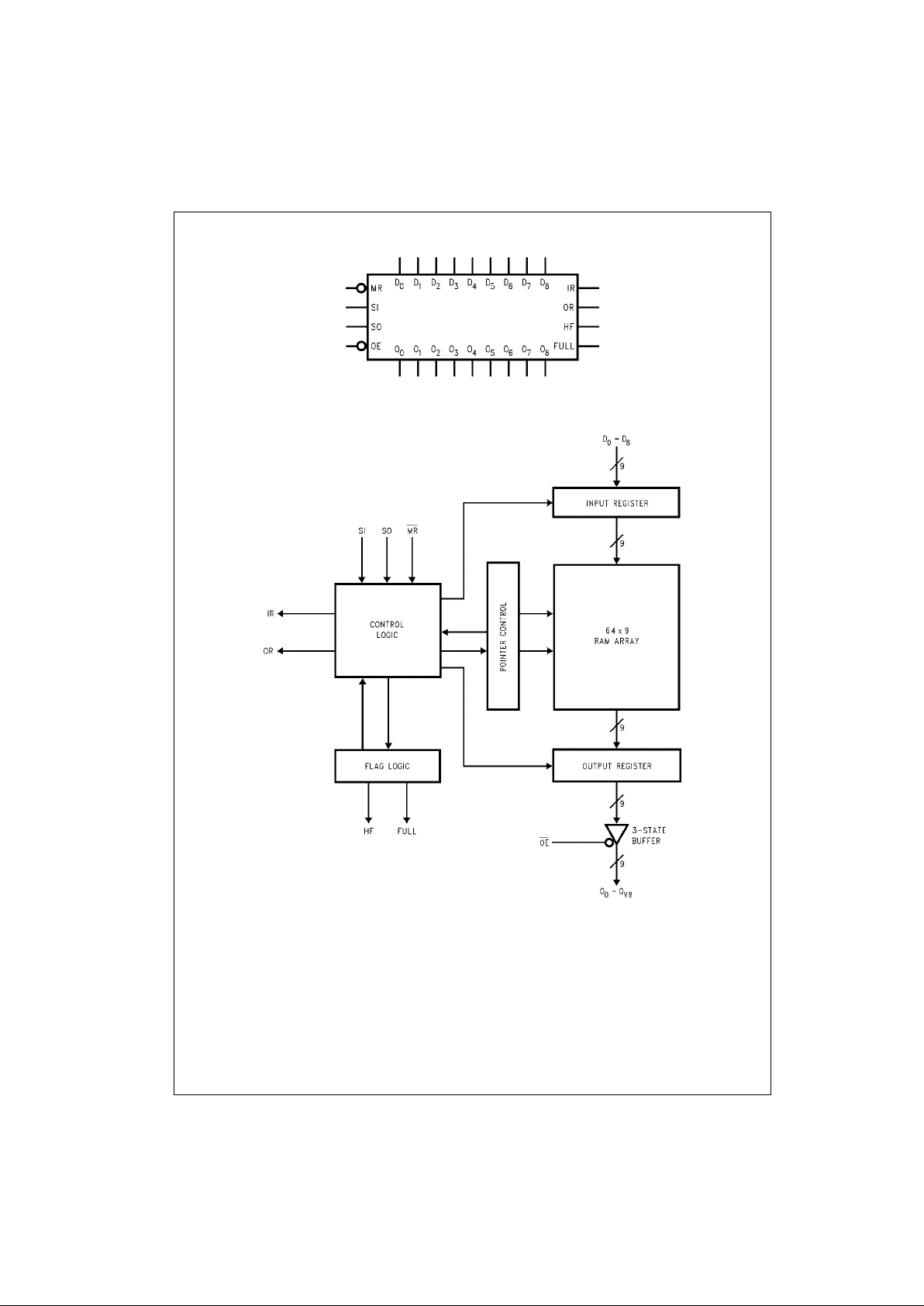

Logic Symbol

Block Diagram

3 www.fairchildsemi.com

74ACT2708

Functional Description

INPUTS

Data Inputs (D0–D8)

Data inputs for 9-bit wide d ata are TTL-compatible. Word

width can be reduced by tryin g unused inputs to ground

and leaving the corresponding outputs open.

Reset (MR

)

Reset is accomplished by pulsing th e MR

input LOW. Dur-

ing normal operation MR

is HIGH. A reset is requir ed aft er

power up to guarantee correct operation. On reset, the

data outputs go LOW, IR goes HIGH, OR goes LOW, FH

and FULL go LOW. During reset, both inter nal read and

write pointers are set to the first location in the array.

Shift-In (SI)

Data is written into the FIFO by pulsing SI HIGH. When

Shift-In goes HIGH, the data is l oad ed in to an i nte r n al da ta

latch. Data setup and hold times need to be adhered to

with respect to the falling edge of SI. The write cycle is

complete after the falling edge of SI. The shift-in is independent of any ongoing shift-out operation. After the first

word has been written in to the FIFO, the falling ed ge of SI

makes HF go HIGH, indicating a non-empty FIFO. The first

data word appears at the output after the falling edge of SI.

After half the memor y is filled, the next rising edge of SI

makes FULL go HIGH indicating a half-full FIFO. When the

FIFO is full, any further shift-ins are disabled.

When the FIFO is em pty and OE

is LOW, the falling edge

of the first SI will cause the first data word just shifted-in to

appear at the output, even though SO may be LOW.

Shift-Out (SO)

Data is read from the FIFO by the Shift-Out signal provided

the FIFO is not empty. SO going HIGH causes OR to go

LOW indicating that output stage is busy. On the falling

edge of SO, new data reaches the output after propagation

delay t

D

. If the last data has been shifted-o ut of the mem -

ory, OR continues to remain LOW, and the last word

shifted-out remains on the output pins.

Output Enable (OE

)

OE

LOW enables the 3-STATE output buffers. When OE is

HIGH, the outputs are in a 3-STATE mode.

OUTPUTS

Data Outputs (O0–O8)

Data outputs are enabled when OE

is LOW and in the 3-

STATE condition when OE

is HIGH.

Input Ready (IR)

IR HIGH indicates data can be shifted-in . When SI goes

HIGH, IR goes LOW, indicating input stage is busy. IR

stays LOW when the FIFO is full and goes HIGH after the

falling edge of the first shift-out.

Output Ready (OR)

OR HIGH indicates dat a can be shifted -out f rom t he FI FO.

When SO goes HIGH, OR goes LOW, indicating output

stage is busy. OR is LOW when the FIFO is reset or empty

and goes HIGH after the falling edge of the first shift-in.

Half-Full (HF)

This status flag alo ng with the FULL status flag indicates

the degree of fullness of the F IFO. On reset, HF is LOW; it

rises on the falling edg e of the first SI. Th e rising edg e of

the SI pulse that fills up the FIFO makes HF go LOW.

Going from the empty t o the full state with SO LOW, the

falling edge of the first SI causes HF to go HIGH, the rising

edge of the 33 rd SI causes FU LL t o go HIG H, and the rising edge of the 64th SI causes HF to go LOW.

When the FIFO is full, HF is LOW and the falling edge of

the first shift-out causes HF to g o HIGH indicating a “n onfull” FIFO.

Full Flag (FULL)

This status flag along with the HF status flag indicates the

degree of fullness of the FIFO. On reset, FULL is LOW.

When half the memory is filled, on the ri sing edge of the

next SI, the FULL flag goes HIGH. It remains set until the

difference between the write pointer and the read pointer is

less than or equal to o ne-half of the total memor y of the

device. The FULL flag then goes LOW on the rising edge of

the next SO.

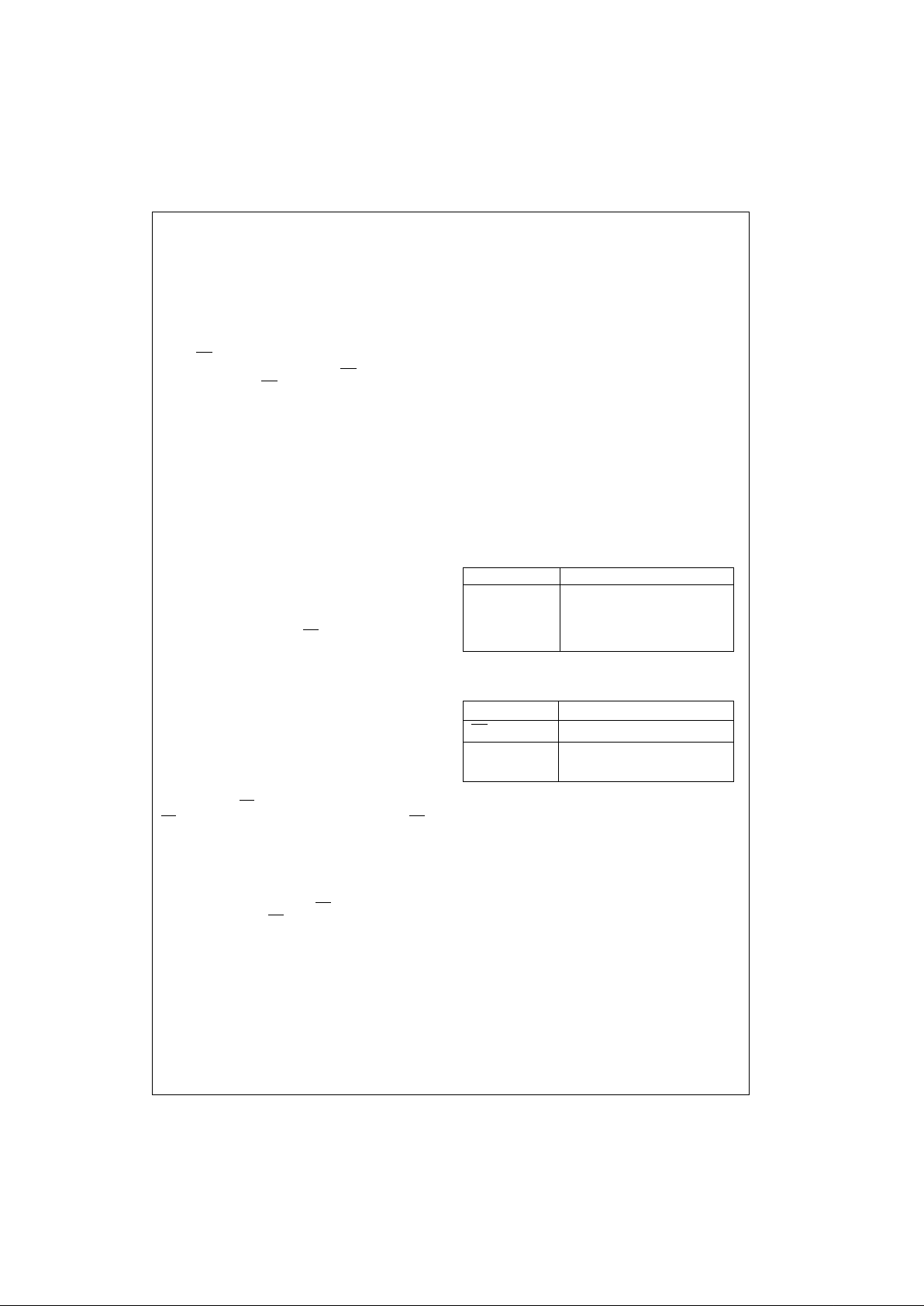

Status Flags Truth Table

H = HIGH Voltage Level

L = LOW Voltage Level

Reset Truth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

HF FULL Status Flag Condition

L L Empty

L H Full

H L <32 Locations Filled

H H ≥32 Locations Filled

Inputs Outputs

MR

SI SO IR OR HF FULL O0–O

8

H X X X X X X X

L X X H L L L L

www.fairchildsemi.com 4

74ACT2708

MODES OF OPERATION

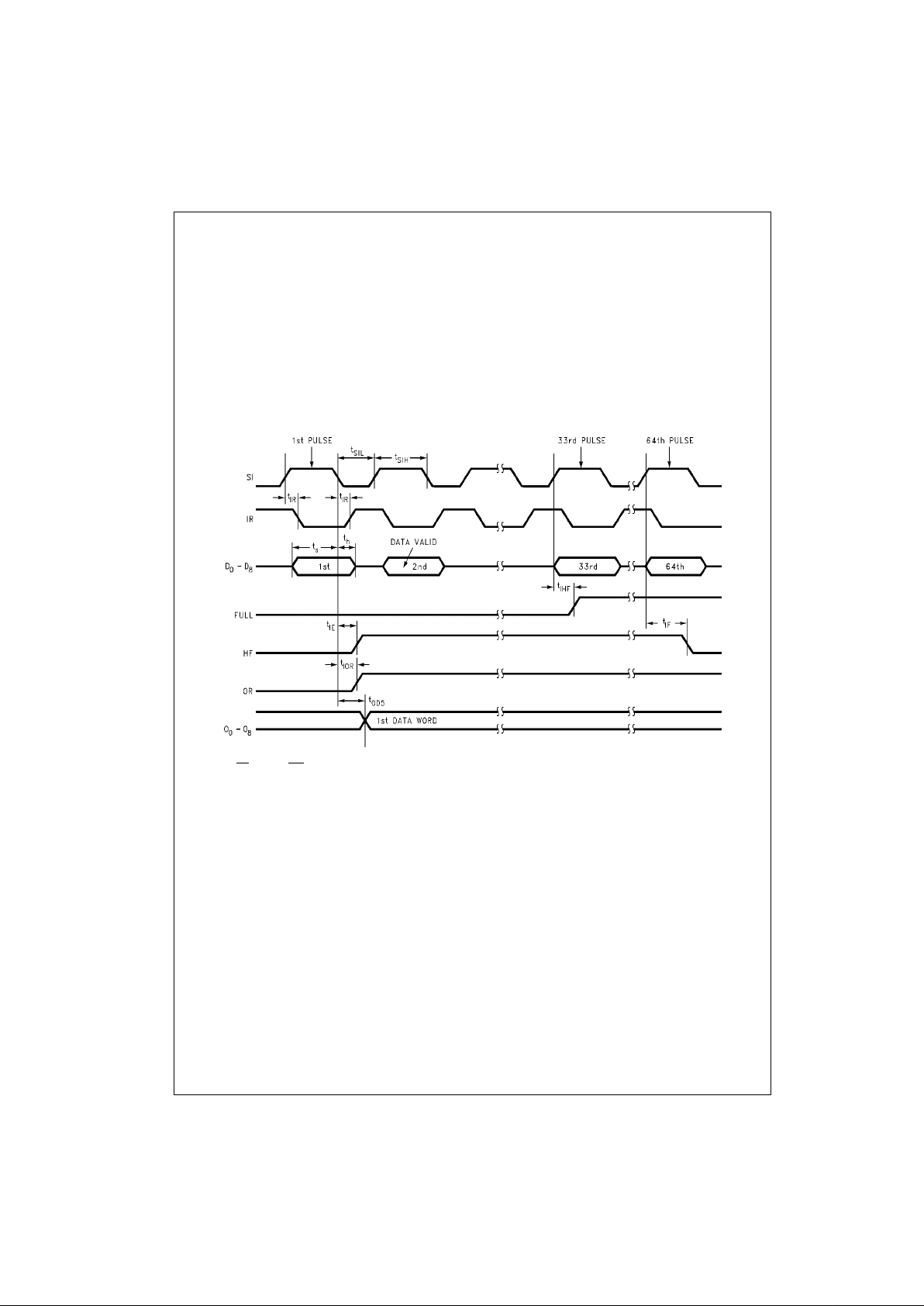

Mode 1: Shift in Sequence for FIFO Empty to Full

Sequence of Operation

1. Input Rea dy is initially HIGH; HF and FULL flags are

LOW. The FIFO is empty and prepared for valid dat a.

OR is LOW indicating that the FIFO is not yet ready to

output data.

2. Sh ift-In is set H IGH, and dat a is loaded in to the FIFO.

Data has to be settled t

s

before the falling edge of SI

and held t

h

after.

3. I nput Read y (IR) goes LOW prop agation delay t

IR

after

SI goes HIGH: input stage is busy.

4. Shift- In is set LOW; IR goes HIGH indicating the FIFO

is ready for additional data. Data just shifted -in arrives

at output propagation delay t

OD5

after SI falls. OR goes

HIGH propagation delay t

IOR

after SI goes LOW, indi-

cating the FIFO has valid data on it s outputs. HF goes

HIGH propagation delay t

IE

after SI falls, indicating the

FIFO is no longer empty.

5. Th e process is repeated thr ough the 64th data word.

On the rising edge of the 33rd SI, FULL flag goes HIGH

propagation delay t

IHF

after SI, indicating a half-full

FIFO. HF goes LOW propagation de lay t

IF

after the ris-

ing edge of the 64th puls e indicating that the FIFO is

full. Any further shift-ins are disabled.

Note: SO and OE are LOW; MR is HIGH.

FIGURE 1. Modes of Operation Mode 1

Loading...

Loading...