查询USB1T1102供应商

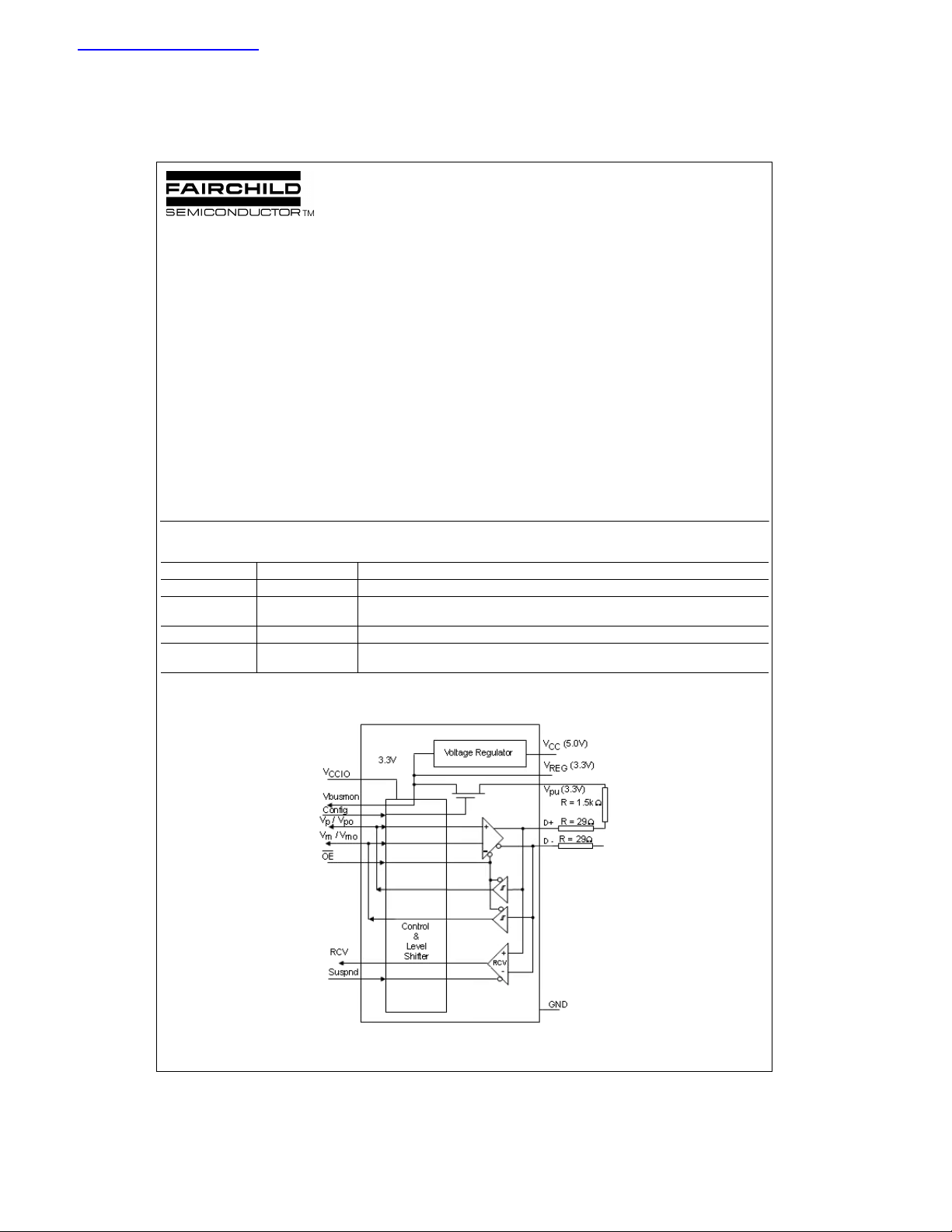

USB1T1102 • USB1T1102R (Preliminary)

Universal Serial Bus Peripheral Transceiver

with Voltage Regulator

USB1T1102 • USB1T1102R (Preliminary) Universal Serial Bus Peripheral Transceiver with Voltage Regulator

August 2004

Revised August 2004

General Description

This chip provides a USB Transceiver functionality with a

voltage regulator that is compliant to USB Specification

Rev 2.0. this integrated 5V to 3.3V regulator allows interfacing of USB Application specific devices with supply voltages ranging from 1.65 V to 3.6V wi th the physica l layer of

Universal Serial Bus. It is capable of operating at 12Mbits/s

(full speed) data ra tes and hence is fu lly co mpliant to U SB

Specification Rev 2.0. The Vbusmon pin allows for monitoring the Vbus line.

The USB1T1102 also provides exceptional ESD pro tection

with 15kV contact HBM on D

+, D− pins.

Features

■ Complies with Universal Serial Bus Specification 2.0

■ Integrated 5V to 3.3V voltage regulator for powering

VBus

■ Utilizes digital inputs and outputs to transmit and receive

USB cable data

■ Supports full speed (12Mbits/s) data rates

■ Ideal for portable electronic devices

■ MLP technology package (16 pin) with HBCC footprint

■ 15kV contact HBM ESD protection on bus pins

Ordering Code:

Order Number Package Number Package Description

USB1T1 102MPX MLP14D 14-Terminal Molded Leadless Package (MLP), 2.5mm Square

USB1T1102RMPX

(Preliminary)

USB1T1 102MHX MLP16HB 16-Terminal Molded Leadless Package (MHBCC), JEDEC MO-217, 3mm Square

USB1T1102RMHX

(Preliminary)

MLP14D 14-Terminal Molded Leadless Package (MLP), 2.5mm Square

MLP16HB 16-Terminal Molded Leadless Package (MHBCC), JEDEC MO-217, 3mm Square

Logic Diagram

Note: On the USB1T1102R the 1.5k resistor is integrat ed into the part, and connects VPU and D+ eliminating the need for this external pull-up resistor.

© 2004 Fairchild Semiconductor Corporation DS500877 www.fairchildsemi.com

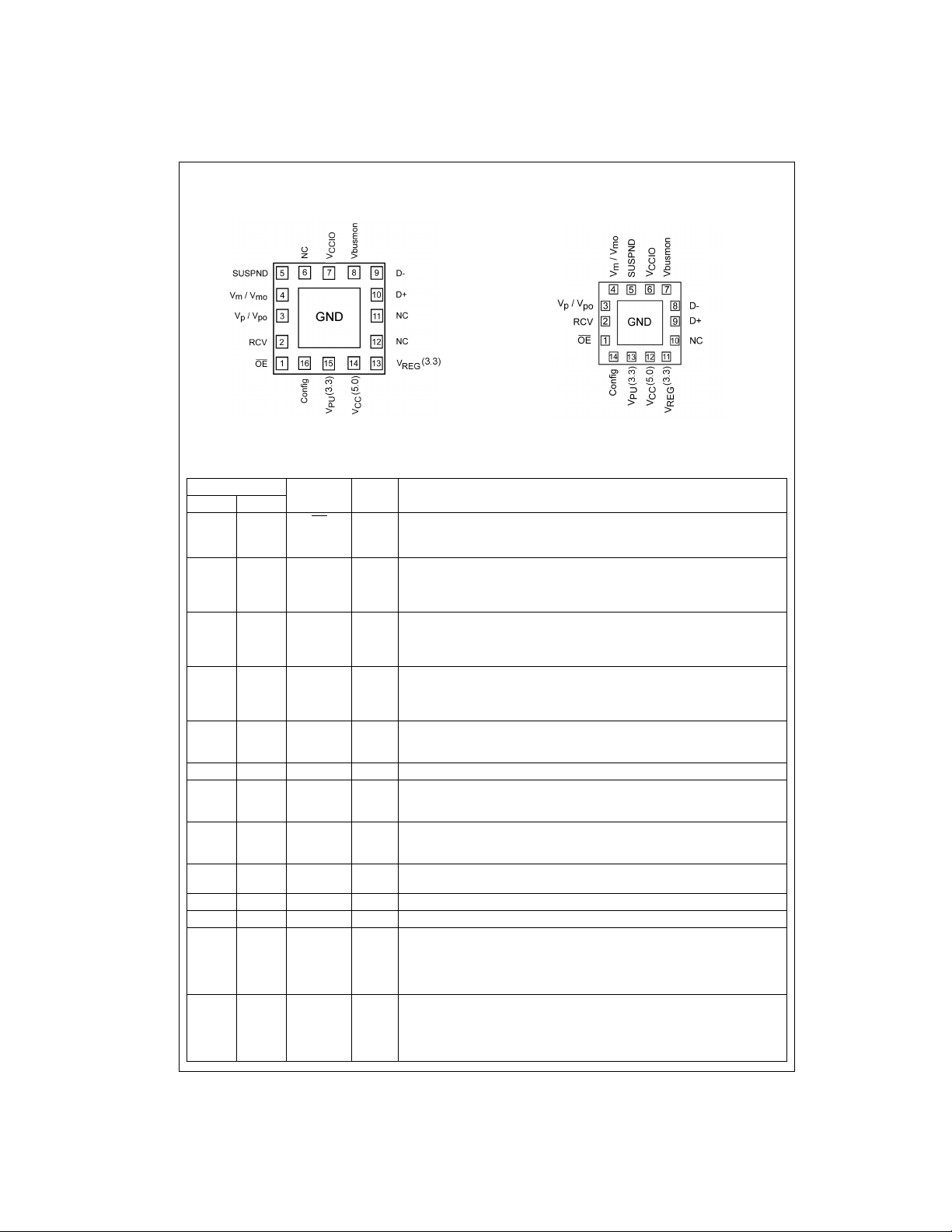

Connection Diagrams

MLP16 GND Exposed Diepad

(Bottom View)

Terminal Descriptions

USB1T1102 • USB1T1102R (Preliminary)

Terminal Number

MLP14 MLP16

11 OE

2 2 RCV O Receive Data Output:

33V

44V

5 5 SUSPND I Suspend:

— 6 NC No Connect

67V

7 8 Vbusmon O Vbus monitor output (CMOS level relative to V

9, 8 10, 9 D

10 11 NC No Connect

— 12 NC No Connect

11 13 V

12 14 V

Terminal

Name

I/O Terminal Description

I Output Enable:

Active LOW enables the transceiver to transmit data on the bus. When not

active the transceiver is in the receive mode (CMOS level is relative to V

Non-inverted CMOS level out put for USB differe ntial Inpu t (CMO S out put level

p/Vpo

is relative to V

and preserved during SE0 condi tio n.

I/O Single-ended D+ receiver output VP (CMOS level relative to V

Used for external detection of SE0, error conditions, speed of connected device;

CCIO

Pin also acts as drive data input V

Output drive is 4 mA buffer.

m/Vmo

CCIO

I/O Single-ended D− receiver output Vm (CMOS level relative to V

Used for external detection of SE0, error conditions, speed of connected device;

Pin also acts as drive data input V

Output drive is 4 mA buffer.

Enables a low power state (CMOS level is relative to V

SUSPND pin is active (HIGH) it will drive the RCV pin to logic “0” state.

Supply Voltage for digital I/O pins (1.65V to 3.6V):

When not connected the D

totally independent of V

When Vbus

Vbusmon

+, D− AI/O Data +, Data −:

(3.3V) Internal Regulator Option:

REG

Differential data bus conforming to the USB standard.

Regulated supply output voltage (3.0V to 3.6V) during 5V operation;

decoupling capacitor of at least 0. 1

Regulator ByPass Option:

> 4.1V then Vbusmon = HIGH and when Vbus < 3.6V then

= LOW. If SUSPND = HIGH then Vbusmon is pulled HIGH.

Used as supply voltage input for 3.3V operation.

(5.0V) Internal Regulator Option:

CC

Used as supply voltage input (4.0V to 5.5V); can be connected directly to USB

line Vbus.

Regulator ByPass Option:

Connected to V

REG

). Driven LOW when SUSPN is HIGH; RCV output is stable

+ and D− pins are in 3-STATE. This supply bus is

(5V) and V

CC

(3.3V)

MLP14 GND Exposed Diepad

(Bottom View)

(see Table 1 and Table 2).

po

(see Table 1 and Table 2).

mo

). While the

CCIO

(3.3V).

REG

CCIO

):

µF is required.

CCIO

CCIO

)

CCIO

):

):

www.fairchildsemi.com 2

Terminal Descriptions (Continued)

USB1T1102 • USB1T1102R (Preliminary)

Te rminal Number

MLP14 MLP16

13 15 V

Terminal

Name

(3.3V) Pull-up Supply Voltage (3.3V ± 10%):

PU

I/O Terminal Description

Connect an external 1.5k

Pin function is controlled by Config input pin:

Config

= LOW − V

= HIGH − V

Config

Ω resistor on D+ (FS data rate);

(3.3V) is fl oa t i ng ( H i gh I mp e da nc e ) fo r z er o pu ll - up cu rr en t .

PU

(3.3V) = 3.3V; internally connected to V

PU

REG

(3.3V).

14 16 Config I USB connect or disconnect software control input.

Configures 3.3V to external 1.5k

Exposed

Diepad

Exposed

Diepad

GND GND GND supply down bonded to exposed diepad to be connected to the PCB GND.

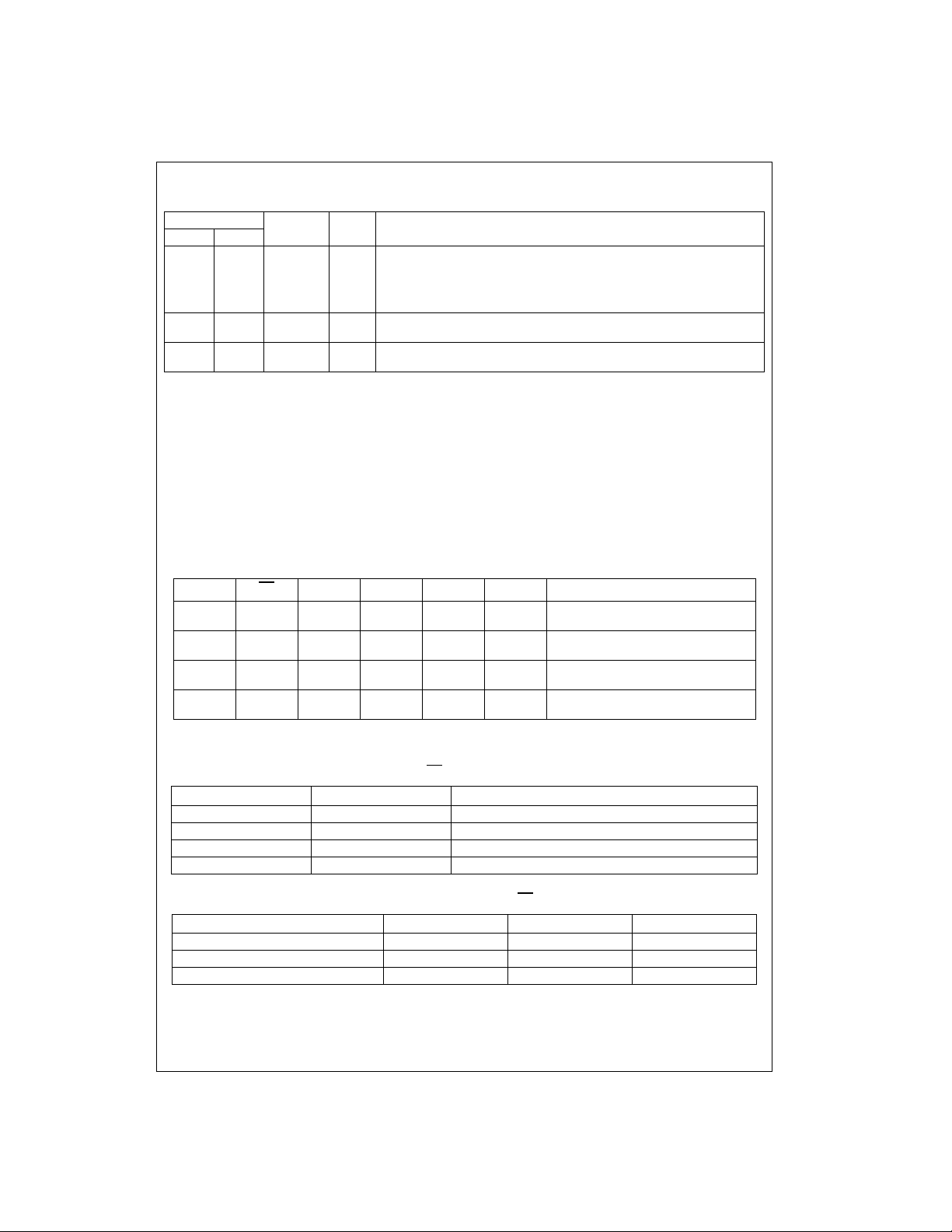

Functional Description

The USB1T1102 transceiver is designe d to convert CMOS

data into USB differentia l bus signal levels a nd to convert

USB differential bus signal to CMOS data.

To minimize EMI and noise the outputs are edge ra te controlled with the rise and fall times controlled and defined for

full speed data rates only (12Mbits/s) . The rise, fall times

are balanced between the differential pins to minimize

skew.

The USB1T1102 differs from earlier USB Transceiver in

that the V

than discrete input and output pins. Table 1 describes the

specific pin functionality selection. Table 2 and Table 3

describe the specific Truth Tables for Driver and Receiver

operating functions.

The USB1T1102 also has the capability of various power

supply configurations to support mixed voltage supply

applications (see Table 4) and Section 2.1 for detailed

descriptions.

Ω resistor on D+ when HIGH.

and Vpo/Vmo pins are now I/O pins rat her

p/Vm

Functional Tables

TABLE 1. Function Select

SUSPND OE D+, D− RCV

L L Driving &

Active V

Receiving

L H Receiving

Active V

(Note 1)

H L Driving Inactive

HH3-STATE

(Note 1)

Note 1: Signal levels is function of connection and/or pull-up/pull-down resistors.

Note 2: For SUSPND = HIGH mode the differential receive r is inactive and t he output RCV is forced LOW. The out-of-suspend s ignaling (K) is detected via

the single-ended receivers of the V

and Vm/Vmo pins.

p/Vpo

(Note 2)

Inactive

(Note 2)

V

p/Vpo

Input Vmo Input Normal Driving

po

Output Vm Output Receiving

p

Input Vmo Input Driving during Suspend

V

po

V

Output Vm Output Low Power State

p

TABLE 2. Driver Functi on (OE = L) using Differential Input Interface

V

m/Vmo

Vp/V

po

L L SE0 (Note 3)

L H Differential Logic 1

H L Differential Logic 0

H H Illegal State

Note 3: SE0 = Single Ended Zero

TABLE 3. Receiver Function (OE = H)

D

+, D− RCV

Differential Logic 1 H H L

Differential Logic 0 L L H

SE0 X L L

X = Don’t Care

Vm/V

mo

(Differential Receiver Active)

(Differential Receiver Inactive)

Data

V

p/Vpo

Function

Vm/V

mo

3 www.fairchildsemi.com

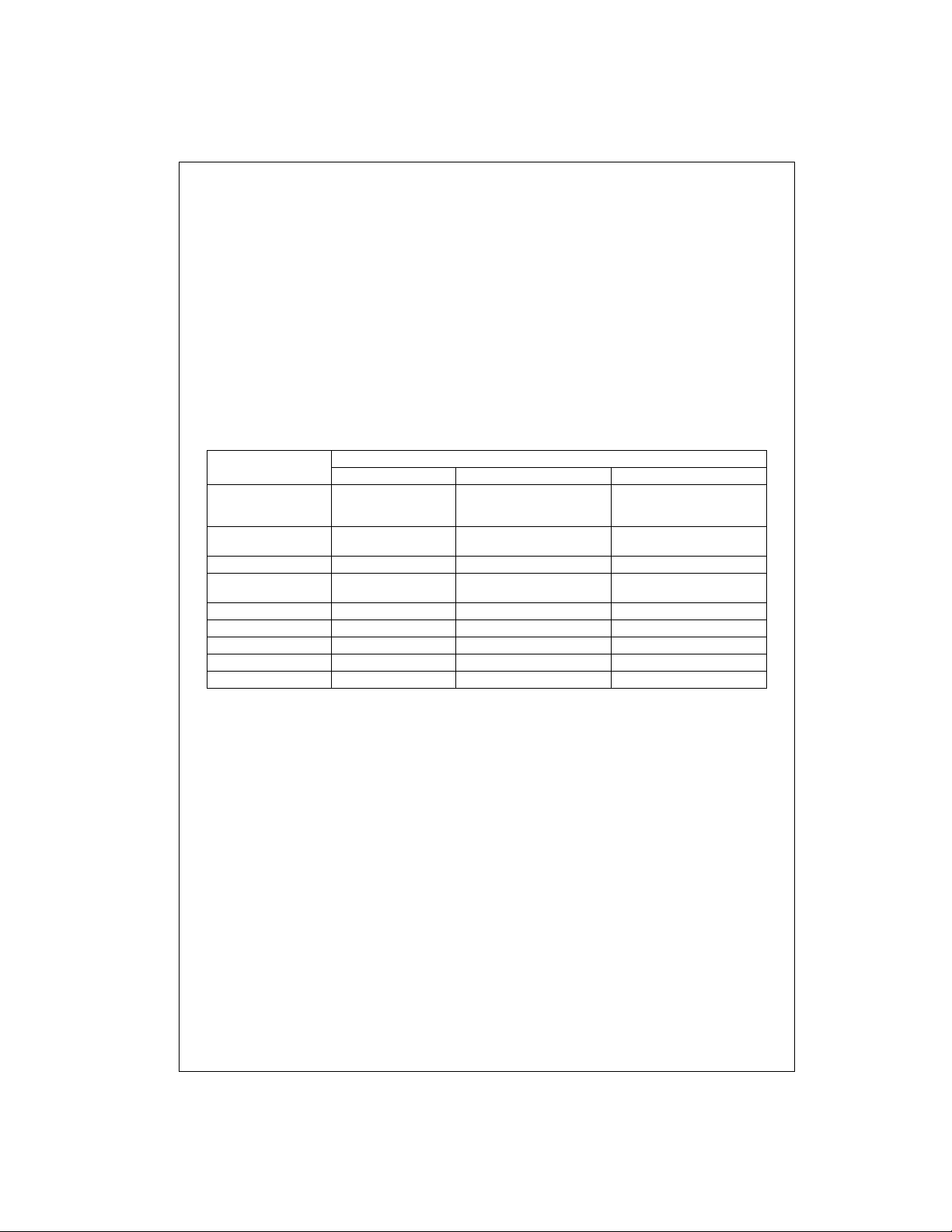

Power Supply Configurations and Options

The two modes of power supply operation are:

• Normal Mode: V

V

, VCC (5V) and [V

CCIO

for Bypass mode]

1. For 5V operation V

(4.0V to 5.5V) and the internal voltage regulator then

produces 3.3V for the USB connections.

2. For 3.3V operation both V

nected to a 3.3V source (3.0V to 3.6V)

In both cases for normal mode the V

dent voltage source ( 1.65V to 3.6V ) that is a function of

the external circuit configuration.

Pins

USB1T1102 • USB1T1102R (Preliminary)

V

CC

V

REG

V

V

PU

D

V

p/Vpo

RCV L Function of Mode Set Up Function of Mode Set Up

Vbusmon L Function of Mode Set Up Function of Mode Set Up

OE, SUSPND, Config Hi-Z Function of Mode Set Up Function of Mode Set Up

and VCC (5V) are connected or

CCIO

(3.3V) and VCC (5V) shorted

REG

is connected to 5V source

CC

CC

and V

REG

is an indepen-

CCIO

are con-

TABLE 4. Power Supply Configuration Options

Power Supply Mode Configuration

Sharing Normal (Regulated Output) Normal (Regulator Bypass)

(5V) Not Connected Connected to 5V Source Connected to V

(3.3V) Not Connected 3.3V, 300 µA

CCIO

1.65V to 3.6V Source 1.65V to 3.6V Source 1.65V to 3.6V Source

(3.3V) 3-STATE (Off) 3.3V Available if

+, D− 3-STATE Function of Mode Set Up Function of Mode Set Up

, Vm/V

mo

L Function of Mode Set Up Function of Mode Set Up

• Sharing Mode: V

are not connected. In thi s mode the D+ and D−

V

REG

is only supply connected. VCC and

CCIO

pins are 3-STATE and the USB1T1102 allows external

signals up to 3.6V to share the D

Internally the circuitry limits leakage from D

pins (maximum 10 µA) a nd V

+ and D− bus lines.

such that device is in

CCIO

+ and D−

low power (suspended) sta te. Pins Vbusmon and RCV

are forced LOW as an indication of this mode with Vbusmon being ignored during this state.

A summary of the Supply Co nfigurations is described in

Table 4.

(3.3V)

[Max Drop of 0.3V]

REG

(2.7V to 3.6V)

Regulated Output

Config

= HIGH

Connected to 3.3V Source

3.3V Available if

Config = HIGH

www.fairchildsemi.com 4

ESD Protection

ESD Performance of the USB1T1102

HBM D

+/D−: 15.0kV

HBM, all other pins (Mil-Std 883E): 6.5kV

ESD Protection: D

Since the differential pins of a USB transceiver may be

subjected to extreme ESD voltages, additional immunity

has been included in the D

mising performance. The USB1T1102 differential pins have

ESD protection to the following limits:

• 15kV using the contact Human Body Model

• 8kV using the Contact Discharge method as sp eci fie d in

IEC 61000-4-2

Human Body Model

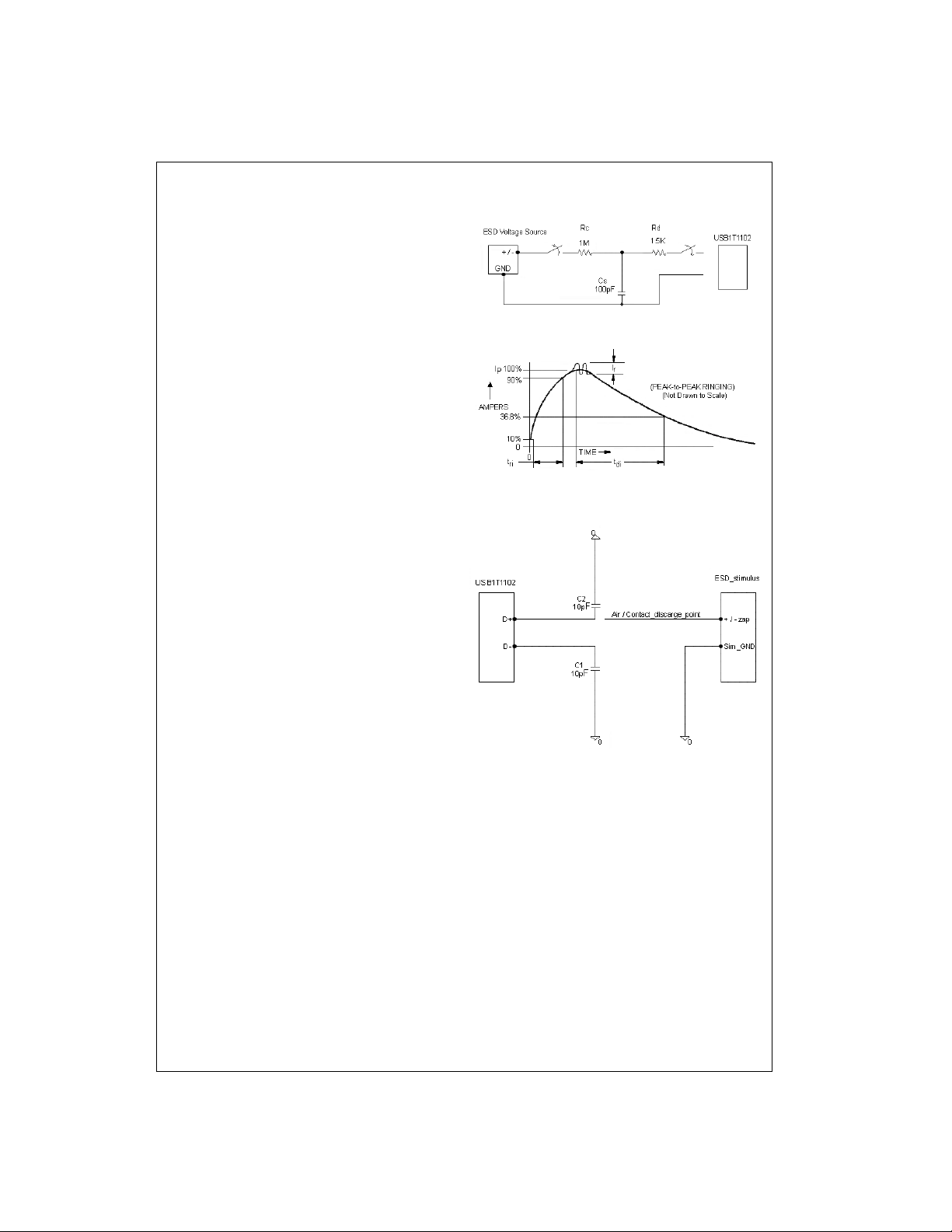

Figure 1 shows the schematic representation of the Human

Body Model ESD event. Figure 2 is the ideal waveform representation of the Human Body Model.

IEC 61000-4-2, IEC 60749-26 and IEC 60749-27

The IEC 61000-4-2 standa rd covers ESD testing and pe rformance of finished equipment, and as such evaluates the

equipment in its entirety for ESD immunity. Fairchild

Semiconductor has evaluated this device using the

IEC 6100-4-2 representative system model depicted in Figure 3. Under the additi onal standa rds set forth by the IEC,

this device is also compliant with IE C 6074 9-2 6 (H BM) and

IEC 60749-27 (MM).

Additional ESD Test Conditions

For additional inform atio n regar ding our produ ct test methodologies and performance levels, please contact Fairchild

Semiconductor.

+/D− Pins

+ and D− pins without compro-

USB1T1102 • USB1T1102R (Preliminary)

FIGURE 1. Human Body ESD Test Model

FIGURE 2. HBM Current Waveform

FIGURE 3. IEC 61000-4-2 ESD Test Model

5 www.fairchildsemi.com

Loading...

Loading...